# **AEAT-84AD**

# 14/12 Bit Multi-turn Encoder Module

# **Data Sheet**

### Description

The AEAT-84AD provides all functions as an optoelectronic-mechanical unit in order to implement, with single turn absolute encoder, an absolute multiturn encoder with a combined capacity of up to 30 bits at extended temperature.

The unit consists of an IR-LED circuit board, a phototransistor (PT) circuit board, and 6 or 7 gear wheels arranged in between the PCBs.

#### **Specifications**

The multi-turn unit is available in the following versions:

- 12-bit solid shaft

- 14-bit solid shaft

### **Features**

- 16384 (14bits) and 4096 (12bits) revolution count versions

- Optical, absolute multi-turn assembly with max. Ø55 mm and typical height 12.2 mm.

- Operating temperatures of -40°C to +125°C

- Mechanical coupling by means of 14 teeth gear pinion with module of 0.3

- Operating speeds up to 12,000 rpm

- A 2x4-pole pin strip for power supply and signal

### **Applications**

- Major component of Multi-turn housed encoder

- Cost effective solution for direct integration into OEM systems

- Linear positioning system

#### **Benefits**

- No battery or capacitor required for number of revolution counting during power failure

- Immediate position detection on power up

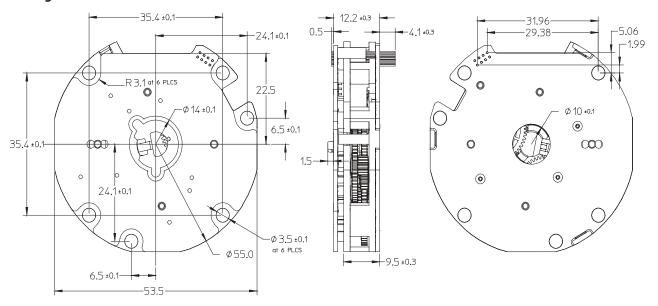

### **Package Dimensions**

#### Notes:

- 1. 3rd Angle Projection

- 2. Dimensions are in millimeters

- 3. Example of matching connector: MPE GARRY 521 Series, No. BL21-43GGG-008

Figure 1. Package dimensions

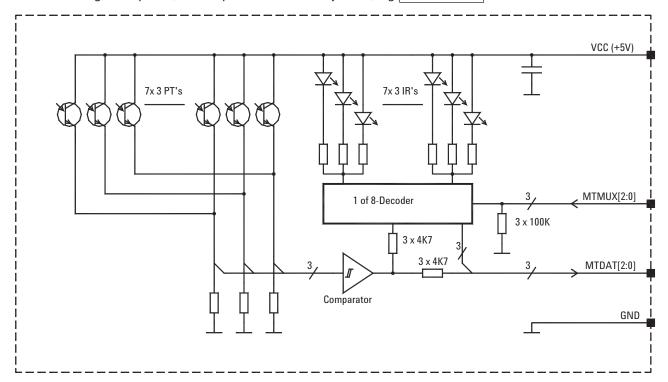

# **Block Diagram and Detailed Description**

In the following descriptions, the I/O pins are enclosed by a box, e.g., MTMUX[2:0].

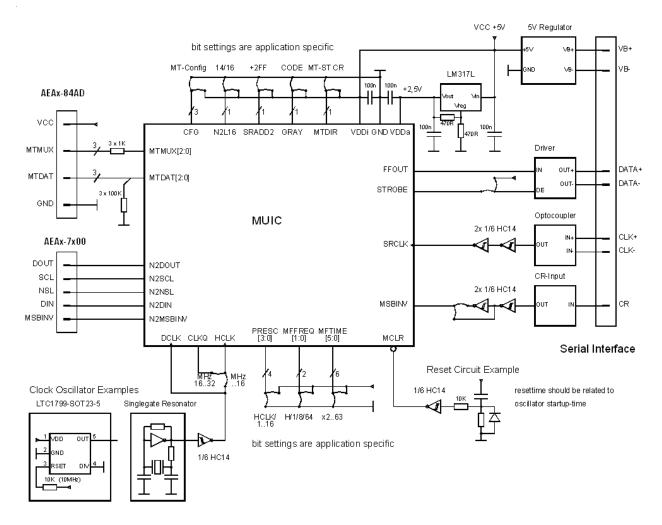

Figure 2. Block Diagram

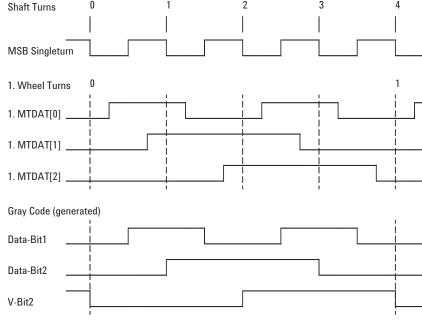

### **Multiplexing and Position Data**

Each of the 1:4 reduced 7 coded gear wheels generates a 3-bit code, from which the 14-bit Gray code can be generated as position data through V-bit processing.

The 3-bit code is identical electrically for all gear wheels, only the projection on the mechanical angle (the revolutions) is different according to the 1:4 divisions.

The code and the data bits and V-bits to be generated are shown in the Figure 3 for the gear wheel 1:

Figure 3. Multiplexing Diagram for gear wheel 1

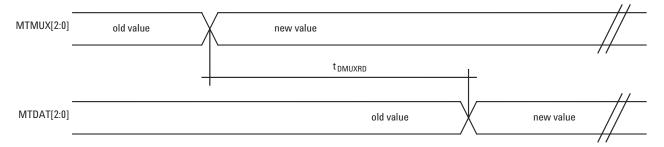

The 3-bit codes of the gear wheels 1 to 7 are output on MTDAT[2:0] demultiplexed with MTMUX[2:0]. Here, the binary value on MTMUX[2:0] corresponds to the gear-wheel number (1 = gear wheel 1, 2 = gear wheel 2, etc.). The configuration is displayed with the value "0."

Table 1 shows the assignments:

Table 1. Demultiplexing Diagram for all gear wheels

| Bin/ Dec<br>MTMUX [2:0] | MTDAT[2]           | MTDAT[1]                 | MTDAT[0]        | Notes |  |

|-------------------------|--------------------|--------------------------|-----------------|-------|--|

| 001 / 1                 |                    | 3-bit gear whe           | eel 1           |       |  |

| 010 / 2                 | 3-bit gear wheel 2 |                          |                 |       |  |

| to                      | to                 |                          |                 |       |  |

| 111 / 7                 | ;                  | 3-bit gear whe           | el 7            |       |  |

| 000 / 0                 | always 1           | 0 = 12 bit<br>1 = 14 bit | 1 = Solid Shaft | 1     |  |

Notes:

1. Applicable for AEAx-84AD solid shaft version only

### **Gray code-generation**

For the readout schematic of the multi-turn code gears, i.e. with the user's microcontroller, there must be a logical replication of the V-bit multiplexers. This can be done by a bit manipulation or by look up tables. Care needs to be taken with the real time readout conditions.

#### The procedure is as follows:

- The 3 bits (MTDAT[2:0]) of each gear (C1[2:0] to C7[2:0]) are continuously de-multiplexed. Thus there are maximal 3 bits x 7gears = 21-bit AEAT-84AD data in parallel.

- 2. Synchronous to the readout of the single turn absolute encoder, those AEAT-84AD bits (depending on the MSB bit, i.e. SEL-bit, of the single turn encoder) needs to be complemented to the complete Gray code word (cascading).

- 3. The bit change of the complete Gray code will be synchronized by the single turn absolute encoder and thus electronically eliminating gear play.

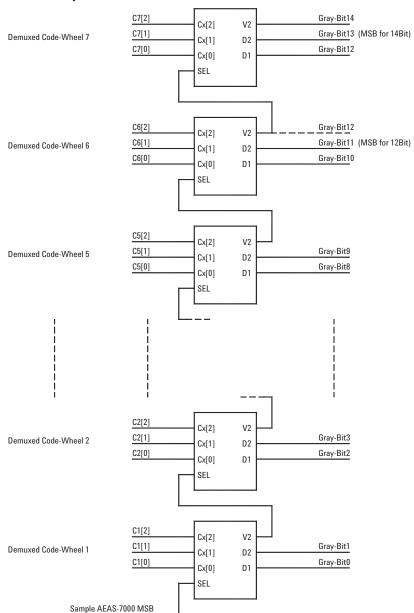

The logic diagram for ONE gear is shown in the following diagram (V-bit-Multiplexer), Figure 4.

#### **Logic Diagram**

From MTDAT-Demux

(Code-Wheel x)

4x MUX2

Cx[2]

Cx[1]

V2

(V-Bit2)

D2

(Data-Bit2)

XOR

D1

(Data-Bit1)

| SEL | Cx[0] | Cx[1] | Cx[2] | D1 | D2 | V2 |

|-----|-------|-------|-------|----|----|----|

| 0   | 0     | 0     | 0     | 0  | 0  | 0  |

| 0   | 1     | 0     | 0     | 0  | 0  | 0  |

| 1   | 1     | 0     | 0     | 1  | 0  | 0  |

| 1   | 1     | 1     | 0     | 1  | 0  | 0  |

| 0   | 1     | 1     | 0     | 1  | 1  | 0  |

| 0   | 0     | 1     | 0     | 1  | 1  | 0  |

| 1   | 0     | 1     | 0     | 0  | 1  | 0  |

| 1   | 0     | 1     | 1     | 0  | 1  | 0  |

| 0   | 0     | 1     | 1     | 0  | 1  | 1  |

| 0   | 1     | 1     | 1     | 0  | 1  | 1  |

| 1   | 1     | 1     | 1     | 1  | 1  | 1  |

| 1   | 1     | 0     | 1     | 1  | 1  | 1  |

| 0   | 1     | 0     | 1     | 1  | 0  | 1  |

| 0   | 0     | 0     | 1     | 1  | 0  | 1  |

| 1   | 0     | 0     | 1     | 0  | 0  | 1  |

| 1   | 0     | 0     | 0     | 0  | 0  | 1  |

Figure 4. Logic Diagram and Truth Table for one of the gear wheels

The Figure 5 shows the cascading of the V-bit- Multiplexer of all gear wheels. The outputs are the 14bits Gray code in parallel.

The MSB of the complete code is dependant on the total resolution of the system. It can be used in steps of 2 bits (14Bit,12Bit,...etc). Unused higher bits should be masked to logical zero.

With the data-multiplexer IC version of the multi-turn encoder module, the data multiplexer IC will perform the complete driving and data processing of the encoder units while maintaining all time constraints.

There is an IC available to combine both the AEAS-7x00 13/16bit single turn component and the AEAx-84AD 12/14bit multiturn module into one-single powerful multi-turn absolute encoder. This one-stop solution enables the design of a high-end absolute encoder with minimum component count at integration level. Figure 6 shows an application example of integration of single-turn absolute encoder and multiturn module using MUIC.

#### Note

To simplify the synchronization with single-turn absolute encoder(e.g. AEAS-7000), the total solution has been embedded into a single chip - MUIC. Please refer to the Ordering Information for this device.

### V-bit-Multiplexer Cascade

Figure 5. The cascading of V-bit-Multiplexer of all gear wheels

### **Application Example of Multiturn Absolute Encoder**

Figure 6. Application example of integration of single-turn absolute encoder module and multiturn module using MUIC.

#### **Device Selection Guide 1**

| Part Number     | Resolution | Operating Temperature (°C) | Output Format | DC Supply Voltage (V) |

|-----------------|------------|----------------------------|---------------|-----------------------|

| AEAT-84AD-LBSC0 | 12 bit     | -40 to 125                 | Multiplexed   | 5.0 to 5.5            |

| AEAT-84AD-LBSF0 | 14 bit     | -40 to 125                 | Multiplexed   | 5.0 to 5.5            |

#### Notes

<sup>1.</sup> SSI interface is enabled through MUIC. Please refer to Ordering Information for MUIC.

### Absolute Maximum Ratings 1, 2

| Parameter                       | Symbol           | Limits            | Units |  |

|---------------------------------|------------------|-------------------|-------|--|

| DC Supply Voltage               | VCC              | -0.3 to + 6.0     | V     |  |

| Input Voltage                   | Vi               | -0.5 to 5.5       | V     |  |

| Output Voltage                  | V <sub>o</sub>   | -0.5 to +VCC +0.5 | V     |  |

| Moisture Level (Non-Condensing) | %RH              | 85                | %     |  |

| Encoder Shaft Speed             | S <sub>RPM</sub> | Max 12000         | rpm   |  |

| Storage Temperature             | $T_{stg}$        | -40 to 125        | °C    |  |

#### Notes

- 1. Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

- 2. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 3. This device meets the ESD ratings of the IEC61000-4-2 Level 2 (4KV).

### **Recommended Operating Conditions**

| Parameter            | Symbol               | Values         | Units | Notes |

|----------------------|----------------------|----------------|-------|-------|

| DC Supply Voltage    | VCC                  | +5.0 / +5.5    | V     |       |

| Ambient Temperature  | $T_{amb}$            | -40 to +125    | °C    |       |

| Multiplex Read Delay | $t_{	extsf{DMUXRD}}$ | 64             | μs    |       |

| Encoder Shaft Speed  | S <sub>RPM</sub>     | 10000 or below | rpm   | 1     |

#### Notes

### **DC Characteristics**

DC Characteristics over Recommended Operating Range, typical at 25 °C

|                                              |                                  |                      |            | Value | S   |       |

|----------------------------------------------|----------------------------------|----------------------|------------|-------|-----|-------|

| Parameter                                    | Symbol                           | Condition            | Min        | Тур.  | Max | Units |

| MTDAT[2:0] Output High Voltage (10k Pull-up) | $V_{\text{OH}}$                  | $I_{0H} = -50\mu A$  | 4.0        |       |     | V     |

| MTDAT[2:0] Output Low Voltage (4k7 Series-R) | $V_{0L}$                         | $I_{0L} = -50\mu A$  |            |       | 0.4 | V     |

| Input High Voltage                           | $V_{IH}$                         | VCC=5.0V<br>VCC=5.5V | 3.2<br>3.9 |       |     | V     |

| Input Low Voltage                            | $V_{IL}$                         |                      |            |       | 8.0 | V     |

| MTMUX[2:0]<br>Input Current, VIN-VCC or 0V   | I <sub>IL</sub> /I <sub>IH</sub> | 100k Pull-down       | -10        |       | 100 | μΑ    |

| VCC Supply Current                           | I <sub>CC</sub>                  |                      |            | 68    | 76  | mA    |

<sup>1.</sup> As unique coded gear-wheels techniques are implemented to generate unambigous positional information, the interactions between these highly wear- resistant gear wheels are subjected to mechanical wear and tear.

# **Timing Characteristics**

Timing Characteristics over Recommended Operating Range, typical at 25 °C

|                                 |                     |           |     | Value | s     |       |

|---------------------------------|---------------------|-----------|-----|-------|-------|-------|

| Parameter                       | Symbol              | Condition | Min | Тур.  | Max   | Units |

| Input Transition Rise/Fall Time | $t_R/t_F$           | 0.8V/3.0V |     |       | 500   | ns    |

| Multiplex Read Delay            | t <sub>DMUXRD</sub> |           |     |       | 64    | μs    |

| Encoder Shaft Speed             | S <sub>RPM</sub>    | Max 12000 |     |       | 12000 | rpm   |

Figure 7. Timing Characteristics of MTMUX[2:0] and MTDAT[2:0]

### **Electrical Connections**

| 1 |

|---|

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

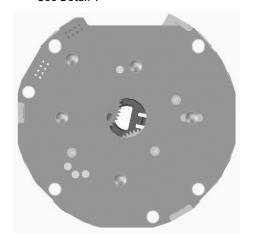

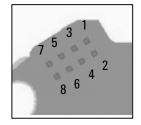

### See Detail 1

Detail 1

Figure 8. Pin Configuration

### **Application Note**

The encoder is mechanically fixed by means of holes in adapters, which accommodate M3 threads. The encoder has 2 adapters for attaching in a 3 x 120° and 4 x 90° arrangement. For details, please refer to the mechanical drawings in Figure 1.

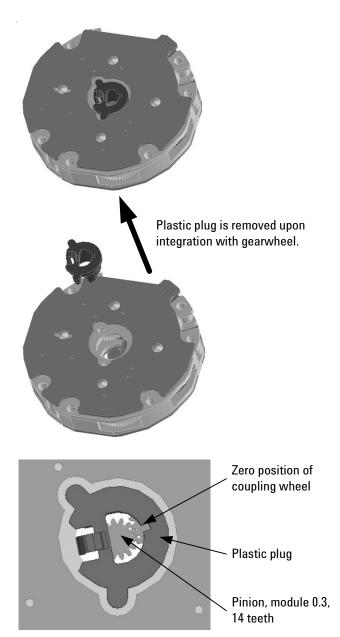

The mechanical coupling of the encoder shaft is realised by means of gear pinion with a module of 0.3, 14 teeth. The zero positions of the coupling wheels are locked with a plastic plug for alignment to the single turn absolute encoder, with the coupling wheel being able to compensate for an angle error of about +/-7°.

The electrical connection is realized by means of a 2x4 pin strip (1.27mm pitch), which is plugged into a corresponding female connector.

The encoder is attached with a plastic plug that locks the absolute zero position. During the mating of the gear pinion and the encoder coupling gear wheel it may be necessary to align the teeth of the gears for proper matching. The plastic plug can be removed upon integration with the gear wheel.

Figure 9. Mechanical coupling with Multiturn Encoder Module

# **Ordering Information**

AEAT-84AD-LBSC0 multi-turn, -40 to +125°C, solid shaft, serial, 12 bit AEAT-84AD-LBSF0 multi-turn, -40 to +125°C, solid shaft, serial, 14 bit

For ordering information of MUIC, please refer to factory.

For product information and a complete list of distributors, please go to our web site: **www.avagotech.com**

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies, Limited in the United States and other countries. Data subject to change. Copyright © 2006 Avago Technologies Pte. All rights reserved. Obsoletes 5989-1952EN AV01-0275EN - July 4, 2006