# Smart Four Channel Highside Power Switch

## for Industrial Applications

#### Features

- Overload protection

- Current limitation

- Short-circuit protection

- Thermal shutdown

- Overvoltage protection (including load dump)

- Fast demagnetization of inductive loads

- Reverse battery protection<sup>1</sup>)

- Undervoltage and overvoltage shutdown with auto-restart and hysteresis

- Open drain diagnostic output

- Open load detection in ON-state

- CMOS compatible input

- $\bullet$  Loss of ground and loss of  $V_{bb}$  protection

- Electrostatic discharge (ESD) protection

#### Application

- μC compatible power switch with diagnostic feedback for 12 V and 24 V DC grounded loads in industrial applications

- All types of resistive, inductive and capacitive loads

- Replaces electromechanical relays and discrete circuits

#### **General Description**

N channel vertical power FET with charge pump, ground referenced CMOS compatible input and diagnostic feedback, monolithically integrated in Smart SIPMOS<sup>®</sup> technology. Providing embedded protective functions.

| Pin                                | Symbol          | Function                                                                                                                                                          |

|------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,10,<br>11,12,<br>15,16,<br>19,20 | V <sub>bb</sub> | <b>Positive power supply voltage</b> . Design the wiring for the simultaneous max. short circuit currents from channel 1 to 4 and also for low thermal resistance |

| 3                                  | IN1             | Input 1 4, activates channel 1 4 in case of                                                                                                                       |

| 5                                  | IN2             | logic high signal                                                                                                                                                 |

| 7                                  | IN3             |                                                                                                                                                                   |

| 9                                  | IN4             |                                                                                                                                                                   |

| 18                                 | OUT1            | Output 1 4, protected high-side power output                                                                                                                      |

| 17                                 | OUT2            | of channel 1 4. Design the wiring for the                                                                                                                         |

| 14                                 | OUT3            | max. short circuit current                                                                                                                                        |

| 13                                 | OUT4            |                                                                                                                                                                   |

| 4                                  | ST1/2           | Diagnostic feedback 1/2 of channel 1 and<br>channel 2, open drain, low on failure                                                                                 |

| 8                                  | ST3/4           | Diagnostic feedback 3/4 of channel 3 and                                                                                                                          |

|                                    |                 | channel 4, open drain, low on failure                                                                                                                             |

| 2                                  | GND1/2          | Ground 1/2 of chip 1 (channel 1 and channel 2)                                                                                                                    |

| 6                                  | GND3/4          | Ground 3/4 of chip 2 (channel 3 and channel 4)                                                                                                                    |

Pin Definitions and Functions

#### **Product Summary**

| i i oudot oummury                      |                    |              |               |                  |

|----------------------------------------|--------------------|--------------|---------------|------------------|

| Overvoltage Protection                 | V <sub>bb(AZ</sub> | )            | 43            | V                |

| Operating voltage                      | V <sub>bb(on</sub> | ) 5.         | 0 34          | V                |

| Operating temperature                  | Ta                 | -30          | +85           | °C               |

| active channels:                       | one                | two parallel | four parallel |                  |

| On-state resistance RON                | 200                | 100          | 50            | $\text{m}\Omega$ |

| Nominal load current IL(NOM)           | 1.9                | 2.8          | 4.4           | А                |

| Current limitation I <sub>L(SCr)</sub> | 4                  | 4            | 4             | А                |

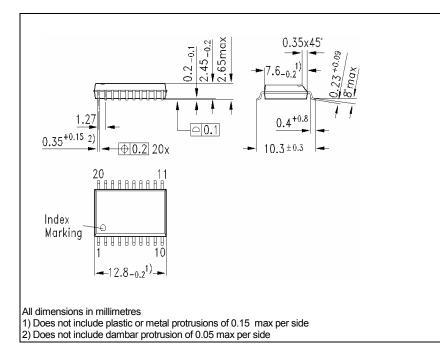

### PG-DSO-20

Pin configuration (top view)

| _               |    |   |    | _               |

|-----------------|----|---|----|-----------------|

| V <sub>bb</sub> | 1  | • | 20 | V <sub>bb</sub> |

| GND1/2          | 2  |   | 19 | V <sub>bb</sub> |

| IN1             | 3  |   | 18 | OŨT1            |

| ST1/2           | 4  |   | 17 | OUT2            |

| IN2             | 5  |   | 16 | V <sub>bb</sub> |

| GND3/4          | 6  |   | 15 | V <sub>bb</sub> |

| IN3             | 7  |   | 14 | OUT3            |

| ST3/4           | 8  |   | 13 | OUT4            |

| IN4             | 9  |   | 12 | V <sub>bb</sub> |

| V <sub>bb</sub> | 10 |   | 11 | V <sub>bb</sub> |

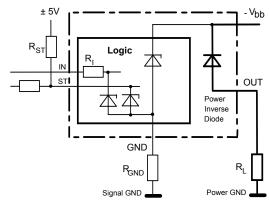

<sup>&</sup>lt;sup>1)</sup> With external current limit (e.g. resistor  $R_{GND}$ =150  $\Omega$ ) in GND connection, resistor in series with ST connection, reverse load current limited by connected load.

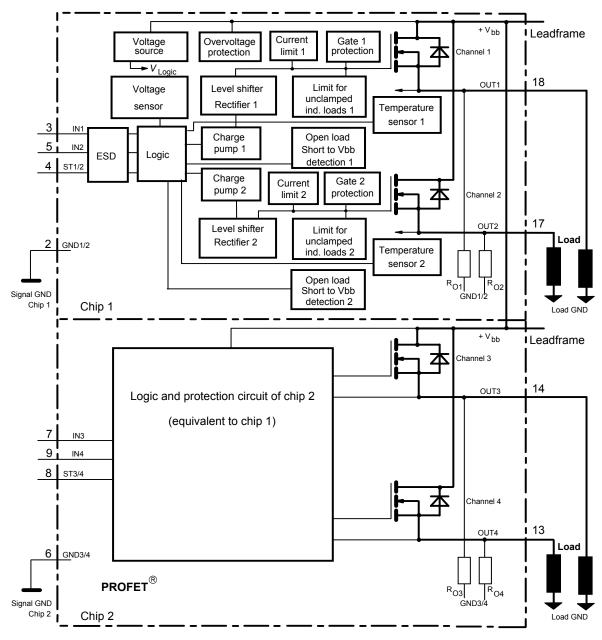

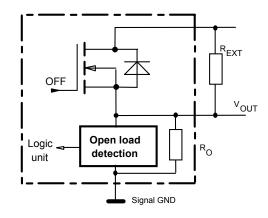

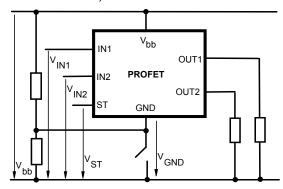

### **Block diagram**

Four Channels; Open Load detection in on state;

Leadframe connected to pin 1, 10, 11, 12, 15, 16, 19, 20

#### **Maximum Ratings** at $T_i = 25^{\circ}$ C unless otherwise specified

| Parameter                                                                                                                                                                            |                                                                                              | Symbol                           | Values       | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------|--------------|------|

|                                                                                                                                                                                      |                                                                                              | -                                | 40           |      |

| Supply voltage (overvoltage prot                                                                                                                                                     |                                                                                              | V <sub>bb</sub>                  | 43           | V    |

| Supply voltage for full short circu $T_{j,start} = -40 \dots + 150^{\circ}C$                                                                                                         | lit protection                                                                               | V <sub>bb</sub>                  | 34           | V    |

| Load current (Short-circuit curre                                                                                                                                                    |                                                                                              | ΙL                               | self-limited | A    |

| Load dump protection <sup>2)</sup> $V_{\text{LoadDum}}$<br>$R_{\text{I}^{(3)}} = 2 \Omega$ , $t_{\text{d}} = 200 \text{ ms}$ ; IN = low<br>each channel loaded with $R_{\text{L}} =$ | $_{\rm p} = U_{\rm A} + V_{\rm S}, U_{\rm A} = 13.5 \text{ V}$<br>or high,<br>7.1 $\Omega$ , | $V_{\sf Load} \ {\sf dump}^{4)}$ | 60           | V    |

| Junction temperature                                                                                                                                                                 |                                                                                              | Tj                               | +150         | С°   |

| Operating temperature range                                                                                                                                                          |                                                                                              | Ta                               | -30 +85      |      |

| Storage temperature range                                                                                                                                                            |                                                                                              | $T_{stg}$                        | -40 +105     |      |

| Power dissipation (DC) <sup>5</sup>                                                                                                                                                  | <i>T</i> <sub>a</sub> = 25°C:                                                                | P <sub>tot</sub>                 | 3.6          | W    |

| (all channels active)                                                                                                                                                                | <i>T</i> <sub>a</sub> = 85°C:                                                                |                                  | 1.9          |      |

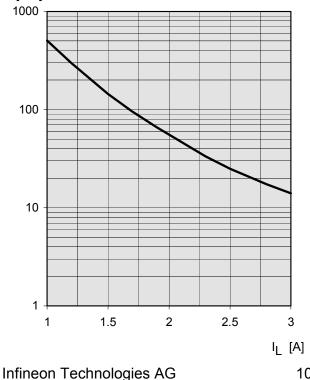

| Inductive load switch-off energy $V_{bb} = 12V$ , $T_{j,start} = 150^{\circ}C^{5}$ ,                                                                                                 | dissipation, single pulse                                                                    |                                  |              |      |

| $I_{\rm L}$ = 1.9 A, Z_{\rm L} = 66 mH, 0 $\Omega$                                                                                                                                   | one channel:                                                                                 | E <sub>AS</sub>                  | 150          | mJ   |

| $I_{\rm L}$ = 2.8 A, $Z_{\rm L}$ = 66 mH, 0 $\Omega$                                                                                                                                 | two parallel channels:                                                                       |                                  | 320          |      |

| $I_{\rm L}$ = 4.4 A, Z <sub>L</sub> = 66 mH, 0 $\Omega$                                                                                                                              | four parallel channels:                                                                      |                                  | 800          |      |

| see diagrams on page 9 and page 10                                                                                                                                                   |                                                                                              |                                  |              |      |

| Electrostatic discharge capability (Human Body Model)                                                                                                                                | (ESD)                                                                                        | V <sub>ESD</sub>                 | 1.0          | kV   |

| Input voltage (DC)                                                                                                                                                                   |                                                                                              | V <sub>IN</sub>                  | -10 +16      | V    |

| Current through input pin (DC)                                                                                                                                                       |                                                                                              | I <sub>IN</sub>                  | ±2.0         | mA   |

| Current through status pin (DC)                                                                                                                                                      |                                                                                              | I <sub>ST</sub>                  | ±5.0         |      |

| see internal circuit diagram page 8                                                                                                                                                  |                                                                                              |                                  |              |      |

| Thermal resistance                                                                                                                                                                   |                                                                                              |                                  |              |      |

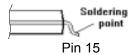

| junction - soldering point <sup>5),6)</sup>                                                                                                                                          | each channel:                                                                                | <b>R</b> <sub>thjs</sub>         | 16           | K/W  |

| junction - ambient <sup>5)</sup>                                                                                                                                                     | one channel active:                                                                          | <b>R</b> <sub>thja</sub>         | 44           |      |

|                                                                                                                                                                                      | all channels active:                                                                         |                                  | 35           |      |

<sup>&</sup>lt;sup>2)</sup> Supply voltages higher than  $V_{bb(AZ)}$  require an external current limit for the GND and status pins, e.g. with a 150  $\Omega$  resistor in the GND connection and a 15 k $\Omega$  resistor in series with the status pin. A resistor for input protection is integrated.

<sup>&</sup>lt;sup>3)</sup>  $R_{\rm I}$  = internal resistance of the load dump test pulse generator

<sup>&</sup>lt;sup>4)</sup> V<sub>Load dump</sub> is setup without the DUT connected to the generator per ISO 7637-1 and DIN 40839

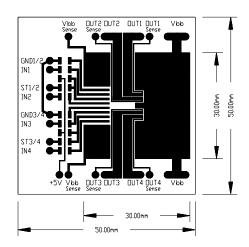

<sup>&</sup>lt;sup>5)</sup> Device on 50mm\*50mm\*1.5mm epoxy PCB FR4 with 6cm<sup>2</sup> (one layer, 70μm thick) copper area for V<sub>bb</sub> connection. PCB is vertical without blown air. See page 15

<sup>&</sup>lt;sup>6)</sup> Soldering point: upper side of solder edge of device pin 15. See page 15

## **Electrical Characteristics**

| Parameter and Conditions, each of the four channels                   | Symbol |     | Values |     | Unit |

|-----------------------------------------------------------------------|--------|-----|--------|-----|------|

| at T <sub>j</sub> = 25 °C, $V_{bb}$ = 12 V unless otherwise specified |        | min | typ    | max |      |

#### Load Switching Capabilities and Characteristics

| U I                                                            |                                   |                              |     |     |     |      |

|----------------------------------------------------------------|-----------------------------------|------------------------------|-----|-----|-----|------|

| On-state resistance (Vbb to OU                                 | Г)                                |                              |     |     |     |      |

| I <sub>L</sub> = 1.8 A each cha                                | nnel, $T_j = 25^{\circ}C$ :       | R <sub>ON</sub>              |     | 165 | 200 | mΩ   |

|                                                                | <i>T</i> <sub>j</sub> = 150°C:    |                              |     | 320 | 400 |      |

|                                                                |                                   |                              |     |     |     |      |

| two parallel cha                                               | annels, $T_j = 25^{\circ}C$ :     |                              |     | 83  | 100 |      |

| four parallel cha                                              | nnels, $T_j = 25^{\circ}C$ :      |                              |     | 42  | 50  |      |

| Nominal load current o                                         | ne channel active:                | I <sub>L(NOM)</sub>          | 1.7 | 1.9 |     | Α    |

| two parall                                                     | el channels active:               |                              | 2.6 | 2.8 |     |      |

| four parall                                                    | el channels active:               |                              | 4.1 | 4.4 |     |      |

| Device on PCB <sup>5)</sup> , $T_a = 85^{\circ}C$ , 7          | j ≤ 150°C                         |                              |     |     |     |      |

| Output current while GND discor                                | nnected or pulled                 | I <sub>L(GNDhigh)</sub>      |     |     | 10  | mA   |

| up; $V_{bb} = 30 \text{ V}, V_{IN} = 0$ , see dia              | agram page 9                      |                              |     |     |     |      |

| Turn-on time                                                   | to 90% V <sub>OUT</sub> :         | t <sub>on</sub>              | 80  | 200 | 400 | μs   |

| Turn-off time                                                  | to 10% V <sub>OUT</sub> :         | t <sub>off</sub>             | 80  | 200 | 400 |      |

| <i>R</i> <sub>L</sub> = 12 Ω, <i>T</i> <sub>j</sub> =-40+150°C |                                   |                              |     |     |     |      |

| Slew rate on                                                   |                                   | d <i>V</i> /dt <sub>on</sub> | 0.1 |     | 1   | V/µs |

| 10 to 30% $V_{OUT}$ , $R_{L}$ = 12 $\Omega$ ,                  | <i>T</i> <sub>j</sub> =-40+150°C: |                              |     |     |     |      |

| Slew rate off                                                  |                                   | -dV/dt <sub>off</sub>        | 0.1 |     | 1   | V/μs |

| 70 to 40% $V_{OUT}$ , $R_{L}$ = 12 $\Omega$ ,                  | <i>T</i> <sub>j</sub> =-40+150°C: |                              |     |     |     |      |

#### **Operating Parameters**

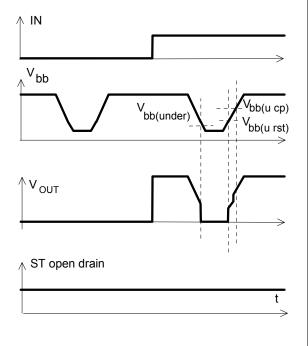

| Operating voltage <sup>7)</sup>                                                   | <i>T</i> <sub>j</sub> =-40+150°C:         | V <sub>bb(on)</sub>       | 5.0 |     | 34  | V |

|-----------------------------------------------------------------------------------|-------------------------------------------|---------------------------|-----|-----|-----|---|

| Undervoltage shutdown                                                             | <i>T</i> <sub>j</sub> =-40+150°C:         | V <sub>bb(under)</sub>    | 3.5 |     | 5.0 | V |

| Undervoltage restart                                                              | <i>T</i> <sub>j</sub> =-40+25°C:          | V <sub>bb(u rst)</sub>    |     |     | 5.0 | V |

|                                                                                   | <i>T</i> <sub>j</sub> =+150°C:            |                           |     |     | 7.0 |   |

| Undervoltage restart of charge p<br>see diagram page 14                           | oump<br><i>T</i> <sub>j</sub> =-40+150°C: | V <sub>bb(ucp)</sub>      |     | 5.6 | 7.0 | V |

| Undervoltage hysteresis<br>$\Delta V_{bb(under)} = V_{bb(u rst)} - V_{bb(under)}$ |                                           | $\Delta V_{bb(under)}$    |     | 0.2 |     | V |

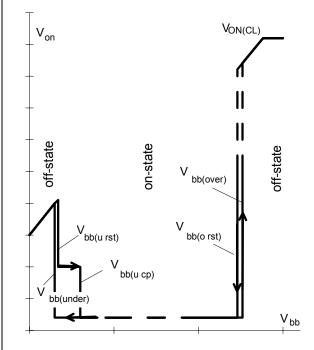

| Overvoltage shutdown                                                              | <i>T</i> <sub>j</sub> =-40+150°C:         | V <sub>bb(over)</sub>     | 34  |     | 43  | V |

| Overvoltage restart                                                               | <i>T</i> <sub>j</sub> =-40+150°C:         | V <sub>bb(o rst)</sub>    | 33  |     |     | V |

| Overvoltage hysteresis                                                            | <i>T</i> <sub>j</sub> =-40+150°C:         | $\Delta V_{\rm bb(over)}$ |     | 0.5 |     | V |

| Overvoltage protection <sup>8)</sup>                                              | <i>T</i> <sub>j</sub> =-40+150°C:         | V <sub>bb(AZ)</sub>       | 42  | 47  |     | V |

| / <sub>bb</sub> = 40 mA                                                           |                                           |                           |     |     |     |   |

<sup>7)</sup> At supply voltage increase up to  $V_{bb}$  = 5.6 V typ without charge pump,  $V_{OUT} \approx V_{bb}$  - 2 V

<sup>&</sup>lt;sup>8)</sup> see also  $V_{ON(CL)}$  in circuit diagram on page 8.

| Parameter and Conditions, each of the                                     | ne four channels                        | Symbol               | Values    |           |         | Unit |

|---------------------------------------------------------------------------|-----------------------------------------|----------------------|-----------|-----------|---------|------|

| at T <sub>j</sub> = 25 °C, $V_{bb}$ = 12 V unless otherwise sp            | pecified                                |                      | min       | typ       | max     |      |

| Standby current, all channels off                                         | <i>T</i> <sub>i</sub> =25°C:            | I <sub>bb(off)</sub> |           | 28        | 60      | μA   |

| $V_{IN} = 0$                                                              | <i>T</i> <sub>i</sub> =150°C:           | 55(01)               |           | 44        | 70      |      |

| Leakage output current (included in $I_t$<br>$V_{IN} = 0$                 | bb(off))                                | I <sub>L(off)</sub>  |           |           | 12      | μA   |

| 0.12                                                                      | +150°C<br>e channel on:<br>channels on: | I <sub>GND</sub>     |           | 2<br>8    | 3<br>12 | mA   |

| Protection Functions <sup>10)</sup>                                       |                                         |                      |           |           |         |      |

| Initial peak short circuit current limit, diagrams, page 12)              | (see timing                             |                      |           |           |         |      |

| each channe                                                               | el, $T_{j} = -40^{\circ}C$ :            | I <sub>L(SCp)</sub>  | 5.5       | 9.5       | 13      | Α    |

|                                                                           | <i>T</i> j =25°C∶                       |                      | 4.5       | 7.5       | 11      |      |

|                                                                           | <i>T</i> j =+150°C:                     |                      | 2.5       | 4.5       | 7       |      |

| two para                                                                  | allel channels                          | twice                | the curre | nt of one | channel |      |

| four par                                                                  | allel channels                          | four times           | the curre | nt of one | channel |      |

| Repetitive short circuit current limit,                                   |                                         |                      |           |           |         |      |

| $T_{\rm j} = T_{\rm jt}$                                                  | each channel                            | I <sub>L(SCr)</sub>  |           | 4         |         | Α    |

| two para                                                                  | allel channels                          |                      |           | 4         |         |      |

| four par                                                                  | allel channels                          |                      |           | 4         |         |      |

| (see timing diagrams, page 12)                                            |                                         |                      |           |           |         |      |

| Initial short circuit shutdown time                                       | T <sub>j,start</sub> =-40°C:            | t <sub>off(SC)</sub> |           | 5.5       |         | ms   |

|                                                                           | T <sub>j,start</sub> = 25°C:            |                      |           | 4         |         |      |

| (see page 11 and timing diagrams on page                                  | e 12)                                   |                      |           |           |         |      |

| Output clamp (inductive load switch of at $V_{ON(CL)} = V_{bb} - V_{OUT}$ | off) <sup>11)</sup>                     | V <sub>ON(CL)</sub>  |           | 47        |         | V    |

| Thermal overload trip temperature                                         |                                         | T <sub>jt</sub>      | 150       |           |         | °C   |

| Thermal hysteresis                                                        |                                         | $\Delta T_{jt}$      |           | 10        |         | K    |

| Reverse Battery                                                           |                                         |                      |           |           |         |      |

| Reverse battery voltage <sup>12</sup> )                                   |                                         | -V <sub>bb</sub>     |           |           | 32      | V    |

| Drain-source diode voltage (Vout > Vbb                                    | )                                       | -V <sub>ON</sub>     |           | 610       |         | mV   |

<sup>9)</sup> Add  $I_{ST}$ , if  $I_{ST} > 0$

$I_{\rm L} = -1.9 \, \text{A}, T_{\rm j} = +150^{\circ} \text{C}$

<sup>12)</sup> Requires a 150 Ω resistor in GND connection. The reverse load current through the intrinsic drain-source diode has to be limited by the connected load. Note that the power dissipation is higher compared to normal operating conditions due to the voltage drop across the intrinsic drain-source diode. The temperature protection is not active during reverse current operation! Input and Status currents have to be limited (see max. ratings page 3 and circuit page 8).

<sup>&</sup>lt;sup>10)</sup> Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

<sup>&</sup>lt;sup>11)</sup> If channels are connected in parallel, output clamp is usually accomplished by the channel with the lowest V<sub>ON(CL)</sub>

| Parameter and Conditions, eac                                                                             | h of the four channels                                | Symbol                 |           | Values    |         | Unit |

|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------|-----------|-----------|---------|------|

| at T <sub>j</sub> = 25 °C, $V_{bb}$ = 12 V unless otherw                                                  | vise specified                                        |                        | min       | typ       | max     |      |

| Diagnostic Characteristics                                                                                |                                                       |                        |           |           |         |      |

| Open load detection current, (on-                                                                         | -condition)                                           |                        |           |           |         |      |

| each ch                                                                                                   | annel, $T_{i}$ = -40°C:                               | I <sub>L (OL)</sub>    | 10        |           | 200     | mA   |

|                                                                                                           | $T_{\rm j} = 25^{\circ}\rm C$ :                       |                        | 10        |           | 150     |      |

|                                                                                                           | <i>T</i> <sub>j</sub> = 150°C:                        |                        | 10        |           | 150     |      |

| two                                                                                                       | parallel channels                                     | twice                  | the curre | nt of one | channel |      |

|                                                                                                           | r parallel channels                                   | four times             | the curre | nt of one | channel |      |

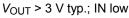

| Open load detection voltage <sup>13</sup> )                                                               | <i>T</i> <sub>i</sub> =-40+150°C:                     | V <sub>OUT(OL)</sub>   | 2         | 3         | 4       | V    |

| Internal output pull down                                                                                 | ,                                                     | (- /                   |           |           |         |      |

| (OUT to GND), $V_{OUT} = 5 V$                                                                             | <i>T</i> <sub>j</sub> =-40+150°C:                     | Ro                     | 4         | 10        | 30      | kΩ   |

| Input and Status Feedback <sup>14)</sup>                                                                  |                                                       |                        |           |           |         |      |

| Input resistance                                                                                          |                                                       | R                      | 2.5       | 3.5       | 6       | kΩ   |

| (see circuit page 8)                                                                                      | <i>T</i> <sub>j</sub> =-40+150°C:                     |                        |           |           |         |      |

| Input turn-on threshold voltage                                                                           |                                                       | V <sub>IN(T+)</sub>    | 1.7       |           | 3.5     | V    |

| Input turn-off threshold voltage                                                                          | <i>T</i> <sub>j</sub> =-40+150°C:                     | V <sub>IN(T-)</sub>    | 1.5       |           |         | V    |

| Input threshold hysteresis                                                                                | -                                                     | $\Delta V_{\rm IN(T)}$ |           | 0.5       |         | V    |

| Off state input current $T_i = -40+150^{\circ}C$ :                                                        | V <sub>IN</sub> = 0.4 V:                              | I <sub>IN(off)</sub>   | 1         |           | 50      | μA   |

| On state input current $T_i = -40+150^{\circ}C$ :                                                         | V <sub>IN</sub> = 5 V:                                | I <sub>IN(on)</sub>    | 20        | 50        | 90      | μA   |

| Delay time for status with open lo<br>off (other channel in off state)<br>(see timing diagrams, page 13), | oad after switch<br><i>T</i> <sub>j</sub> =-40+150°C: | t <sub>d(ST OL4)</sub> | 100       | 320       | 800     | μs   |

| Delay time for status with open lo<br>off (other channel in on state)<br>(see timing diagrams, page 13),  | oad after switch<br>$T_j = -40+150^{\circ}C$ :        | t <sub>d(ST OL5)</sub> |           | 5         | 20      | μs   |

| Status invalid after positive input (open load)                                                           | : slope<br><i>T</i> <sub>j</sub> =-40+150°C:          | $t_{d(ST)}$            |           | 200       | 600     | μs   |

| Status output (open drain)                                                                                |                                                       |                        |           |           |         |      |

| Zener limit voltage $T_j = -40+150$                                                                       | °C, <i>I</i> <sub>ST</sub> = +1.6 mA:                 | $V_{\rm ST(high)}$     | 5.4       | 6.1       |         | V    |

| - 2                                                                                                       | 6°C, <i>I</i> <sub>ST</sub> = +1.6 mA:                | V <sub>ST(low)</sub>   |           |           | 0.4     |      |

|                                                                                                           | °C, <i>I</i> <sub>ST</sub> = +1.6 mA:                 |                        |           |           | 0.6     |      |

<sup>&</sup>lt;sup>13)</sup> External pull up resistor required for open load detection in off state.

<sup>&</sup>lt;sup>14)</sup> If ground resistors  $R_{GND}$  are used, add the voltage drop across these resistors.

#### Truth Table

| Channel 1 and 2                  | Chip 1        | IN1 | IN2 | OUT1 | OUT2 | ST1/2                |

|----------------------------------|---------------|-----|-----|------|------|----------------------|

| Channel 3 and 4                  | Chip 2        | IN3 | IN4 | OUT3 | OUT4 | ST3/4                |

| (equivalent to channel 1 and 2)  |               |     |     |      |      |                      |

|                                  |               |     |     |      |      | BTS 711L1            |

| Normal operation                 |               | L   | L   | L    | L    | Н                    |

|                                  |               | L   | н   | L    | н    | н                    |

|                                  |               | н   | L   | Н    | L    | н                    |

|                                  |               | Н   | н   | Н    | Н    | Н                    |

| Open load                        | Channel 1 (3) | L   | L   | Z    | L    | H(L <sup>15)</sup> ) |

|                                  |               | L   | н   | Z    | н    | Н                    |

|                                  |               | н   | Х   | Н    | Х    | L                    |

|                                  | Channel 2 (4) | L   | L   | L    | Z    | H(L <sup>15)</sup> ) |

|                                  |               | н   | L   | н    | Z    | н                    |

|                                  |               | X   | Н   | Х    | н    | L                    |

| Short circuit to V <sub>bb</sub> | Channel 1 (3) | L   | L   | н    | L    | L <sup>16)</sup>     |

|                                  |               | L   | н   | Н    | Н    | н                    |

|                                  |               | н   | Х   | н    | Х    | H(L <sup>17)</sup> ) |

|                                  | Channel 2 (4) | L   | L   | L    | Н    | L <sup>16)</sup>     |

|                                  |               | н   | L   | н    | н    | н                    |

|                                  |               | Х   | н   | Х    | Н    | H(L <sup>17)</sup> ) |

| Overtemperature                  | both channel  | L   | L   | L    | L    | н                    |

|                                  |               | Х   | н   | L    | L    | L                    |

|                                  |               | Н   | X   | L    | L    | L                    |

|                                  | Channel 1 (3) | L   | Х   | L    | Х    | Н                    |

|                                  |               | Н   | X   | L    | Х    | L                    |

|                                  | Channel 2 (4) | Х   | L   | Х    | L    | Н                    |

|                                  |               | X   | н   | Х    | L    | L                    |

| Undervoltage/ Overvoltage        |               | Х   | Х   | L    | L    | н                    |

H = "High" Level Status signal valid after the time delay shown in the timing diagrams

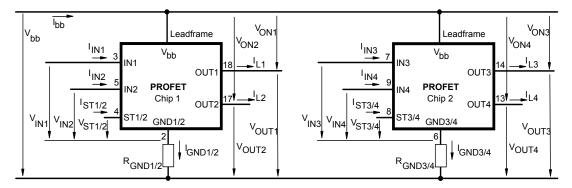

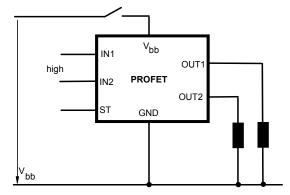

Parallel switching of channel 1 and 2 (also channel 3 and 4) is easily possible by connecting the inputs and outputs in parallel (see truth table). If switching channel 1 to 4 in parallel, the status outputs ST1/2 and ST3/4 have to be configured as a 'Wired OR' function with a single pull-up resistor.

#### Terms

Leadframe (V<sub>bb</sub>) is connected to pin 1,10,11,12,15,16,19,20 External R<sub>GND</sub> optional; two resistors R<sub>GND1/2</sub>, R<sub>GND3/4</sub> = 150  $\Omega$  or a single resistor R<sub>GND</sub> = 75  $\Omega$  for reverse battery protection up to the max. operating voltage.

<sup>17)</sup> Low resistance to  $V_{bb}$  may be detected by no-load-detection

<sup>&</sup>lt;sup>15)</sup> With additional external pull up resistor

<sup>&</sup>lt;sup>16)</sup> An external short of output to  $V_{bb}$  in the off state causes an internal current from output to ground. If  $R_{GND}$  is used, an offset voltage at the GND and ST pins will occur and the  $V_{ST low}$  signal may be errorious.

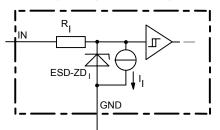

#### Input circuit (ESD protection), IN1...4

ESD zener diodes are not to be used as voltage clamp at DC conditions. Operation in this mode may result in a drift of the zener voltage (increase of up to 1 V).

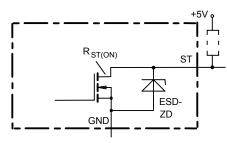

#### Status output, ST1/2 or ST3/4

ESD-Zener diode: 6.1 V typ., max 5.0 mA;  $R_{ST(ON)} < 380 \ \Omega$  at 1.6 mA, ESD zener diodes are not to be used as voltage clamp at DC conditions. Operation in this mode may result in a drift of the zener voltage (increase of up to 1 V).

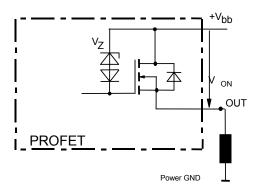

# Inductive and overvoltage output clamp, OUT1...4

VON clamped to VON(CL) = 47 V typ.

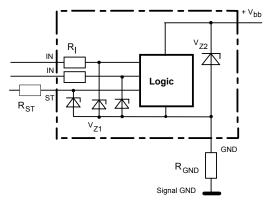

# Overvoltage protection of logic part GND1/2 or GND3/4

$V_{Z1}$  = 6.1 V typ.,  $V_{Z2}$  = 47 V typ.,  $R_I$  = 3.5 k $\Omega$  typ.,  $R_{GND}$  = 150  $\Omega$

#### **Reverse battery protection**

Temperature protection is not active during inverse current operation.

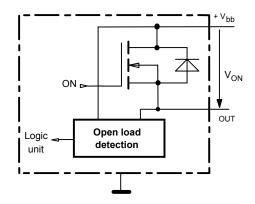

#### Open-load detection, OUT1...4

ON-state diagnostic condition:

$V_{ON} < R_{ON} \cdot I_{L(OL)}$ ; IN high

OFF-state diagnostic condition:

### GND disconnect

(channel 1/2 or 3/4)

Any kind of load. In case of IN = high is  $V_{OUT} \approx V_{IN} - V_{IN(T+)}$ . Due to  $V_{GND} > 0$ , no  $V_{ST}$  = low signal available.

#### GND disconnect with GND pull up

(channel 1/2 or 3/4)

Any kind of load. If  $V_{GND} > V_{IN} - V_{IN}(T+)$  device stays off Due to  $V_{GND} > 0$ , no  $V_{ST} =$  low signal available.

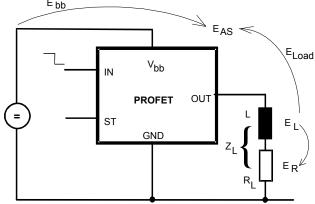

# $V_{\mbox{\scriptsize bb}}$ disconnect with energized inductive load

For an inductive load current up to the limit defined by  ${\sf E}_{AS}$  (max. ratings see page 3 and diagram on page 10) each switch is protected against loss of  ${\sf V}_{bb}.$

Consider at your PCB layout that in the case of Vbb disconnection with energized inductive load the whole load current flows through the GND connection.

Inductive load switch-off energy dissipation E bb

Energy stored in load inductance:

$$E_{\rm L} = \frac{1}{2} \cdot {\rm L} \cdot {\rm I}_{\rm L}^2$$

While demagnetizing load inductance, the energy dissipated in PROFET is

$E_{AS} = E_{bb} + E_L - E_R = \int V_{ON(CL)} \cdot i_L(t) dt$

with an approximate solution for  $R_{I} > 0 \Omega$ :

$$E_{\text{AS}} = \frac{I_{\text{L}} \cdot L}{2 \cdot R_{\text{L}}} (V_{\text{bb}} + |V_{\text{OUT}(\text{CL})}|) ln (1 + \frac{I_{\text{L}} \cdot R_{\text{L}}}{|V_{\text{OUT}(\text{CL})}|})$$

#### Maximum allowable load inductance for a single switch off (one channel)<sup>5)</sup>

$L = f(\bar{I_L})$ ; T<sub>j,start</sub> = 150°C, V<sub>bb</sub> = 12 V, R<sub>L</sub> = 0  $\Omega$

L [mH]

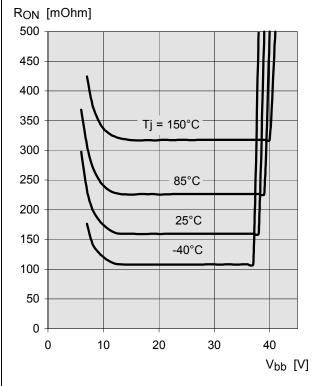

## Typ. on-state resistance

$R_{ON} = f(V_{bb}, T_i); I_{L} = 1.8 \text{ A}, IN = high$

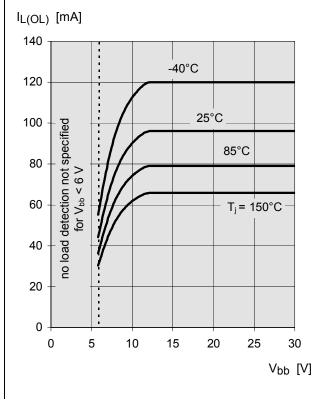

## Typ. open load detection current

$I_{L(OL)} = f(V_{bb}, T_i);$  IN = high

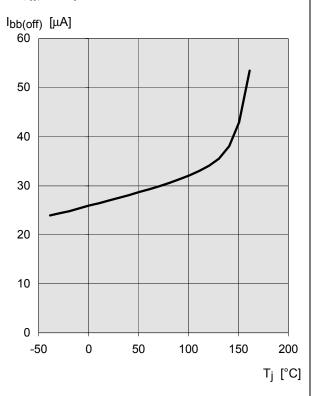

#### Typ. standby current

$I_{bb(off)} = f(T_j); V_{bb} = 9...34 \text{ V}, \text{IN1...4} = \text{Iow}$

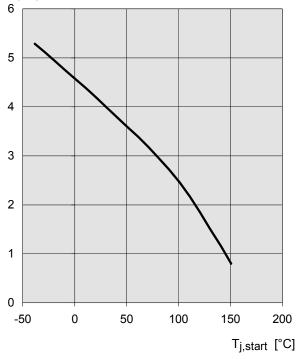

## Typ. initial short circuit shutdown time

$t_{off(SC)} = f(T_{j,start}); V_{bb} = 12 V$

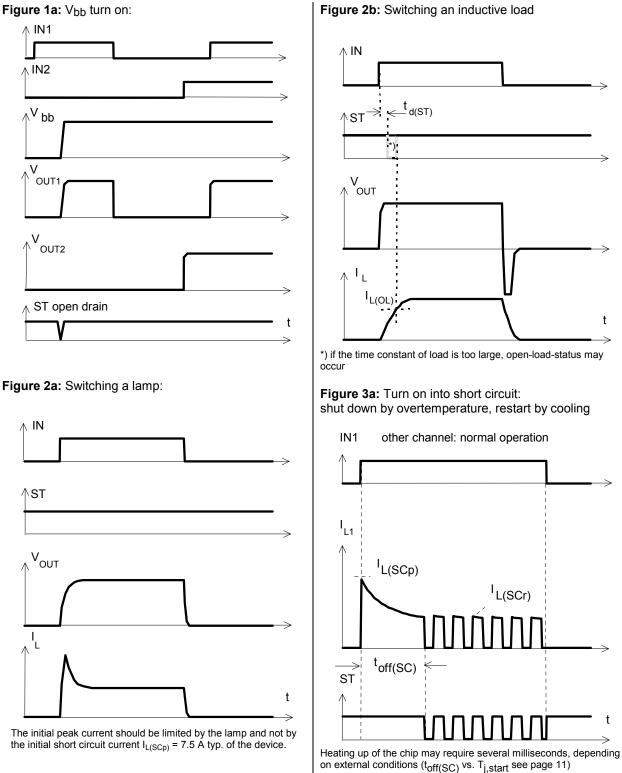

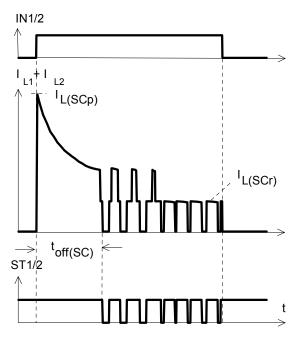

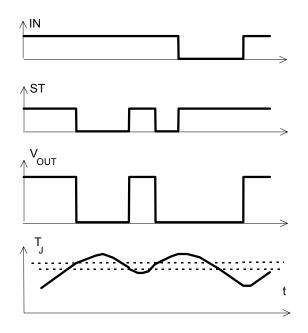

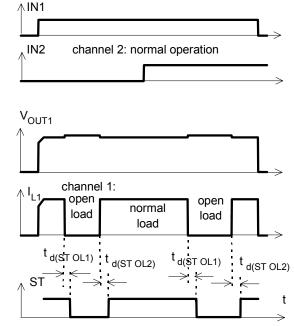

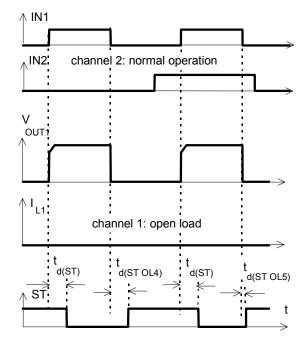

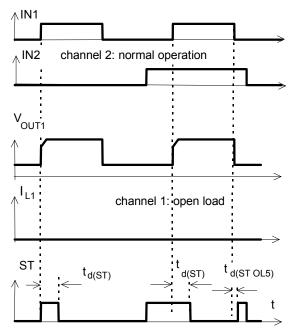

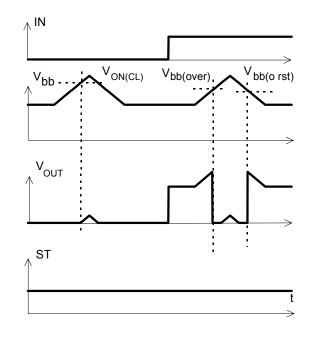

## **Timing diagrams**

Timing diagrams are shown for chip 1 (channel 1/2). For chip 2 (channel 3/4) the diagrams are valid too. The channels 1 and 2, respectively 3 and 4, are symmetric and consequently the diagrams are valid for each channel as well as for permuted channels

**Figure 3b:** Turn on into short circuit: shut down by overtemperature, restart by cooling (two parallel switched channels 1 and 2)

#### Figure 4a: Overtemperature: Reset if $T_j < T_{jt}$

Figure 5a: Open load: detection in ON-state, open load occurs in on-state

$t_{d(ST OL1)}$  = 30 µs typ.,  $t_{d(ST OL2)}$  = 20 µs typ

Figure 5b: Open load: detection in ON-state, turn on/off to open load

The status delay time td(STOL4) allows to distinguish between the failure modes "open load in ON-state" and "overtemperature".

Figure 5c: Open load: detection in ON- and OFF-state (with  $R_{EXT}$ ), turn on/off to open load

$t_{d(\text{ST OL5})}$  depends on external circuitry because of high impedance

Figure 6b: Undervoltage restart of charge pump

IN = high, normal load conditions. Charge pump starts at  $V_{bb(ucp)}$  = 5.6V typ.

#### Figure 6a: Undervoltage:

#### Figure 7a: Overvoltage:

# Package and Ordering Code

Standard PG-DSO-20-9 Ordering Code

ITS711L1 SP000219532

Definition of soldering point with temperature  $T_s$ : upper side of solder edge of device pin 15.

Printed circuit board (FR4, 1.5mm thick, one layer 70 $\mu$ m, 6cm<sup>2</sup> active heatsink area) as a reference for max. power dissipation P<sub>tot</sub>, nominal load current I<sub>L(NOM)</sub> and thermal resistance R<sub>thia</sub>

#### Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81669 München © Infineon Technologies AG 2006 All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.