# all austriamicrosystems

### AS5046

# PROGRAMMABLE 12-bit 360° MAGNETIC ANGLE ENCODER WITH ABSOLUTE 2-WIRE SERIAL AND ANALOG INTERFACES

#### PRELIMINARY DATA SHEET

# 1 General Description

The AS5046 is a contactless magnetic angle encoder for accurate measurement up to 360°.

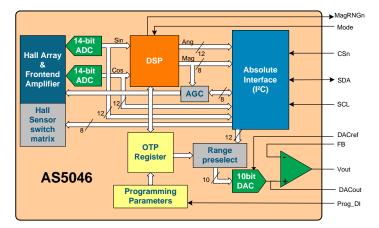

It is a system-on-chip, combining integrated Hall elements, analog front end and digital signal processing in a single device.

The AS5046 provides a digital serial 12-bit as well as a programmable 10-bit ratiometric analog output that is directly proportional to the angle of a magnet, rotating over the chip.

In addition, the serial interface enables a user configurable arrangement of the Hall array and allows access to each individual Sensor of the Hall Array.

The AS5046 also provides high resolution information of the magnetic field strength, respectively the vertical distance of the magnet, thus adding excellent state-ofhealth information of the overall system.

An internal voltage regulator allows operation of the AS5046 from 3.3V or 5.0V supplies.

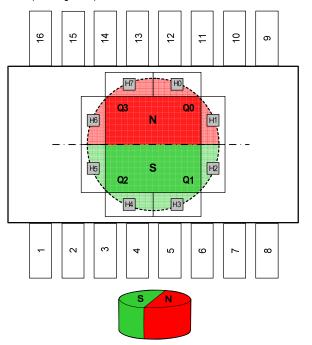

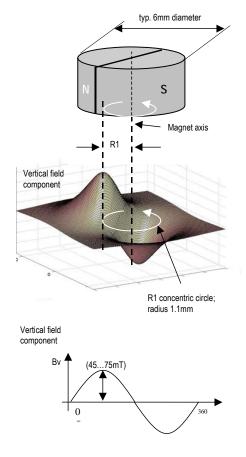

Figure 1: Typical arrangement of AS5046 and magnet

# Benefits

- Complete system-on-chip

- High reliability due to non-contact sensing

- Bi-directional 2-wire interface

- Programmable ratiometric analog output

- Ideal for application s in harsh environments

- Robust system, tolerant to magnet misalignment, airgap variations, temperature variations and external magnetic fields

- No calibration required

# 2 Key Features

- 360° contactless high resolution angular position encoding

- User programmable zero position

- 12-bit 2-wire serial interface

- Versatile analog output programmable angular range up to 360° programmable ratiometric output voltage range

- High resolution magnet distance indication

256 steps within recommended range (~0.5 to 1.8mm)

256 steps over extended range (~0 to 5mm)

- Mode input for optimizing noise vs. speed

- Alignment mode for magnet placement guidance

- Wide temperature range: 40°C to + 125°C

- Small package: SSOP 16 (5.3mm x 6.2mm)

# 3 Applications

The AS5046 is ideal for applications that require high resolution, a minimum of wires between controller and sensor and where the vertical distance of the magnet is of importance:

- Remote sensors

- Rotate-and-push manual input devices

- Joysticks

- Applications with extended safety requirements regarding magnet distance

Figure 2: AS5046 block diagram

# 4 Pin Configuration

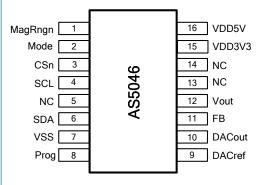

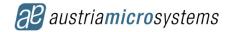

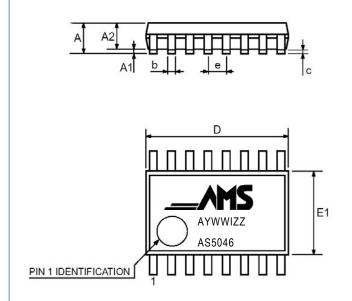

Figure 3: AS5046 pin configuration SSOP16

Package = SSOP16 (16 lead Shrink Small Outline Package)

| Pin | Symbol  | Туре         | Description                                                                                                                                               |

|-----|---------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | MagRngn | DO_OD        | Magnet Field Magnitude RaNGe warning;<br>active low, indicates that the magnetic<br>field strength is outside of the<br>recommended limits.               |

| 2   | Mode    | DI_PD,<br>ST | Mode input. Select between low noise<br>(open, low) and high speed (high) mode.<br>Internal pull-down resistor                                            |

| 3   | CSn     | DI_PU,<br>ST | Chip Select, active low; Schmitt-Trigger input, internal pull-up resistor ( $\sim$ 50k $\Omega$ ). Must be connected to VSS for serial data transmission. |

| 4   | SCL     | DI,ST        | Serial Clock Line.Clock input for 2-wire serial data transmission                                                                                         |

| 5   | NC      | -            | must be left unconnected                                                                                                                                  |

| 6   | SDA     | DIO          | Serial Data Line. Bi-directional I/O for 2-<br>wire serial data transmission                                                                              |

| 7   | VSS     | S            | Negative Supply Voltage (GND)                                                                                                                             |

| 8   | Prog    | DI_PD        | OTP Programming Input.<br>Internal pull-down resistor (~74kΩ).<br>Should be connected to VSS if<br>programming is not used                                |

| 9   | DACref  | AI           | DAC Reference voltage input for external reference                                                                                                        |

| 10  | DACout  | AO           | DAC output (unbuffered, Ri ~8k $\Omega$ )                                                                                                                 |

| 11  | FB      | AI           | Feedback, OPAMP inverting input                                                                                                                           |

| 12  | Vout    | AO           | OPAMP output                                                                                                                                              |

| 13  | NC      | -            | Must be left unconnected                                                                                                                                  |

| 14  | NC      | -            | Must be left unconnected                                                                                                                                  |

| 15  | VDD3V3  | S            | 3V-Regulator Output for internal core,<br>regulated from VDD5V.Connect to<br>VDD5V for 3V supply voltage. Do not<br>load externally.                      |

| 16  | VDD5V   | S            | Positive Supply Voltage, 3.0 to 5.5 V                                                                                                                     |

Table 1: Pin description SSOP16

| DO_OD | digital output open drain | S    | supply pin                |

|-------|---------------------------|------|---------------------------|

| DI_PD | digital input pull-down   | DO_T | digital output /tri-state |

| DI_PU | digital input pull-up     | ST   | schmitt-trigger input     |

| AI    | analog input              | AO   | analog output             |

| DI    | digital input             |      |                           |

### 4.1 Pin Description

Pins 7, 15 and 16 are supply pins, pins 5, 13 and 14 are for internal use and must be left open.

Pin 1 is the magnetic field strength indicator, MagRNGn. It is an open-drain output that is pulled to VSS when the magnetic field is out of the recommended range (45mT to 75mT). The chip will still continue to operate, but with reduced performance, when the magnetic field is out of range. When this pin is low, the analog output at pins #10 and #12 will be 0V to indicate the out-of-range condition.

Pin 2 MODE allows switching between filtered (slow) and unfiltered (fast mode). See section 10.

Pin 3 Chip Select (CSn; active low) selects a device for serial data transmission over the 2-wire interface. A "logic high" at CSn forces output SDA to digital tri-state.

Pin 4 SCL (Serial Clock) is the clock input for data transmission over the 2-wire serial interface

Pin 6 SDA (Serial Data Line) is the serial data input / output line during data transmission over the 2-wire interface

Pin 8 PROG is used to program the different operation modes, as well as the zero-position in the OTP register.

Pin 9 DACref is the external voltage reference input for the Digital-to-Analog Converter (DAC). If selected, the analog output voltage on pin 12 ( $V_{out}$ ) will be ratiometric to the voltage on this pin.

Pin10 DACout is the unbuffered output of the DAC. This pin may be used to connect an external OPAMP, etc. to the DAC.

Pin 11 FB (Feedback) is the inverting input of the OPAMP buffer stage.

Access to this pin allows various OPAMP configurations.

Pin 12 Vout is the analog output pin. The analog output is a DC voltage, ratiometric to VDD5V (3.0 - 5.5V) or an external voltage source and proportional to the angle.

# 5 Electrical Characteristics

### 5.1 Absolute Maximum Ratings (non operating)

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameter                            | Symbol            | Min  | Мах        | Unit | Note                                               |

|--------------------------------------|-------------------|------|------------|------|----------------------------------------------------|

| DC supply voltage                    | VDD5V             | -0.3 | 7          | V    | Pin VDD5V                                          |

| DC supply voltage                    | VDD3V3            |      | 5          | V    | Pin VDD3V3                                         |

|                                      |                   | -0.3 | VDD5V +0.3 |      | Pins MagRngn, Mode, CSn, CLK, DO, DACout, FB, Vout |

| Input pin voltage                    | Vin               | -0.3 | 5          | V    | Pin DACref                                         |

|                                      |                   | -0.3 | 7.5        |      | Pin PROG_DI                                        |

| Input current (latchup immunity)     | Iscr              | -100 | 100        | mA   | Norm: JEDEC 78                                     |

| Electrostatic discharge              | ESD               |      | ±2         | kV   | Norm: MIL 883 E method 3015                        |

| Storage temperature                  | T <sub>strg</sub> | -55  | 125        | °C   | Min – 67°F ; Max +257°F                            |

| Body temperature (Lead-free package) | T <sub>Body</sub> |      | 260        | °C   | t=20 to 40s, Norm: IPC/JEDEC J-Std-020C            |

|                                      |                   |      | 200        | Ŭ    | Lead finish 100% Sn "matte tin"                    |

| Humidity non-condensing              | Н                 | 5    | 85         | %    |                                                    |

# 5.2 Operating Conditions

| Parameter                                      | Symbol            | Min | Тур | Max | Unit | Note                             |

|------------------------------------------------|-------------------|-----|-----|-----|------|----------------------------------|

| Ambient temperature                            | T <sub>amb</sub>  | -40 |     | 125 | °C   | -40°F+257°F                      |

| Supply current                                 | I <sub>supp</sub> |     | 16  | 21  | mA   |                                  |

| Supply voltage at pin VDD5V                    | VDD5V             | 4.5 | 5.0 | 5.5 | V    | 5V operation                     |

| Voltage regulator output voltage at pin VDD3V3 | VDD3V3            | 3.0 | 3.3 | 3.6 | V    |                                  |

| Supply voltage at pin VDD5V                    | VDD5V             | 3.0 | 3.3 | 3.6 | V    | 3.3V operation                   |

| Supply voltage at pin VDD3V3                   | VDD3V3            | 3.0 | 3.3 | 3.6 | V    | (pin VDD5V and VDD3V3 connected) |

### 5.3 DC Characteristics for Digital Inputs and Outputs

### 5.3.1 CMOS Schmitt-Trigger Inputs: SCL, CSn (internal Pull-up), Mode (internal Pull-down)

(operating conditions: Tamb = -40 to +125°C, VDD5V = 3.0-3.6V (3V operation) VDD5V = 4.5-5.5V (5V operation) unless otherwise noted)

| Parameter                          | Symbol          | Min         | Max         | Unit | Note                  |

|------------------------------------|-----------------|-------------|-------------|------|-----------------------|

| High level input voltage           | V⊮              | 0.7 * VDD5V |             | V    | Normal operation      |

| Low level input voltage            | Vil             |             | 0.3 * VDD5V | V    |                       |

| Schmitt Trigger hysteresis         | Vlon- Vloff     | 1           |             | V    |                       |

| Input leakage current              | ILEAK           | -1          | 1           |      | Pin CLK, VDD5V = 5.0V |

| Pull-up low level input current    | l <sub>iL</sub> | -30         | -100        | μΑ   | Pin CSn, VDD5V= 5.0V  |

| Pull-down high level input current | liн             | 30          | 100         |      | Pin Mode, VDD5V= 5.0V |

### 5.3.2 CMOS Input: Program Input (Prog)

(operating conditions: T<sub>amb</sub> = -40 to +125°C, VDD5V = 3.0-3.6V (3V operation) VDD5V = 4.5-5.5V (5V operation) unless otherwise noted)

| Parameter               |              | Symbol | Min             | Мах                          | Unit | Note               |

|-------------------------|--------------|--------|-----------------|------------------------------|------|--------------------|

| High level input voltag | ge           | VIH    | 0.7 * VDD5V     | 5                            | V    |                    |

| High level input voltag | ge           | VPROG  | See "programmin | See "programming conditions" |      | During programming |

| Low level input voltag  | e            | VIL    |                 | 0.3 * VDD5V                  | V    |                    |

| Pull-down high level i  | nput current | liL    |                 | 100                          | μA   | VDD5V: 5.5V        |

### 5.3.3 CMOS Output Open Drain: MagRngn

(operating conditions: T<sub>amb</sub> = -40 to +125°C, VDD5V = 3.0-3.6V (3V operation) VDD5V = 4.5-5.5V (5V operation) unless otherwise noted)

| Parameter                  | Symbol | Min | Max     | Unit | Note        |

|----------------------------|--------|-----|---------|------|-------------|

| Low level output voltage   | Vol    |     | VSS+0.4 | V    |             |

| Output current             | l.     |     | 4       | mA   | VDD5V: 4.5V |

| Output current             | lo     |     | 2       | IIIA | VDD5V: 3V   |

| Open drain leakage current | loz    |     | 1       | μA   |             |

### 5.3.4 Tristate CMOS Output: SDA

(operating conditions: Tamb = -40 to +125°C, VDD5V = 3.0-3.6V (3V operation) VDD5V = 4.5-5.5V (5V operation) unless otherwise noted)

| Parameter                 | Symbol          | Min        | Мах     | Unit | Note        |

|---------------------------|-----------------|------------|---------|------|-------------|

| High level output voltage | V <sub>OH</sub> | VDD5V -0.5 |         | V    |             |

| Low level output voltage  | Vol             |            | VSS+0.4 | V    |             |

| Output current            | lo              |            | 4       | mA   | VDD5V: 4.5V |

|                           |                 |            | 2       | mA   | VDD5V: 3V   |

| Tri-state leakage current | l <sub>oz</sub> |            | 1       | μΑ   |             |

### 5.3.5 Digital-to-Analog Converter

| Parameter                                       | Symbol               | Min                    | Тур | Max          | Unit | Note                                                             | OTP setting             |

|-------------------------------------------------|----------------------|------------------------|-----|--------------|------|------------------------------------------------------------------|-------------------------|

| Resolution                                      |                      |                        | 10  |              | bit  |                                                                  |                         |

| Output Range                                    | V <sub>OUTM1</sub>   | 0                      |     | Vref         | V    | 0100% V <sub>ref</sub> (default)                                 | ClampMdEn = 0 (default) |

|                                                 | V <sub>OUTM2</sub>   | 0.10 *V <sub>ref</sub> |     | 0.90 *Vref   | V    | 1090% V <sub>ref</sub>                                           | ClampMdEn = 1           |

| Output resistance                               | R <sub>Out,DAC</sub> |                        |     | 8            | kΩ   | Unbuffered Pin DACout (#10)                                      |                         |

| DAC reference voltage<br>(DAC full scale range) | V <sub>ref</sub>     | 0.2                    |     | VDD3V3 - 0.2 | V    | DAC reference = external:<br>Pin: DACref (#9)                    | RefExt EN = 1           |

| (DAO Iuli scale range)                          |                      |                        |     | VDD5V / 2    | V    | DAC reference = internal                                         | RefExtEn = 0 (default)  |

| Integral Non-Linearity                          | INLDAC               |                        |     | +/- 1.5      | LSB  | Non-Linearity of DAC and                                         |                         |

| Differential Non-Linearity                      | DNLdac               |                        |     | +/- 0.5      | LSB  | OPAMP; -40+125°C, For all<br>analog modes:<br>1LSB = Vref / 1024 |                         |

|                                                 |                      |                        |     | 1            | LSB  | All analog modes                                                 |                         |

| Analog output hysteresis                        | Hyst                 |                        |     | 2            | LSB  | At 360°-0° transition,<br>360° mode only                         | OR1,OR0 = 00 (default)  |

### 5.3.6 OPAMP Output Stage

| Parameter                  | Symbol             | Min          | Тур | Max          | Unit  | Note                                                                                                                |

|----------------------------|--------------------|--------------|-----|--------------|-------|---------------------------------------------------------------------------------------------------------------------|

| Power Supply Range         | VDD5V              | 3.0          |     | 5.5          | V     |                                                                                                                     |

| Parallel Load Capacitance  | CL                 |              |     | 100          | pF    |                                                                                                                     |

| Parallel Load Resistance   | RL                 | 4.7          |     |              | kΩ    | 3.3V operation                                                                                                      |

| Open Loop Gain             | A0                 | 92           | 130 | 144          | dB    |                                                                                                                     |

| Offset Voltage RTI         | VosOP              | -5           |     | 5            | mV    | 3 sigma                                                                                                             |

| Output Range Low           | VoutL              |              |     | 0.05 * VDD5V | V     | Linear range of analog output                                                                                       |

| Output Range High          | VoutH              | 0.95 * VDD5V |     |              | V     |                                                                                                                     |

| current capability sink    | lsink              | 4.8          |     | 50           | mA    | Permanent short circuit current:<br>V <sub>out</sub> to VDD5V                                                       |

| current capability source  | lsource            | 4.6          |     | 66           | mA    | Permanent short circuit current:<br>V <sub>out</sub> to VSS                                                         |

| Output noise               | V <sub>noise</sub> | 160          | 220 | 490          | µVrms | Over full temperature range;<br>BW= 1Hz10MHz,Gain = 2x                                                              |

|                            |                    |              | 2   |              |       | Internal; OTP: FB_int EN = 1                                                                                        |

| OPAMP gain (non-inverting) | Gain               | 1            |     | 4            |       | External OTP: FB_int EN = 0<br>(default)<br>With external resistors, pins Vout<br>[#12] and FB [#11]: see Figure 17 |

# 5.4 Magnetic Input Specification

(operating conditions: T<sub>amb</sub> = -40 to +125°C, VDD5V = 3.0-3.6V (3V operation) VDD5V = 4.5-5.5V (5V operation)

unless otherwise noted)

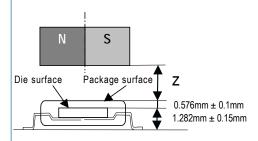

Two-pole cylindrical diametrically magnetised source:

| Parameter                      | Symbol               | Min | Тур    | Max  | Unit  | Note                                                                                                                                             |

|--------------------------------|----------------------|-----|--------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Diameter                       | d <sub>mag</sub>     | 4   | 6      |      | mm    | Recommended magnet: Ø 6mm x 2.5mm for cylindrical                                                                                                |

| Thickness                      | t <sub>mag</sub>     | 2.5 |        |      | mm    | magnets                                                                                                                                          |

| Magnetic input field amplitude | B <sub>pk</sub>      | 45  |        | 75   | mT    | Required vertical component of the magnetic field strength on<br>the die's surface, measured along a concentric circle with a<br>radius of 1.1mm |

| Magnetic offset                | Boff                 |     |        | ± 10 | mT    | Constant magnetic stray field                                                                                                                    |

| Field non-linearity            |                      |     |        | 5    | %     | Including offset gradient                                                                                                                        |

| Input frequency                | $f_{mag\_abs}$       |     |        | 10   | Hz    | Absolute mode: 600 rpm @ readout of 1024 positions (see table 6)                                                                                 |

| (rotational speed of magnet)   | f <sub>mag_inc</sub> |     |        | 166  | Hz    | Incremental mode: no missing pulses at rotational speeds of up to 10,000 rpm (see table 6)                                                       |

| Displacement radius            | Disp                 |     |        | 0.25 | mm    | Max. offset between defined device center and magnet axis                                                                                        |

| Recommended magnet material    |                      |     | -0.12  |      | %/K   | NdFeB (Neodymium Iron Boron)                                                                                                                     |

| and temperature drift          |                      |     | -0.035 |      | 70/ K | SmCo (Samarium Cobalt)                                                                                                                           |

# 5.5 Electrical System Specifications

(operating conditions: T<sub>amb</sub> = -40 to +125°C, VDD5V = 3.0-3.6V (3V operation) VDD5V = 4.5-5.5V (5V operation) unless otherwise noted)

| Parameter                                                                                            | Symbol                              | Min          | Тур        | Max        | Unit   | Note                                                                                                                                     |

|------------------------------------------------------------------------------------------------------|-------------------------------------|--------------|------------|------------|--------|------------------------------------------------------------------------------------------------------------------------------------------|

| Resolution <sup>1)</sup>                                                                             | RES                                 |              |            | 12         | bit    | 0.088 deg                                                                                                                                |

| Integral non-linearity (optimum) 1)                                                                  | INL <sub>opt</sub>                  |              |            | ± 0.5      | deg    | Maximum error with respect to the best line fit. Verified at optimum magnet placement, $T_{amb}$ =25 °C.                                 |

| Integral non-linearity (optimum) 1)                                                                  | INL <sub>temp</sub>                 |              |            | ± 0.9      | deg    | Maximum error with respect to the best line fit. Verified at optimum magnet placement , $T_{amb} = -40 \text{ to } +125^{\circ}\text{C}$ |

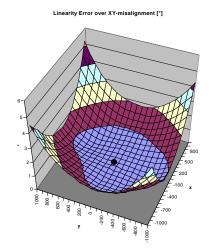

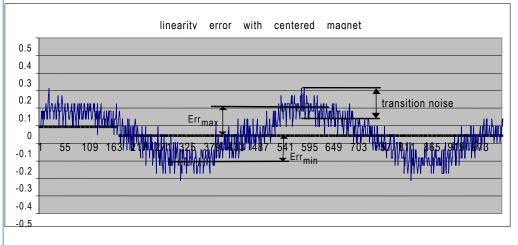

| Integral non-linearity <sup>1)</sup>                                                                 | INL                                 |              |            | ± 1.4      | deg    | Best line fit = $(Err_{max} - Err_{min}) / 2$<br>Over displacement tolerance with 6mm diameter magnet,<br>$T_{amb} = -40$ to +125°C      |

| Differential non-linearity 1)                                                                        | DNL                                 |              |            | ± 0.044    | deg    | 12bit, no missing codes                                                                                                                  |

| Transition noise <sup>1)</sup>                                                                       | TN                                  |              |            | 0.06       | Deg    | 1 sigma, fast mode (pin MODE = 1)                                                                                                        |

|                                                                                                      |                                     |              |            | 0.03       | RMS    | 1 sigma, slow mode (pin MODE=0 or open)                                                                                                  |

| Power-on reset thresholds<br>On voltage; 300mV typ. hysteresis<br>Off voltage; 300mV typ. hysteresis | V <sub>on</sub><br>V <sub>off</sub> | 1.37<br>1.08 | 2.2<br>1.9 | 2.9<br>2.6 | V<br>V | DC supply voltage 3.3V (VDD3V3)<br>DC supply voltage 3.3V (VDD3V3)                                                                       |

| Power-up time,<br>Until offset compensation finished,                                                | t <sub>PwrUp</sub>                  |              |            | 20         | ms     | fast mode (pin MODE=1)                                                                                                                   |

| OCF = 1, Angular Data valid                                                                          |                                     |              |            | 80         |        | slow mode (pin MODE=0 or open)                                                                                                           |

| System propagation delay                                                                             |                                     |              |            | 96         |        | fast mode (pin MODE=1)                                                                                                                   |

| absolute output : delay of ADC and DSP                                                               | t <sub>delay</sub>                  |              |            | 384        | μs     | slow mode (pin MODE=0 or open)                                                                                                           |

| Parameter                           | Symbol               | Min  | Тур   | Max   | Unit  | Note                                                             |

|-------------------------------------|----------------------|------|-------|-------|-------|------------------------------------------------------------------|

| Internal sampling rate for absolute | f <sub>S.mode0</sub> | 2.48 | 2.61  | 2.74  | kHz   | T <sub>amb</sub> = 25°C, slow mode (pin MODE=0 or open)          |

| output                              | rs,modeu             | 2.35 | 2.61  | 2.87  | KI IZ | T <sub>amb</sub> = -40 to +125°C, slow mode (pin MODE=0 or open) |

| Internal sampling rate for absolute | f <sub>S.mode1</sub> | 9.90 | 10.42 | 10.94 | kHz   | $T_{amb} = 25^{\circ}C$ , fast mode (pin MODE = 1)               |

| output                              | 'S,mode I            | 9.38 | 10.42 | 11.46 | KI IZ | $T_{amb}$ = -40 to +125°C, : fast mode (pin MODE = 1)            |

| Read-out frequency                  | CLK                  | >0   |       | 1     | MHz   | Max. clock frequency to read out serial data                     |

Note: 1) digital interface

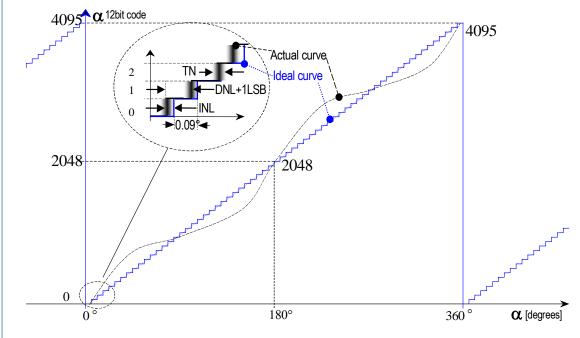

Figure 4: Integral and differential non-linearity (exaggerated curve)

Integral Non-Linearity (INL) is the maximum deviation between actual position and indicated position. Differential Non-Linearity (DNL) is the maximum deviation of the step length from one position to the next. Transition Noise (TN) is the repeatability of an indicated position.

# 5.6 Timing Characteristics

2-wire Serial Interface

(operating conditions: T<sub>amb</sub> = -40 to +125°C, VDD5V = 3.0-3.6V (3V operation) VDD5V = 4.5-5.5V (5V operation) unless otherwise noted)

| Parameter                             | Symbol                | Min | Тур | Max | Unit | Note                                                           |

|---------------------------------------|-----------------------|-----|-----|-----|------|----------------------------------------------------------------|

| Data output activated (logic high)    | t DO active           |     |     | 100 | ns   | Time between falling edge of CSn and data output activated     |

| First data shifted to output register | tclk FE               | 500 |     |     | ns   | Time between falling edge of CSn and first falling edge of CLK |

| Start of data output                  | T <sub>CLK/2</sub>    | 500 |     |     | ns   | Rising edge of CLK shifts out one bit at a time                |

| Data output valid                     | t <sub>DO valid</sub> | 357 | 375 | 394 | ns   | Time between rising edge of CLK and data output valid          |

| Data output tristate                  | t DO tristate         |     |     | 100 | ns   | After the last bit DO changes back to "tristate"               |

| Pulse width of CSn                    | t <sub>CSn</sub>      | 500 |     |     | ns   | CSn = high; To initiate read-out of next angular position      |

| Read-out frequency                    | fclĸ                  | >0  |     | 1   | MHz  | Clock frequency to read out serial data                        |

# 5.7 Programming Conditions

(operating conditions: T<sub>amb</sub> = -40 to +125°C, VDD5V = 3.0-3.6V (3V operation) VDD5V = 4.5-5.5V (5V operation) unless otherwise noted)

| Parameter                               | Symbol               | Min | Тур | Max | Unit | Note                                                           |

|-----------------------------------------|----------------------|-----|-----|-----|------|----------------------------------------------------------------|

| Programming enable time                 | t Prog enable        | 2   |     |     | μs   | Time between rising edge at Prog<br>pin and rising edge of CSn |

| Write data start                        | t Data in            | 2   |     |     | μs   |                                                                |

| Write data valid                        | t Data in valid      | 250 |     |     | ns   | Write data at the rising edge of CLK <sub>PROG</sub>           |

| Load programming data                   | t Load PROG          | 3   |     |     | μs   |                                                                |

| Rise time of VPROG before CLK PROG      | t PrgR               | 0   |     |     | μs   |                                                                |

| Hold time of VPROG after CLK PROG       | t PrgH               | 0   |     | 5   | μs   |                                                                |

| Write data – programming CLK PROG       | CLK PROG             |     |     | 250 | kHz  |                                                                |

| CLK pulse width                         | t <sub>PROG</sub>    | 1.8 | 2   | 2.2 | μs   | During programming; 16 clock cycles                            |

| Hold time of Vprog after<br>programming | t PROG finished      | 2   |     |     | μs   | Programmed data is available after next power-on               |

| Programming voltage                     | V prog               | 7.3 | 7.4 | 7.5 | V    | Must be switched off after zapping                             |

| Programming voltage off level           | V ProgOff            | 0   |     | 1   | V    | Line must be discharged to this level                          |

| Programming current                     | I PROG               |     |     | 130 | mA   | During programming                                             |

| Analog read CLK                         | CLK <sub>Aread</sub> |     |     | 100 | kHz  | Analog readback mode                                           |

| Programmed zener voltage (log.1)        | Vprogrammed          |     |     | 100 | mV   | $V_{\text{Ref}}V_{\text{PROG}}$ during analog readback         |

| Unprogrammed zener voltage (log. 0)     | Vunprogrammed        | 1   |     |     | V    | mode (see 13)                                                  |

# 6 Functional Description

The AS5046 is manufactured in a CMOS standard process and uses a spinning current Hall technology for sensing the magnetic field distribution across the surface of the chip.

The integrated Hall elements are placed in a circle around the center of the device and deliver a voltage representation of the magnetic field perpendicular to the surface of the IC.

Through Sigma-Delta Analog / Digital Conversion and Digital Signal-Processing (DSP) algorithms, the AS5046 provides accurate high-resolution absolute angular position information. For this purpose a Coordinate Rotation Digital Computer (CORDIC) calculates the angle and the magnitude of the Hall array signals.

The DSP is also used indicate movements of the magnet towards or away from the chip and to indicate, when the magnetic field is outside of the recommended range (status bits = MagInc, MagDec; hardware pin = MagRngn). In addition, two 8-bit registers are available that allow determination of the magnetic field strength over a wide range.

A small low cost diametrically magnetized (two-pole) standard magnet, centered over the chip, is used as the input device.

The AS5046 senses the orientation of the magnetic field and calculates a 12-bit binary code. This code can be accessed via a bi-directional serial two-wire interface. In addition to the digital output, the absolute angle is converted into a 1024-step (10-bit) analog signal, ratiometric to the supply voltage.

The analog output can be configured in many ways, such as 360°/180°/90° or 45° angular range, external or internal DAC reference voltage, 0-100%\*VDD or 10-90% \*VDD analog output range, external or internal amplifier gain setting.

The various output modes as well as a user programmable zero position can be programmed in an OTP register. As long as no programming voltage is applied to pin PROG, the new setting may be overwritten at any time and will be reset to default when power is cycled. To make the setting permanent, the OTP register must be programmed by applying a programming voltage.

The AS5046 is tolerant to magnet misalignment and unwanted external magnetic fields due to differential measurement technique and Hall sensor conditioning circuitry.

It is also tolerant to airgap and temperature variations due to Sin-/Cos- signal evaluation.

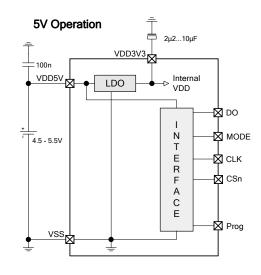

# 7 3.3V / 5V Operation

The AS5046 operates either at  $3.3V \pm 10\%$  or at 5V  $\pm 10\%$ . This is made possible by an internal 3.3V Low-Dropout (LDO) Voltage regulator. The core supply voltage is always taken from the LDO output, as the internal blocks are always operating at 3.3V.For 3.3V operation, the LDO must be bypassed by connecting VDD3V3 with VDD5V (see Figure 5).

For 5V operation, the 5V supply is connected to pin VDD5V, while VDD3V3 (LDO output) must be buffered by a 2.2...10 $\mu$ F capacitor, which should be placed close to the supply pin (see Figure 5).

The VDD3V3 output is intended for internal use only It should not be loaded with an external load.

The voltage levels of the digital interface I/O's correspond to the voltage at pin VDD5V, as the I/O buffers are supplied from this pin (see Figure 5).

A buffer capacitor of 100nF is recommended in both cases close to pin VDD5V. Note that pin VDD3V3 must always be buffered by a capacitor. It must not be left floating, as this may cause an instable internal 3.3V supply voltage which may lead to larger than normal jitter of the measured angle.

# 8 Two Wire Serial Interface

The AS5046 is accessible via an bi-directional serial interface.

CSn must be low during serial data transmission.

# 8.1 Serial Interface Timing Diagrams

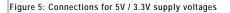

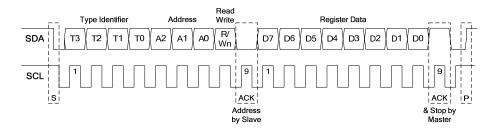

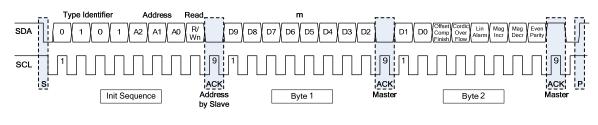

The registers in the AS5046 are available in a data length of 8 bit (1 byte), 24 bit (3 bytes) and 32 bit (4 bytes). Shown below in Figure 6 is a common 8-bit data transfer.

Figure 6: 8-bit serial Read / Write timing

Figure 7 shows a transfer timing diagram for the first 16 bits of the Serial Interface Unit.

Figure 7: 16-bit serial Read / Write timing

# 9 Accessible Registers for Serial Interface

| Status Register                 | Internal<br>Type<br>Identifier | 000 Programmable wi<br>A2A0 <sup>1)</sup>                                   |  | Register<br>Bit<br>Count | Read /<br>Write | Note                                               |  |  |

|---------------------------------|--------------------------------|-----------------------------------------------------------------------------|--|--------------------------|-----------------|----------------------------------------------------|--|--|

|                                 |                                | Address       000     Programmable v       000 -111     fixed address range |  |                          |                 | 10 bit angle <upper 10bits:="" d11:d2=""></upper>  |  |  |

|                                 |                                | 000 Programmable wit<br>A2A0 <sup>1)</sup>                                  |  |                          |                 | 6 bit status                                       |  |  |

| Serial Interface Unit           | 0101                           |                                                                             |  | 32                       | Read only       | 8 bit magnitude                                    |  |  |

|                                 |                                |                                                                             |  |                          |                 | 2 bit angle <lower 2="" bits:="" d1:d0=""></lower> |  |  |

| Hall Sensor Front End           | 0001                           | 01 000 -111 fixed address rang                                              |  | 8                        | Read / Write    | 8 selectable Hall front-end status registers       |  |  |

| ADC outputs, SIN/COS signal bus | 0100                           |                                                                             |  | 24                       | Read / Write    | 12bit SIN , 12bit COS input                        |  |  |

| Automatic Gain Control          | 0111                           | 000 Fixed address                                                           |  | 8                        | Read / Write    | AGC Counter                                        |  |  |

Table 2: Serial register overview

Notes:

- 1) This address is also modified with the analog mode setting

- 2) Writing a value to any of the SIN- COS- registers halts the conversion loop and calculates an angle that is given by the values in the SIN and COS registers. A Read command from these registers restarts the automatic conversion loop.

- 3) Writing a value to the AGC counter register halts the automatic gain control loop and sets the AGC to the value written in this register. The angle conversion loop continues to operate. A Read command from the AGC register restarts the automatic gain control loop.

### 9.1 Serial Interface Unit (Type ID: 0101)

The Serial Interface Unit contains 32 bits of data:

| T.I. 0101 |         |                                |  |  |  |  |    | Byte 2 |                                                 |      |   |  |  |      |       |        | Byt   | e 3   |       |   |   | Byte 4 |    |     |  |  |  |  |  |

|-----------|---------|--------------------------------|--|--|--|--|----|--------|-------------------------------------------------|------|---|--|--|------|-------|--------|-------|-------|-------|---|---|--------|----|-----|--|--|--|--|--|

| Auur.     | D11 D10 | 11 D10 D9 D8 D7 D6 D5 D4 D3 D2 |  |  |  |  | D2 | OCFC   | FCOF LIN M_I M_D P M7 M6 M5 M4 M3 M2 M1 M0 D1 D |      |   |  |  |      |       | D0     | 0     | 0     | 0     | 0 | 0 | 0      |    |     |  |  |  |  |  |

| 000111    |         |                                |  |  |  |  |    | 6      | bit s                                           | tatu | s |  |  | 8 bi | t mag | gnituo | de (N | ISB f | irst) |   |   |        | An | gle |  |  |  |  |  |

Note that the angle information is only valid, if the Hall Sensor Front-end is configured properly. See Table 4 for more information.

#### 9.1.1 12-bit Angle Information

the 12-bit angle data consists of two blocks: the upper 10-bits in bytes 1 & 2 and the lower two bits in byte 4

| Status bit 1 | SIU bit 11 | Offset Comp Finish | OCF | must be 1 for valid data                                                                                                   |

|--------------|------------|--------------------|-----|----------------------------------------------------------------------------------------------------------------------------|

| Status bit 2 | SIU bit 12 | CORDIC Over Flow   | COF | must be 0; if this bit is set, the angular data is invalid                                                                 |

| Status bit 3 | SIU bit 13 | Lin Alarm          | LIN | LINearity warning bit. Should be 0<br>for normal operation. Will be 1 when<br>the magnetic field is too high or too<br>low |

| Status bit 4 | SIU bit 14 | Mag Incr.          | M_I | This bit is set temporarily when the<br>magnetic field increases, when the<br>magnet is pushed towards the IC              |

| Status bit 5 | SIU bit 15 | Mag Decr.          | M_D | This bit is set temporarily when the<br>magnetic field decreases, when the<br>magnet is pulled away from the IC            |

| Status bit 6 | SIU bit 16 | Even Parity        | Р   | Even parity check bit of bytes 1 & 2                                                                                       |

#### 9.1.2 6-bit Status Information

Table 3: Status bits of byte 2 of the SIU

#### 9.1.3 8-bit Magnitude Information

The magnitude information is a value that is proportional to the magnetic field strength. A strong magnet (or close distance between magnet and chip) will result in a high magnitude value and vice versa. When the automatic gain control (AGC) is active (default state), it tries to keep the magnitude value stable at a value of 3F<sub>H</sub>.

# 9.2 Hall Sensor Front End (Type ID: 0001)

The Hall Sensor Front End allows configuration of each Hall Sensor. Each sensor can be disabled or connected to either the SIN or COS signal bus. Additionally, each sensor can be inverted for differential measurement.

Each Hall Sensor is selected through a device address for the type identifier 0001,

address 000 selects Hall Sensor H0 (see Figure 8)

address 111 selects Hall Sensor H7 (see Figure 8)

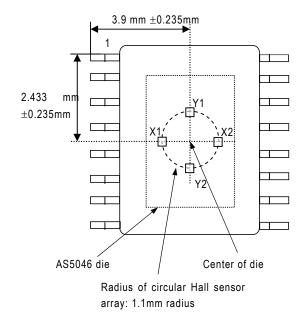

Figure 8: Location of Hall Elements on chip (top view)

Note: If the magnet is placed like shown in Figure 8 the encoder reading will be of zero.

For each Hall Sensor, the corresponding Front End contains 8 bits

| Type ID: 0001 | Byte1 TestEN SenseEN NC NC COS EN SIN EN INV PD |         |    |    |        |        |     |    |  |  |  |  |  |  |

|---------------|-------------------------------------------------|---------|----|----|--------|--------|-----|----|--|--|--|--|--|--|

| Addr. 000111  | TestEN                                          | SenseEN | NC | NC | COS_EN | SIN_EN | INV | PD |  |  |  |  |  |  |

| TestEN:  | always set to 0                                                                                                                                                           |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SenseEN: | set to 1 for enabled Hall Elements, set to 0 for disabled Hall Elements                                                                                                   |

| COS_EN:  | set to 0 for disabled Hall Elements, set to 1 if this Hall Element should be added to the COS signal bus. It is also possible to enable multiple Hall sensors to this bus |

| SIN_EN:  | set to 0 for disabled Hall Elements, set to 1 if this Hall Element should be added to the SIN signal bus. It is also possible to enable multiple Hall sensors to this bus |

| INV:     | set to 1 if the Hall Element should be inverted for differential measurement. set to 0 if the Hall Element should not be inverted                                         |

| PD:      | set to 0 for normal operation, set to 1 if the Hall Sensor should be powered down.                                                                                        |

Note: When enabling or disabling individual Hall elements to the SIN- and COS- signal buses it is recommended to allow several milliseconds (typ. 5ms) of dwelling time until the signal is stable and eventual offsets are compensated.

# 9.3 Hall Sensor Front-End Configuration

The default configuration for the Hall Sensor Front-End is set for angle measurement. This configuration must always be programmed when an angle should be measured and read from the Serial Interface Unit register.

|     | Addr | testEN | SenseEN | NC | NC | COS_EN | SIN_EN | Inv | PD |

|-----|------|--------|---------|----|----|--------|--------|-----|----|

| FE0 | 000  | 0      | 1       | 0  | 0  | 0      | 1      | 0   | 0  |

| FE1 | 001  | 0      | 1       | 0  | 0  | 0      | 1      | 0   | 0  |

| FE2 | 010  | 0      | 1       | 0  | 0  | 1      | 0      | 0   | 0  |

| FE3 | 011  | 0      | 1       | 0  | 0  | 1      | 0      | 0   | 0  |

| FE4 | 100  | 0      | 1       | 0  | 0  | 0      | 1      | 1   | 0  |

| FE5 | 101  | 0      | 1       | 0  | 0  | 0      | 1      | 1   | 0  |

| FE6 | 110  | 0      | 1       | 0  | 0  | 1      | 0      | 1   | 0  |

| FE7 | 111  | 0      | 1       | 0  | 0  | 1      | 0      | 1   | 0  |

Table 4: Hall Sensor Front-End default configuration

The following configuration example selects Hall Sensor 0 and assigns it to the SIN signal bus:

|     | Addr | testEN | SenseEN | NC | NC | COS_EN | SIN_EN | Inv | PD |

|-----|------|--------|---------|----|----|--------|--------|-----|----|

| FE0 | 000  | 0      | 1       | 0  | 0  | 0      | 1      | 0   | 0  |

| FE1 | 001  | 0      | 0       | 0  | 0  | 0      | 0      | 0   | 0  |

| FE2 | 010  | 0      | 0       | 0  | 0  | 0      | 0      | 0   | 0  |

| FE3 | 011  | 0      | 0       | 0  | 0  | 0      | 0      | 0   | 0  |

| FE4 | 100  | 0      | 0       | 0  | 0  | 0      | 0      | 0   | 0  |

| FE5 | 101  | 0      | 0       | 0  | 0  | 0      | 0      | 0   | 0  |

| FE6 | 110  | 0      | 0       | 0  | 0  | 0      | 0      | 0   | 0  |

| FE7 | 111  | 0      | 0       | 0  | 0  | 0      | 0      | 0   | 0  |

Table 5: Example: Readout of a single Hall Sensor (Sensor #0)

This example uses two opposite Hall sensors 1 and 5 in differential mode and assigns the resulting signal to the COS signal bus:

|     | Addr | testEN | SenseEN | NC | NC | COS_EN | SIN_EN | Inv | PD |

|-----|------|--------|---------|----|----|--------|--------|-----|----|

| FE0 | 000  | 0      | 0       | 0  | 0  | 0      | 0      | 0   | 0  |

| FE1 | 001  | 0      | 1       | 0  | 0  | 1      | 0      | 0   | 0  |

| FE2 | 010  | 0      | 0       | 0  | 0  | 0      | 0      | 0   | 0  |

| FE3 | 011  | 0      | 0       | 0  | 0  | 0      | 0      | 0   | 0  |

| FE4 | 100  | 0      | 0       | 0  | 0  | 0      | 0      | 0   | 0  |

| FE5 | 101  | 0      | 1       | 0  | 0  | 1      | 0      | 1   | 0  |

| FE6 | 110  | 0      | 0       | 0  | 0  | 0      | 0      | 0   | 0  |

| FE7 | 111  | 0      | 0       | 0  | 0  | 0      | 0      | 0   | 0  |

Table 6: Example: Differential measurement of two opposite Hall Sensors (#1 and 5)

# 9.4 Analog-Digital Converter Outputs, SIN/COS Signal Bus (Type ID: 0100)

| Type ID:<br>0100 |                   | Byte 1<br>12-bit ADC output: COS signal bus |  |   |                |  |       |    |                                                   |    |   | Byte | 9 2 |   |   |   |   |   |                 | Byt | e 3 |               |   |   |

|------------------|-------------------|---------------------------------------------|--|---|----------------|--|-------|----|---------------------------------------------------|----|---|------|-----|---|---|---|---|---|-----------------|-----|-----|---------------|---|---|

| Addr. 000        | 12-               | bit A[                                      |  | • | : CO<br>8 bits |  | nal b | us | 12-bit ADC output: SIN signal bus<br>Upper 8 bits |    |   |      |     |   |   |   |   |   | ınal k<br>4 bit |     |     | N sig<br>ower |   |   |

|                  | 11 10 9 8 7 6 5 4 |                                             |  |   |                |  |       | 4  | 11                                                | 10 | 9 | 8    | 7   | 6 | 5 | 4 | 3 | 2 | 1               | 0   | 3   | 2             | 1 | 0 |

The analog signals on the SIN- and COS- buses are converted into a signed 12-bit digital value by two ADC's, one for each bus.

To read the signal from one or more Hall Sensors, first assign a signal bus (SIN, COS) for each Hall Sensor in the Hall Sensor front-end and then read the corresponding amplitude value from the ADC output register.

Note that the ADC's are 14-bit (see Block diagram, Figure 2), but only 12-bit are available to the user. The available 12-bit ADC output is again split into an upper 8-bit block (available in bytes 1 & 2) and a lower 4-bit block in byte 3. The resulting 12-bit value is formatted as a signed 12-bit value and has a range from -2048...+2047 (decimal). Bit 11 (MSB) is the sign bit; if this bit is set, the Sin/Cos value is negative.

### 9.5 Automatic Gain Control Register (Type ID: 0111)

The Automatic Gain Control is active in the "green" range of the magnetic field, when the magnetic field is within  $\sim$ 35...63mT. If the magnetic field is too low, e.g. when the magnet is too far away from the chip, the AGC register will be FF<sub>H</sub>, if the magnetic field is too strong, e.g. when the magnet is too close to the chip, the AGC register will be 00<sub>H</sub>. The Automatic Gain control can be disabled by writing a value into this register. It will be enabled by reading from this register.

The AGC tries to maintain a constant magnitude value of 3F<sub>H</sub>. If the AGC has reached its upper or lower limit, the magnitude value can no longer be maintained ad 3F<sub>H</sub> and will also change accordingly (see 9.1.3 and 9.6).

| Type ID: 0111 |      |      |      | By   | /te 1 |      |      |      |

|---------------|------|------|------|------|-------|------|------|------|

| Addr. 000     | AGC7 | AGC6 | AGC5 | AGC5 | AGC3  | AGC2 | AGC1 | AGC0 |

### 9.6 AGC and Magnitude Registers

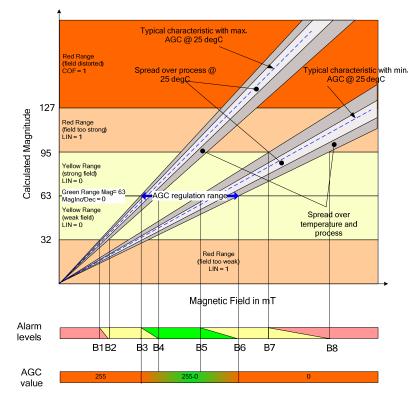

The AS5046 allows the readout of two additional registers related to magnetic field strength: magnitude and AGC registers. Figure 9 shows a graphic example of the interrelations of these two registers in respect to the magnetic field strength of the magnet (all register levels are in decimal format).

at a low magnetic field strength (below level B1 / B2) the magnitude will be <32 and the AGC will be at maximum: 255. the LIN status bit will be set (red range). It is not recommended to operate in this range, although the AS5046 will still produce usable results at very weak magnetic fields.

if the magnetic field strength is further increased above a magnitude value of 32, LIN will be cleared. The AGC will remain at 255 until the magnitude has reached a value of 63 (yellow range; level B3/B4). The angular data can still be used in the yellow range, but the noise (=jitter) will be larger than normal.

Once the magnitude is strong enough to reach a value of 63, the AGC will regulate the internal loop gain to maintain this value. Magnitude will remain at 63 and the AGC will regulate between 0 and 255 (green range; magnetic field strength between level B3/B4 and B5/B6). This is the recommended operating range

If the magnetic field strength rises further than B5/B4, the AGC can no longer regulate the loop and will be at its minimum value of 0. The magnitude value will increase (yellow range; up to B7/B8). In this range, the angular data will still be valid. Due to the rather strong field, there is no issue with noise, but the magnetic field may be more distorted than in the normal operating range which may lead to additional errors.

Above level B7/B8 the LIN alarm will be set once the magnitude has exceeded a level of 95 (red range). It is not recommended to operate in this range. The main contributing part for errors will be a more distorted magnetic field.

If the magnitude exceeds a value of 127, the COF (cordic overflow) alarm will be set. This case can only occur with very strong magnets and does usually not occur in practice. The angular data will be invalid when the COF bit is set.

Figure 9: Magnitude and AGC values vs. magnetic field strength

| Parameter                                        | Symbol             | Min   | Тур   | Max    | Unit | Note              |

|--------------------------------------------------|--------------------|-------|-------|--------|------|-------------------|

| Input Field tolerance level red2yellow B1 - B2   | Br2y25             | 16.77 | 17.95 | 19.33  | mT   |                   |

| Input Field tolerance level yellow2green B3 - B4 | B <sub>y2g25</sub> | 33.01 | 35.35 | 38.06  | mT   | At 25°C ambient   |

| Input Field tolerance level green2yellow B5 - B6 | B <sub>g2y25</sub> | 60.0  | 64.24 | 69.15  | mT   | temperature       |

| Input Field tolerance level yellow2red B7 – B8   | B <sub>y2r25</sub> | 90.45 | 96.87 | 104.28 | mT   |                   |

| Input Field tolerance level red2yellow B1 - B2   | Br2y               | 15.64 | 17.95 | 22.37  | mT   | Over the full     |

| Input Field tolerance level yellow2green B3 - B4 | B <sub>y2g</sub>   | 30.80 | 35.35 | 44.05  | mT   | specified         |

| Input Field tolerance level green2yellow B5 - B6 | B <sub>g2y</sub>   | 55.96 | 64.24 | 80.04  | mT   | temperature range |

| Input Field tolerance level yellow2red B7 – B8   | B <sub>y2r</sub>   | 84.39 | 96.87 | 120.69 | mT   |                   |

### 9.7 Z-Axis Range Indication (Push Button Feature, Red/Yellow/Green Indicator

The AS5046 provides several options of detecting movement and distance of the magnet in the vertical (Z-) direction. Signal indicators MagINC, MagDEC and LIN are available as status bits in the serial data stream, while MagRngn is an open-drain output that indicates an out-of range status (on in YELLOW or RED range). Additionally, the analog output provides a safety feature in the form that it will be turned off when the magnetic field is too strong or too weak (RED range). The serial data is always available, the red/yellow/green status is indicated by the status bits as shown below:

| Statu      | s Bits     |     | Hardware Pins |                  |                                                                                                                                                                                                                                                                                |

|------------|------------|-----|---------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mag<br>INC | Mag<br>DEC | LIN | Mag<br>Rngn   | Analog<br>output | Description                                                                                                                                                                                                                                                                    |

| 0          | 0          | 0   | Off           | enabled          | No distance change<br>Magnetic Input Field OK (GREEN range, ~4575mT)                                                                                                                                                                                                           |

| 0          | 1          | 0   | Off           | enabled          | Distance increase, GREEN range; Pull-function. This state is dynamic and only active while the magnet is moving away from the chip.                                                                                                                                            |

| 1          | 0          | 0   | Off           | enabled          | Distance decrease, GREEN range; Push- function. This state is dynamic and only active while the magnet is moving towards the chip.                                                                                                                                             |

| 1          | 1          | 0   | On            | enabled          | YELLOW Range: Magnetic field is ~ 2545mT or ~75135mT. The AS5046 may still be operated in this range, but with slightly reduced accuracy.                                                                                                                                      |

| 1          | 1          | 1   | On            | disabled         | RED Range: Magnetic field is ~<25mT or >~135mT. The analog output will be turned off in this range by default. It can be enabled permanently by OTP programming (see 11.1.2). It is still possible to use the absolute serial interface in the red range, but not recommended. |

Table 7: Magnetic field strength indicators

# 10 Mode Input Pin

The absolute angular position is sampled at a rate of 10.4kHz (t=96µs) in fast mode and at a rate of 2.6kHz (t=384µs) in slow mode.

These modes are selected by pin MODE (#2). The mode input pin activates or deactivates an internal filter, which is used to reduce the digital jitter and consequently the analog output noise.

Activating the filter by pulling Mode = LOW or leaving it open reduces the transition noise to  $<0.03^{\circ}$  rms. At the same time, the sampling rate is reduced to 2.6kHz and the signal propagation delay is increased to 384µs. This mode is recommended for high precision, low speed and  $\leq$ 360° applications.

Deactivating the filter by setting Mode = HIGH increases the sampling rate to 10.4kHz and reduces the signal propagation delay to 96µs. The transition noise will increase to <0.06° rms. This mode is recommended for higher speed and full scale = 360° applications.

Revision 1.1

www.austriamicrosystems.com

Switching the MODE pin affects the following parameters:

| Parameter                     | Slow Mode<br>(Pin MODE = 0 or<br>open) | Fast Mode<br>(Pin MODE = 1) |

|-------------------------------|----------------------------------------|-----------------------------|

| sampling rate                 | 2.61 kHz                               | 10.42 kHz                   |

|                               | (383µs)                                | (95.9µs)                    |

| transition noise<br>(1 sigma) | ≤ 0.03° rms                            | $\leq$ 0.06° rms            |

| propagation<br>delay          | 384µs                                  | 96µs                        |

| Startup time                  | 20ms                                   | 80ms                        |

Table 8: Mode pin settings

Pin MODE should be fixed at power-up. A mode change during operation is not recommended.

# Parallel Mode

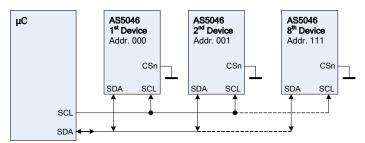

The Parallel Mode allows connection of up to 8 AS5046's in parallel on the SCL and SDA line, maintaining just two wires for data transmission. This mode is accomplished by connecting all the SDA and SCL inputs/outputs in parallel. Each AS5046 device can be programmed one address ranging from 0...7 (see Table 2)

Figure 10: Parallel connection of up to 8 devices

Note that the parallel connection has some restrictions:

- Each unit must be programmed to have a different address (ranging from 000 to 111; see Table 2)

- Changing the address also changes the analog mode, as these OTP bits share the same position.(see Figure 13)

- Only the SIU containing angle data and status bits can be read from parallel devices (type ID 0101). The other

registers all share the same type identifier (0001, 1011, 0111; see Table 2), which would lead to data collision

when trying to read any of these registers from parallel devices.

# 11 Ratiometric Analog Angle Output

The analog output V<sub>out</sub> provides an analog voltage that is proportional to the angle of the rotating magnet and ratiometric to the supply voltage VDD5V (max.5.5V). It can source or sink currents up to  $\pm$ 1mA in normal operation (up to 66mA short circuit current).

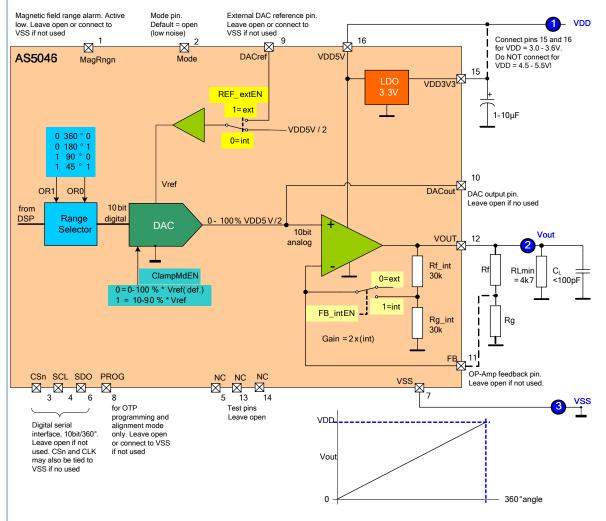

The analog output block consists of a digital angular range selector, a 10-bit Digital-to-Analog converter and an OPAMP buffer stage (see Figure 17).

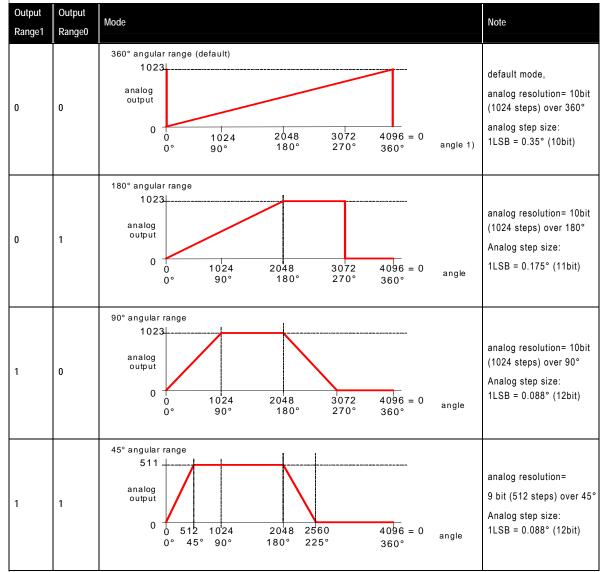

The digital range selector allows a preselection of the angular range for 360°, 180°, 90° or 45° (see Table 9). Fine-tuning of the angular range can be accomplished by adjusting the gain of the OPAMP buffer stage.

The reference voltage for the Digital-to-Analog converter (DAC) can be taken internally from VDD5V / 2. In this mode, the output voltage is ratiometric to the supply voltage.

Alternatively, an external DAC reference can be applied at pin DACref (#9). In this mode, the analog output is ratiometric to the external reference voltage.

Revision 1.1

www.austriamicrosystems.com

An on-chip diagnostic feature turns the analog output off in case of an error (broken supply or magnetic field out of range; see Table 7). The DAC output can be accessed directly at pin #10 DACout.

The addition of an OPAMP to the DAC output allows a variety of user configurable options, such as variable output voltage ranges and variable output voltage versus angle response. By adding an external transistor, the analog voltage output can be buffered to allow output currents up to hundred milliamperes or more.

Furthermore, the OPAMP can be configured as constant current source.

As an OTP option, the DAC can be configured to 2 different output ranges:

a) 0.....100% VDACref. The reference point may be either taken from VDD5V/2 or from the external DACref input. The 0...100% range allows easy replacement of potentiometers. Due to the nature of rail-to-rail outputs, the linearity will degrade at output voltages that are close to the supply rails.

b) 10.....90% V<sub>DACref</sub>. This range allows better linearity, as the OPAMP is not driven to the rails. Furthermore, this mode allows failure detection, when the analog output voltage is outside of the normal operating range of 10...90%VDD, as in the case of broken supply or when the magnetic field is out of range and the analog output is turned off.

### 11.1 Analog Output Voltage Modes

The Analog output voltage modes are programmable by OTP. Depending on the application, the analog output can be selected as rail-to-rail output or as clamped output with 10%-90% VDD5V.

The output is ratiometric to the supply voltage (VDD5V), which can range from 3.0V to 5.5V. If the DAC reference is switched to an external reference (pin DACref), the output is ratiometric to the external reference.

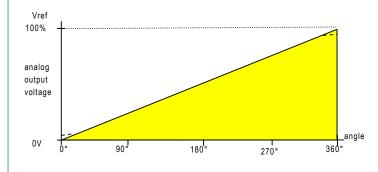

#### 11.1.1 Full Scale Mode

This output mode provides a ratiometric DAC output of (0% to 100%)x Vref \*), amplified by the OPAMP stage (default = internal 2x gain, see Figure 17)

Note: For simplification, Figure 11 describes a linear output voltage from rail to rail (0V to VDD). In practice, this is not feasible due to saturation effects of the OPAMP output driver transistors. The actual curve will be rounded towards the supply rails (as indicated in Figure 11).

Figure 11: Analog output, full scale mode (shown for 360°mode)

Note: Figure 11 and are shown for 360° operation. See Table 9 (page 24) for further angular range programming options.

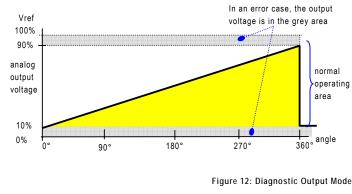

11.1.2 Diagnostic Output Mode

In Diagnostic Output Mode (see Figure 12) the analog output of the internal DAC ranges from 10% - 90% Vref\*). In an error case, either when the supply is interrupted or when the magnetic field is in the "red" range, (see Table 7) the output is switched to OV and thus indicates the error condition.

Revision 1.1

www.austriamicrosystems.com

It is possible to enable the analog output permanently (it will not be switched off even if the magnetic field is out of range). To enable this feature an OTP bit in the factory setting must be set. The corresponding bit is FS6. See application note AS5040-20 (Extended features of OTP programming) for further details. The application note is available for download at the austriamicrosystems website.

The analog and digital outputs will have the following conditions:

| Status                                                                                  | DAC Output Voltage                                                                                                  | Serial Digital Output                                                                                     |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| normal operation                                                                        | 10% - 90% Vref <sup>1)</sup>                                                                                        | #0 - #1023 (0°-360°),<br>MagRngn = 1                                                                      |

| magnetic field out of range                                                             | < 10% Vref <sup>1)</sup> ,<br>DAC output is switched to<br>0V<br>(this feature may be disabled<br>in OTP; see text) | #0 - #1023 (0°-360°)<br>out of range is signaled in status<br>bits:<br>MagInc=MagDec=LIN=1,<br>MagRngn= 0 |

| broken positive power supply<br>(V <sub>OUT</sub> pull down resistor at receiving side) | < 10% VDD <sup>2)</sup>                                                                                             |                                                                                                           |

| broken power supply ground<br>(Vour pull down resistor at receiving side)               | < 10% VDD <sup>2)</sup>                                                                                             | The serial data bits read by the serial interface will be either all                                      |

| broken positive power supply<br>(V <sub>OUT</sub> pull up resistor at receiving side)   | > 90% VDD 2)                                                                                                        | "0"-s or all "1"-s, indicating a non-<br>valid output                                                     |

| broken power supply ground<br>(V <sub>OUT</sub> pull up resistor at receiving side)     | > 90% VDD <sup>2</sup> )                                                                                            |                                                                                                           |

Notes:

1) Vref = internal: ½ \* VDD5V (pin #16) or external: V<sub>DACref</sub> (pin#9), depending on Ref\_extEN bit in OTP (0=int., 1=ext.)

2) VDD = positive supply voltage at receiving side (3.0 – 5.5V)

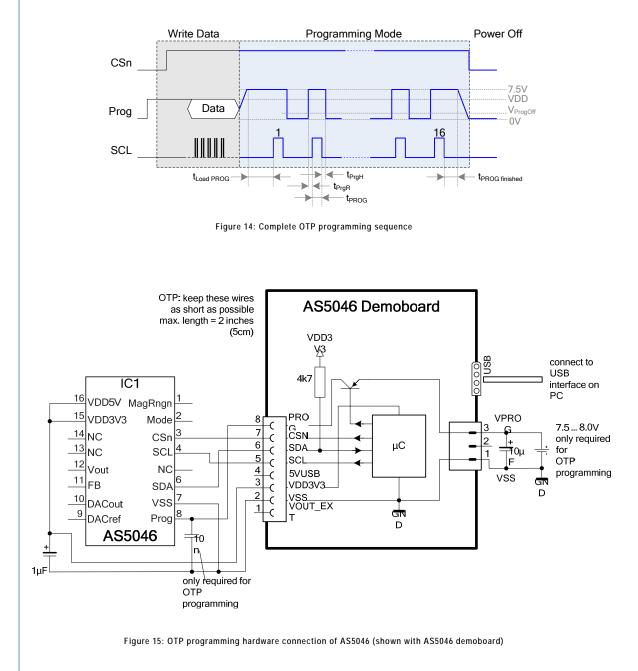

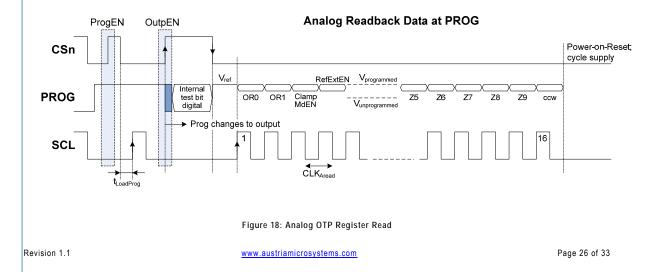

# 12 Programming the AS5046

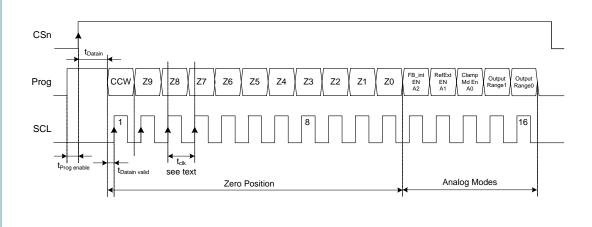

After power-on, programming the AS5046 is enabled with the rising edge of CSn and Prog = logic high. 16 bit configuration data must be serially shifted into the OTP register via the Prog-pin. The first "CCW" bit is followed by the zero position data (MSB first) and the Analog Output Mode setting as shown in Table 9. Data must be valid at the rising edge of CLK (see Figure 13). Following this sequence, the voltage at pin Prog must be raised to the programming voltage V<sub>PROG</sub> (see Figure 14). 16 CLK pulses (t<sub>PROG</sub>) must be applied to program the fuses. To exit the programming mode, the chip must be reset by a power-on-reset. The programmed data is available after the next power-up.

Note: During the programming process, the transitions in the programming current may cause high voltage spikes generated by the inductance of the connection cable. To avoid these spikes and possible damage to the IC, the connection wires, especially the signals PROG and VSS must be kept as short as possible. The maximum wire length between the  $V_{PROG}$  switching transistor and pin PROG (Figure 15) should not exceed 50mm (2 inches).

To suppress eventual voltage spikes, a 10nF ceramic capacitor should be connected close to pins PROG and VSS. This capacitor is only required for programming, it

is not required for normal operation. The clock timing t<sub>clk</sub> must be selected at a proper rate to ensure that the signal PROG is stable at the rising edge of CLK (see Figure 13). Additionally, the programming supply voltage should be buffered with a 10 $\mu$ F capacitor mounted close to the switching transistor. This capacitor aids in providing peak currents during programming. The specified programming voltage at pin PROG is 7.3 – 7.5V (see section 5.7). To compensate for the voltage drop across the V<sub>PROG</sub> switching transistor, the applied programming voltage may be set slightly higher (7.5 - 8.0V, see Figure 15).

**OTP Register Contents:**

- CCW Counter Clockwise Bit

- ccw=0 angular value increases with clockwise rotation

- ccw=1 angular value increases with counterclockwise rotation

- Z [9:0]: Programmable Zero / Index Position

- FB\_intEN: OPAMP gain setting: 0=external, 1=internal; this bit also sets device address bit A2 !

- RefExtEN: DAC reference: 0=internal, 1=external; this bit also sets device address bit A1 !

- ClampMd EN: Analog output span: 0=0-100%, 1=10-90%\*VDD;

this bit also sets device address bit A0

Output Range (OR0, OR1):

|       | Analog Output | Range Selection |

|-------|---------------|-----------------|

| [1:0] | 00 = 360°     | 01 = 180°       |

|       | 10 = 90°      | 11 = 45°        |

Disable shutdown of analog output : see 11.1.2

Figure 13: Programming Access – OTP Write Cycle (section of Figure 14)

### 12.1 Zero Position Programming

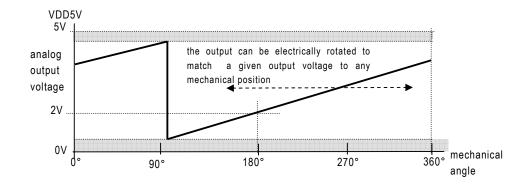

The AS5046 allows easy assembly of the system, as the actual angle of the magnet does not need to be considered. By OTP programming, any position can be assigned as the new permanent zero position with an accuracy of 0.35° (all modes).

Using the same procedure, the AS5046 can be calibrated to assign a given output voltage to a given angle. With this approach, all offset errors (DAC + OPAMP) are also compensated for the calibrated position. Essentially, for a given mechanical position, the angular measurement system is electrically rotated (by changing the Zero Position value in the OTP register), until the output matches the desired mechanical position.

The example in Figure 16 below shows a configuration for 5V supply voltage and 10%-90% output voltage range. It adjusted by Zero Position Programming to provide an analog output voltage of 2.0 Volts at an angle of 180°. The slope of the curve may be further adjusted by changing the gain of the OPAMP output stage and by selecting the desired angular range (360°/180°/90°/45°).

Figure 16: Zero position programming (shown for 360° mode)

### 12.2 Analog Mode Programming

The analog output can be configured in many ways:

It consists of three major building blocks,

a digital range preselector,

a 10-bit Digital-to-Analog-Converter (DAC)

and an OP-AMP buffer stage.

In the default configuration (all OTP bits = 0), the analog output is set for 360° operation, internal DAC reference (VDD5V/2), external OPAMP gain, 0-100% ratiometric to VDD5V.

Shown below is a typical example for a 0°-360° range, 0-5V output. The complete application requires only one external component, a buffer capacitor at VDD3V3 and has only 3 connections VDD, VSS and Vout (connectors 1-3).

Note: the default setting for the OPAMP feedback path is:FB\_intEn=0=external. The external resistors Rf and Rg must be installed. In the programmed state (FB\_intEn=1=internal), these resistors do not need to be installed as the feedback path is internal (Rf\_int and Rg\_int).

AS5046 Programmable 360° Magnetic Angle Encoder – Preliminary Data Sheet

Figure 17: Analog output block diagram

#### 12.2.1 Angular Range Selector

The Angular Range selector allows a digital pre-selection of the angular range. The AS5046 can be configured for a full scale angular range of 45°, 90°, 180° or 360°. In addition, the Output voltage versus angle response can be fine-tuned by setting the gain of the OP-AMP with external resistors and the maximum output voltage can be set in the DAC.

The combination of these options allows to configure the operation range of the AS5046 for all angles up to 360° and output voltages up to 5.5V

The response curve for the analog output is linear for the selected range  $(45^{\circ}/90^{\circ}/180^{\circ}/360^{\circ})$ . In addition, the slope is mirrored at  $180^{\circ}$  for  $45^{\circ}$ - and  $90^{\circ}$ - modes and has a step response at  $270^{\circ}$  for the  $180^{\circ}$ -mode. This allows the AS5046 to be used in a variety of applications. In these three modes, the output remains at V<sub>out,max</sub> and V<sub>out,min</sub> to avoid a sudden output change when the mechanical angle is rotated beyond the selected analog range. In  $360^{\circ}$ -mode, a jitter between V<sub>out,max</sub> and V<sub>out,min</sub> at the  $360^{\circ}$  point is also prevented due to a hysteresis.

Note: 1) The resolution on the digital serial interface is always 12bit (0.088°/step) over 360°, independent of analog mode

Table 9: Digital Range Selector programming option

### 12.3 Repeated OTP Programming

Although a single AS5046 OTP register bit can be programmed only once (from 0 to 1), it is possible to program other, unprogrammed bits in subsequent programming cycles. However, a bit that has already been programmed should not be programmed twice. Therefore it is recommended that bits that are already programmed are set to "0" during a programming cycle.

### 12.4 Non-permanent Programming

It is also possible to re-configure the AS5046 in a nonpermanent way by overwriting the OTP register.

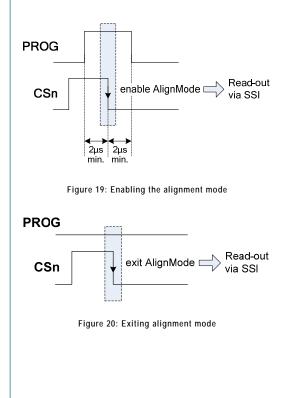

This procedure is essentially a "Write Data" sequence (see Figure 13) without a subsequent OTP programming cycle.