# Pin-Programmable Dual Controller—Portable PCs

## **FEATURES**

- Fixed 5-V and Programmable 3.3-V, 3.45 V, or 3.6 V Step-Down Converters

- Less than 500-μA Quiescent Current per Converter

- 25-µA Shutdown Current

- 5.5-V to 30-V Operating Range

## DESCRIPTION

The Si9130 Pin-programmable Dual Controller for Portable PCs is a pin-programmable version of the Si786 dual-output power supply controller for notebook computers. The Buck controllers provide 5 V and a pin-programmable output delivering 3.3 V, 3.45 V, or 3.6 V.

The circuit is a system level integration of two step-down controllers and micropower 5-V and 3.3-V linear regulators. The controllers perform high efficiency conversion of the battery pack energy (typically 12 V) or the output of an ac to dc wall converter (typically 18-V to 24-V dc) to 5-V and 3.3-V system supply voltages. The micropower linear regulator can be used to keep power management and back-up circuitry alive during the shutdown of the step-down converters.

A complete power conversion and management system can be implemented with the Si9130 Pin-programmable Dual Controller for Portable PCs, an inexpensive linear regulator, the Si9140 SMP Controller for High Performance Processor Power Supplies, five Si4410 n-channel TrenchFET® Power MOSFETs, one Si4435 p-channel TrenchFET Power MOSFET, and two Si9712 PC Card (PCMCIA) Interface Switches.

The Si9130 is available in both standard and lead (Pb)-free 28-pin SSOP packages and specified to operate over the commercial (0°C to 70°C) and extended commercial ( $-10^{\circ}C$  to 90°C) temperature ranges. See Ordering Information for corresponding part numbers.

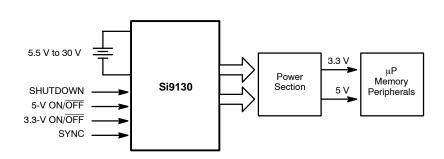

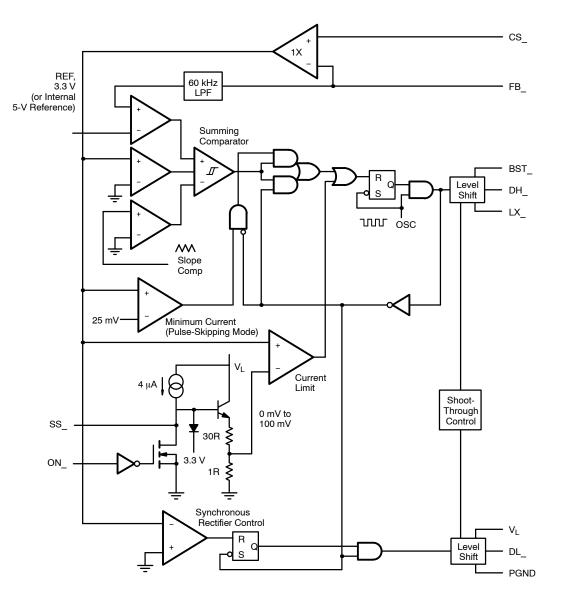

## FUNCTIONAL BLOCK DIAGRAM

## **ABSOLUTE MAXIMUM RATINGS**

| V+ to GND                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PGND to GND $\hfill {\rm GND}$ $\hfill {\rm Eq}$ $\hfill {\rm SND}$                                                                                                                                                                                                                                                                                      |

| $V_L$ to GND $\ldots$                                                                                                                                                                                                                                                                                                                                    |

| BST_3, BST_5 to GND $\ldots \ldots 0.3$ V to 36 V                                                                                                                                                                                                      |

| $LX_3$ to $BST_3$                                                                                                                                                                                                                                                                                                                                        |

| $LX_5$ to $BST_5$                                                                                                                                                                                                                                                                                                                                        |

| $\label{eq:2.1} \begin{array}{l} \mbox{Inputs/Outputs to GND} \\ (3.45ADJ, 3.6ADJ, \overline{SHDN}, ON_5, REF, SS_5, CS_5, FB_5, SYNC, CS_3, FB_3, SS_3, ON_3)) & -0.3 V, (V_L + 0.3 V) \\ \mbox{DL}_3, DL_5 to PGND & -0.3 V, (V_L + 0.3 V) \\ \mbox{DH}_3 to LX_3 & -0.3 V (BST_3 + 0.3) \\ \mbox{DH}_5 to LX_5 & -0.3 V (BST_5 + 0.3) \\ \end{array}$ |

| REF, V <sub>L</sub> Short to GND N                    | <i>lomentary</i> |

|-------------------------------------------------------|------------------|

| REF Current                                           | 20 mA            |

| V <sub>L</sub> Current                                | 50 mA            |

| Continuous Power Dissipation (T <sub>A</sub> = 70°C)a |                  |

| 28-Pin SSOP <sup>b</sup>                              | . 762 mW         |

| Operating Temperature Range:                          |                  |

| Si9130CG                                              | 0 to 70°C        |

| Si9130LG                                              | )° to 90°C .     |

| Lead Temperature (soldering, 10 sec)                  | 300°C            |

Notes

a. Device mounted with all leads soldered or welded to PC board.

b. Derate 9.52 mW/°C above 70°C.

Exposure to Absolute Maximum rating conditions for extended periods may affect device reliability. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied.

| SPECIFICATIONS                                      |                                                                            |                                                                                                                                                                                                                                                                                                                       |      |        |                  |      |

|-----------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|------------------|------|

|                                                     | Specific                                                                   | $\label{eq:specific Test Conditions} \begin{split} & \textbf{Specific Test Conditions} \\ V+ = 15 \text{ V}, _{VL} = _{REF} = 0 \text{ mA}, \overline{SHDN} = \text{ON}_3 = \text{ON}_5 = 5 \text{ V} \\ \text{Other Digital Input Levels 0 V or 5 V, } _{A} = \text{T}_{MIN} \text{ to } \text{T}_{MAX} \end{split}$ |      | LIMITS |                  |      |

| PARAMETER                                           | V+ = 15 V, I <sub>VL</sub> = I <sub>REF</sub> =<br>Other Digital Input Lev |                                                                                                                                                                                                                                                                                                                       |      | ТҮРВ   | MAX <sup>A</sup> | UNIT |

| 3.3-V and 5-V Step-Down Co                          | ontrollers                                                                 |                                                                                                                                                                                                                                                                                                                       |      |        |                  |      |

| Input Supply Range                                  |                                                                            |                                                                                                                                                                                                                                                                                                                       | 5.5  |        | 30               |      |

| FB <sub>5</sub> Output Voltage                      |                                                                            | 0 mV < (CS <sub>5</sub> -FB <sub>5</sub> ) < 70 mV, 6 V < V + < 30 V<br>(includes load and line regulation)                                                                                                                                                                                                           |      | 5.08   | 5.20             |      |

| FB <sub>3</sub> Output Voltage                      | 0 mV < (CS <sub>3</sub> -FB <sub>3</sub> ) <                               | 3.6ADJ = 3.45ADJ = OPEN                                                                                                                                                                                                                                                                                               | 3.17 | 3.35   | 3.46             | V    |

|                                                     | 70 mV<br>6 V < V + < 30 V                                                  | 3.6ADJ = OPEN<br>3.45ADJ = GND                                                                                                                                                                                                                                                                                        | 3.32 | 3.50   | 3.60             |      |

|                                                     | (includes load and line regulation)                                        | 3.6ADJ = GND<br>3.45ADJ = OPEN                                                                                                                                                                                                                                                                                        | 3.46 | 3.65   | 3.75             |      |

| Load Regulation                                     | Either Controller                                                          | Either Controller (CS_to FB_ = 0 to 70 mV)                                                                                                                                                                                                                                                                            |      | 2.5    |                  | %    |

| Line Regulation                                     | Either Contro                                                              | Either Controller (V+ = 6 V to 30 V)                                                                                                                                                                                                                                                                                  |      | 0.03   |                  | %/V  |

| Current-Limit Voltage                               | CS <sub>3</sub> -I                                                         | CS <sub>3</sub> -FB <sub>3</sub> or CS <sub>5</sub> -FB <sub>5</sub>                                                                                                                                                                                                                                                  |      | 100    | 120              | mV   |

| SS <sub>3</sub> /SS <sub>5</sub> Source Current     |                                                                            |                                                                                                                                                                                                                                                                                                                       |      | 4.0    | 6.5              | μA   |

| SS <sub>3</sub> /SS <sub>5</sub> Fault Sink Current |                                                                            |                                                                                                                                                                                                                                                                                                                       | 2    |        |                  | mA   |

| Internal Regulator and Refe                         | rence                                                                      |                                                                                                                                                                                                                                                                                                                       |      |        |                  | •    |

| V <sub>L</sub> Output Voltage                       |                                                                            | $ON_5 = ON_3 = 0 \text{ V}, 5.5 \text{ V} < \text{V}+ < 30 \text{ V}$<br>0 mA < I <sub>L</sub> < 25 mA                                                                                                                                                                                                                |      |        | 5.5              |      |

| V <sub>L</sub> Fault Lockout Voltage                | Falling Ed                                                                 | Falling Edge, Hysteresis = 1%                                                                                                                                                                                                                                                                                         |      |        | 4.2              |      |

| VL/FB5 Switchover Voltage                           | Rising Edge of                                                             | Rising Edge of FB <sub>5</sub> , Hysteresis = 1%                                                                                                                                                                                                                                                                      |      |        | 4.7              | V    |

| REF Output Voltage                                  | No I                                                                       | No External Load <sup>c</sup>                                                                                                                                                                                                                                                                                         |      |        | 3.36             | 1    |

| REF Fault Lockout Voltage                           | F                                                                          | alling Edge                                                                                                                                                                                                                                                                                                           | 2.4  |        | 3.2              | 1    |

| REF Load Regulation                                 | 0 m.                                                                       | 0 mA < I <sub>L</sub> < 5 mA <sup>d</sup>                                                                                                                                                                                                                                                                             |      | 30     | 75               | mV   |

www.vishay.com **2**

| SPECIFICATIONS                                                                                                                                        |                                                                                                                                                            |                        |      |      |                      |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------|----------------------|--|

|                                                                                                                                                       | Specific Test Conditions                                                                                                                                   | LIMITS                 |      |      |                      |  |

| PARAMETER                                                                                                                                             | V+ = 15 V, $I_{VL}$ = $I_{REF}$ = 0 mA, $\overline{SHDN}$ = $ON_3$ = $ON_5$ = 5 V<br>Other Digital Input Levels 0 V or 5 V, $T_A$ = $T_{MIN}$ to $T_{MAX}$ | MIN <sup>A</sup>       | ТҮРВ | МАХА | UNIT                 |  |

| Internal Regulator and Refer                                                                                                                          | ence (Cont'd)                                                                                                                                              |                        |      |      |                      |  |

| V+ Shutdown Current                                                                                                                                   | SHDN = ON <sub>3</sub> = ON <sub>5</sub> = 0 V, V+ = 30 V                                                                                                  |                        | 25   | 40   | 40<br>110 μ <b>Α</b> |  |

| V+ Standby Current                                                                                                                                    | ON <sub>3</sub> = ON <sub>5</sub> = 0 V, V+ = 30 V                                                                                                         |                        | 70   | 110  |                      |  |

| Quiescent Power Consumption<br>(both PWM controllers on)                                                                                              | $\label{eq:FB5} \begin{array}{l} {\sf FB}_5 = {\sf CS}_5 = 5.25 \ {\sf V} \\ {\sf FB}_3 = {\sf CS}_3 = 3.5 \ {\sf V} \end{array}$                          |                        | 5.5  | 8.6  | mW                   |  |

| V+ Off Current                                                                                                                                        | $FB_5 = CS_5 = 5.25 \text{ V}, \text{ V}_L \text{ Switched Over to } FB_5$                                                                                 |                        | 30   | 60   | μΑ                   |  |

| Oscillator and Inputs/Output                                                                                                                          | s                                                                                                                                                          |                        |      |      |                      |  |

| o                                                                                                                                                     | SYNC = 3.3 V                                                                                                                                               | 270                    | 300  | 330  | - kHz                |  |

| Oscillator Frequency                                                                                                                                  | SYNC = 0 V, 5 V                                                                                                                                            | 170                    | 200  | 230  |                      |  |

| SYNC High Pulse Width                                                                                                                                 |                                                                                                                                                            | 200                    |      |      |                      |  |

| SYNC Low Pulse Width                                                                                                                                  |                                                                                                                                                            | 200                    |      |      | ns                   |  |

| SYNC Rise/Fall Time                                                                                                                                   | Not Tested                                                                                                                                                 |                        |      | 200  |                      |  |

| Oscillator SYNC Range                                                                                                                                 |                                                                                                                                                            | 240                    |      | 350  | kHz                  |  |

| Maufanuar Dutu Quala                                                                                                                                  | SYNC = 3.3 V                                                                                                                                               | 89                     | 92   |      | ~ %                  |  |

| Maximum Duty Cycle                                                                                                                                    | SYNC = 0 V, 5 V                                                                                                                                            | 92                     | 95   |      |                      |  |

| Input Low Voltage                                                                                                                                     | SHDN, ON3, ON5 SYNC                                                                                                                                        |                        |      | 0.8  |                      |  |

| 1                                                                                                                                                     | SHDN, ON <sub>3</sub> , ON <sub>5</sub>                                                                                                                    | 2.4                    |      |      | v                    |  |

| Input High Voltage                                                                                                                                    | SYNC                                                                                                                                                       | V <sub>L</sub> - 0.5 V |      |      | 1                    |  |

| Input Current                                                                                                                                         | $\overline{\text{SHDN}}$ , $\text{ON}_3$ , $\text{ON}_5$ V <sub>IN</sub> = 0 V, 5 V                                                                        |                        |      | ±1   | μΑ                   |  |

| DL <sub>3</sub> /DL <sub>5</sub> Sink/Source Current                                                                                                  | V <sub>OUT</sub> = 2 V                                                                                                                                     |                        | 1    | 1    | •                    |  |

| DH <sub>3</sub> /DH <sub>5</sub> Sink/Source Current BST <sub>3</sub> - LX <sub>3</sub> = BST <sub>5</sub> - LX <sub>5</sub> = 4.5 V, $V_{OUT}$ = 2 V |                                                                                                                                                            |                        | 1    | 1    | A                    |  |

| DL <sub>3</sub> /DL <sub>5</sub> On-Resistance                                                                                                        | High or Low                                                                                                                                                |                        | 7    |      |                      |  |

| DH <sub>3</sub> /DH <sub>5</sub> On-Resistance                                                                                                        | High or Low<br>BST <sub>3</sub> - LX <sub>3</sub> = BST <sub>5</sub> - LX <sub>5</sub> = 4.5 V                                                             |                        |      | 7    | Ω                    |  |

Notes

The algebraic convention whereby the most negative value is a minimum and the most positive a maximum.

Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

The main switching outputs track the reference voltage. Loading the reference reduces the main outputs slightly according to the closed-loop gain (AV<sub>CL</sub>) and the reference voltage load-regulation error. AV<sub>CL</sub> for the 3.3-V supply is unity gain. AV<sub>CL</sub> for the 5-V supply is 1.54.

Since the reference uses V<sub>L</sub> as its supply, its V+ line regulation error is insignificant.

V<sub>IN</sub> = 15 V

1

Vini = 15

1

5 V On

0.1

3.3-V Output Current (A)

$ON_3 = ON_5 = 0 V$

12

Supply Voltage (V)

18

10

10

TIIII V<sub>IN</sub> = 30 V . .....

3.3 V Off

0.1

5-V Output Current (A)

V<sub>IN</sub> = 6 V

V<sub>IN</sub> = 30 V

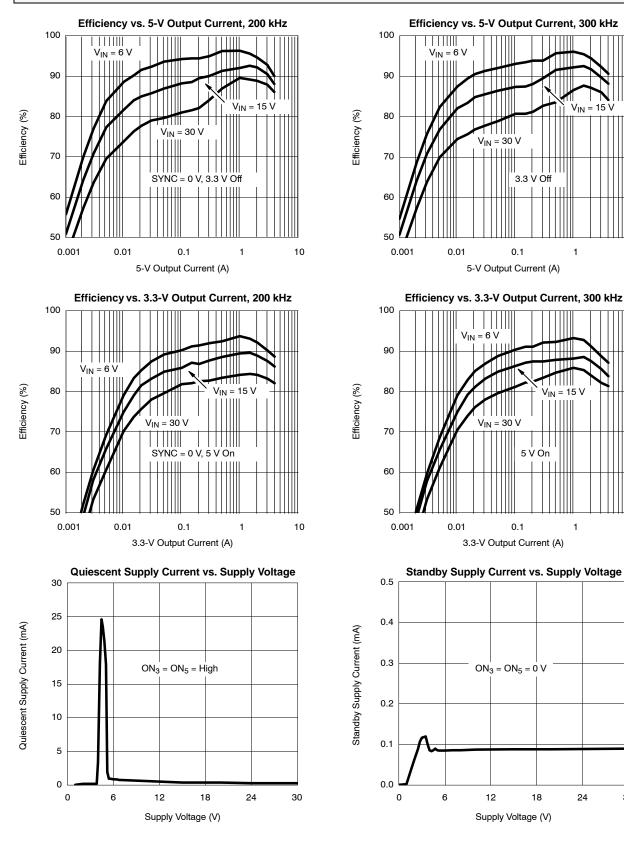

## **TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)**

www.vishay.com 4

Document Number: 70190 S-40805-Rev. F, 26-Apr-04

30

24

## **TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)**

# Si9130

# **Vishay Siliconix**

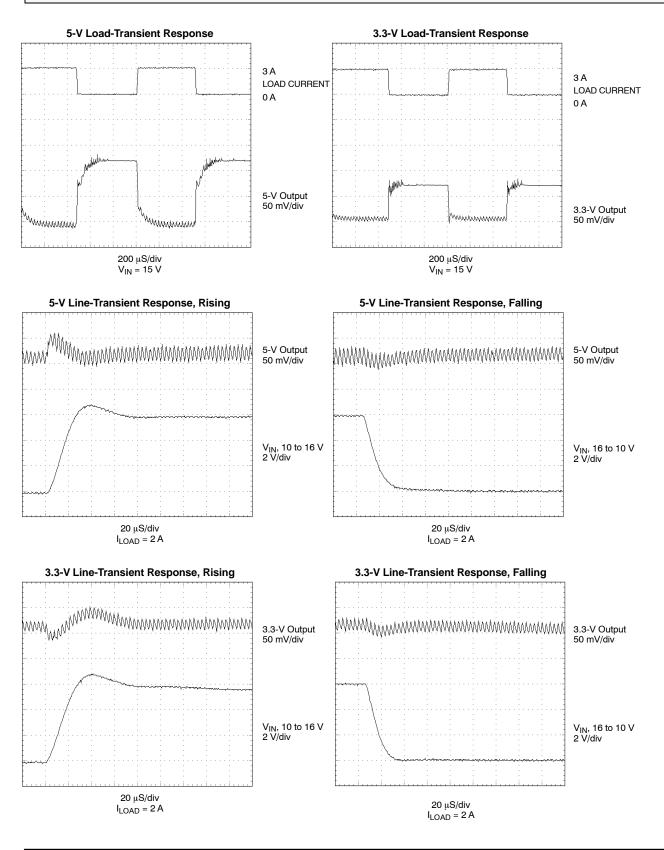

## TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

www.vishay.com 6

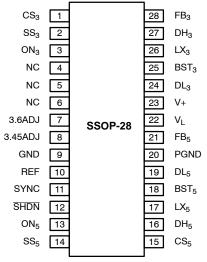

## **PIN CONFIGURATION AND DESCRIPTION**

Top View

| Ordering Information    |                               |                      |                  |  |

|-------------------------|-------------------------------|----------------------|------------------|--|

| Standard<br>Part Number | Lead (Pb)-Free<br>Part Number | Temperature<br>Range | V <sub>OUT</sub> |  |

| Si9130CG                |                               | 0 to 70°C            |                  |  |

| Si9130CG-T1             | Si9130CG-T1—E3                | 010700               | 5 V and 3.3 V    |  |

| Si9130LG                |                               | 10.1-00%0            | 3.45 V or 3.6 V  |  |

| Si9130LG-T1             | Si9130LG-T1-E3                | –10 to 90°C          |                  |  |

| Demo Board | Temperature Range | Board Type    |

|------------|-------------------|---------------|

| Si9130DB   | 0 to 70°C         | Surface Mount |

| Pin | Symbol           | Description                                                                                                                                                                                                                                                                             |  |

|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | CS <sub>3</sub>  | Current-sense input for 3.3-V Buck controller-this pins over current threshold is 100 mV with respect to FB <sub>3</sub> .                                                                                                                                                              |  |

| 2   | SS <sub>3</sub>  | Soft-start input for 3.3 V. Connect capacitor from $SS_3$ to GND.                                                                                                                                                                                                                       |  |

| 3   | ON <sub>3</sub>  | ON/OFF logic input disables the 3.3-V Buck controller. Connect directly to VL for automatic turn-on.                                                                                                                                                                                    |  |

| 4   | NC               | Not internally connected.                                                                                                                                                                                                                                                               |  |

| 5   | NC               | Not internally connected.                                                                                                                                                                                                                                                               |  |

| 6   | NC               | Not internally connected.                                                                                                                                                                                                                                                               |  |

| 7   | 3.6ADJ           | Control input to select 3.6-V output. See Voltage Selection Table for input and output combinations.                                                                                                                                                                                    |  |

| 8   | 3.45ADJ          | Control input to select 3.45-V output. See Voltage Selection Table for input and output combinations.                                                                                                                                                                                   |  |

| 9   | GND              | Analog ground.                                                                                                                                                                                                                                                                          |  |

| 10  | REF              | 3.3-V reference output. Supplies external loads up to 5 mA.                                                                                                                                                                                                                             |  |

| 11  | SYNC             | Oscillator control/synchronization input. Connect capacitor to GND, 1-µF/mA output or 0.22 µF minimum. For external clock synchronization, a rising edge starts a new cycle to start. To use internal 200-kHz oscillator, connect to VL or GND. For 300-kHz oscillator, connect to REF. |  |

| 12  | SHDN             | Shutdown logic input, active low. Connect to V <sub>L</sub> for automatic turn-on. The 5-V V <sub>L</sub> supply will not be disabled in shutdown allowing connection to SHDN.                                                                                                          |  |

| 13  | ON <sub>5</sub>  | ON/OFF logic input disables the 5-V Buck Controller. Connect to VL for automatic turn-on.                                                                                                                                                                                               |  |

| 14  | SS5              | Soft-start control input for 5-V Buck controller. Connect capacitor from SS <sub>5</sub> to GND.                                                                                                                                                                                        |  |

| 15  | CS <sub>5</sub>  | Current-sense input for 5-V Buck controller—this pins over current threshold is 100 mV referenced to FB <sub>3</sub> .                                                                                                                                                                  |  |

| 16  | DH <sub>5</sub>  | Gate-drive output for the 5-V supply high-side n-channel MOSFET.                                                                                                                                                                                                                        |  |

| 17  | LX <sub>5</sub>  | Inductor connection for the 5-V supply.                                                                                                                                                                                                                                                 |  |

| 18  | BST <sub>5</sub> | Boost capacitor connection for the 5-V supply.                                                                                                                                                                                                                                          |  |

| 19  | $DL_5$           | Gate-drive output for the 5-V supply rectifying n-channel MOSFET.                                                                                                                                                                                                                       |  |

| 20  | PGND             | Power Ground.                                                                                                                                                                                                                                                                           |  |

| 21  | FB <sub>5</sub>  | Feedback input for the 5-V Buck controller.                                                                                                                                                                                                                                             |  |

| 22  | VL               | 5-V logic supply voltage for internal circuitry—able to source 5-mA external loads. V <sub>L</sub> remains on with valid voltage at V+.                                                                                                                                                 |  |

| 23  | V+               | Supply voltage input.                                                                                                                                                                                                                                                                   |  |

| 24  | DL <sub>3</sub>  | Gate-drive output for the 3.3-V supply rectifying n-channel MOSFET.                                                                                                                                                                                                                     |  |

| 25  | BST <sub>3</sub> | Boost capacitor connection for the 3.3-V supply.                                                                                                                                                                                                                                        |  |

| 26  | LX <sub>3</sub>  | Inductor connection for the 3.3-V supply.                                                                                                                                                                                                                                               |  |

| 27  | DH <sub>3</sub>  | Gate-drive output for the 3.3-V supply high-side n-channel MOSFET.                                                                                                                                                                                                                      |  |

| 28  | FB <sub>3</sub>  | Feedback input for the 3.3-V Buck controller.                                                                                                                                                                                                                                           |  |

| Voltage Selection Table |        |                 |  |

|-------------------------|--------|-----------------|--|

| Ing                     | Output |                 |  |

| 3.45ADJ                 | 3.6ADJ | FB <sub>3</sub> |  |

| OPEN                    | OPEN   | 3.3 V           |  |

| GND                     | OPEN   | 3.45 V          |  |

| OPEN                    | GND    | 3.6 V           |  |

## **DESCRIPTION OF OPERATION**

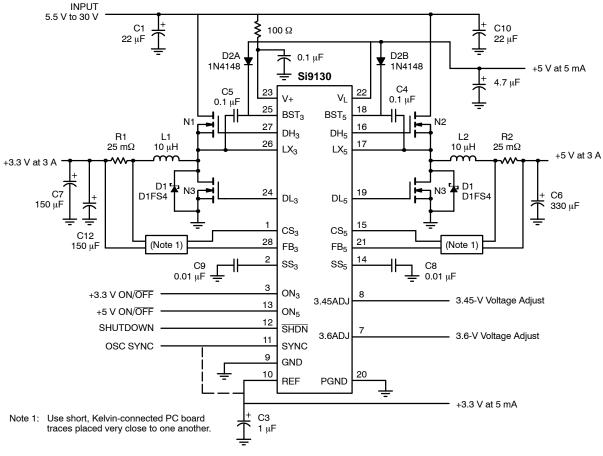

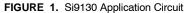

The Si9130 is a dual step-down converter, which takes a 5.5-V to 30-V input and supplies power via two PWM controllers (see Figure 1). These 5-V and 3.3-V supplies run on an optional 300-kHz or 200-kHz internal oscillator, or an external sync signal. Amount of output current is limited by external components, but can deliver greater than 6 A on either supply. As well as these two main Buck controllers, additional loads can be driven from two micropower linear regulators, one 5 V (V<sub>L</sub>) and the other 3.3 V (REF)—see Figure 2. These supplies are each rated to deliver 5 mA. If the linear regulator circuits fall out of regulation, both Buck controllers are shut down.

### 3.3-V PWM Voltage Selection (Pins 3.45ADJ, 3.6ADJ)

The voltage at this output can be selected to 3.3 V, 3.45 V or 3.6 V, depending on the configuration of pins 3.45ADJ and 3.6ADJ. Leaving both pins open results in 3.3V nominal output. Grounding pin 3.45ADJ while leaving 3.6ADJ open delivers 3.45-V nominal output. Grounding 3.6 ADJ while leaving 3.45ADJ open sets a 3.6-V nominal output.

www.vishay.com 8

### 3.3-V Switching Supply

The 3.3-V supply is regulated by a current-mode PWM controller in conjunction with several externals: two n-channel MOSFETs, a rectifier, an inductor and output capacitors (see Figure 1). The gate drive supplied by DH<sub>3</sub> needs to be greater than V<sub>L</sub>, so it is provided by the bootstrap circuit consisting of a 100-nF capacitor and diode connected to BST3.

A low-side switching MOSFET connected to  $DL_3$  increases efficiency by reducing the voltage across the rectifier diode. A low value sense resistor in series with the inductor sets the maximum current limit, to disallow current overloads at power-on or in short-circuit situations.

The soft-start feature on the Si9130 is capacitor programmable; pin  $SS_3$  functions as a constant current source to the external capacitor connected to GND. Excess currents

at power-on are avoided, and power-supplies can be sequenced with different turn-on delay times by selecting the correct capacitor value.

### 5-V Switching Supply

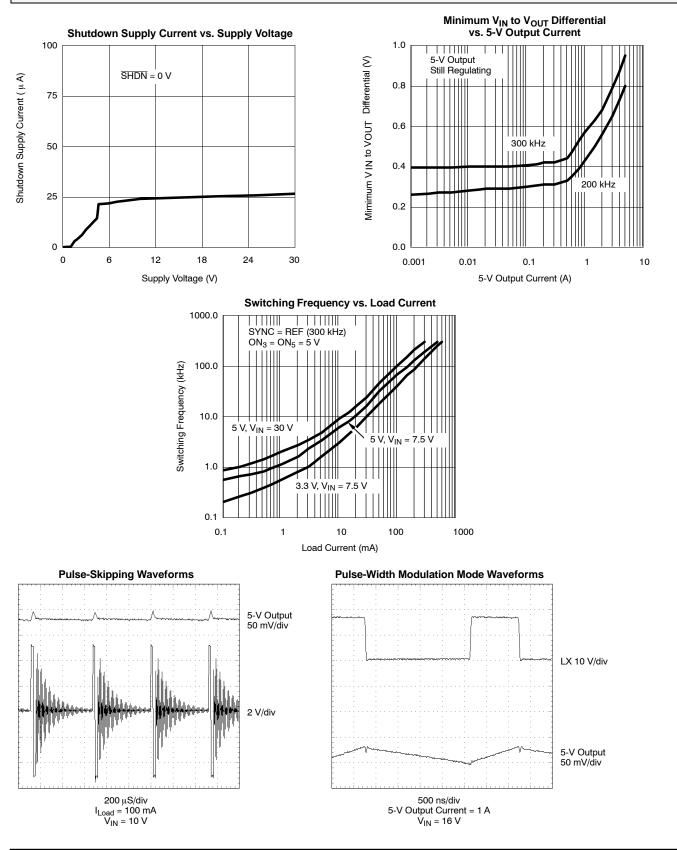

The 5-V supply is regulated by a current-mode PWM controller which is nearly the same as the 3.3-V output. The dropout voltage across the 5-V supply, as shown in the schematic in Figure 1, is 400 mV (typ) at 2 A. If the voltage at V+ falls, nearing 5 V, the 5-V supply will lower as well, until the V<sub>L</sub> linear regulator output falls below the 4-V undervoltage lockout threshold. Below this threshold, the 5-V controller is shut off.

The frequency of both PWM controllers is set at 300 kHz when the SYNC pin is tied to REF. Connecting SYNC to either GND or  $V_L$  sets the frequency at 200 kHz.

FIGURE 2. Si9130 Block Diagram

FIGURE 3. Si9130 Controller Block Diagram

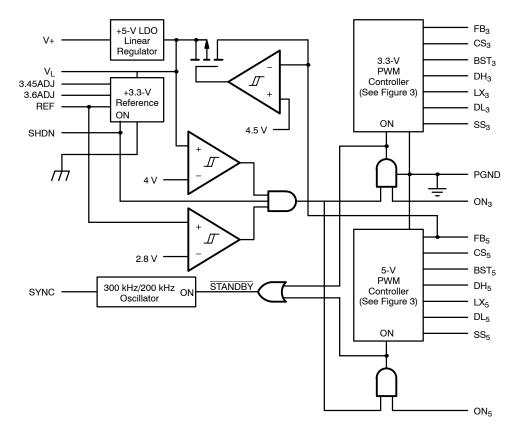

#### 3.3-V and 5-V Switching Controllers

Each PWM controller on the Si9130 is identical with the exception of the preset output voltages. The controllers only share three functional blocks (see Figure 3): the oscillator, the voltage reference (REF) and the 5-V logic supply (V<sub>L</sub>). The 3.3-V and 5-V controllers are independently enabled with pins ON<sub>3</sub> and ON<sub>5</sub>, respectively. The PWMs are a direct-summing type, without the typical integrating error amplifier along with the phase shift which is a side effect of this type of topology. Feedback compensation is not needed, as long as the output capacitance and its ESR requirements are met, according to the *Design Considerations* section of this data sheet.

www.vishay.com 10 The main PWM comparator is an open loop device which is comprised of three comparators summing four signals: the feedback voltage error signal, current sense signal, slope-compensation ramp and voltage reference as shown in Figure 3. This method of control comes closer to the ideal of maintaining the output voltage on a cycle-by-cycle basis. When the load demands high current levels, the controller is in full PWM mode. Every cycle from the oscillator asserts the output latch and drives the gate of the high-side MOSFET for a period determined by the duty cycle (approximately  $V_{\rm OU}T/V_{\rm IN} \times 100\%$ ) and the frequency.

The high-side switch turns off, setting the synchronous rectifier latch and 60 ns later, the rectifier MOSFET turns on. The low-side switch stays on until the start of the next clock cycle in continuous mode, or until the inductor current becomes positive again, in discontinuous mode. In over-current situations, where the inductor current is greater than the 100-mV current-limit threshold, the high-side latch is reset and the high-side gate drive is shut off.

During low-current load requirements, the inductor current will not deliver the 25-mV minimum current threshold. The Minimum Current comparator signals the PWM to enter pulse-skipping mode when the threshold has not been reached. pulse-skipping mode skips pulses to reduce switching losses, the losses which decrease efficiency the most at light load. Entering this mode causes the minimum current comparator to reset the high-side latch at the beginning of each oscillator cycle.

#### Soft-Start

To slowly bring up the 3.3-V and 5-V supplies, connect capacitors from SS<sub>3</sub> and SS<sub>5</sub> to GND. Asserting ON<sub>3</sub> or ON<sub>5</sub> starts a 4-A constant current source to charge these capacitors to 4 V. As the voltage on these pins ramps up, so does the current limit comparator threshold, to increase the duty cycle of the MOSFETs to their maximum level. If ON<sub>3</sub> or ON<sub>5</sub> are left low, the respective capacitor is discharged to GND. Leaving the SS<sub>3</sub> or SS<sub>5</sub> pins open will cause either controller to reach the terminal over-current level within 10  $\mu$ s.

Soft start helps prevent current spikes at turn-on and allows separate supplies to be delayed using external programmability.

### Synchronous Rectifiers

Synchronous rectification replaces the Schottky rectifier with a MOSFET, which can be controlled to increase the efficiency of the circuit.

When the high-side MOSFET is switched off, the inductor will try to maintain its current flow, inverting the inductor's polarity. The path of current then becomes the circuit made of the Schottky diode, inductor and load, which will charge the output capacitor. The diode has a 0.5-V forward voltage drop, which contributes a significant amount of power loss, decreasing efficiency. A low-side switch is placed in parallel with the Schottky diode and is turned on just after the diode begins to conduct. Because the  $r_{DS(ON)}$  of the MOSFET is low, the I\*R voltage drop will not be as large as the diode, which increases efficiency.

The low-side rectifier is shut off when the inductor current drops to zero.

Document Number: 70190 S-40805—Rev. F, 26-Apr-04 Shoot-through current is the result when both the high-side and rectifying MOSFETs are turned on at the same time. Break-before-make timing internal to the Si9130 manages this potential problem. During the time when neither MOSFET is on, the Schottky is conducting, so that the body diode in the low-side MOSFET is not forced to conduct.

Synchronous rectification is always active when the Si9130 is powered-up, regardless of the operational mode.

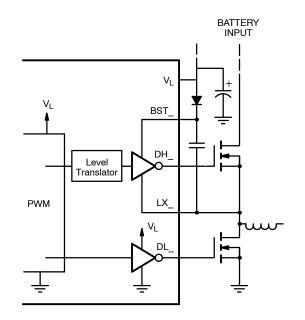

### **Gate-Driver Boost**

The high-side n-channel drive is supplied by a flying-capacitor boost circuit (see Figure 4). The capacitor takes a charge from  $V_L$  and then is connected from gate to source of the high-side MOSFET to provide gate enhancement. At power-up, the low-side MOSFET pulls LX\_ down to GND and charges the BST\_ capacitor connected to 5 V. During the second half of the oscillator cycle, the controller drives the gate of the high-side MOSFET by internally connecting node BST\_ to DH\_. This supplies a voltage 5 V higher than the battery voltage to the gate of the high-side MOSFET.

Oscillations on the gates of the high-side MOSFET in discontinuous mode are a natural occurrence caused by the LC network formed by the inductor and stray capacitance at the LX\_pins. The negative side of the BST\_capacitor is connected to the LX\_node, so ringing at the inductor is translated through to the gate drive.

FIGURE 4. Boost Supply for Gate Drivers

## OPERATIONAL MODES

### **PWM Mode**

The 3.3-V and 5-V Buck controllers operate in continuous-current PWM mode when the load demands more than approximately 25% of the maximum current (see typical curves). The duty cycle can be approximated as Duty\_Cycle =  $V_{OUT}/V_{IN}$ .

In this mode, the inductor current is continuous; in the first half of the cycle, the current slopes up when the high-side MOSFET conducts and then, in the second half, slopes back down when the inductor is providing energy to the output capacitor and load. As current enters the inductor in the first half-cycle, it is also continuing through to the load; hence, the load is receiving continuous current from the inductor. By using this method, output ripple is minimized and smaller form-factor inductors can be used. The output capacitor's ESR has the largest effect on output ripple. It is typically under 50mV; the worst case condition is under light load with higher input battery voltage.

### **Pulse-Skipping Mode**

When the load requires less than 25% of its maximum, the Si9130 enters a mode which drives the gate for one clock cycle and skips the majority of the remaining cycles. Pulse-skipping mode cuts down on the switching losses, the dominant power consumer at low current levels.

In the region between pulse-skipping mode and PWM mode, the controller may transition between the two modes, delivering spurts of pulses. This may cause the current waveform to look irregular, but will not overly affect the ripple voltage. Even in this transitioning mode efficiency will stay high.

### **Current Limit**

The current through an external resistor, is constantly monitored to protect against over-current. A low value resistor is placed in series with the inductor. The voltage across it is measured by connecting it between CS\_ and FB\_. If this voltage is larger than 100 mV, the high-side MOSFET drive is shut down. Eliminating over-currents protects the MOSFET, the load and the power source. Typical values for the sense resistors with a 3-A load will be 25 m $\Omega$ .

### **Oscillator and SYNC**

There are two ways to set the Si9130 oscillator frequency: by using an external SYNC signal, or using the internal oscillator.

www.vishay.com

The SYNC pin can be driven with an external CMOS level signal with frequency from 240 kHz and 350 kHz to synchronize to the internal oscillator. Tying SYNC to either  $V_L$  or GND sets the frequency to 200 kHz and to REF sets the frequency to 300 kHz.

Operation at 300 kHz is typically used to minimize output passive component sizes. Slower switching speeds of 200 kHz may be needed for lower input voltages.

Internal V<sub>L</sub> and REF

A 5-V linear regulator supplies power to the internal logic circuitry. The regulator is available for external use from pin V<sub>L</sub>, able to source 5 mA. A 4.7- $\mu$ F capacitor should be connected between V<sub>L</sub> and GND. To increase efficiency, when the 5-V switching supply has voltage greater than 4.5 V, V<sub>L</sub> is internally switched over to the output of the 5-V switching supply and the linear regulator is turned off.

The 5-V linear regulator provides power to the internal 3.3-V bandgap reference (REF). The 3.3-V reference can supply 5 mA to an external load, connected to pin REF. Between REF and GND connect a capacitor, 0.22  $\mu F$  plus 1  $\mu F$  per mA of load current. The switching outputs will vary with the reference; therefore, placing a load on the REF pin will cause the main outputs to decrease slightly, within the specified regulation tolerance.

$V_L$  and REF supplies stay on as long as V+ is greater than 4.5 V, even if the switching supplies are not enabled. This feature is necessary when using the micropower regulators to keep memory alive during shutdown.

Both linear regulators can be connected to their respective switching supply outputs. For example, REF would be tied to the output of the 3.3 V and V<sub>L</sub> to 5 V. This will keep the main supplies up in standby mode, provided that each load current in shutdown is not larger than 5 mA.

#### **Fault Protection**

The 3.3-V and 5-V switching controllers are shut down when one of the linear regulators drops below 85% of its nominal value; that is, shut down will occur when V<sub>L</sub> < 4.0 V or REF < 2.8 V.

## **DESIGN CONSIDERATIONS**

#### Inductor Design

Three specifications are required for inductor design: inductance (L), peak inductor current ( $I_{LPEAK}$ ), and coil resistance ( $R_L$ ). The equation for computing inductance is:

$$L = \frac{(V_{OUT})(V_{IN(MAX)} - V_{OUT})}{(V_{IN(MAX)})(f)(I_{OUT})(LIR)}$$

$\begin{array}{lll} \mbox{Where:} & V_{OUT} = \mbox{Output} \mbox{ voltage } (3.3 \mbox{ V or 5 } V); \\ V_{IN(MAX)} = \mbox{Maximum input} \mbox{ voltage } (V); \\ f = & \mbox{Switching frequency, normally} \\ & 300 \mbox{ kHz}; \\ I_{OUT} = \mbox{Maximum dc load current } (A); \\ & \mbox{LIR} = \mbox{Ratio of inductor pea-to-peak ac current to} \\ & \mbox{average dc load current, typically } 0.3. \end{array}$

When LIR is higher, smaller inductance values are acceptable, at the expense of increased ripple and higher losses.

The peak inductor current ( $I_{LPEAK}$ ) is equal to the steady-state load current ( $I_{OUT}$ ) plus one half of the peak-to-peak ac current ( $I_{LPP}$ ). Typically, a designer will select the ac inductor current to be 30% of the steady-state current, which gives  $I_{LPEAK}$  equal to 1.15 times  $I_{OUT}$ .

The equation for computing peak inductor current is:

$$I_{\text{LPEAK}} = I_{\text{OUT}} + \frac{\left(V_{\text{OUT}}\right) \left(V_{\text{IN}(\text{MAX})} - V_{\text{OUT}}\right)}{(2)(f)(L) \left(V_{\text{IN}(\text{MAX})}\right)}$$

## OUTPUT CAPACITORS

The output capacitors determine loop stability and ripple voltage at the output. In order to maintain stability, minimum capacitance and maximum ESR requirements must be met according to the following equations:

Document Number: 70190 S-40805—Rev. F, 26-Apr-04

$$C_{F} > \frac{V_{REF}}{(V_{OUT})(R_{CS})(2)(\pi)(GPWP)}$$

and,

$$\mathsf{ESR}_{\mathsf{CF}} < \frac{\left(\mathsf{V}_{\mathsf{OUT}}\right)\!\!\left(\mathsf{R}_{\mathsf{CS}}\right)}{\mathsf{V}_{\mathsf{REF}}}$$

$\begin{array}{ll} \mbox{Where:} & C_{F} = \mbox{Output filter capacitance (F)} \\ & V_{REF} = \mbox{Reference voltage, } 3.3 \ V; \\ & V_{OUT} = \mbox{Output voltage, } 3.3 \ V \ or \ 5 \ V; \\ & R_{CS} = \mbox{Sense resistor } (\Omega); \\ & GBWP = \mbox{Gain-bandwidth product, } 60 \ \mbox{kHz}; \\ & ESR_{CF} = \mbox{Output filter capacitor ESR } (\Omega). \end{array}$

Both minimum capacitance and maximum ESR requirements must be met. In order to get the low ESR, a capacitance value two to three times greater than the required minimum may be necessary.

The equation for output ripple in continuous current mode is:

$$V_{OUT(RPL)} = I_{LPP(MAX)} \times \left( ESR_{CF} + \frac{1}{(2 \times f \times CF)} \right)$$

The equations for capacitive and resistive components of the ripple in pulse-skipping mode are:

$$V_{OUT(RPL)}(C) =$$

$$\frac{(4)(10^{-4})(L)}{(R_{CS}^{2})(C_{F})} \times \left(\frac{1}{V_{OUT}} + \frac{1}{V_{IN} - V_{OUT}}\right) \text{Volts}$$

$$V_{OUT(RPL)}(R) = \frac{(0.02)(ESR_{CF})}{R_{CS}}$$

Volts

The total ripple,  $V_{\text{OUT}(\text{RPL})}$  , can be approximated as follows:

$$\begin{array}{ll} & \text{if} & V_{OUT(\text{RPL})}(R) < 0.5 \; V_{OUT(\text{RPL})}(C), \\ & \text{then} & V_{OUT(\text{RPL})} = V_{OUT(\text{RPL})}(C), \\ & \text{otherwise,} & V_{OUT(\text{RPL})} = V_{OUT(\text{RPL})}(C) + \\ & V_{OUT(\text{RPL})}(R). \end{array}$$

#### Lower Voltage Input

The application circuit shown here can be easily modified to work with 5.5-V to 12-V input voltages. Oscillation frequency should be set at 200 kHz and increase the output capacitance to 660  $\mu F$  on the 5-V output to maintain stable performance up to 2 A of load current. Operation on the 3.3-V supply will not be affected by this reduced input voltage.

Vishay

# Disclaimer

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.