## LM2650

# Synchronous Step-Down DC/DC Converter

## **General Description**

The LM2650 is a step-down DC/DC converter featuring high efficiency over a 3A to milliamperes load range. This feature makes the LM2650 an ideal fit in battery-powered applications that demand long battery life in both run and standby modes.

The LM2650 also features a logic-controlled shutdown mode in which it draws at most 25µA from the input power supply.

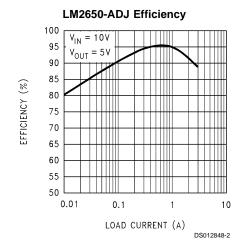

The LM2650 employs a fixed-frequency pulse-width modulation (PWM) and synchronous rectification to achieve very high efficiencies. In many applications, efficiencies reach 95%+ for loads around 1A and exceed 90% for moderate to heavy loads from 0.2A to 2A.

A low-power hysteretic or "sleep" mode keeps efficiencies high at light loads. The LM2650 enters and exits sleep mode automatically as the load crosses "sleep in" and "sleep out" thresholds. The LM2650 provides nodes for programming both thresholds via external resistors. A logic input allows the user to override the automatic sleep feature and keep the LM2650 in PWM mode regardless of the load level.

An optional soft-start feature limits current surges from the input power supply at start up and provides a simple means of sequencing multiple power supplies.

### **Features**

- Ultra high efficiencies (95% possible)

- High efficiency over a 3A to milliamperes load range

- Synchronous switching of internal NMOS power FETs

- Wide input voltage range (4.5V to 18V)

- Output voltage adjustable from 1.5V to 16V

- Automatic low-power sleep mode

- Logic-controlled micropower shutdown ( $I_{QSD} \le 25 \mu A$ )

- Frequency adjustable up to 300 kHz

- Frequency synchronization with external signal

- Programmable soft-start

- Short-circuit current limiting

- Thermal shutdown

- Available in 24-lead Small-Outline package

## **Applications**

- Notebook and palmtop personal computers

- Portable data terminals

- Modems

- Portable Instruments

- Global positioning devices (GPSs)

- Battery-powered digital devices

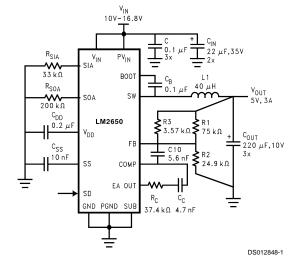

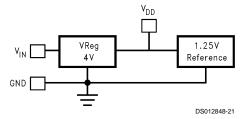

## **Typical Application**

Converting a Four-Cell Li Ion Battery to 5V

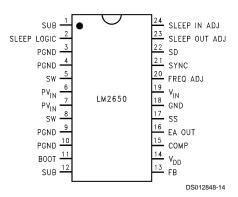

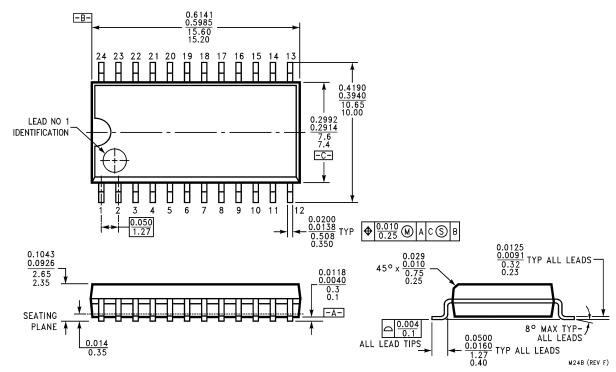

# **Connection Diagram**

Top View 24-Lead Small Outline Package (M) Order Number LM2650M-ADJ See Package Number M24B

# Pin Descriptions (Refer to the Block Diagrams)

| Pins        | Description                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1, 12       | SUB: These pins make electrical contact with the substrate of the die. Ground them. For best thermal                                                                                                                                                                                                                                 |  |  |  |  |

|             | performance, ground them to the same large, uninterrupted copper plane as the PGND pins.                                                                                                                                                                                                                                             |  |  |  |  |

| 2           | <b>SLEEP LOGIC</b> : Use this logic input to select the conversion mode; low selects PWM, high selects sleep, and high impedance (open) permits the LM2650 to move freely and automatically between the modes, using PWM for moderate to heavy loads and sleep for light loads.                                                      |  |  |  |  |

| 3, 4, 9, 10 | <b>PGND</b> : The ground return of the power stage. The power stage consists of the two power switches Q1 and Q2, the gate drivers DH and DL, and the linear voltage regulators VRegH and VRegL. For best electrical and thermal performance, ground these pins to a large, uninterrupted copper plane.                              |  |  |  |  |

| 5, 8        | <b>SW</b> : The output node of the power stage. It swings from slightly below ground to slightly below the voltage to PV <sub>IN</sub> . To minimize the effects of switching noise on nearby circuitry, keep all traces originating from SW short and to the point. Route all traces carrying signals well away from the SW traces. |  |  |  |  |

| 6, 7        | <b>PV<sub>IN</sub></b> : The positive supply rail of the power stage. Bypass each PV <sub>IN</sub> pin to PGND with a 0.1 μF capacitor. Use capacitors having low ESL and low ESR, and locate them close to the IC.                                                                                                                  |  |  |  |  |

| 11          | BOOT: The positive supply rail of the high-side gate driver DH. Connect a 0.1 μF capacitor from this node to SW. Bootstrapping action creates a supply rail about 9V above that at PV <sub>IN</sub> , and DH uses this rail to override the gate of the NMOS power FET Q1. Overriding ensures low R <sub>DS(on)</sub> .              |  |  |  |  |

| 13          | FB: The feedback input.                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 14          | $V_{DD}$ : An internal regulator steps the input voltage down to a 4V rail used by the signal-level circuitry. $V_{DD}$ is the output node of this regulator. Bypass $V_{DD}$ to GND close to the IC with a 0.2 $\mu$ F capacitor.                                                                                                   |  |  |  |  |

| 15          | COMP: The inverting input of the error amplifier EA.                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 16          | EA OUT: The output node of the error amplifier EA.                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 17          | SS: The soft start node. Connect a capacitor from SS to GND.                                                                                                                                                                                                                                                                         |  |  |  |  |

| 18          | GND: The ground return of the signal-level circuitry.                                                                                                                                                                                                                                                                                |  |  |  |  |

| 19          | $V_{IN}$ : The positive supply rail of the internal 4V regulator. Bypass $V_{IN}$ to GND close to the IC with a 0.1 $\mu$ F capacitor.                                                                                                                                                                                               |  |  |  |  |

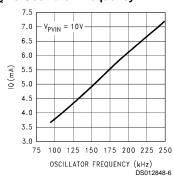

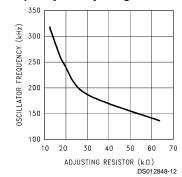

| 20          | <b>FREQ ADJ</b> : The LM2650 switches at a nominal 90 kHz. Connect a resistor between FREQ ADJ and GND to adjust the frequency up from the nominal. Use the graph under Typical performance Characteristics to select the resistor.                                                                                                  |  |  |  |  |

| 21          | <b>SYNC</b> : The synchronization input. If the switching frequency is to be synchronized with an external clock signal, apply the clock signal here. Ground if not used.                                                                                                                                                            |  |  |  |  |

| 22          | SD: Use this logic input to control shutdown; pull low for operation, high for shutdown.                                                                                                                                                                                                                                             |  |  |  |  |

| 23          | SLEEP OUT ADJ (SOA): The value of the resistor connected between SIA and ground programs the sleep-in threshold. Higher values program lower thresholds.                                                                                                                                                                             |  |  |  |  |

| 24          | SLEEP IN ADJ (SIA): The value of the resistor connected between SIA and ground programs the sleep-in threshold. Higher values program lower thresholds.                                                                                                                                                                              |  |  |  |  |

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

(All voltages are referenced to the PGND and GND pins.) DC Voltage at  $PV_{IN}$  and  $V_{IN}$  20V DC Voltage at SD, SLEEP LOGIC

and SYNC 15V

DC current into SW ±7.5A

Junction Temperature Limited by the IC DC Power Dissipation (Note 2) 1.28W

Storage Temperature -65°C to +150°C

Soldering Time, Temperature (Note

## **Operating Ratings** (Note 1)

Supply Voltage Range (PV $_{\rm IN}$  and

$V_{IN}$ ) 4.5V to 18V Junction Temperature Range  $-40^{\circ}$ C to  $+125^{\circ}$ C

## **Electrical Characteristics**

$V_{PVIN}$  = 15V,  $V_{SLEEP\ LOGIC}$  = 0V and  $V_{SD}$  = 0V unless superseded under **Conditions**. Typicals and limits appearing in plain type apply for  $T_A$  =  $T_J$  = +25°C. Limits appearing in **boldface** type apply over the full junction temperature range shown under **Operating Ratings**.

| Symbol                                                         | Parameter                                                                                               | Conditions                                                                                                                                   | Typ (Note 5) | Limit (Note 6)                             | Units                          |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------|--------------------------------|

| V <sub>OUT</sub>                                               | Output Voltage                                                                                          | R1 = 75 k $\Omega$ , 1%,<br>R2 = 25 k $\Omega$ , 1%,<br>7.5V $\leq$ V <sub>PVIN</sub> $\leq$ 18V<br>0.12A $\leq$ I <sub>LOAD</sub> $\leq$ 3A | 5.00         | 4.80/ <b>4.75</b><br>5.20/ <b>5.25</b>     | V<br>V(min)<br>V(max)          |

| η1                                                             | System Efficiency                                                                                       | $I_{LOAD} = 1A, T_A = 25^{\circ}C,$<br>$F_{OSC}$ Not Adjusted                                                                                | 94           |                                            | %                              |

| η2                                                             | System Efficiency                                                                                       | $I_{LOAD} = 3A, T_A = 25^{\circ}C,$<br>$F_{OSC}$ Not Adjusted                                                                                | 89           |                                            | %                              |

| $V_{REF}$                                                      | Reference Voltage                                                                                       | V <sub>SLEEPLOGIC</sub> = 3V (Note 7)                                                                                                        | 1.25         | 1.281/ <b>1.294</b><br>1.219/ <b>1.206</b> | V(min)<br>V(max)               |

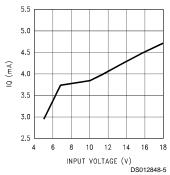

| I <sub>Q</sub>                                                 | Quiescent Current in PWM mode                                                                           | $V_{FB} = V_{REF}$ -20mV (Note 8)                                                                                                            | 4.0          | 6.50/ <b>7.0</b>                           | mA<br>mA(max)                  |

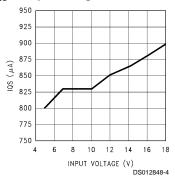

| I <sub>QS</sub>                                                | Quiescent Current in Sleep mode                                                                         | IV <sub>FB</sub> = V <sub>REF</sub> -20mV,<br>V <sub>SLEEPLOGIC</sub> = 3V (Note 8)                                                          | 850          | 1.35/ <b>1.60</b>                          | μA<br>mA(max)                  |

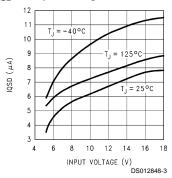

| I <sub>QSD</sub>                                               | Quiescent Current in Shutdown mode                                                                      | V <sub>SD</sub> = 3V<br>(Note 8)                                                                                                             | 9            | 20/ <b>25</b>                              | μΑ<br>μΑ(max)                  |

| R <sub>DS(on)</sub> HS                                         | DC On-Resistance Drain-to-Source of the High-Side Power Switch                                          | $I_{DS} = 1A,$ $V_{SLEEPLOGIC} = 3V,$ $V_{FB} = 3V,$ $V_{BOOT} = 24V$                                                                        | 130          | 170/ <b>245</b>                            | m $\Omega$<br>m $\Omega$ (max) |

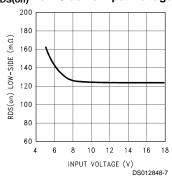

| R <sub>DS(on)</sub> LS                                         | DC On-Resistance Drain-to-Source of the Low-Side Power Switch                                           | I <sub>DS</sub> = 1A,<br>V <sub>FB</sub> = 3V                                                                                                | 125          | 175/ <b>245</b>                            | mΩ<br>mΩ(max)                  |

| I <sub>L HS</sub>                                              | Leakage current of the<br>High-Side Power Switch                                                        | $V_{PVIN} = 18V, V_{SW} = 0V,$<br>$V_{SD} = 3V$                                                                                              | 100          | 10                                         | nA<br>μA(max)                  |

| I <sub>L LS</sub> Leakage current of the Low-Side Power Switch |                                                                                                         | $V_{PVIN} = 18V, V_{SW} = 18V,$<br>$V_{SD} = 3V$                                                                                             | 95           | 210                                        | μΑ<br>μΑ(max)                  |

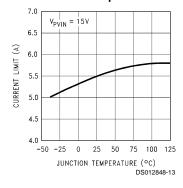

| I <sub>LIMIT</sub>                                             | Active Current Limit of the High-Side Power Switch                                                      | $V_{PVIN} = 15V,$ $V_{BOOT} = 24V,$ $V_{FB} = 3V,$ $V_{SLEEPLOGIC} = 3V,$                                                                    | 5.5          | 3.5<br>7.5                                 | A<br>A(min)<br>A(max)          |

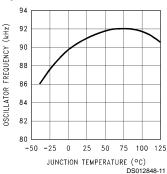

| F <sub>osc</sub>                                               | Oscillator Frequency                                                                                    | $V_{FB} = V_{REF} - 20 \text{ mV}$                                                                                                           | 90           | 80/ <b>75</b><br>100/ <b>105</b>           | kHz<br>kHz(min)<br>kHz(max)    |

| F <sub>MAX</sub>                                               | Maximum Oscillator Frequency $I_{FREQ ADJ} = 100 \mu A, (Note 9)$<br>$V_{FB} = V_{REF} - 20 \text{ mV}$ |                                                                                                                                              | 315          | 270/ <b>260</b><br>360/ <b>370</b>         | kHz<br>kHz(min)<br>kHz(max)    |

| D <sub>MAX</sub>                                               | Maximum Duty Cycle                                                                                      | $V_{FB} = V_{REF} - 20 \text{ mV},$<br>$F_{OSC}$ Not Adjusted                                                                                | 97           | 94/ <b>93</b>                              | %<br>%(min)                    |

### **Electrical Characteristics** (Continued)

$V_{PVIN}$  = 15V,  $V_{SLEEP\ LOGIC}$  = 0V and  $V_{SD}$  = 0V unless superseded under **Conditions**. Typicals and limits appearing in plain type apply for  $T_A$  =  $T_J$  = +25°C. Limits appearing in **boldface** type apply over the full junction temperature range shown under **Operating Ratings**.

| Symbol            | Parameter                           | Conditions                         | Typ (Note 5) | Limit (Note 6)    | Units   |

|-------------------|-------------------------------------|------------------------------------|--------------|-------------------|---------|

| D <sub>MIN</sub>  | Minimum Duty Cycle                  | $V_{FB} = V_{REF} +50 \text{ mV},$ | 2.8          |                   | %       |

|                   |                                     | F <sub>OSC</sub> Not Adjusted      |              | 5                 | %(min)  |

| $V_{DD}$          | Internal Rail Voltage               | I <sub>VDD</sub> = 1 mA            | 4.0          |                   | V       |

|                   |                                     |                                    |              | 3.6/ <b>3.4</b>   | V(min)  |

|                   |                                     |                                    |              | 4.2/ <b>4.3</b>   | V(max)  |

| $V_{BOOT}$        | Bootstrap Regulator Voltage         | I <sub>BOOT</sub> = 1 mA           | 7.5          |                   | V       |

|                   | (VRegH)                             |                                    |              | 6.5/ <b>6.0</b>   | V(min)  |

| I <sub>SS</sub>   | Soft Start Current                  |                                    | 10           |                   | μA      |

|                   |                                     |                                    |              | 13.5/ <b>20.0</b> | μA(max) |

| V <sub>HYST</sub> | Hysteresis of the Sleep             | V <sub>SLEEPLOGIC</sub> = 3V       | 30           |                   | mV      |

|                   | Comparator (C2Figure 2)             |                                    |              | 10                | mV(min) |

|                   |                                     |                                    |              | 50                | mV(max) |

|                   | V <sub>IL</sub> of SD               |                                    |              | 0.95              | V(max)  |

|                   | V <sub>IH</sub> of SD               |                                    |              | 2.10              | V(min)  |

|                   | V <sub>IL</sub> of SLEEP LOGIC      |                                    |              | 0.9               | V(max)  |

|                   | V <sub>IH</sub> of SLEEP LOGIC      |                                    |              | 2.0               | V(min)  |

|                   | V <sub>IL</sub> of SYNC             |                                    |              | 0.50              | V(max)  |

|                   | V <sub>IH</sub> of SYNC             |                                    |              | 1.45              | V(min)  |

| T <sub>SD</sub>   | T <sub>J</sub> for Thermal Shutdown |                                    | 170          |                   | °C      |

**Note 1:** Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which the device operates correctly. Operating ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics.

Note 2: This rating is calculated using the formula  $P_{DCmax} = (T_{Jmax} - T_A) / \theta_{JA}$ , where  $P_{DCmax}$  is the absolute maximum power dissipation,  $T_{Jmax}$  is the maximum junction temperature, and  $\theta_{JA}$  is the junction of ambient thermal resistance of the package. The  $P_{DCmax}$  rating of 1.28W results from substituting 170°C, 70°C and 78°C/W for  $T_{Jmax}$ ,  $T_A$  and  $\theta_{JA}$  respectively. A  $\theta_{JA}$  of 78°C represents the worst condition of no heat sinking of the M24B small-outline package. Heat sinking allows the safe dissipation of more power. See Application Notes on thermal management. The LM2650 actively limits its junction temperature to about 170°C.

Note 3: For detailed information on soldering plastic small-outline packages, refer to the Packaging Databook published by National Semiconductor Corporation.

Note 4: ESD is applied using the human-body model, a 100pF capacitor discharged through a 1.5k $\Omega$  resistor.

Note 5: A typical is the center of characterization data taken at  $T_A = T_J = 25$  °C.

Note 6: All limits are guaranteed. The guarantee is backed with 100% testing at T<sub>A</sub> = T<sub>J</sub> = 125°C and statistical correlation for room temperature and cold limits.

Note 7:  $V_{REF}$  is measured at SLEEP OUT ADJ.

Note 8: Quiescent current is the total current flowing into the P<sub>VIN</sub> and V<sub>IN</sub> pins. I<sub>Q</sub> includes the current used to drive the gates of the two NMOS power FETs at the nominal switching frequency. I<sub>OS</sub> includes no such current.

Note 9: Pulling 100μA out of FREQ ADJ simulates adjusting the oscillator frequency with a 12.5 kΩ resistor connected from FREQ ADJ to GND. The sleep mode cannot be used at switching frequencies above 250 kHz.

# **Typical Performance Characteristics**

## I<sub>QSD</sub> vs Input Voltage

### I<sub>QS</sub> vs Input Voltage

### I<sub>Q</sub> vs Input Voltage

### Io vs Oscillator Frequency

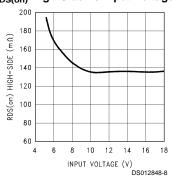

R<sub>DS(on)</sub> Low-Side vs Input Voltage

R<sub>DS(on)</sub> High-Side vs Input Voltage

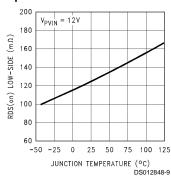

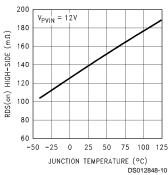

# $R_{DS(on)}$ Low-Side vs Junction Temperature

R<sub>DS(on)</sub> High-Side vs Junction Temperature

Oscillator Frequency vs Junction Temperature

### Oscillator Frequency vs Adjusting Resistor

## **Current Limit vs Junction Temperature**

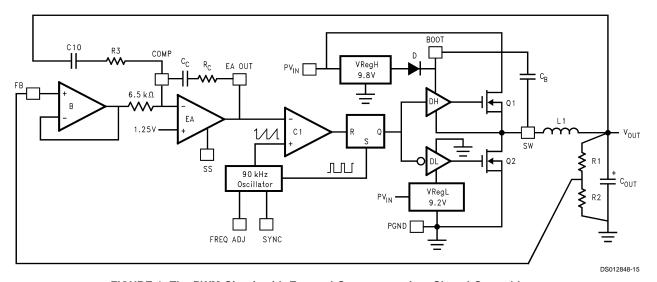

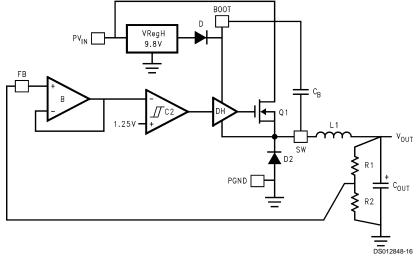

# **Block Diagrams**

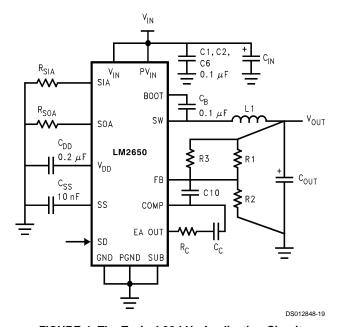

FIGURE 1. The PWM Circuit with External Components in a Closed Control Loop

FIGURE 2. The Hysteretic or "Sleep" Circuit with External Components in a Closed Control Loop

FIGURE 3. The Internal Voltage Regulator and Voltage Reference used by Both the PWM and Hysteretic Circuits

## **Operation**

#### **OVERVIEW**

The LM2650 uses two step-down conversion modes: fixed-frquency pulse-width modulation (PWM) and hysteretic. It moves freely and automatically between them, using PWM for moderate to heavy loads and hysteretic for light loads.

For clarity, separate block diagrams for each conversion mode have been included. See *Figure 1* and *Figure 2*. Blocks used in both modes appear in both diagrams with the same label. For example, both modes use the input buffer B. To keep the diagrams simple, most power supply rails have been omitted. R3, C10, R $_{\rm C}$ , C $_{\rm C}$ , C $_{\rm B}$ , L1, R1, R2, and C $_{\rm OUT}$  are outside the IC.

### THE PWM CIRCUIT (Figure 1)

The PWM is a fixed-frequency, voltage-mode pulse-width modulator. It consists of four functional blocks: an input buffer, an error amplifier, a modulator, and a power stage.

- The input buffer B: B is a voltage follower. A fraction of the output voltage is fed back to its noninverting input FB. Circumventing B by using the COMP input as the feedback input will cause the IC to malfunction.

- 2. The error amplifier EA: EA is a voltage amplifier. It subtracts the feedback voltage from the 1.25V reference and amplifies the difference to produce an error voltage for the control loop. For the purpose of loop compensation, EA is typically configured as an integrator. In this configuration, a capacitor C<sub>C</sub> and a resistor R<sub>C</sub> are connected in series between the inverting input COMP and the output terminal EA OUT. The capacitor and the internal 6.5kΩ resistor create a pole, while the capacitor and series resistor create a zero.

- The modulator: The modulator is the heart of the PWM circuit. It consists of the 90 kHz oscillator, the voltage comparator C1, and output logic represented here as a simple SR latch.

The modulator generates a continuous stream of rectangular, signal-level. It generates the pulses at a fixed frequency, and it modulates or varies their widths in response to variations in the error voltage. The pulses appear at Q, the output of the SR latch. An increase in the error voltage results in a proportional increase in the pulse widths, and, conversely, a decrease in the error voltage results in a proportional decrease in the pulse widths.

The oscillator produces a 90 kHz sawtooth that ramps between 1V and 2V. At the beginning of each ramp, the oscillator sets the SR latch sending Q high. As the ramp voltage surpasses the error voltage, C1 resets the SR latch sending Q low. An increase in the error voltage increases the time between the setting and the resetting of the SR latch which , in turn, results in an equal increase in pulse widths: that is, an equal increase in the time Q spends high in each cycle. A decrease in the error voltage has the opposite effect on the pulse widths as it decreases the time between the setting and resetting of the SR latch.

4. The power stage: The power stage puts some punch between the output of the modulator by translating the stream of signal-level pulses generated by the modulator into a stream of power pulses that swing from ground up to the input voltage while sinking and sourcing as much as 3.5A. The power stage consists of two gate drivers DH and DL, two linear voltage regulators VRegH and VRegL, and two NMOS power FETs Q1 and Q2.

The power pulses appear at the SW mode. When Q goes high, DL drives the gate of Q2 low turning Q23 off. While Q2 turns off, the SW potential may remain at just below ground as the body diode of Q2 conducts what was previously reverse current (source-to-drain) in Q2, or the SW potential may swing up to just above the input voltage as the body diode of Q1 conducts what was previously forward current (drain-to-source) in Q2. About 50 ns after Q goes high, DH drives the gate of Q1 high turning Q1 on. If the task remains, Q1 pulls the SW potential up, if not, Q1 simply takes over the conduction responsibility from its own body diode. When Q goes low, the inverse action occurs resulting in the SW potential swinging from the input voltage to the ground. The 50 ns delay between one switch beginning to turn off and the other switch beginning to turn on prevents the switches from "shooting through" directly from the input supply to the ground.

The PWM circuit drives the pulse stream into the low-pass filter made up of L1 and  $C_{\rm OUT}$ . The filter passed the DC component of the stream and attenuates the AC components. The output of the filter is the DC voltage  $V_{\rm OUT}$  superimposed with a small ripple voltage. Since the DC component of any periodic waveforms the average value of the waveform,  $V_{\rm OUT}$  can be found using:

$$V_{OUT} = \frac{1}{T} \times \int_0^T v(t) dt.$$

(1)

Here T is the switching period in seconds V(t) is the pulse stream. Under DC steady-state conditions, (1) yields

$$V_{OUT} = V_{IN} \times \frac{t_{ON}}{T} = V_{IN} \times D.$$

(2)

Here  $V_{\rm IN}$  is the input voltage, and therefore the height of the pulses, in volts, is the width of the pulses in seconds, and D is the ratio of  $t_{\rm ON}$  to T, the duty or the duty cycle.

The output voltage is programmed using the resistive divider made up for R1 and R2,

$$V_{OUT} = 1.25 \times (1 + \frac{R1}{R2}).$$

(3)

As Q1 turns on, its source voltage swings up to just below the input voltage. The LM2650 uses a simple technique called "bootstrapping" to pull the positive supply rail of DH (at BOOT) up along with the source voltage of Q1, but to a voltage above the input voltage. Because the source of Q1 and the positive supply rail of DH make the same voltage swing together, DH maintains the positive gate-to-source voltage required to turn Q1 on. Q12 plays an active role in pulling the supply rail of DH up and is therefore said to pull itself up by its "bootstraps", thus the name of the technique and of the BOOT pin.

In the typical application, a capacitor CB is connected outside the IC between the BOOT and SW pins. When Q2 is on, the input supply charges CB through VRegH and the internal diode D.

### THE HYSTERETIC CIRCUIT AND LOOP (Figure 2)

Except for C2, the hysteretic circuit borrows all its circuit blocks from the PWM circuit.

The hysteretic comparator C2 is a voltage comparator with built-in hysteresis  $V_{\rm HYST}$  of typically 30mV centered at 1.25V.

## **Operation** (Continued)

The diode D2 is the body diode of Q2. The hysteretic circuit uses D2 as a rectifier instead of switching Q2 as a synchronous rectifier.

When the load current drops below the prescribed sleep-in threshold, the LM2650 shuts down the PWM loop and starts up the hysteretic loop. The hysteretic loop supports light loads more efficiently because it uses less power to support its own operation; it uses less bias power because it's a simpler loop having less circuit blocks to bias, and it switches slower, so it incurs lower switching losses.

The hysteretic control loop does not switch at a constant frequency. Instead, it monitors  $V_{OUT}$  and switches only when  $V_{OUT}$  reaches either side of a narrow window centered on the desired output voltage. C2 directs the switching based on its reading of the feedback voltage. Switching in this manner yields a regulated voltage consisting of the desired output voltage and an AC ripple voltage. The magnitude of the AC component can be approximated using

$$V_{OUT\_PP} = V_{HYST} \times \frac{(R1 + R2)}{R2}.$$

(4)

For example, with  $V_{OUT}$  set to 5V,  $V_{OUT\_PP}$  is approximately 120mV.

$$V_{OUT\_PP} = 0.03 \times \frac{(75 + 24.9)}{24.9} = 120 \text{ mV}.$$

(5)

When it starts up, the hysteretic loop turns Q1 on. While Q1 is on, the input power supply charges  $C_{\mathsf{OUT}}$  and supplies current to the load. Current from the supply reaches C and the load via the series path provided by Q1 and L1. As the feedback voltage just surpasses the upper hysteretic threshold of C2, the output of C2 changes from high to low, and HD responds by pulling the gate of Q1 down turning Q1 off. As Q1 turns off, L1 generates a negative-going voltage transient that D2 clamps at just below ground. D2 remains on only briefly as the current in L1 runs out. While both Q1 and D2 are off,  $C_{\mathsf{OUT}}$  alone supplies current to the load. As the

feedback voltage just surpasses the lower hysteretic threshold of C2, the output of C2 changes states from low to high, and DH responds by pulling the gate of Q1 up turning Q1 on and starting the hysteretic cycle over.

Note that as the load current decreases, it takes increasingly longer periods for the load current to discharge  $C_{\text{OUT}}$  through the hysteretic window, and as the load current increases, the periods become even shorter. It can be seen from the above observation that the switching frequency of the hysteretic loop varies as the load varies. The switching frequency can be approximated using

$$f = \frac{I}{(C_{OUT} \times V_{OUT\_PP})}.$$

(6)

Here f is the switching frequency in hertz, I is the load current in amperes,  $C_{OUT}$  is the value of the capacitor in farads, and  $V_{OUT\_PP}$  is the magnitude of the AC ripple voltage in volts. Typical switching frequencies range anywhere from a few hertz for very light loads to a few thousand hertz for light loads bordering on the moderate level.

## **Application Circuits**

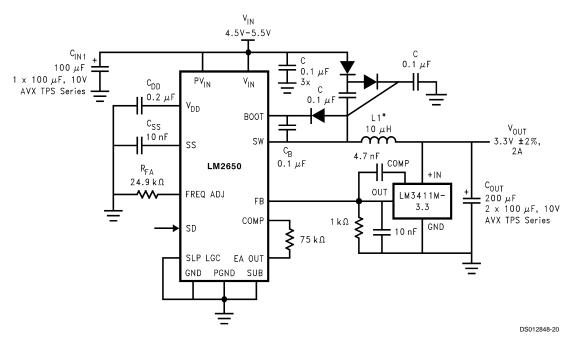

Figure 4 is a schematic of the typical application circuit. use the component values shown in the figure and those contained in *Table 1* to build a 5V, 3A, or 3.3V, 3A step-down DC/DC converter. As with the design of any DC/DC converter, the design of these circuits involved tradeoffs between efficiency, size, and cost. Here more weight was given to efficiency than to size as evidenced by the low switching frequency which keeps switching losses low but pushes the value and size of the inductor up.

From a smaller circuit, use the component values shown in Figure 4 and those contained in Table 3. These circuits trade slightly higher switching losses for a much smaller inductor. Note, Figure 4 does not show  $R_{\rm FA}$ , the resistor required to adjust the switching frequency from 90 kHz up to 200 kHz. Connect  $R_{\rm FA}$  between the FREQ ADJ pin and ground.

FIGURE 4. The Typical 90 kHz Application Circuit

# Application Circuits (Continued)

TABLE 1. Components for the Typical 90 kHz Application Circuit

| Input Voltage                                                | 7V to 18V IN  8 to 12 Cell NiCd or NiMh, 3 to 4 Cell Li Ion, 8 to 11 Cell Alkaline, 6 Cell Lead Acid                         |                                                                                                                   |  |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|

| Applicable Cell Stacks                                       |                                                                                                                              |                                                                                                                   |  |

| Output                                                       | 5V, 3A Out                                                                                                                   | 3.3V, 3A out                                                                                                      |  |

| Input Capacitor C <sub>IN</sub>                              | 2 x 22 μF, 35V AVX TPS<br>Series or Sprague 593D Series                                                                      | 2 x 22 µF, 35V AVX TPS<br>Series or Sprague 593D Series                                                           |  |

| Inductor L1                                                  | 40μH (See <i>Table 2</i> )                                                                                                   | 33µH (See <i>Table 2</i> )                                                                                        |  |

| Output Capacitor C <sub>OUT</sub>                            | 3x220 μF, 10V AVX TPS<br>Series or Sprague 593D Series                                                                       | 3x220 μF, 10V AVX TPS<br>Series or Sprague 593D Series                                                            |  |

| Feedback Resistors R1 and R2                                 | R1 = $75k\Omega$ , 1%,<br>R2 = 24.9 $k\Omega$ , 1%,                                                                          | R1 = $41.2k\Omega$ , 1%,<br>R2 = $24.9k\Omega$ , 1%,                                                              |  |

| Compensation Components $R_C$ , $C_C$ , $R_3$ , and $C_{10}$ | $R_{C} = 37.4 \text{ k}\Omega,$<br>$C_{C} = 4.7 \text{ nF},$<br>$R_{3} = 3.57 \text{ k}\Omega,$<br>$C_{10} = 5.6 \text{ nF}$ | $R_{C} = 23.2 \text{ k}\Omega,$ $C_{C} = 8.2 \text{ nF},$ $R_{3} = 2.0 \text{ k}\Omega,$ $C_{10} = 10 \text{ nF}$ |  |

| Sleep Resistors R <sub>SIA</sub> and R <sub>SOA</sub>        | $R_{SIA}$ = 33 kΩ,<br>$R_{SOA}$ = 200 kΩ                                                                                     | $R_{SIA} = 39 \text{ k}\Omega,$<br>$R_{SOA} = 130 \text{ k}\Omega$                                                |  |

TABLE 2. Toroidal Inductors Using Cores from MICROMETALS, INC.

|      | Core    | Core     | Wire     | Number of | Number of |

|------|---------|----------|----------|-----------|-----------|

|      | Number  | Material | Gauge    | Strands   | Turns     |

| 15µH | T38     | -52      | AWG # 23 | 1         | 21        |

| 20μH | T38     | -52      | AWG # 23 | 1         | 25        |

| 33µH | T50     | -52      | AWG # 21 | 1         | 41        |

| 40μH | T50 (B) | -18      | AWG # 21 | 1         | 41        |

MICROMETALS

5615 E. La Palma Ave. Anaheim, CA 92807 USA (800) 356-5977

TABLE 3. Components for Typical 200 kHz Applications

| Input Voltage                                                | 7V to 18V IN  8 to 12 Cell NiCd or NiMh, 3 to 4 Cell Li Ion, 8 to 11 Cell Alkaline, 6 Cell Lead Acid                |                                                                                                                     |  |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| Applicable Cell Stacks                                       |                                                                                                                     |                                                                                                                     |  |

| Output                                                       | 5V, 3A Out                                                                                                          | 3.3V, 3A out                                                                                                        |  |

| Input Capacitor C <sub>IN</sub>                              | 2 x 22 μF, 35V AVX TPS<br>Series or Sprague 593D Series                                                             | 2 x 22 μF, 35V AVX TPS<br>Series or Sprague 593D Series                                                             |  |

| Inductor L1                                                  | 20µH (See <i>Table 2</i> )                                                                                          | 15µН (See <i>Table 2</i> )                                                                                          |  |

| Output Capacitor C <sub>OUT</sub>                            | 3x220 μF, 10V AVX TPS<br>Series or Sprague 593D Series                                                              | 3x220 μF, 10V AVX TPS<br>Series or Sprague 593D Series                                                              |  |

| Feedback Resistors R1 and R2                                 | R1 = $75k\Omega$ , 1%,<br>R2 = $24.9k\Omega$ , 1%,                                                                  | R1 = $41.2k\Omega$ , 1%,<br>R2 = $24.9k\Omega$ , 1%,                                                                |  |

| Compensation Components $R_C$ , $C_C$ , $R_3$ , and $C_{10}$ | $R_{C} = 53.6 \text{ k}\Omega,$ $C_{C} = 2.7 \text{ nF},$ $R_{3} = 4.02 \text{ k}\Omega,$ $C_{10} = 4.7 \text{ nF}$ | $R_{C} = 33.2 \text{ k}\Omega,$ $C_{C} = 3.9 \text{ nF},$ $R_{3} = 3.01 \text{ k}\Omega,$ $C_{10} = 6.8 \text{ nF}$ |  |

| Sleep Resistors R <sub>SIA</sub> and R <sub>SOA</sub>        | $R_{SIA} = 33 \text{ k}\Omega,$<br>$R_{SOA} = 200 \text{ k}\Omega$                                                  | $R_{SIA} = 47 \text{ k}\Omega,$<br>$R_{SOA} = 91 \text{ k}\Omega$                                                   |  |

| Frequency Adjusting<br>Resistor R <sub>FA</sub>              | $R_{FA} = 24.9 \text{ k}\Omega$                                                                                     | $R_{FA} = 24.9 \text{ k}\Omega$                                                                                     |  |

# Application Circuits (Continued)

FIGURE 5. An Efficient, 2% Accurate 5V to 3.3V Converter

### Physical Dimensions inches (millimeters) unless otherwise noted

24-Lead Small-Outline Package (M) Order Number LM2650M-ADJ NS Package Number M24B

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor** Corporation Americas

Tel: 1-800-272-9959 Fax: 1-800-737-7018

Email: support@nsc.com www.national.com

**National Semiconductor** Europe

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466 Email: ap.support@nsc.com **National Semiconductor** Tel: 81-3-5639-7560 Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.