### **FEATURES**

- Fast access time : 55ns

- Low power consumption: Operating current : 30/20mA (TYP.) Standby current : 6µA (TYP.) LL-version

- Single 2.7V ~ 5.5V power supply

- All inputs and outputs TTL compatible

- Fully static operation

- Tri-state output

- Data retention voltage : 2.0V (MIN.)

- Lead free and green package available

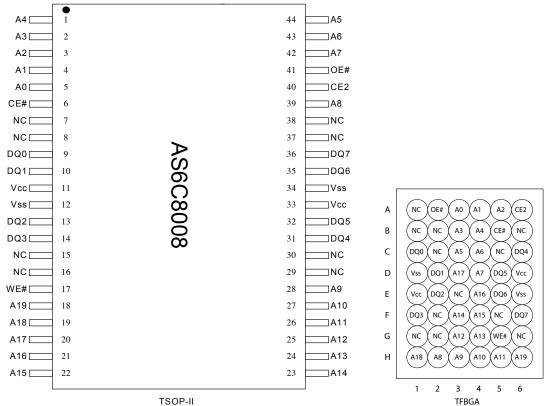

- Package : 44-pin 400 mil TSOP-II 48-ball 6mm x 8mm TFBGA

#### **GENERAL DESCRIPTION**

The AS6C8008 is a 8,388,608-bit low power CMOS static random access memory organized as 1,048,576 words by 8 bits. It is fabricated using very high performance, high reliability CMOS technology. Its standby current is stable within the range of operating temperature.

The AS6C8008 is well designed for very low power system applications, and particularly well suited for battery back-up nonvolatile memory application.

The AS6C8008 operates from a single power supply of 2.7V  $\sim$  5.5V and all inputs and outputs are fully TTL compatible

### **PRODUCT FAMILY**

| Product     | Operating         | Vcc Range  | Speed | Power Dissipation  |                     |  |

|-------------|-------------------|------------|-------|--------------------|---------------------|--|

| Family      | Temperature       | veervange  | Speed | Standby(IsB1,TYP.) | Operating(Icc,TYP.) |  |

| AS6C8008(I) | <b>-40 ~ 85</b> ℃ | 2.7 ~ 5.5V | 55ns  | 6µA(LL)            | 30/20mA             |  |

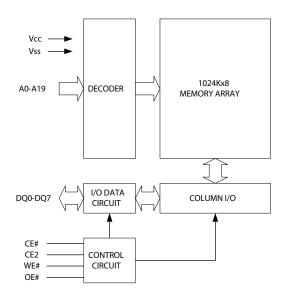

### FUNCTIONAL BLOCK DIAGRAM

### **PIN DESCRIPTION**

| SYMBOL    | DESCRIPTION         |

|-----------|---------------------|

| A0 - A19  | Address Inputs      |

| DQ0 – DQ7 | Data Inputs/Outputs |

| CE#, CE2  | Chip Enable Inputs  |

| WE#       | Write Enable Input  |

| OE#       | Output Enable Input |

| Vcc       | Power Supply        |

| Vss       | Ground              |

| NC        | No Connection       |

JANUARY/2008, V 1.0

### **PIN CONFIGURATION**

TSOP-II

JANUARY/2008, V 1.0

Alliance Memory Inc.

AS6C8008

1024K X 8 BIT SUPER LOW POWER CMOS SRAM

### ABSOLUTE MAXIMUM RATINGS

| PARAMETER                                | SYMBOL  | RATING             | UNIT |

|------------------------------------------|---------|--------------------|------|

| Voltage on Vcc relative to Vss           | Vt1     | -0.5 to 6.5        | V    |

| Voltage on any other pin relative to Vss | Vt2     | -0.5 to Vcc+0.5    | V    |

| Operating Temperature                    | TA      | -40 to 85(I grade) | °C   |

| Storage Temperature                      | Тѕтс    | -65 to 150         | °C   |

| Power Dissipation                        | PD      | 1                  | W    |

| DC Output Current                        | Ιουτ    | 50                 | mA   |

| Soldering Temperature (under 10 sec)     | TSOLDER | 260                | °C   |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to the absolute maximum rating conditions for extended period may affect device reliability.

#### **TRUTH TABLE**

| MODE           | CE# | CE2 | OE# | WE# | I/O OPERATION | SUPPLY CURRENT |

|----------------|-----|-----|-----|-----|---------------|----------------|

| Standby        | Н   | Х   | X   | Х   | High-Z        | ISB1           |

| Standby        | Х   | L   | Х   | Х   | High-Z        | ISB1           |

| Output Disable | L   | Н   | Н   | Н   | High-Z        | lcc,lcc1       |

| Read           | L   | Н   | L   | Н   | Dout          | lcc,lcc1       |

| Write          | L   | Н   | Х   | L   | DIN           | lcc,lcc1       |

Note:  $H = V_{H}, L = V_{L}, X = Don't care.$

### **DC ELECTRICAL CHARACTERISTICS**

| PARAMETER                       | SYMBOL            | TEST CONDITION                                                                                                                                            |       | MIN. | <b>TYP.</b> <sup>*4</sup> | MAX.    | UNIT |

|---------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|---------------------------|---------|------|

| Supply Voltage                  | Vcc               |                                                                                                                                                           |       | 2.7  | 3.0                       | 5.5     | V    |

| Input High Voltage              | VIH <sup>*1</sup> |                                                                                                                                                           |       | 2.4  | -                         | Vcc+0.3 | V    |

| Input Low Voltage               | VIL <sup>*2</sup> |                                                                                                                                                           | - 0.2 | -    | 0.6                       | V       |      |

| Input Leakage Current           | LI                | $V_{CC} \ge V_{IN} \ge V_{SS}$                                                                                                                            |       | - 1  | -                         | 1       | μA   |

| Output Leakage<br>Current       | ILO               | Vcc ≧ Vou⊤ ≧ Vss<br>Output Disabled                                                                                                                       | - 1   | -    | 1                         | μA      |      |

| Output High Voltage             | Vон               | Iон = -1mA                                                                                                                                                | 2.4   | 2.7  | -                         | V       |      |

| Output Low Voltage              | Vol               | I <sub>OL</sub> = 2mA                                                                                                                                     |       | -    | -                         | 0.4     | V    |

| Average Operating               | lcc               | Cycle time = Min.<br>CE# = Vi∟ and CE2 = ViH<br>Ii∕o = 0mA<br>Other pins at Vi∟ or ViH                                                                    | - 55  | -    | 30                        | 60      | mA   |

| Power supply Current            | Icc1              | Cycle time = $1\mu$ s<br>CE# $\leq$ 0.2V and CE2 $\geq$ V <sub>CC</sub> -0.2V<br>I <sub>VO</sub> = 0mA<br>Other pins at 0.2V or V <sub>CC</sub> -0.2V     |       | -    | -                         | 4       | mA   |

| Standby Power<br>Supply Current | I <sub>SB1</sub>  | $\label{eq:cell} \begin{array}{l} CE\# \geqq V_{CC}\text{-}0.2V \\ or \ CE2 \leqq 0.2V \\ Other \ pins \ at \ 0.2V \ or \ V_{CC}\text{-}0.2V \end{array}$ |       | _    | 6                         | 80      | μA   |

JANUARY/2008, V 1.0

Notes:

1. VIH(max) = V<sub>CC</sub> + 3.0V for pulse width less than 10ns.

- 2.  $V_{IL}(min) = V_{SS} 3.0V$  for pulse width less than 10ns.

- 3. Over/Undershoot specifications are characterized, not 100% tested.

- 4. Typical values are included for reference only and are not guaranteed or tested.

- Typical valued are measured at V<sub>CC</sub> = V<sub>CC</sub>(TYP.) and T<sub>A</sub> =  $25^{\circ}$ C

#### **CAPACITANCE** (TA = 25? , f = 1.0MHz)

| PARAMETER                | SYMBOL | MIN. | MAX | UNIT |

|--------------------------|--------|------|-----|------|

| Input Capacitance        | Cin    | -    | 6   | pF   |

| Input/Output Capacitance | Cı/o   | -    | 8   | pF   |

Note : These parameters are guaranteed by device characterization, but not production tested.

#### **AC TEST CONDITIONS**

| Input Pulse Levels                       | 0.2V to Vcc - 0.2V                               |

|------------------------------------------|--------------------------------------------------|

| Input Rise and Fall Times                | 3ns                                              |

| Input and Output Timing Reference Levels | 1.5V                                             |

| Output Load                              | $C_L = 30pF + 1TTL$ , $I_{OH}/I_{OL} = -1mA/2mA$ |

### **AC ELECTRICAL CHARACTERISTICS**

#### (1) READ CYCLE

| PARAMETER                          | SYM.         | AS6C8008-55 |      | UNIT |

|------------------------------------|--------------|-------------|------|------|

|                                    |              | MIN.        | MAX. |      |

| Read Cycle Time                    | trc          | 55          | -    | ns   |

| Address Access Time                | taa          | -           | 55   | ns   |

| Chip Enable Access Time            | <b>t</b> ACE | -           | 55   | ns   |

| Output Enable Access Time          | <b>t</b> OE  | -           | 30   | ns   |

| Chip Enable to Output in Low-Z     | tcLz*        | 10          | -    | ns   |

| Output Enable to Output in Low-Z   | tolz*        | 5           | -    | ns   |

| Chip Disable to Output in High-Z   | tснz*        | -           | 20   | ns   |

| Output Disable to Output in High-Z | toнz*        | -           | 20   | ns   |

| Output Hold from Address Change    | tон          | 10          | -    | ns   |

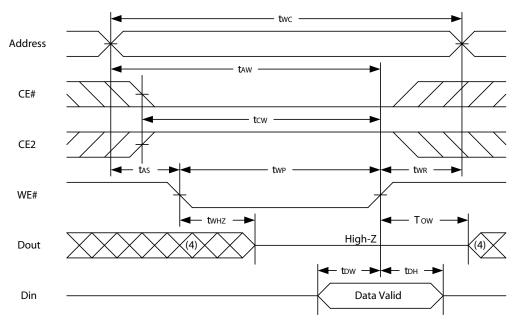

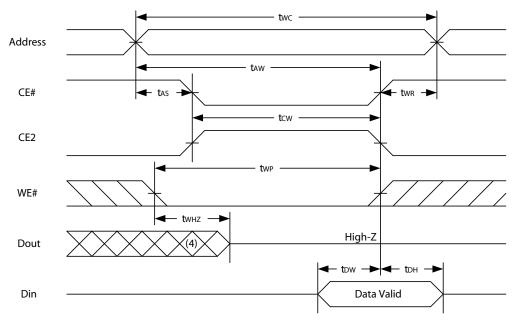

#### (2) WRITE CYCLE

| PARAMETER                        | SYM.  | AS6C80 | 08-55 | UNIT |

|----------------------------------|-------|--------|-------|------|

|                                  |       | MIN.   | MAX.  |      |

| Write Cycle Time                 | twc   | 55     | -     | ns   |

| Address Valid to End of Write    | taw   | 50     | -     | ns   |

| Chip Enable to End of Write      | tcw   | 50     | -     | ns   |

| Address Set-up Time              | tas   | 0      | -     | ns   |

| Write Pulse Width                | twp   | 45     | -     | ns   |

| Write Recovery Time              | twr   | 0      | -     | ns   |

| Data to Write Time Overlap       | tow   | 25     | -     | ns   |

| Data Hold from End of Write Time | tон   | 0      | -     | ns   |

| Output Active from End of Write  | tow*  | 5      | -     | ns   |

| Write to Output in High-Z        | twнz* | -      | 20    | ns   |

\*These parameters are guaranteed by device characterization, but not production tested.

JANUARY/2008, V 1.0

### TIMING WAVEFORMS

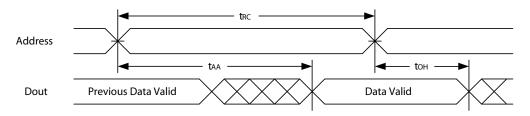

READ CYCLE 1 (Address Controlled) (1,2)

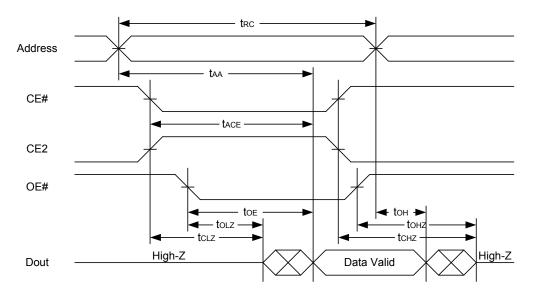

#### READ CYCLE 2 (CE# and CE2 and OE# Controlled) (1,3,4,5)

#### Notes :

1.WE# is high for read cycle.

2.Device is continuously selected OE# = low, CE# = low., CE2 = high.

3.Address must be valid prior to or coincident with CE# = low, CE2 = high; otherwise t<sub>AA</sub> is the limiting parameter. 4.t<sub>CLZ</sub>, t<sub>CLZ</sub>, t<sub>CHZ</sub> and t<sub>OHZ</sub> are specified with C<sub>L</sub> = 5pF. Transition is measured  $\pm$ 500mV from steady state.

5.At any given temperature and voltage condition, tCHZ is less than tCLZ , tOHZ is less than tOLZ.

JANUARY/2008, V 1.0

Alliance Memory Inc.

Page 5 of 11

AS6C8008

AS6C8008

#### WRITE CYCLE 1 (WE# Controlled) (1,2,3,5,6)

WRITE CYCLE 2 (CE# and CE2 Controlled) (1,2,5,6)

Notes :

1.WE#, CE# must be high or CE2 must be low during all address transitions.

2.A write occurs during the overlap of a low CE#, high CE2, low WE#.

3.During a WE#controlled write cycle with OE# low, twp must be greater than twHz + tow to allow the drivers to turn off and data to be placed on the bus.

4. During this period, I/O pins are in the output state, and input signals must not be applied.

5. If the CE#low transition and CE2 high transition occurs simultaneously with or after WE# low transition, the outputs remain in a high impedance state.

6.tow and twHz are specified with  $C_L$  = 5pF. Transition is measured ±500mV from steady state.

JANUARY/2008, V 1.0

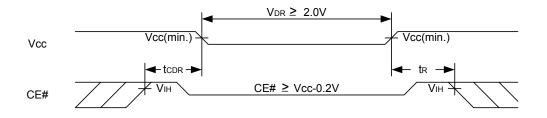

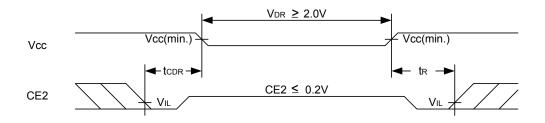

## **DATA RETENTION CHARACTERISTICS**

| PARAMETER                              | SYMBOL | TEST CONDITION                                                                                  |    | MIN.             | TYP. | MAX. | UNIT |

|----------------------------------------|--------|-------------------------------------------------------------------------------------------------|----|------------------|------|------|------|

| Vcc for Data Retention                 | Vdr    | CE# $\geq$ V <sub>CC</sub> - 0.2V or CE2 $\leq$ 0.2V                                            |    | 2.0              | -    | 5.5  | V    |

| Data Retention Current                 | ldr    | $V_{CC} = 2.0V$<br>CE# $\geq$ Vcc - 0.2V or CE2 $\leq$ 0.2V<br>Other pins at 0.2V or Vcc - 0.2V | -1 | -                | 5    | 50   | μA   |

| Chip Disable to Data<br>Retention Time | tcdr   | See Data Retention<br>Waveforms (below)                                                         |    | 0                | -    | -    | ns   |

| Recovery Time                          | tR     |                                                                                                 |    | t <sub>RC⁺</sub> | -    | -    | ns   |

tRC∗ = Read Cycle Time

#### **DATA RETENTION WAVEFORM**

Low Vcc Data Retention Waveform (1) (CE# controlled)

#### Low Vcc Data Retention Waveform (2) (CE2 controlled)

JANUARY/2008, V 1.0

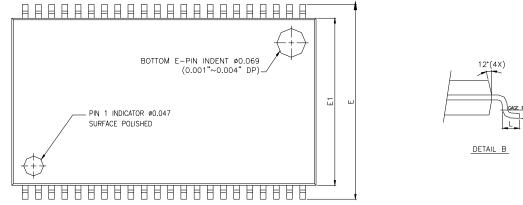

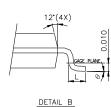

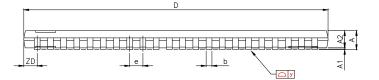

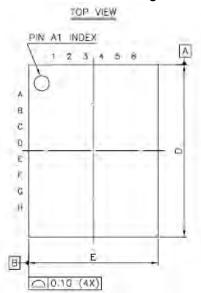

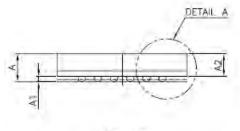

### PACKAGE OUTLINE DIMENSION

#### 44-pin 400mil TSOP-II Package Outline Dimension

AS6C8008

| SYMBOLS | DIMENSI | ONS IN MILL | METERS | DIMI | ENSIONS IN I | MILS |

|---------|---------|-------------|--------|------|--------------|------|

| STMBOLS | MIN.    | NOM.        | MAX.   | MIN. | NOM.         | MAX. |

| A       | -       | -           | 1.20   | -    | -            | 47.2 |

| A1      | 0.05    | 0.10        | 0.15   | 2.0  | 3.9          | 5.9  |

| A2      | 0.95    | 1.00        | 1.05   | 37.4 | 39.4         | 41.3 |

| b       | 0.30    | -           | 0.45   | 11.8 | -            | 17.7 |

| С       | 0.12    | -           | 0.21   | 4.7  | -            | 8.3  |

| D       | 18.212  | 18.415      | 18.618 | 717  | 725          | 733  |

| E       | 11.506  | 11.760      | 12.014 | 453  | 463          | 473  |

| E1      | 9.957   | 10.160      | 10.363 | 392  | 400          | 408  |

| е       | -       | 0.800       | -      | -    | 31.5         | -    |

| L       | 0.40    | 0.50        | 0.60   | 15.7 | 19.7         | 23.6 |

| ZD      | -       | 0.805       | -      | -    | 31.7         | -    |

| У       | -       | -           | 0.076  | -    | -            | 3    |

| θ       | 0°      | 3°          | 6°     | 0°   | 3°           | 6°   |

JANUARY/2008, V 1.0

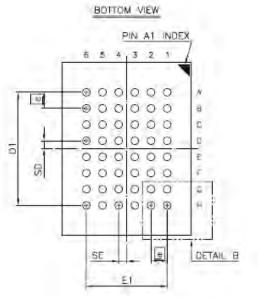

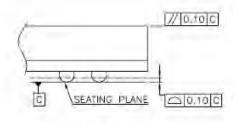

#### 48-ball 6mm × 8mm TFBGA Package Outline Dimension

SIDE VIEW

SOLDER BALL

Φ

Øb(48x PLACES)

0.08M C

0.150 CAB

|      | D         | MENSIO<br>(mm) | N    | DIMENSION<br>(inch) |         |       |  |  |

|------|-----------|----------------|------|---------------------|---------|-------|--|--|

| SYM. | MIN.      | NOM.           | MAX. | MIN.                | NOM.    | MAX.  |  |  |

| A    | -         | -              | 1.40 | =                   | -       | 0.055 |  |  |

| A1   | 0.20      | 0.25           | 0.30 | 0.008               | 0.010   | 0.012 |  |  |

| A2   | -         | -              | 1.05 | -                   |         | 0.041 |  |  |

| ъ    | 0.30      | 0.35           | 0.40 | 0.012               | 0.014   | 0.016 |  |  |

| 0    | 7.95      | 8.00           | 8.05 | 0.313               | 0.315   | 0.317 |  |  |

| D1   | 5         | .25 BS         | 0    | 0                   | 207 65  | SC.   |  |  |

| E    | 5.95      | 6.00           | 6.05 | 0.234               | 0.236   | 0.238 |  |  |

| 61   | 3         | 3.75 BSC       |      |                     | 148 BS  | SC    |  |  |

| SE   | 0.375 TYP |                |      | 8                   | 015 TY  | 'p    |  |  |

| SD   | 0.375 TYP |                |      | 8                   | 015 TY  | P     |  |  |

| 0    | 0         | .75 BS         | 0    | 0                   | .030 BS | SC    |  |  |

1. CONTROLLING DIMENSION . MILLIMETER:

2. REFERENCE DOCUMENT : JEDEC MO-207

#### JANUARY/2008, V 1.0

0

C

C

DETAIL B

# **ORDERING INFORMATION**

| Alliance       | Organization | VCC Range  | Package       | Operating Temp            | Speed<br>ns |

|----------------|--------------|------------|---------------|---------------------------|-------------|

| AS6C8008-55ZIN | 1024K x 8    | 2.7 - 5.5V | 44pin TSOP II | Industrial ~ -40 F - 85 F | 55          |

| AS6C8008-55BIN | 1024K x 8    | 2.7 - 5.5V | 48ball TFBGA  | Industrial ~ -40 F - 85 F | 55          |

# PART NUMBERING SYSTEM

| AS6C                      | 8008                                | -55            | X                                                    | X                                                      | N                                       |

|---------------------------|-------------------------------------|----------------|------------------------------------------------------|--------------------------------------------------------|-----------------------------------------|

| low power<br>S RAM prefix | Device Number<br>380 =8M<br>08 = x8 | Access<br>Time | Package Option<br>Z - 44pin TSOP<br>B = 48ball TFBGA | Temperature Range<br>I = Industrial<br>(-40 to + 85 C) | N = Lead Free<br>RoHS<br>compliant part |

1024K X 8 BIT LOW POWER CMOS SRAM

Alliance Memory, Inc 511 Taylor Way, San Carlos, CA 94070, USA Phone: 650-610-6800 Fax: 650-620-9211

www.alliancememory.com

Copyright © Alliance Memory All Rights Reserved

© Copyright 2007 Alliance Memory, Inc. All rights reserved. Our three-point logo, our name and Intelliwatt are trademarks or registered trademarks of Alliance. All other brand and product names may be the trademarks of their respective companies. Alliance reserves the right to make changes to thisdocument and its products at any time without notice. Alliance assumes no responsibility for any errors that may appear in this document. The datacontained herein represents Alliance's best data and/or estimates at the time of issuance. Alliance reserves the right to change or correct this data at anytime, without notice. If the product described herein is under development, significant changes to these specifications are possible. The information inthis product data sheet is intended to be general descriptive information for potential customers and users, and is not intended to operate as, or provide, any guarantee or warrantee to any user or customer. Alliance does not assume any responsibility or liability arising out of the application or use of anyproduct described herein, and disclaims any express or implied warranties related to the sale and/or use of Alliance products including liability orwarranties related to fitness for a particular purpose, merchantability, or infringement of any intellectual property rights, except as express agreed to inAlliance's Terms and Conditions of Sale (which are available from Alliance). All sales of Alliance products are made exclusively according to Alliance's Terms and Conditions of Sale. The purchase of products from Alliance does not convey a license under any patent rights, copyrights; mask works rights, trademarks, or any other intellectual property rights of Alliance or third parties. Alliance does not authorize its products for use as critical components inlife-supporting systems implies that the manufacturer assumes all risk of such use and agrees to indemnify Alliance against allclaims arising from such use.

JANUARY/2008, V 1.0

Alliance Memory Inc.

Page 11 of 11