# DS90LV001 800 Mbps LVDS Buffer

#### **General Description**

The DS90LV001 LVDS-LVDS Buffer takes an LVDS input signal and provides an LVDS output signal. In many large systems, signals are distributed across backplanes, and one of the limiting factors for system speed is the "stub length" or the distance between the transmission line and the unterminated receivers on individual cards. Although it is generally recognized that this distance should be as short as possible to maximize system performance, real-world packaging concerns often make it difficult to make the stubs as short as the designer would like.

The DS90LV001, available in the LLP (Leadless Leadframe Package) package, will allow the receiver to be placed very close to the main transmission line, thus improving system performance.

A wide input dynamic range will allow the DS90LV001 to receive differential signals from LVPECL as well as LVDS sources. This will allow the device to also fill the role of an LVPECL-LVDS translator.

An output enable pin is provided, which allows the user to place the LVDS output in TRI-STATE.

The DS90LV001 is offered in two package options, an 8 pin LLP and SOIC.

#### **Features**

- Single +3.3 V Supply

- LVDS receiver inputs accept LVPECL signals

- TRI-STATE outputs

- Receiver input threshold < ±100 mV</p>

- Fast propagation delay of 1.4 ns (typ)

- Low jitter 800 Mbps fully differential data path

- 100 ps (typ) of pk-pk jitter with PRBS = 2<sup>23</sup>-1 data pattern at 800 Mbps

- Compatible with ANSI/TIA/EIA-644-A LVDS standard

- 8 pin SOIC and space saving (70%) LLP package

- Industrial Temperature Range

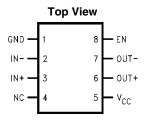

### **Connection Diagram**

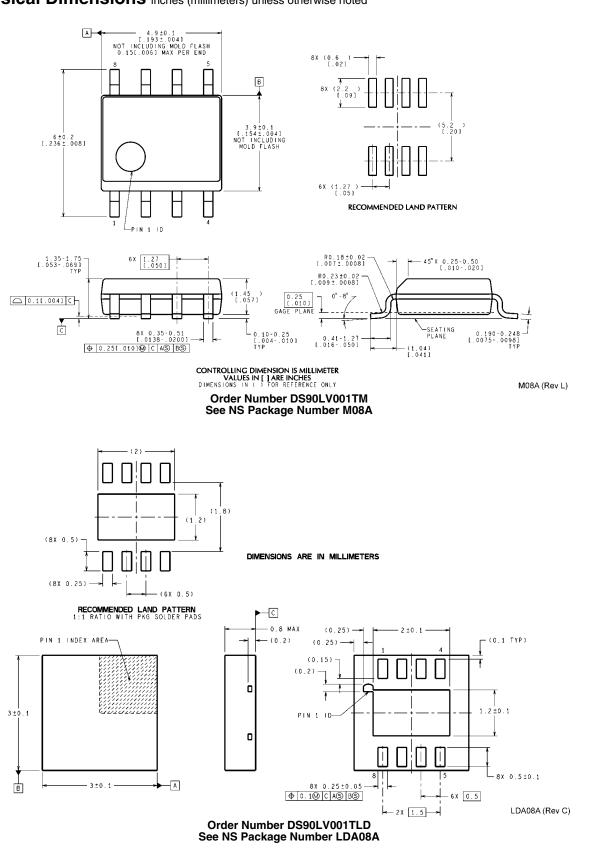

Order Number DS90LV001TM, DS90LV001TLD See NS Package Number M08A, LDA08A

# **Block Diagram**

### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage ( $V_{CC}$ ) -0.3V to +4V

LVCMOS/LVTTL Input Voltage -0.3V to  $(V_{CC} + 0.3V)$

LVDS Receiver Input Voltage (IN

+, IN-) -0.3V to +4V

LVDS Driver Output Voltage (OUT

+, OUT-) -0.3V to +4V LVDS Output Short Circuit Current Continuous Junction Temperature +150°C

Storage Temperature Range Lead Temperature Range

Soldering (4 sec.) +260°C

Maximum Package Power Dissipation at 25°C

M Package 726 mW

Derate M Package 5.8 mW/°C above +25°C

LDA Package 2.44 W

Derate LDA Package 19.49 mW/°C above +25°C

**ESD Ratings**

(HBM, 1.5kΩ, 100pF) ≥2.5kV (EIAJ, 0Ω, 200pF) ≥250V

# Recommended Operating Conditions

|                                   | Min | Тур | Max      | Units |

|-----------------------------------|-----|-----|----------|-------|

| Supply Voltage (V <sub>CC</sub> ) | 3.0 | 3.3 | 3.6      | V     |

| Receiver Input Voltage            | 0   |     | $V_{CC}$ | V     |

| Operating Free Air                | -40 | +25 | +85      | °C    |

| Temperature                       |     |     |          |       |

#### **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified. (Notes 2, 3)

-65°C to +150°C

| Symbol           | Parameter                                                                 | С                                                    | Conditions                   |       | Тур  | Max             | Units |

|------------------|---------------------------------------------------------------------------|------------------------------------------------------|------------------------------|-------|------|-----------------|-------|

| LVCMO            | S/LVTTL DC SPECIFICATIONS (EN)                                            |                                                      |                              |       |      |                 |       |

| $V_{IH}$         | High Level Input Voltage                                                  |                                                      |                              | 2.0   |      | V <sub>CC</sub> | ٧     |

| V <sub>IL</sub>  | Low Level Input Voltage                                                   |                                                      |                              | GND   |      | 0.8             | V     |

| I <sub>IH</sub>  | High Level Input Current                                                  | $V_{IN} = 3.6V \text{ or } 2$                        | 2.0V, V <sub>CC</sub> = 3.6V |       | +7   | +20             | μΑ    |

| I <sub>IL</sub>  | Low Level Input Current                                                   | V <sub>IN</sub> = GND or 0                           | $0.8V, V_{CC} = 3.6V$        |       | ±1   | ±10             | μΑ    |

| V <sub>CL</sub>  | Input Clamp Voltage                                                       | I <sub>CL</sub> = -18 mA                             |                              |       | -0.6 | -1.5            | V     |

| LVDS O           | UTPUT DC SPECIFICATIONS (OUT)                                             | •                                                    |                              |       |      |                 |       |

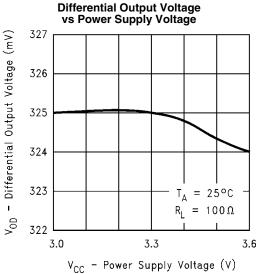

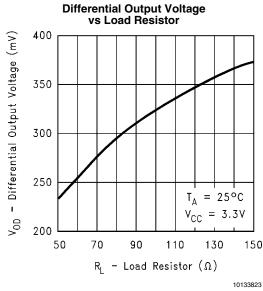

| V <sub>OD</sub>  | Differential Output Voltage                                               | $R_L = 100\Omega$                                    |                              | 250   | 325  | 450             | mV    |

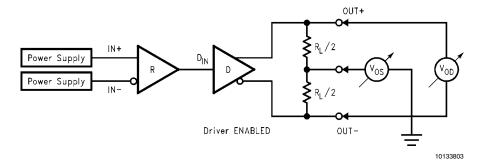

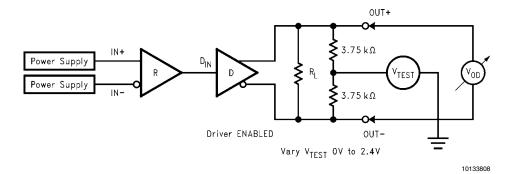

| ΔV <sub>OD</sub> | Change in Magnitude of V <sub>OD</sub> for Complimentary<br>Output States | Figure 1 and Figure 2                                |                              |       |      | 20              | mV    |

| V <sub>os</sub>  | Offset Voltage                                                            | $R_1 = 100\Omega$                                    |                              | 1.080 | 1.19 | 1.375           | V     |

| ΔV <sub>OS</sub> | Change in Magnitude of V <sub>OS</sub> for Complimentary<br>Output States | Figure 1                                             |                              |       |      | 20              | mV    |

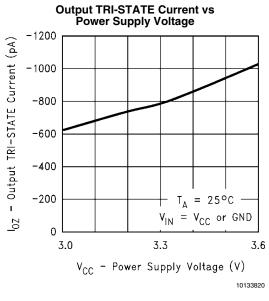

| I <sub>oz</sub>  | Output TRI-STATE Current                                                  | EN = 0V, V <sub>OUT</sub> = V <sub>CC</sub> or GND   |                              |       | ±1   | ±10             | μA    |

| I <sub>OFF</sub> | Power-Off Leakage Current                                                 | V <sub>CC</sub> = 0V, V <sub>OUT</sub> = 3.6V or GND |                              |       | ±1   | ±10             | μA    |

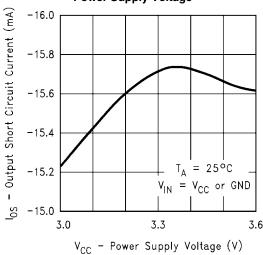

| I <sub>os</sub>  | Output Short Circuit Current (Note 4)                                     | $EN = V_{CC}, V_{OUT+}$ and $V_{OUT-} = 0V$          |                              |       | -16  | -24             | mA    |

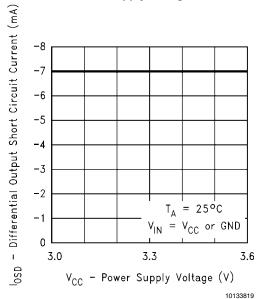

| I <sub>OSD</sub> | Differential Output Short Circuit Current (Note 4)                        | $EN = V_{CC}, V_{OD} = 0V$                           |                              |       | -7   | -12             | mA    |

| LVDS R           | ECEIVER DC SPECIFICATIONS (IN)                                            |                                                      |                              |       |      |                 |       |

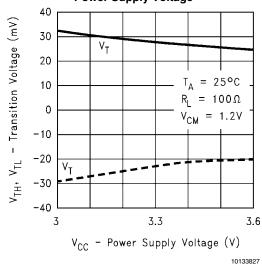

| $V_{TH}$         | Differential Input High Threshold                                         | V <sub>CM</sub> = +0.05V, +1.2V or +3.25V            |                              |       | 0    | +100            | mV    |

| $V_{TL}$         | Differential Input Low Threshold                                          | 7                                                    |                              | -100  | 0    |                 | mV    |

| $V_{CMR}$        | Common Mode Voltage Range                                                 | $V_{ID} = 100 \text{mV}, V_{CC} = 3.3 \text{V}$      |                              | 0.05  |      | 3.25            | V     |

| I <sub>IN</sub>  | Input Current                                                             | $V_{IN} = +3.0V$                                     | V <sub>CC</sub> = 3.6V or 0V |       | ±1   | ±10             | μΑ    |

|                  |                                                                           | $V_{IN} = 0V$                                        |                              |       | ±1   | ±10             | μΑ    |

| ΔI <sub>IN</sub> | Change in Magnitude of I <sub>IN</sub>                                    | V <sub>IN</sub> = +3.0V                              | V <sub>CC</sub> = 3.6V or 0V |       | 1    | 6               | μΑ    |

|                  |                                                                           | $V_{IN} = 0V$                                        | ]                            |       | 1    | 6               | μA    |

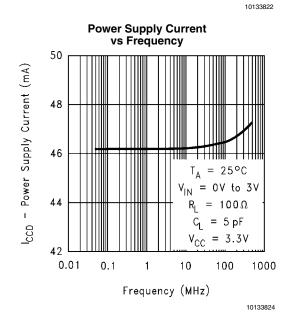

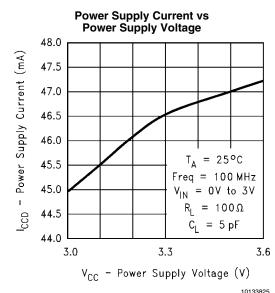

| SUPPLY           | CURRENT                                                                   | •                                                    |                              |       |      |                 |       |

| I <sub>CCD</sub> | Total Supply Current                                                      | $EN = V_{CC}, R_{L} = 100Ω, C_{L} = 5 pF$            |                              |       | 47   | 70              | mA    |

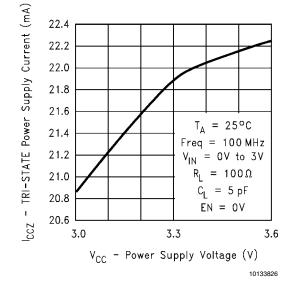

| I <sub>CCZ</sub> | TRI-STATE Supply Current                                                  | EN = 0V                                              |                              |       | 22   | 35              | mA    |

#### **AC Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified. (Note 3)

| Symbol            | Parameter                                                        | Conditions                                                                    | Min | Тур | Max | Units |

|-------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------|-----|-----|-----|-------|

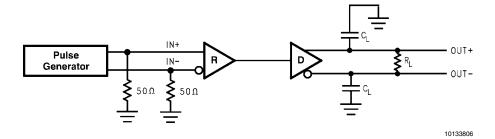

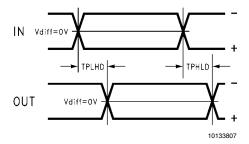

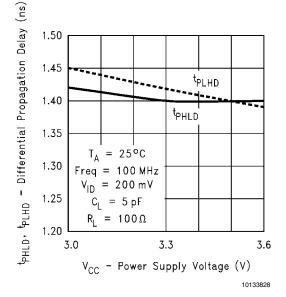

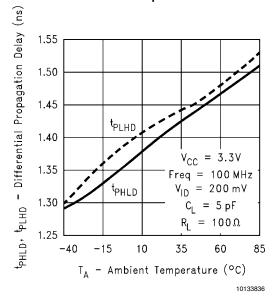

| t <sub>PHLD</sub> | Differential Propagation Delay High to Low                       | $R_L = 100\Omega$ , $C_L = 5pF$                                               | 1.0 | 1.4 | 2.0 | ns    |

| t <sub>PLHD</sub> | Differential Propagation Delay Low to High                       | Figure 3 and Figure 4                                                         | 1.0 | 1.4 | 2.0 | ns    |

| t <sub>SKD1</sub> | Pulse Skew It <sub>PLHD</sub> – t <sub>PHLD</sub> I (Notes 5, 6) |                                                                               |     | 20  | 200 | ps    |

| t <sub>SKD3</sub> | Part to Part Skew (Notes 5, 7)                                   |                                                                               |     | 0   | 60  | ps    |

| t <sub>SKD4</sub> | Part to Part Skew (Notes 5, 8)                                   |                                                                               |     |     | 400 | ps    |

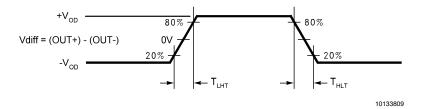

| t <sub>LHT</sub>  | Rise Time (Note 5)                                               | $R_{L} = 100\Omega, C_{L} = 5pF$                                              | 200 | 320 | 450 | ps    |

| t <sub>HLT</sub>  | Fall Time (Note 5)                                               | Figure 3 and Figure 5                                                         | 200 | 310 | 450 | ps    |

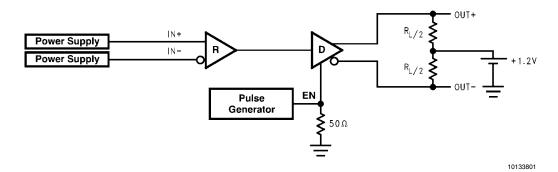

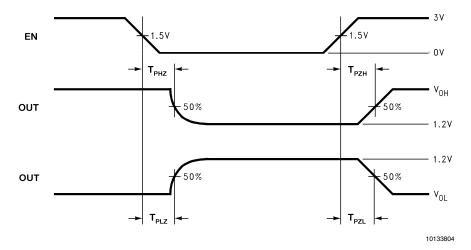

| t <sub>PHZ</sub>  | Disable Time (Active High to Z)                                  | $R_{L} = 100\Omega, C_{L} = 5pF$                                              |     | 3   | 25  | ns    |

| t <sub>PLZ</sub>  | Disable Time (Active Low to Z)                                   | Figure 6 and Figure 7                                                         |     | 3   | 25  | ns    |

| t <sub>PZH</sub>  | Enable Time (Z to Active High)                                   |                                                                               |     | 25  | 45  | ns    |

| t <sub>PZL</sub>  | Enable Time (Z to Active Low)                                    |                                                                               |     | 25  | 45  | ns    |

| t <sub>DJ</sub>   | LVDS Data Jitter, Deterministic (Peak-to-Peak) (Note 9)          | $V_{ID} = 300$ mV; PRBS = $2^{23} - 1$ data; $V_{CM}$ = 1.2V at 800Mbps (NRZ) |     | 100 | 135 | ps    |

| t <sub>RJ</sub>   | LVDS Clock Jitter, Random (Note 9)                               | $V_{ID} = 300$ mV; $V_{CM} = 1.2$ V at 400MHz clock                           |     | 2.2 | 3.5 | ps    |

**Note 1:** "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

**Note 2:** Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except  $V_{OD}$  and  $\Delta V_{OD}$ .

**Note 3:** All typical are given for  $V_{CC}$  = +3.3V and  $T_A$  = +25°C, unless otherwise stated.

Note 4: Output short circuit current (I<sub>OS</sub>) is specified as magnitude only, minus sign indicates direction only.

Note 5: The parameters are guaranteed by design. The limits are based on statistical analysis of the device performance over the PVT (process, voltage and temperature) range.

Note 6: t<sub>SKD1</sub>, It<sub>PLHD</sub> - t<sub>PHLD</sub>I, is the magnitude difference in differential propagation delay time between the positive going edge and the negative going edge of the same channel.

Note 7:  $t_{SKD3}$ , Part to Part Skew, is defined as the difference between the minimum and maximum specified differential propagation delays. This specification applies to devices at the same  $V_{CC}$  and within 5°C of each other within the operating temperature range.

Note 8: t<sub>SKD4</sub>, Part to Part Skew, is the differential channel-to-channel skew of any event between devices. This specification applies to devices over recommended operating temperature and voltage ranges, and across process distribution. t<sub>SKD4</sub> is defined as IMax – MinI differential propagation delay.

**Note 9:** The parameters are guaranteed by design. The limits are based on statistical analysis of the device performance over the PVT range with the following test equipment setup: HP8133A (pattern pulse generator), 5 feet of RG142B cable with DUT test board and HP83480A (digital scope mainframe) with HP83484A (50GHz scope module). The HP8133A with RG142B cable exhibit a t<sub>D,I</sub> = 21ps and t<sub>B,I</sub> = 1.8ps.

## **DC Test Circuits**

FIGURE 1. Differential Driver DC Test Circuit

FIGURE 2. Differential Driver Full Load DC Test Circuit

# **AC Test Circuits and Timing Diagrams**

FIGURE 3. LVDS Output Load

FIGURE 4. Propagation Delay Low-to-High and High-to-Low

FIGURE 5. LVDS Output Transition Time

FIGURE 6. TRI-STATE Delay Test Circuit

FIGURE 7. Output active to TRI-STATE and TRI-STATE to active output time

# DS90LV001 Pin Descriptions (SOIC and LLP)

| Pin Name        | Pin # | Input/Output | Description                                                                                                                                                                                               |

|-----------------|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND             | 1     | Р            | Ground                                                                                                                                                                                                    |

| IN –            | 2     | I            | Inverting receiver LVDS input pin                                                                                                                                                                         |

| IN+             | 3     | I            | Non-inverting receiver LVDS input pin                                                                                                                                                                     |

| NC              | 4     |              | No Connect                                                                                                                                                                                                |

| V <sub>CC</sub> | 5     | Р            | Power Supply, 3.3V ± 0.3V.                                                                                                                                                                                |

| OUT+            | 6     | 0            | Non-inverting driver LVDS output pin                                                                                                                                                                      |

| OUT -           | 7     | 0            | Inverting driver LVDS output pin                                                                                                                                                                          |

| EN              | 8     | I            | Enable pin. When EN is LOW, the driver is disabled and the LVDS outputs are in TRI-STATE. When EN is HIGH, the driver is enabled. LVCMOS/LVTTL levels.                                                    |

| DAP             | NA    | NA           | Die Attach Pad or DAP (LLP Package only). The DAP is NOT connected to the device GND nor any other pin. It is still recommended to connect the DAP to a GND plane of a PCB for enhenced heat dissipation. |

# **Typical Applications**

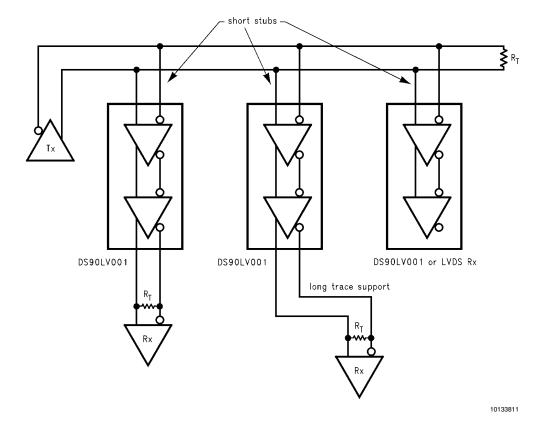

#### **Backplane Stub-Hider Application**

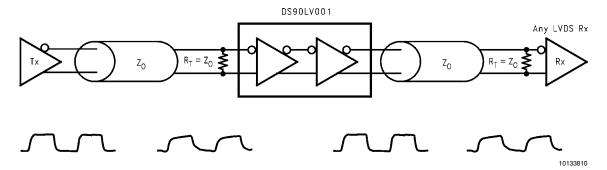

#### **Cable Repeater Application**

### **Application Information**

#### **MODE OF OPERATION**

The DS90LV001 can be used as a "stub-hider." In many systems, signals are distributed across backplanes, and one of the limiting factors for system speed is the "stub length" or the distance between the transmission line and the unterminated receivers on the individual cards. Although it is generally recognized that this distance should be as short as possible to maximize system performance, real-world packaging concerns and PCB designs often make it difficult to make the stubs as short as the designer would like. The DS90LV001, available in the LLP (Leadless Leadframe Package) package, can improve system performance by allowing the receiver to be placed very close to the main transmission line either on the backplane itself or very close to the connector on the card. Longer traces to the LVDS receiver may be placed after the DS90LV001. This very small LLP package is a 75% space savings over the SOIC package.

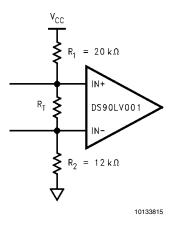

#### **INPUT FAILSAFE**

The receiver inputs of the DS90LV001 do not have internal failsafe biasing. For point-to-point and multidrop applications with a single source, failsafe biasing may not be required. When the driver is off, the link is in-active. If failsafe biasing is required, this can be accomplished with external high value resistors. Using the equations in the LVDS Owner's Manual Chapter 4, the IN+ should be pull to  $V_{\rm CC}$  (3.3V) with 20k $\Omega$  and the IN- should be pull to GND with 12k $\Omega$ . This provides a slight positive differential bias, and sets a known HIGH state on the link with a minimum amount of distortion.

#### **PCB LAYOUT AND POWER SYSTEM BYPASS**

Circuit board layout and stack-up for the DS90LV001 should be designed to provide noise-free power to the device. Good layout practice also will separate high frequency or high level inputs and outputs to minimize unwanted stray noise pickup, feedback and interference. Power system performance may be greatly improved by using thin dielectrics (4 to 10 mils) for power/ground sandwiches. This increases the intrinsic capacitance of the PCB power system which improves power supply filtering, especially at high frequencies, and makes the value and placement of external bypass capacitors less critical. External bypass capacitors should include both RF ceramic and tantalum electrolytic types. RF capacitors may use values in the range 0.01 μF to 0.1 μF. Tantalum capacitors may be in the range 2.2 µF to 10 µF. Voltage rating for tantalum capacitors should be at least 5X the power supply voltage being used. It is recommended practice to use two vias at each power pin of the DS90LV001 as well as all RF bypass capacitor terminals. Dual vias reduce the interconnect inductance by up to half, thereby reducing interconnect inductance and extending the effective frequency range of the bypass components.

The outer layers of the PCB may be flooded with additional ground plane. These planes will improve shielding and isolation as well as increase the intrinsic capacitance of the power supply plane system. Naturally, to be effective, these planes must be tied to the ground supply plane at frequent intervals with vias. Frequent via placement also improves signal integrity on signal transmission lines by providing short paths for image currents which reduces signal distortion. The planes should be pulled back from all transmission lines and component mounting pads a distance equal to the width of the widest transmission line or the thickness of the dielectric separating the transmission line from the internal power or ground plane(s) whichever is greater. Doing so minimizes effects on transmission line impedances and reduces unwanted parasitic capacitances at component mounting pads.

There are more common practices which should be followed when designing PCBs for LVDS signaling. Please see application note AN-1108 for guidelines. In addition, application note AN-1187 has additional information specifically related to LLP recommendations.

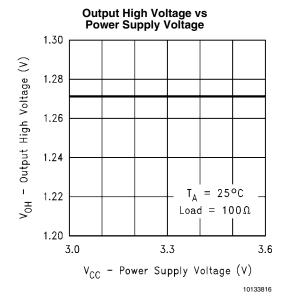

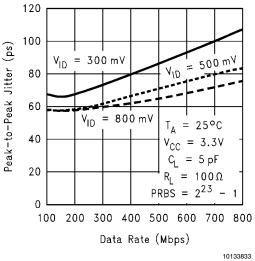

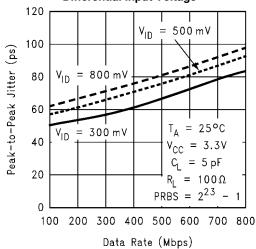

# **Typical Performance Curves**

#### Output Short Circuit Current vs Power Supply Voltage

10133818

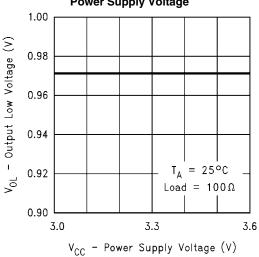

#### Output Low Voltage vs Power Supply Voltage

#### Differential Output Short Circuit Current vs Power Supply Voltage

#### TRI-STATE Power Supply Current vs Power Supply Voltage

#### Differential Propagation Delay vs Power Supply Voltage

#### Differential Transition Voltage vs Power Supply Voltage

#### Differential Propagation Delay vs Ambient Temperature

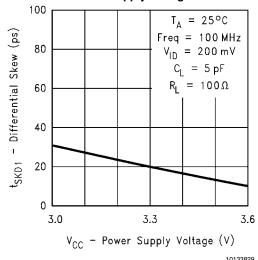

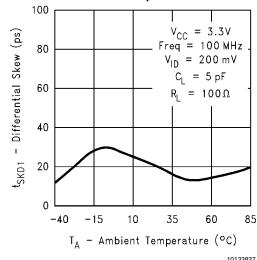

#### Differential Skew vs Power Supply Voltage

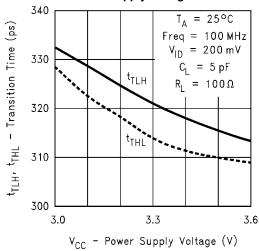

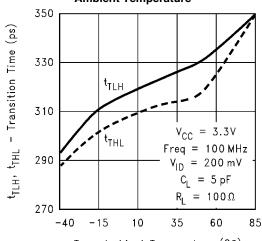

#### Transition Time vs Power Supply Voltage

#### Differential Skew vs Ambient Temperature

#### Transition Time vs Ambient Temperature

$T_A$  - Ambient Temperature (°C)

10133838

10133830

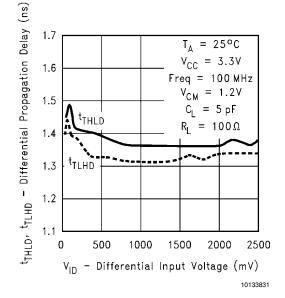

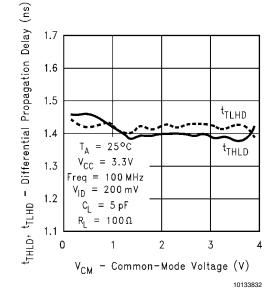

#### Differential Propagation Delay vs Differential Input Voltage

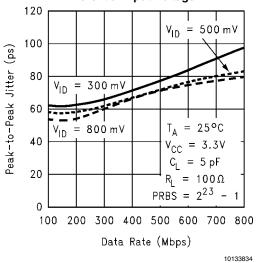

#### Peak-to-Peak Output Jitter at $V_{CM} = 0.4V \text{ vs}$ Differential Input Voltage

#### Differential Propagation Delay vs Common-Mode Voltage

#### Peak-to-Peak Output Jitter at V<sub>CM</sub> = 2.9V vs Differential Input Voltage

10133835

#### Peak-to-Peak Output Jitter at $V_{CM} = 1.2V \text{ vs}$ Differential Input Voltage

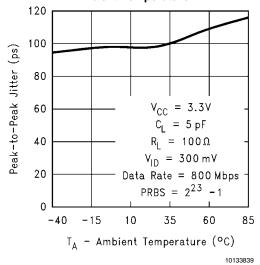

#### Peak-to-Peak Output Jitter at V<sub>CM</sub> = 1.2V vs Ambient Temperature

# Physical Dimensions inches (millimeters) unless otherwise noted

## **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | Design Support          |                                |  |  |

|--------------------------------|------------------------------|-------------------------|--------------------------------|--|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |  |  |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |  |  |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |  |  |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |  |  |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |  |  |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |  |  |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |  |  |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |  |  |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |  |  |

| Switching Regulators           | www.national.com/switchers   |                         |                                |  |  |

| LDOs                           | www.national.com/ldo         |                         |                                |  |  |

| LED Lighting                   | www.national.com/led         |                         |                                |  |  |

| PowerWise                      | www.national.com/powerwise   |                         |                                |  |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |  |  |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |  |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |  |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email:

new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com