December 2001

# MM5452/MM5453 Liquid Crystal Display Drivers General Description

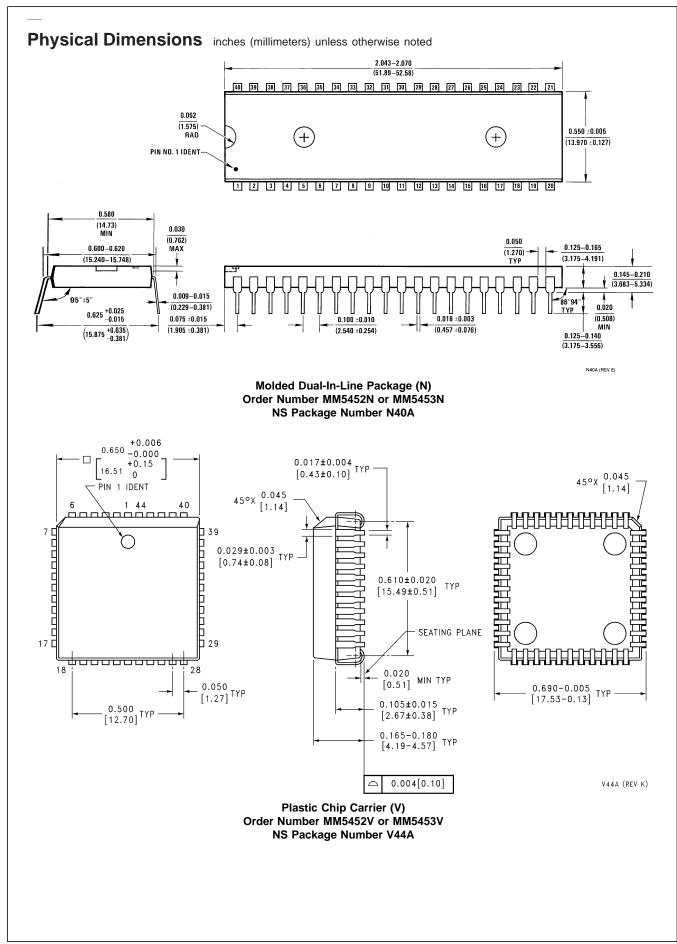

The MM5452 is a monolithic integrated circuit utilizing CMOS metal gate, low threshold enhancement mode devices. It is available in a 40-pin molded package. The chip can drive up to 32 segments of LCD and can be paralleled to increase this number. The chip is capable of driving a  $41/_2$ -digit 7-segment display with minimal interface between the display and the data source.

The MM5452 stores display data in latches after it is clocked in, and holds the data until new display data is received.

#### Features

- Serial data input

- No load signal required

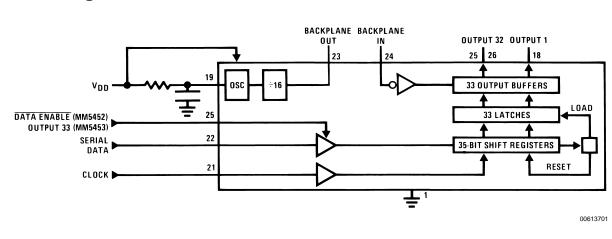

Block Diagram

- DATA ENABLE (MM5452)

Wide power supply operation

- Wide power supply operation

- TTL compatibility

- 32 or 33 outputs

- Alphanumeric and bar graph capability

- Cascaded operation capability

## Applications

- COPS<sup>™</sup> or microprocessor displays

- Industrial control indicator

- Digital clock, thermometer, counter, voltmeter

- Instrumentation readouts

- Remote displays

FIGURE 1.

© 2001 National Semiconductor Corporation DS006137

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| 10V |

|-----|

|     |

| 0°C |

| mW  |

| mW  |

| 0°C |

|     |

Lead Temperature (Soldering, 10s)

300°C

# Recommended Operating Conditions

V<sub>DD</sub> Operating Temperature 3V to 10V -40°C to 85°C

**Electrical Characteristics**  $T_A$  within operating range,  $V_{DD}$  = 3.0V to 10V,  $V_{SS}$  = 0V unless otherwise specified.

| Parameter                                  | Conditions                                              | Min  | Тур  | Max   | Units |

|--------------------------------------------|---------------------------------------------------------|------|------|-------|-------|

| Supply Voltage, V <sub>DD</sub>            |                                                         | 3    |      | 10    | V     |

| Average Supply Current, I <sub>DD</sub>    | All Outputs Open, Clock=Gnd,                            |      |      |       |       |

|                                            | Data=Gnd,OSC=Gnd, BP_IN @ 32Hz                          |      |      |       |       |

|                                            | $V_{DD}$ = 5V                                           |      |      | 10    | μA    |

|                                            | $V_{DD}$ = 10V                                          |      |      | 40    | μA    |

| Input Logical '0' Voltage, V <sub>IL</sub> | V <sub>DD</sub> = 3V                                    |      |      | 0.4   | V     |

|                                            | V <sub>DD</sub> = 5V                                    |      |      | 0.8   | V     |

|                                            | V <sub>DD</sub> = 10V                                   |      |      | 0.8   | V     |

| Input Logical '1' Voltage, V <sub>IH</sub> | V <sub>DD</sub> = 3V                                    | 2.0  |      |       | V     |

|                                            | V <sub>DD</sub> = 5V                                    | 2.0  |      |       | V     |

|                                            | V <sub>DD</sub> = 10V                                   | 8.0  |      |       | V     |

| Segment Sink Current, I <sub>OL</sub>      | V <sub>DD</sub> = 3V, V <sub>OUT</sub> = 0.3V           | -20  | -40  |       | μA    |

| Segment Source Current, I <sub>OH</sub>    | V <sub>DD</sub> = 3V, V <sub>OUT</sub> = 2.7V           | 20   | 40   |       | μA    |

| Backplane Out Sink Current,                | V <sub>DD</sub> = 3V, V <sub>OUT</sub> = 0.3V           | -320 | -500 |       | μΑ    |

| I <sub>OL</sub>                            |                                                         |      |      |       |       |

| Backplane Out Source                       | V <sub>DD</sub> = 3V, V <sub>OUT</sub> = 2.7V           | 320  | 500  |       | μA    |

| Current, I <sub>OH</sub>                   |                                                         |      | 500  |       | μΑ    |

| Segment Output Offset                      | Segment Load = 250pF (Note 2)                           |      | +/-5 | +/-50 | mV    |

| Voltage                                    |                                                         |      |      | 17 50 |       |

| Backplane Output Offset                    | Backplane Load = 8750pF (Note 2)                        |      |      | +/-50 | mV    |

| Voltage                                    |                                                         |      |      | .,    |       |

| Backplane Out Frequency                    | $R_{OSC_{IN}}$ = 50k $\Omega$ , $C_{OSC_{IN}}$ = 0.01µF |      | 75   |       | Hz    |

| Clock Input Frequency, f <sub>CLOCK</sub>  | V <sub>DD</sub> = 3V (Notes 2, 3)                       |      |      | 500   | kHz   |

|                                            | V <sub>DD</sub> = 5V (Note 2)                           |      |      | 750   | kHz   |

|                                            | V <sub>DD</sub> = 10V (Note 2)                          |      |      | 1.0   | MHz   |

| Clock Input Duty Cycle                     |                                                         | 40   |      | 60    | %     |

| Data Input Set-Up Time, t <sub>DS</sub>    |                                                         | 300  |      |       | ns    |

| Data Input Hold Time, t <sub>DH</sub>      |                                                         | 300  |      |       | ns    |

| DataEnable Set-up Time, t <sub>DES</sub>   |                                                         | 100  |      |       | ns    |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

Note 2: This parameter is guaranteed (but not production tested) over the operating temperature range and the operating supply voltage range. Not to be used in Q.A. testing.

**Note 3:** AC input waveform for test purposes:  $t_{f} \le 20ns$ ,  $t_{f} \le 20ns$ ,  $t_{CLOCK} = 500kHz$ , Duty Cycle = 50% ±10% **Note 4:** Clock input rise time ( $t_{f}$ ) and fall time ( $t_{f}$ ) must not exceed 300ns

#### **Functional Description**

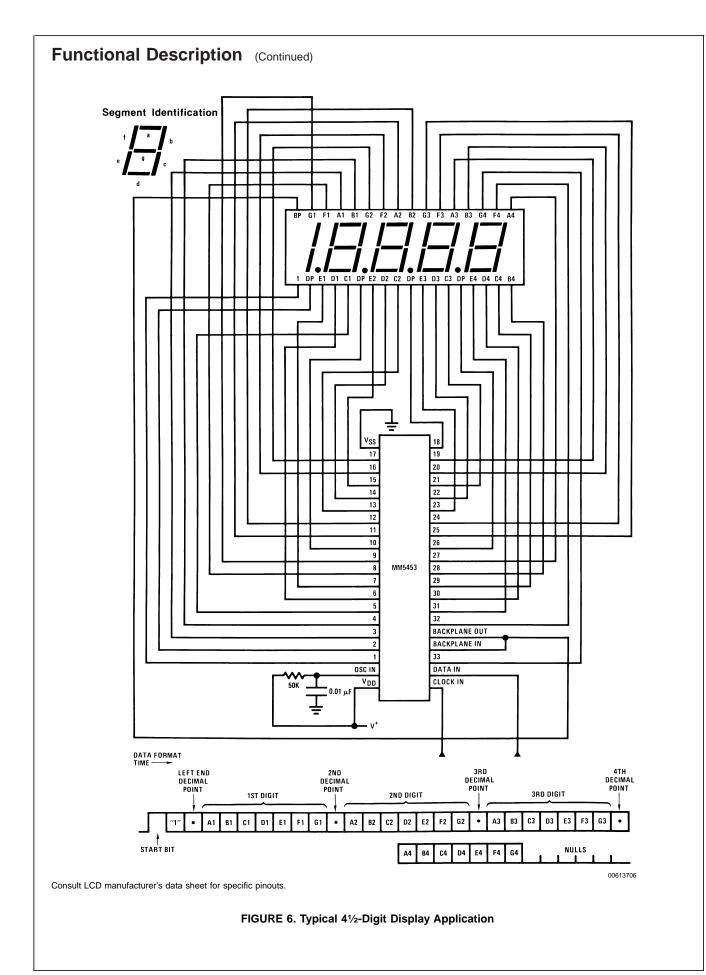

The MM5452 is specifically designed to operate 41/2-digit 7-segment displays with minimal interface with the display and the data source. Serial data transfer from the data source to the display driver is accomplished with 2 signals, serial data and clock. Since the MM5452 does not contain a character generator, the formatting of the segment information must be done prior to inputting the data to the MM5452. Using a format of a leading "1" followed by the 32 data bits allows data transfer without an additional load signal. The 32 data bits are latched after the 36th clock is complete, thus providing non-multiplexed, direct drive to the display. Outputs change only if the serial data bits differ from the previous time.

A block diagram is shown in *Figure 1*. For the MM5452 a DATA ENABLE is used instead of the 33rd output. If the DATA ENABLE signal is not required, the 33rd output can be brought out. This is the MM5453 device.

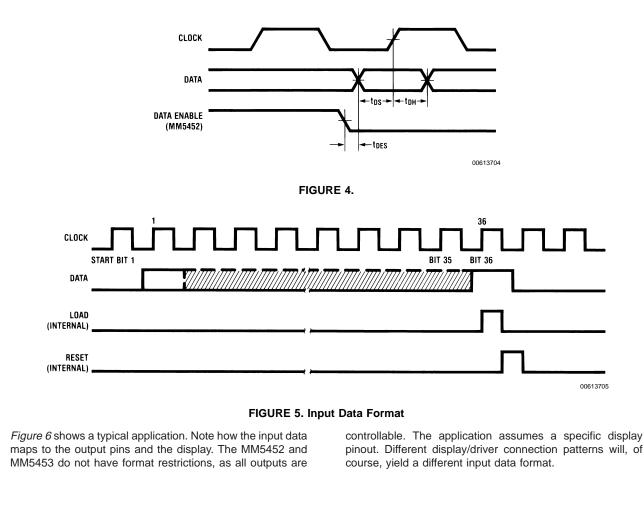

*Figure 5* shows the input data format. A start bit of logical "1" precedes the 32 bits of data. At the 36th clock a LOAD signal is generated synchronously with the high state of the clock, which loads the 32 bits of the shift registers into the latches. At the low state of the clock a RESET signal is generated which clears all the shift registers for the next set of data. The shift registers are static master-slave configuration. There is no clear for the master portion of the first shift register, thus allowing continuous operation.

If the clock is not continuous, there must be a complete set of 36 clocks otherwise the shift registers will not clear.

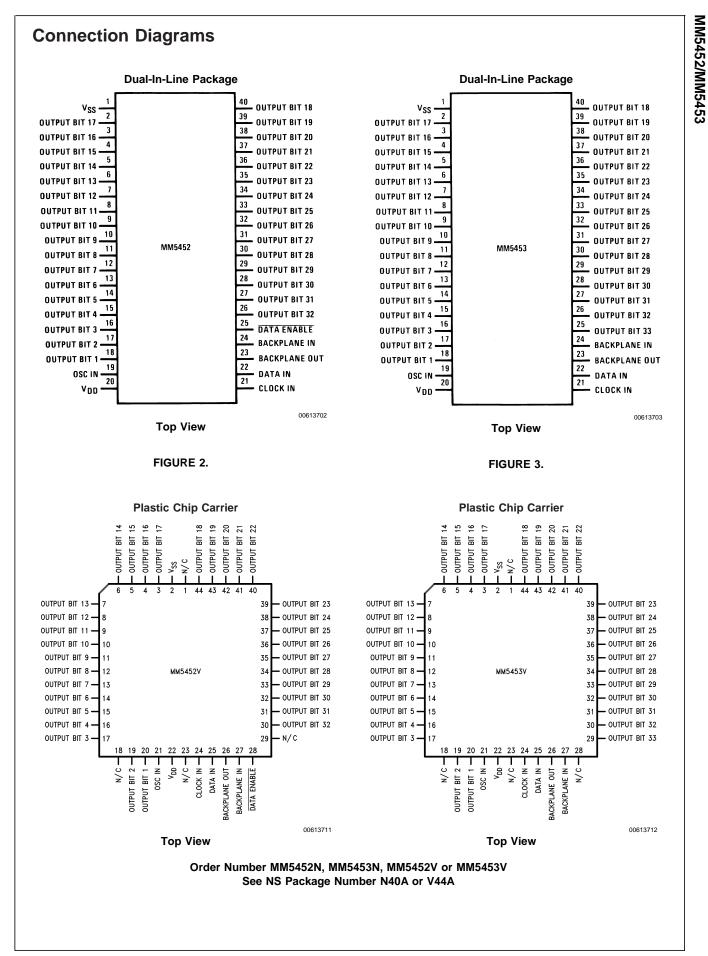

*Figure 2* shows the pin-out of the MM5452. Bit 1 is the first bit following the start bit and it will appear on pin 18.

*Figure 4* shows the timing relationships between data, clock and DATA ENABLE.

# MM5452/MM5453

#### Functional Description (Continued)

\*The minimum recommended value for R for the oscillator input is 9 k $\Omega$ . An RC time constant of approximately 4.91 x 10<sup>-4</sup> should produce a backplane frequency between 30 Hz and 150 Hz.

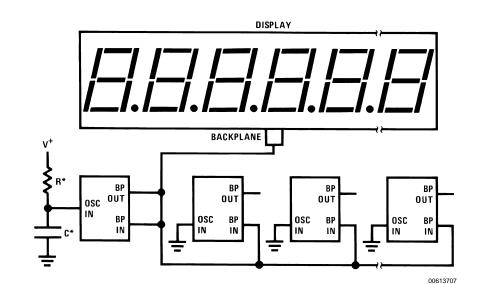

FIGURE 7. Parallel Backplane Outputs

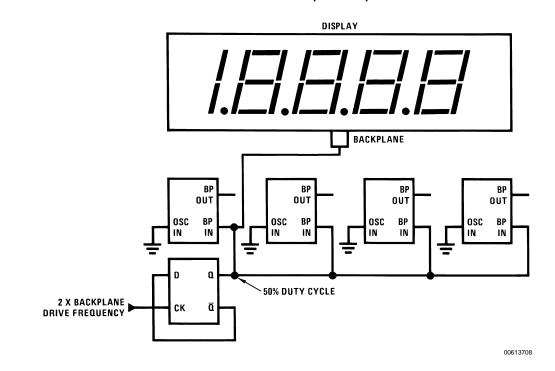

#### **FIGURE 8. External Backplane Clock**

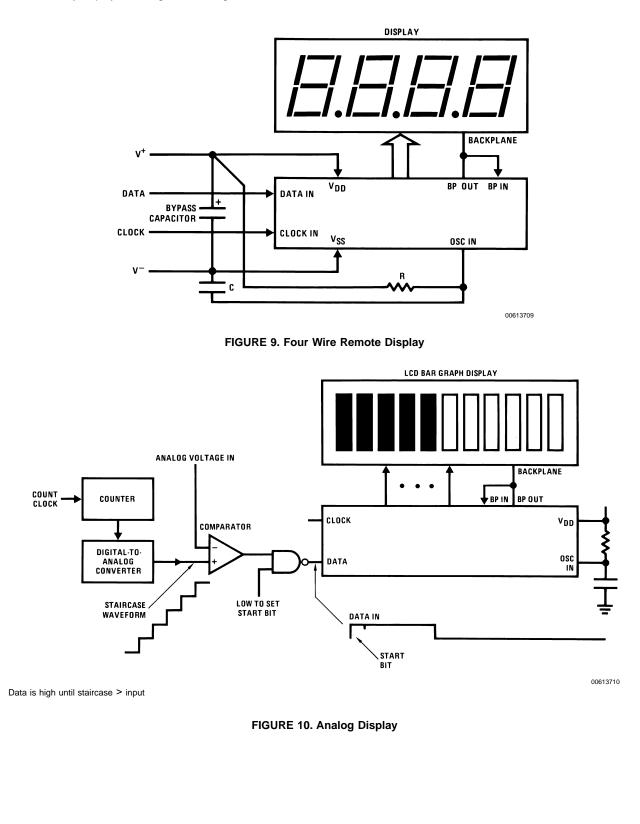

*Figure 9* shows a four wire remote display that takes advantage of the device's serial input to move many bits of display information on a few wires.

#### USING AN EXTERNAL CLOCK

The MM5452/MM5453 LCD Drivers can be used with an externally supplied clock, provided it has a duty cycle of 50%. Deviations from a 50% duty cycle result in an offset voltage on the LCD. In *Figure 8*, a flip-flop is used to assure

a 50% duty cycle. The oscillator input is grounded to prevent oscillation and reduce current consumptions in the chips. The oscillator is not used.

Using an external clock allows synchronizing the display drive with AC power, internal clocks, or DVM integration time to reduce interference from the display.

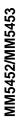

*Figure 10* is a general block diagram that shows how the device's serial input can be used to advantage in an analog display. The analog voltage input is compared with a staircase voltage generated by a counter and a digital-to-analog

### Functional Description (Continued)

converter or resistor array. The result of this comparison is clocked into the MM5452, MM5453. The next clock pulse increments the staircase and clocks the new data in.

With a buffer amplifier, the same staircase waveform can be used for many displays. The digital-to-analog converter need not be linear; logarithmic or other non-linear functions can be displayed by using weighted resistors or special DACs. This system can be used for status indicators, spectrum analyzers, audio level and power meters, tuning indicators, and other applications.

#### **Notes**

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas Email: support@nsc.com

National Semiconductor Europe

www.national.com

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com

Deutsch

Tel: +49 (0) 69 9508 6208 English

Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466 Email: ap.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.