# LM4865 Boomer® Audio Power Amplifier Series

# 750 mW Audio Power Amplifier with DC Volume Control and Headphone Switch

# **General Description**

The LM4865 is a mono bridged audio power amplifier with DC voltage volume control. The LM4865 is capable of delivering 750mW of continuous average power into an  $8\Omega$  load with less than 1% THD when powered by a 5V power supply. Switching between bridged speaker mode and headphone (single ended) mode is accomplished using the headphone sense pin. To conserve power in portable applications, the LM4865's micropower shutdown mode ( $I_Q=0.7\mu A,\ typ)$  is activated when less than 300mV is applied to the DC Vol/SD pin.

Boomer audio power amplifiers are designed specifically to provide high power audio output while maintaining high fidelity. They require few external components and operate on low supply voltages.

# **Applications**

- GSM phones and accessories, DECT, office phones

- Hand held radio

■ Other portable audio devices

## **Key Specifications**

Arr P<sub>O</sub> at 1.0% THD+N into 8Ω 750mW (typ) SO, micro SMD

$\blacksquare$  P<sub>O</sub> at 10% THD+N into 8Ω 1W (typ) SO, micro SMD

■ Shutdown current 0.7µA(typ) ■ Supply voltage range 2.7V to 5.5V

#### **Features**

- DC voltage volume control

- Headphone amplifier mode

- "Click and pop" suppression

- Shutdown control when volume control pin is low

- Thermal shutdown protection

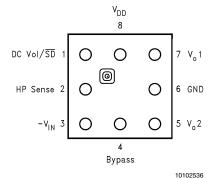

# **Connection Diagrams**

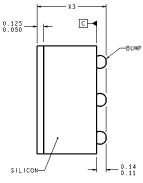

#### micro SMD Package

Top View Order Number LM4865IBP See NS Package Number BPA08CFB

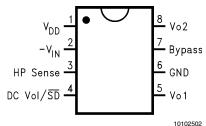

#### Small Outline Package (SO) Mini Small Outline Package (MSOP)

Top View Order Number LM4865M, LM4865MM See NS Package Number M08A, MUA08A

BOOMER™ is a trademark of National Semiconductor Corporation.

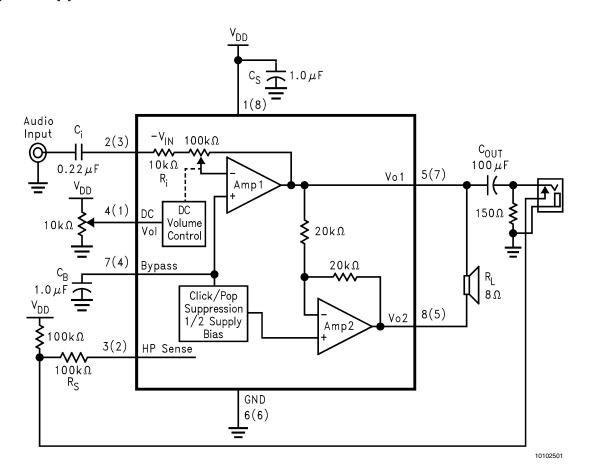

# **Typical Application**

FIGURE 1. Typical Audio Amplifier

Application Circuit

(Numbers in ( ) are specific to the micro SMD package)

# **Absolute Maximum Ratings** (Note 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage              | 6.0V                  |

|-----------------------------|-----------------------|

| Storage Temperature         | −65°C to +150°C       |

| Input Voltage               | –0.3V to $V_{\rm DD}$ |

|                             | +0.3V                 |

| Power Dissipation (Note 3)  | Internally Limited    |

| ESD Susceptibility (Note 4) | 2000V                 |

| ESD Susceptibility (Note 5) | 200V                  |

| Junction Temperature        | 150°C                 |

| Soldering Information       |                       |

Thermal Resistanc

| $\theta_{JC}$ (SOP)       | 35°C/W  |

|---------------------------|---------|

| $\theta_{JA}$ (SOP)       | 150°C/W |

| $\theta_{JC}$ (MSOP)      | 56°C/W  |

| $\theta_{JA}$ (MSOP)      | 190°C/W |

| $\theta_{JA}$ (micro SMD) | 150°C/W |

|                           |         |

# **Operating Ratings**

Temperature Range

| $T_{MIN} \le T_A \le T_{MAX}$ | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$ |

|-------------------------------|-----------------------------------------------------------------------|

| Supply Voltage                | $2.7V \le V_{DD} \le 5.5V$                                            |

See AN-450 "Surface Mounting and their Effects on Product Reliability" for other methods of soldering surface mount devices.

## Electrical Characteristics (Notes 1, 2)

Vapor Phase (60 sec.)

Infrared (15 sec.)

The following specifications apply for  $V_{DD}$  = 5V, unless otherwise specified. Limits apply for  $T_A$  = 25°C.

215°C

220°C

|                       |                                   |                                                                               | LM4865          |                     |                 |       |  |

|-----------------------|-----------------------------------|-------------------------------------------------------------------------------|-----------------|---------------------|-----------------|-------|--|

| Symbol                | Parameter                         | Conditions                                                                    | Min<br>(Note 7) | Typical<br>(Note 6) | Max<br>(Note 7) | Units |  |

| V <sub>DD</sub>       | Supply Voltage                    |                                                                               | 2.7             |                     | 5.5             | V     |  |

|                       | Quiescent Power Supply            | V <sub>IN</sub> = 0V, I <sub>O</sub> = 0A, HP Sense = 0V                      |                 | 4                   | 7               | mA    |  |

| I <sub>DD</sub>       | Current                           | V <sub>IN</sub> = 0V, I <sub>O</sub> - 0A, HP Sense = 5V                      |                 | 3.5                 | 6               | mA    |  |

| I <sub>SD</sub>       | Shutdown Current                  | $V_{PIN4} \le 0.3V$                                                           |                 | 0.7                 |                 | μA    |  |

| Vos                   | Output Offset Voltage             | $V_{IN} = 0V$                                                                 |                 | 5                   | 50              | mV    |  |

| Po                    | Output Power                      | THD = 1% (max), HP Sense < 0.8V,<br>$f = 1kHz$ , $R_L = 8\Omega$              | 500             | 750                 |                 | mW    |  |

|                       |                                   | THD = 10% (max), HP Sense < 0.8V,<br>$f = 1kHz$ , $R_L = 8\Omega$             |                 | 1.0                 |                 | W     |  |

|                       |                                   | THD + N = 1%, HP Sense > 4V,<br>$f = 1kHz$ , $R_L = 32\Omega$                 |                 | 80                  |                 | mW    |  |

|                       |                                   | THD = 10%, HP Sense > 4V,<br>f = 1kHz, $R_L = 32\Omega$                       |                 | 110                 |                 | mW    |  |

| THD+N                 | Total Harmonic Distortion + Noise | $P_O = 300 \text{ mWrms}, f = 20\text{Hz}-20\text{kHz},$<br>$R_L = 8\Omega$   |                 | 0.6                 |                 | %     |  |

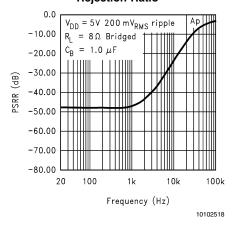

| PSRR                  | Power Supply Rejection Ratio      | $V_{RIPPLE}$ = 200mVrms, $R_L$ = 8 $\Omega$ , $C_B$ = 1.0 $\mu$ F, $f$ = 1kHz |                 | 50                  |                 | dB    |  |

| Gain <sub>RANGE</sub> | Single-Ended Gain Range           | Gain with $V_{PIN4} \ge 4.0V$ , (80% of $V_{DD}$ )                            | 18.8            | 20                  |                 | dB    |  |

|                       |                                   | Gain with $V_{PIN4} \le 0.9V$ , (18% of $V_{DD}$ )                            | -70             | -72                 |                 | dB    |  |

| V <sub>IH</sub>       | HP Sense High Input Voltage       |                                                                               | 4               |                     |                 | V     |  |

| V <sub>IL</sub>       | HP Sense Low Input Voltage        |                                                                               |                 |                     | 0.8             | V     |  |

Note 1: All voltages are measured with respect to the ground pin, unless otherwise specified.

Note 2: "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur. "Operating Ratings" indicate conditions for which the device is functional, but do not guarantee specific performance limits. "Electrical Characteristics" state DC and AC electrical specifications under particular test conditions that guarantee specific performance limits. This assumes that the device operates within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given. The typical value, however, is a good indication of device performance.

Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower. For the LM4865M,  $T_{JMAX} = 150^{\circ}C$ .

**Note 4:** Human body model, 100pF discharged through a 1.5k $\Omega$  resistor.

Note 5: Machine Model, 220pF-240pF discharged through all pins.

Note 6: Typicals are measured at 25°C and represent the parametric norm.

Note 7: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 8: The quiescent power supply current depends on the offset voltage when a practical load is connected to the amplifier.

# **External Components Description**

(Figure 1)

| Comp | onents         | Functional Description                                                                                                                                                                                                                                                                                                                                                          |

|------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.   | C <sub>i</sub> | Input coupling capacitor which blocks the DC voltage at the amplifier's input terminals. It also creates a highpass filter with the internal $R_i$ . The designer should note that 10kOhm<(Ri)<110kOhm. Therefore $f_c = 1/(2\pi R_i C_i)$ . Refer to the section, <b>Proper Selection of External Components</b> , for an explanation of how to determine the value of $C_i$ . |

| 2.   | Cs             | Supply bypass capacitor which provides power supply filtering. Refer to the <b>Power Supply Bypassing</b> section for information concerning proper placement and selection of the supply bypass capacitor.                                                                                                                                                                     |

| 3.   | Св             | Bypass pin capacitor which provides half-supply filtering. Refer to the section, <b>Proper Selection of External Components</b> , for information concerning proper placement and selection of C <sub>B</sub> .                                                                                                                                                                 |

# **Typical Performance Characteristics**

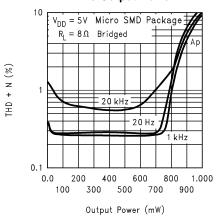

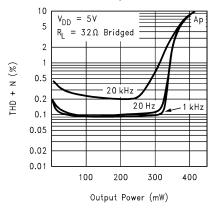

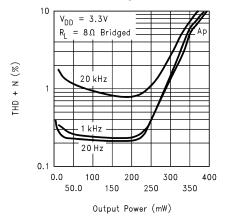

#### THD+N vs Output Power

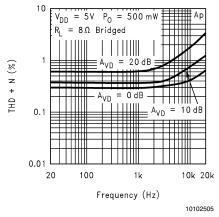

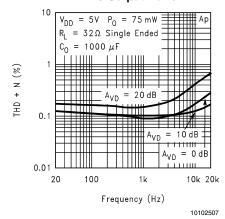

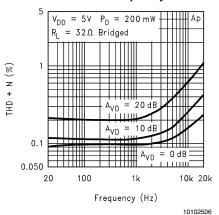

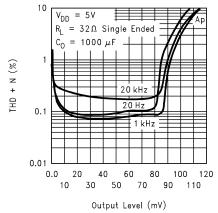

#### THD+N vs Frequency

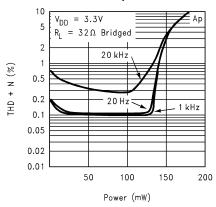

#### THD+N vs Output Power

10102508

#### THD+N vs Output Power

10102510

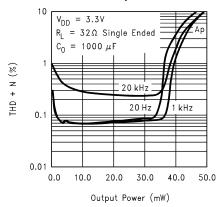

## THD+N vs Output Power

10102511

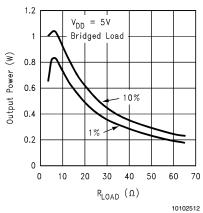

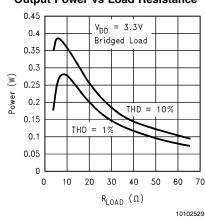

#### Power Dissipation vs Load Resistance

**Power Derating Curve** 0.9 8.0 0.7 Power 0.6 - M08A Dissipated 0.5 0.4 0.3 Мах MUA08A 0.2 0.1 0 20 40 60 80 100 120 140 160

Ambient Temp (°C)

10102514

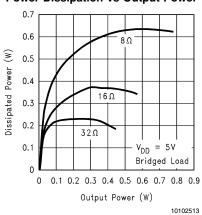

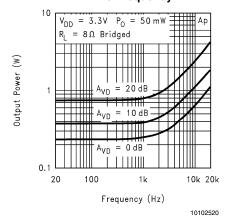

#### **Power Dissipation vs Output Power**

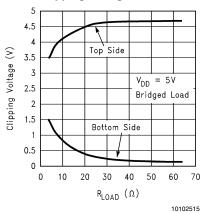

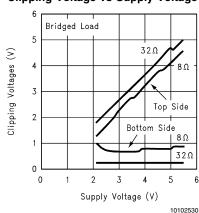

Clipping Voltage vs RL

#### Power Supply Rejection Ratio

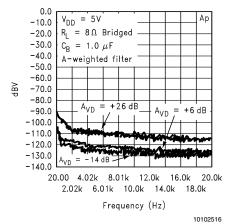

#### THD+N vs Frequency

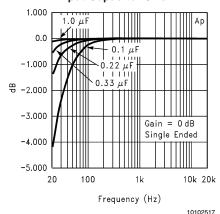

# Frequency Response vs Input Capacitor Size

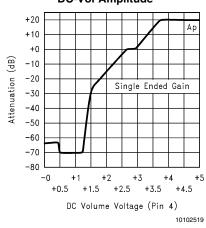

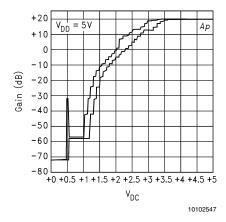

# Attenuation Level vs DC-Vol Amplitude

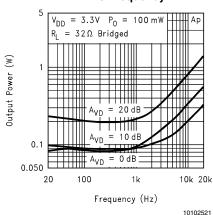

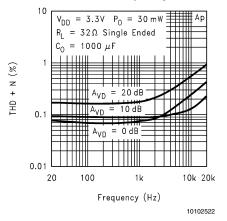

#### THD+N vs Frequency

#### THD+N vs Frequency

#### THD+N vs Output Power

10102523

#### THD+N vs Output Power

10102524

#### THD+N vs Output Power

10102528

#### **Output Power vs Load Resistance**

#### Clipping Voltage vs Supply Voltage

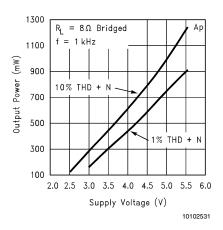

#### **Output Power vs Supply Voltage**

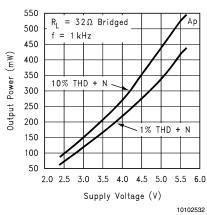

# Output Power vs Supply Voltage

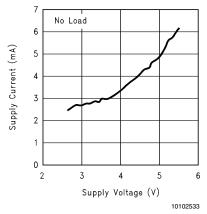

#### Supply Current vs Supply Voltage

# Application Information

#### **BRIDGE CONFIGURATION EXPLANATION**

As shown in Figure 1, the LM4865 consists of two operational amplifiers internally. An external DC voltage sets the closed-loop gain of the first amplifier, whereas two internal  $20k\Omega$  resistors set the second amplifier's gain at -1. The LM4865 can be used to drive a speaker connected between the two amplifier outputs or a monaural headphone connected between  $V_{\rm O}1$  and GND.

Figure 1 shows that the output of Amp1 serves as the input to Amp2. This results in both amplifiers producing signals that are identical in magnitude, but 180° out of phase.

Taking advantage of this phase difference, a load placed between  $V_{\rm O}1$  and  $V_{\rm O}2$  is driven differentially (commonly referred to as "bridge mode"). This mode is different from single-ended driven loads that are connected between a single amplifier's output and ground.

Bridge mode has a distinct advantage over the single-ended configuration: its differential drive to the load doubles the output swing for a specified supply voltage. This results in four times the output power when compared to a single-ended amplifier under the same conditions. This increase in attainable output assumes that the amplifier is not current limited or the output signal is not clipped. To ensure

minimum output signal clipping when choosing an amplifier's closed-loop gain, refer to the **Audio Power Amplifier Design** section.

Another advantage of the differential bridge output is no net DC voltage across load. This results from biasing  $V_O1$  and  $V_O2$  at half-supply. This eliminates the coupling capacitor that single supply, single-ended amplifiers require. Eliminating an output coupling capacitor in a single-ended configuration forces a single supply amplifier's half-supply bias voltage across the load. The current flow created by the half-supply bias voltage increases internal IC power dissipation and may permanently damage loads such as speakers.

#### **POWER DISSIPATION**

Power dissipation is a major concern when designing a successful bridged or single-ended amplifier. Equation (1) states the maximum power dissipation point for a single-ended amplifier operating at a given supply voltage and driving a specified output load.

$$P_{DMAX} = (V_{DD})^2/(2\pi^2 R_L)$$

Single-Ended (1)

However, a direct consequence of the increased power delivered to the load by a bridge amplifier is an increase in internal power dissipation point for a bridge amplifier operating at the same given conditions.

$$P_{DMAX} = 4*(V_{DD})^2/(2\pi^2R_L) \quad Bridge Mode \qquad (2)$$

The LM4865 has two operational amplifiers in one package and the maximum internal power dissipation is 4 times that

of a single-ended amplifier. However, even with this substantial increase in power dissipation, the LM4865 does not require heatsinking. From Equation (2), assuming a 5V power supply and an  $8\Omega$  load, the maximum power dissipation point is 633 mW. The maximum power dissipation point obtained from Equation (2) must not be greater than the power dissipation that results from Equation (3):

$$P_{DMAX} = (T_{JMAX} - T_A)/\theta_{JA}$$

(3)

For the micro SMD and SO packages,  $\theta_{JA} = 150^{\circ}$ C/W. The MSO package has a 190°C/W  $\theta_{JA}$ .  $T_{JMAX} = 150$ °C for the LM4865. For a given ambient temperature T<sub>A</sub>, Equation (3) can be used to find the maximum internal power dissipation supported by the IC packaging. If the result of Equation (2) is greater than that of Equation (3), then either decrease the supply voltage, increase the load impedance, or reduce the ambient temperature. For a typical application using the micro SMD or SO packaged LM4865, a 5V power supply, and an  $8\Omega$  load, the maximum ambient temperature that does not violate the maximum junction temperature is approximately 55°C. The maximum ambient temperature for the MSO package with the same conditions is approximately 30°C. These results further assume that a device is a surface mount part operating around the maximum power dissipation point. Since internal power dissipation is a function of output power, higher ambient temperatures are allowed as output power decreases. Refer to the Typical Performance Characteristics curves for power dissipation information at lower output power levels.

#### **POWER SUPPLY BYPASSING**

As with any power amplifier, proper supply bypassing is critical for low noise performance and high power supply rejection. The capacitors connected to the bypass and power supply pins should be placed as close to the LM4865 as possible. The capacitor connected between the bypass pin and ground improves the internal bias voltage's stability, producing improved PSRR. The improvements to PSRR increase as the bypass pin capacitor value increases. Typical applications employ a 5V regulator with 10µF and a 0.1µF filter capacitors that aid in supply stability. Their presence, however does not eliminate the need for bypassing the supply nodes of the LM4865. The selection of bypass capacitor values, especially CB, depends on desired PSRR requirements, click and pop performance (as explained in the section, Proper Selection of External Components), system cost, and size constraints.

#### DC VOLTAGE VOLUME CONTROL

The LM4865 has internal volume control that is controlled by the DC voltage applied its DC Vol/ $\overline{\text{SD}}$  pin (pin 5 on the micro SMD and pin 4 on the MSOP and SOP packages). The volume control's input range is from GND to V<sub>DD</sub>. A graph showing a typical volume response versus input control voltage is shown in the **Typical Performance Characteristics**section. The DC Vol/ $\overline{\text{SD}}$  pin also functions as the control pin for the LM4865's micropower shutdown feature. See the**Shutdown Function** section for more information.

Like all volume controls, the LM4865's internal volume control is set while listening to an amplified signal that is applied to an external speaker. The actual voltage applied to the DC Vol/SD pin is a result of the volume a listener desires. As such, the volume control is designed for use in a feedback system that includes human ears and preferences. This feedback system operates guite well without the need for

accurate gain. The user simply sets the volume to the desired level as determined by their ear, without regard to the actual DC voltage that produces the volume. Therefore, the accuracy of the volume control is not critical, as long as volume changes monotonically and step size is small enough to reach a desired volume that is not too loud or too soft. Since gain accuracy is not critical, there will be volume variation from part-to-part even with the same applied DC control voltage. The gain of a given LM4865 can be set with a fixed external voltage, but another LM4865 may require a different control voltage to achieve the same gain. Figure 2 is a curve showing the volume variation of twenty typical LM4865s as the voltage applied to the DC Vol/SD pin is varied. For gains greater than unity, the typical part-to-part variation can be as large as 8dB for the same control voltage.

FIGURE 2. Typical part-to-part gain variation as a function of DC-Vol control voltage

#### **MUTE AND SHUTDOWN FUNCTION**

The LM4865's mute and shutdown functions are controlled through the DC Vol/SD pin. Mute is activated by applying a voltage in the range of 500mV to 1V. A typical attenuation of 75dB is achieved is while mute is active. The LM4865's micropower shutdown mode turns off the amplifier's bias circuitry. The micropower shutdown mode is activated by applying less than 300mV<sub>DC</sub> to the DC Vol/SD pin. When shutdown is active, they supply current is reduced to 0.7µA (typ). A degree of uncertainty exists when the voltage applied to the DC Vol/SD pin is in the range of 300mV to 500mV. The LM4865 can be in mute, still fully powered, or in micropower shutdown and fully muted. In mute mode, the LM4865 draws the typical quiescent supply current. The DC Vol/SD pin should be tied to GND for best shutdown mode performance. As the DC Vol/SD is increased above 0.5V the amplifier will follow the attenuation curve in Typical Performance Characteristics.

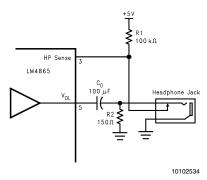

#### **HP-Sense FUNCTION**

Applying a voltage between 4V and  $V_{\rm CC}$  to the LM4865's HP-Sense headphone control pin turns off Amp2 and mutes a bridged-connected load. Quiescent current consumption is reduced when the IC is in this single-ended mode.

Figure 3 shows the implementation of the LM4865's headphone control function. With no headphones connected to the headphone jack, the R1-R2 voltage divider sets the

voltage applied to the HP-Sense pin (pin 3) at approximately 50mV. This 50mV enables the LM4865 and places it in bridged mode operation.

While the LM4865 operates in bridged mode, the DC potential across the load is essentially 0V. Since the HP-Sense threshold is set at 4V, even in an ideal situation, the output swing cannot cause a false single-ended trigger. Connecting headphones to the headphone jack disconnects the headphone jack contact pin from  $\rm V_{\rm O}1$  and allows R1 to pull the HP Sense pin up to  $\rm V_{\rm CC}$ . This enables the headphone function, turns off Amp2, and mutes the bridged speaker. The amplifier then drives the headphones, whose impedance is in parallel with resistor R2. Resistor R2 has negligible effect on output drive capability since the typical impedance of headphones is  $32\Omega$ . The output coupling capacitor blocks the amplifier's half supply DC voltage, protecting the headphones.

A microprocessor or a switch can replace the headphone jack contact pin. When a microprocessor or switch applies a voltage greater than 4V to the HP Sense pin, a bridge-connected speaker is muted and Amp1 drives the headphones.

#### PROPERLY SELECTING EXTERNAL COMPONENTS

Optimizing the LM4865's performance requires properly selecting external components. Though the LM4865 operates well when using external components having wide tolerances, the best performance is achieved by optimizing component values.

FIGURE 3. Headphone Circuit

#### Input Capacitor Value Selection

Amplification of the lowest audio frequencies requires high value input coupling capacitors. These high value capacitors can be expensive and may compromise space efficiency in portable designs. In many cases, however, the speakers used in portable systems, whether internal or external, have little ability to reproduce signals below 150Hz. In application 5 using speakers with this limited frequency response, a large input capacitor will offer little improvement in system performance.

Figure 1 shows that the nominal input impedance (R<sub>IN</sub>) is  $10k\Omega$  at maximum volume and  $110k\Omega$  at minimum volume. Together, the input capacitor, C<sub>i</sub>, and R<sub>IN</sub>, produce a -3dB high pass filter cutoff frequency that is found using Equation (4).

$$f_{-3 dB} = \frac{1}{2\pi R_{IN} C_{i}}$$

(4)

As the volume changes from minimum to maximum,  $R_{IN}$  decrease from  $110k\Omega$  to  $10k\Omega.$  Equation (4) reveals that the -3dB frequency will increase as the volume increases. The nominal value of  $C_i$  for lowest desired frequency response should be calculated with  $R_{IN}=10k\Omega$ . As an example when using a speaker with a low frequency limit of 150Hz,  $C_i$ , using Equation (4) is  $0.1\mu F$ . The  $0.22\mu F$   $C_i$  shown in Figure 1 is optimized for a speaker whose response extends down to 75Hz.

#### **Bypass Capacitor Value Selection**

Besides minimizing the input capacitor size, careful consideration should be paid to value of the bypass capacitor  $C_{\rm B}.$  Since  $C_{\rm B}$  determines how fast the LM4865 turns on, its value is the most critical when minimizing turn-on pops. The slower the LM4865's outputs ramp to their quiescent DC voltage (nominally  $V_{\rm DD}/2$ ), the smaller the turn-on pop. Choosing  $C_{\rm B}$  equal to 1.0µF, along with a small value of  $C_{\rm i}$  (in the range of 0.1µF to 0.39µF), produces a clickless and popless shutdown function. Choosing  $C_{\rm i}$  as small as possible helps minimize clicks and pops.

#### **CLICK AND POP CIRCUITRY**

The LM4865 contains circuitry that minimizes turn-on and shutdown transients or 'clicks and pops'. For this discussion, turn-on refers to either applying the power supply voltage or when the shutdown mode is deactivated. While the power supply is ramping to its final value, the LM4865's internal amplifiers are configured as unity gain buffers. An internal current source changes the voltage of the bypass pin in a controlled, linear manner. Ideally, the input and outputs track the voltage applied to the bypass pin. The gain of the internal amplifiers remains unity until the voltage on the bypass pin reaches 1/2  $\rm V_{\rm DD}$ . As soon as the voltage on the bypass pin is stable, the device becomes fully operational and the gain is set by the external voltage applied to the DC Vol/ $\overline{\rm SD}$  pin.

Although the bypass pin current cannot be modified, changing the size of  $C_B$  alters the device's turn-on time and the magnitude of 'clicks and pops'. Increasing the value of  $C_B$  reduces the magnitude of turn-on pops. However, this presents a tradeoff: as the size of  $C_B$  increases, the turn-on time increases. There is a linear relationship between the size of CB and the turn-on time. Shown below are some typical turn-on times for various values of  $C_B$ :

| Св     | T <sub>ON</sub> |

|--------|-----------------|

| 0.01µF | 20ms            |

| 0.1µF  | 200ms           |

| 0.22µF | 420ms           |

| 0.47µF | 840ms           |

| 1.0µF  | 2sec            |

In order eliminate 'clicks and pops', all capacitors must be discharged before turn-on. Rapidly switching  $V_{DD}$  may not allow the capacitors to fully discharge, which may cause 'clicks and pops'. In a single-ended configuration, the output coupling capacitor,  $C_{OUT},$  is of particular concern. This capacitor discharges through an internal  $20k\Omega$  resistor. Depending on the size of  $C_{OUT},$  the time constant can be relatively large. To reduce transients in single-ended mode,

an external  $1k\Omega$  -  $5k\Omega$  resistor can be placed in parallel with the internal  $20k\Omega$  resistor. The tradeoff for using this resistor is increased quiescent current.

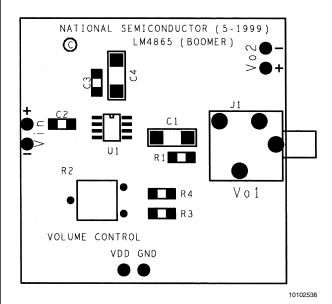

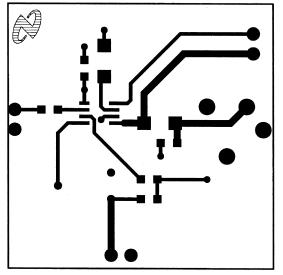

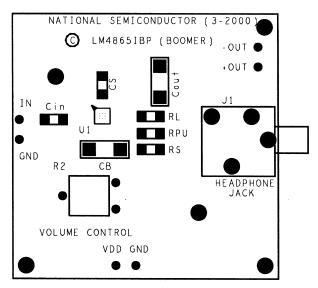

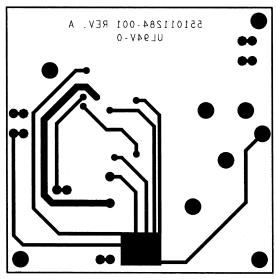

#### RECOMMENDED PRINTED CIRCUIT BOARD LAYOUT

Figure 4 through Figure 6 show the recommended two-layer PC board layout that is optimized for the SO-8 packaged LM4865 and associated external components. Figure 7 through Figure 11 show the recommended four-layer PC board layout for the micro SMD packaged LM4865. A four-layer board is recommended when using the micro SMD packaged LM4865: the two inner layers, one connected to the GND pin, the other to the V<sub>DD</sub> pin, provide heatsinking. Both layouts are designed for use with an external 5V supply, 8Ω speakers, and 32Ω headphones. The schematic for both recommended PC board layouts is Figure 1

Both circuit boards are easy to use. Apply a 5V supply voltage and ground to the board's  $V_{\text{DD}}$  and GND pads, respectively. Connect a speaker with an  $8\Omega$  minimum impedance between the board's -OUT and +OUT pads. For headphone use, the layout has provisions for a headphone jack, J1. When a jack is connected as shown, inserting a headphone plug automatically switches off the external speaker.

FIGURE 4. Recommended SO PC board layout: component side silkscreen

10102539

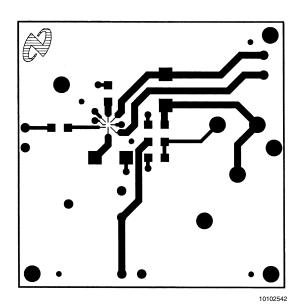

FIGURE 5. Recommended SO PC board layout: component side layout

10102540

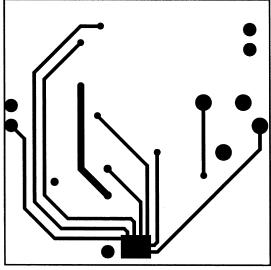

FIGURE 6. Recommended SO PC board layout: bottom side layout

10102541

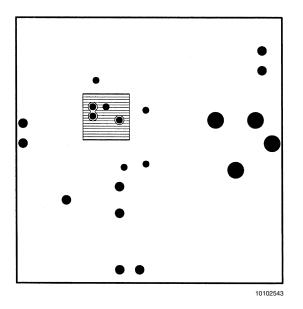

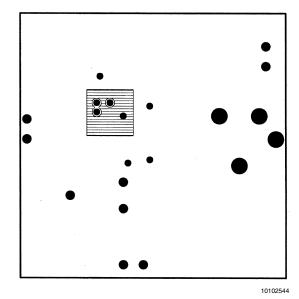

FIGURE 7. Recommended micro SMD PC board layout: component side silkscreen

FIGURE 8. Recommended micro SMD PC board layout: component side layout

FIGURE 9. Recommended micro SMD PC board layout: Inner layer  $V_{\text{CC}}$  layout

FIGURE 10. Recommended micro SMD PC board layout:

Inner layer ground layout

1010254

FIGURE 11. Recommended micro SMD PC board layout:

bottom side layout

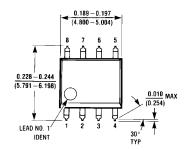

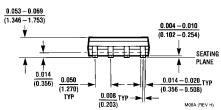

# Physical Dimensions inches (millimeters) unless otherwise noted

Order Number LM4865M NS Package Number M08A

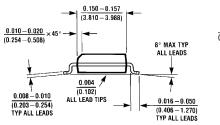

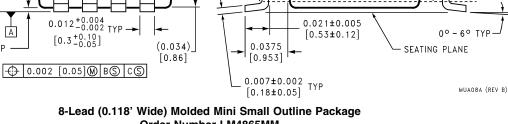

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued) 0.118±0.004 В $[3 \pm 0.1]$ C (0.189) [4.8] 0.118±0.004 0.193±0.004 [4.9±0.1] $[3 \pm 0.1]$ (0.040)TYP [1.02] PIN 1 IDENT NOTE 2 (0.016)(0.0256) TYP [0.41] [0.65]LAND PATTERN RECOMMENDATION (0.0256) TYP [0.65] √R 0.005 TYP GAGE PLANE 0.043 [1.09] R 0.005 TYP MAX(0.010) [0.25]

Order Number LM4865MM **NS Package Number MUAO8A**

○ 0.002[0.05] A

0.002-0.006 TYP

[0.06-0.15]

À

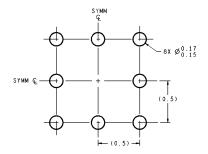

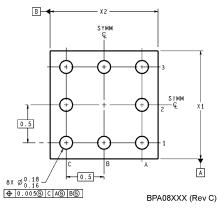

## Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

DIMENSIONS ARE IN MILLIMETERS

#### LAND PATTERN RECOMMENDATION

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor

Americas Customer

Support Center

Email: new feedback@nsc.ci

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Fax: 65-6250 4466 Email: ap.support@nsc.com Tel: 65-6254 4466 National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: nsj.crc@jksmtp.nsc.com Tel: 81-3-5639-7560

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.