# High Voltage High Current LED Driver Controller for Buck Boost, or Buck-Boost Topology

### **General Description**

The RT8482 is a current mode PWM controller designed to drive an external MOSFET for high current LED applications. With a current sense amplifier threshold of 190mV, the LED current is programmable with one external current sense resistor. With a maximum operating input voltage of 36V and output voltage up to 48V, the RT8482 is ideal for buck, boost or buck-boost operation.

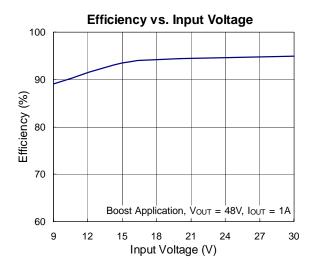

With 350kHz operating frequency, the external inductor and capacitors can be small while maintaining high efficiency.

Dimming can be either analog or PWM digital. The unique built-in clamping comparator and filter allow easy low noise analog dimming conversion from PWM signal with only one external capacitor.

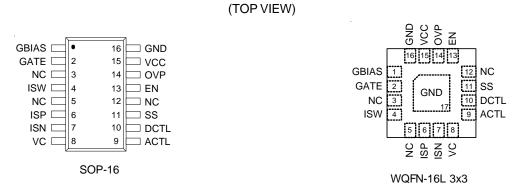

The RT8482 is available in WQFN-16L 3x3 and SOP-16 packages.

# Ordering Information

RT8482 PD Package Type

S: SOP-16

QW: WQFN-16L 3x3 (W-Type)

Operating Temperature Range

G: Green (Halogen Free with Commercial Standard)

#### Note:

Richtek Green products are:

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

#### **Features**

- High Voltage Capability: V<sub>IN</sub> Up to 36V, V<sub>OUT</sub> Up to 48V

- Buck, Boost or Buck Boost Operation

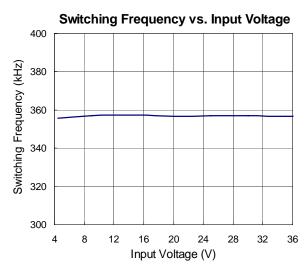

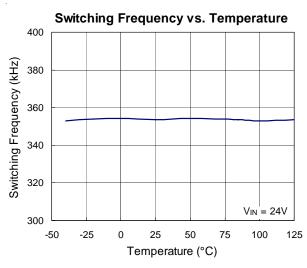

- Current Mode PWM with 350kHz Switching Frequency

- Easy Dimming: Analog, PWM Digital or PWM Converting to Analog with One External Capacitor

- Programmable Soft Start to Avoid Inrush Current

- Programmable Over Voltage Protection

- VIN Under Voltage Lockout and Thermal Shutdown

- 16-Lead WQFN and SOP Packages

- RoHS Compliant and Halogen Free

### **Applications**

- General Industrial High Power LED Lighting

- Desk Lights and Room Lighting

- · Building and Street Lighting

- · Industrial Display Backlight

# **Marking Information**

RT8482GS: Product Number YMDNN: Date Code

SOP-16

H9=YM DNN

H9=: Product Code YMDNN: Date Code

WQFN-16L 3x3

DS8482-00 August 2010

www.richtek.com

# **Pin Configurations**

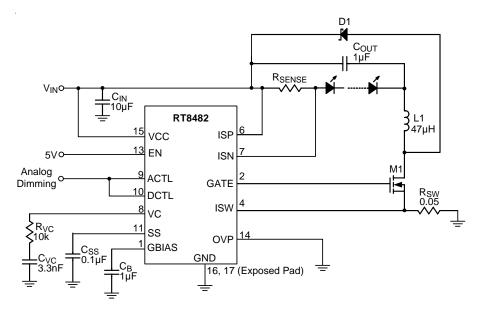

# **Typical Application Circuit**

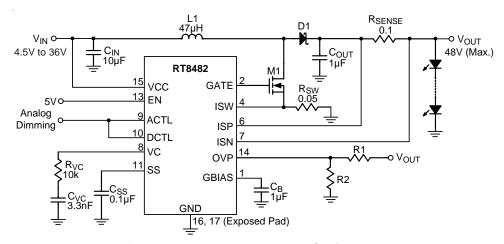

Figure 1. Analog Dimming in Boost Configuration

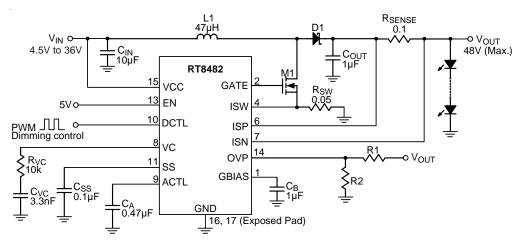

Figure 2. PWM to Analog Dimming in Boost Configuration

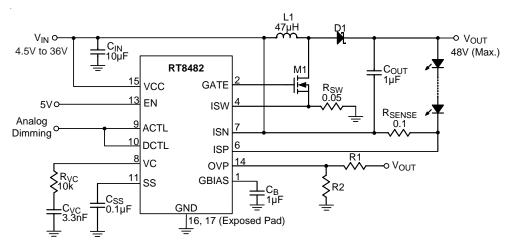

Figure 3. Analog Dimming in Buck-Boost Configuration

Figure 4. Analog Dimming in Buck Configuration

# **Functional Pin Description**

|          | Pin No.                 |          |                                                                                                                                                                                                   |  |  |

|----------|-------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SOP-16   | WQFN-16L 3x3            | Pin Name | Pin Function                                                                                                                                                                                      |  |  |

| 1        | 1                       | GBIAS    | Internal Gate Driver Bias Pin. A good bypass capacitor is required.                                                                                                                               |  |  |

| 2        | 2                       | GATE     | External MOSFET Switch Gate Driver Output Pin.                                                                                                                                                    |  |  |

| 3, 5, 12 | 3, 5, 12                | NC       | No Internal Connection.                                                                                                                                                                           |  |  |

| 4        | 4                       | ISW      | External MOSFET Switch Current Sense Pin. Connect the current sense resistor between external N-MOSFET switch and the ground.                                                                     |  |  |

| 6        | 6                       | ISP      | LED Current Sense Amplifier Positive Input.                                                                                                                                                       |  |  |

| 7        | 7                       | ISN      | LED Current Sense Amplifier Negative Input. Voltage threshold between ISP and ISN is 190mV.                                                                                                       |  |  |

| 8        | 8                       | VC       | PWM Control Loop Compensation Pin.                                                                                                                                                                |  |  |

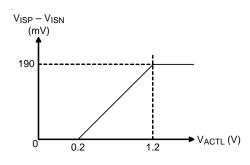

| 9        | 9                       | ACTL     | Analog Dimming Control Pin. The effective programming vorange of the pin is between 0.2V and 1.2V.                                                                                                |  |  |

| 10       | 10                      | DCTL     | By adding signal on DCTL pin can be averaged and converted into analog dimming signal on the ACTL pin following the formula below. a $0.47\mu F$ filtering capacitor on ACTL pin, the PWM dimming |  |  |

| 11       | 11                      | SS       | Soft-Start Pin. A capacitor of at least 10nF is required for proper soft start.                                                                                                                   |  |  |

| 13       | 13                      | EN       | Chip Enable (Active High). When this pin voltage is low, the chip is in shutdown mode.                                                                                                            |  |  |

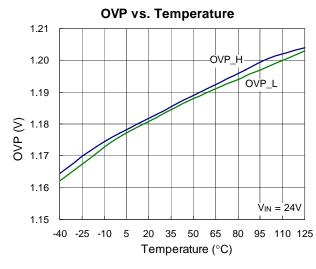

| 14       | 14                      | OVP      | Over Voltage Protection Pin. The PWM converter turns off when the voltage of the pin goes to higher than 1.2V.                                                                                    |  |  |

| 15       | 15                      | VCC      | Power Supply Pin of the Chip. For good bypass, a low ESR capacitor is required.                                                                                                                   |  |  |

| 16       | 16,<br>17 (Exposed Pad) | GND      | Ground Pin. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                                   |  |  |

www.richtek.com

Downloaded from Elcodis.com electronic components distributor

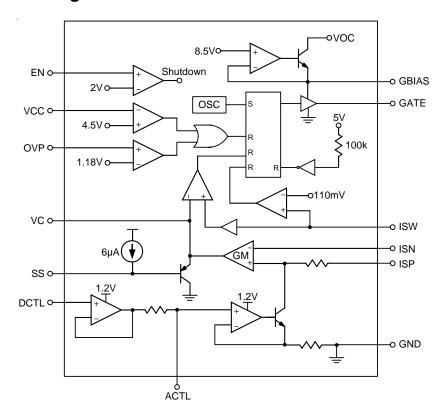

# **Function Block Diagram**

Figure 4

# Absolute Maximum Ratings (Note 1)

| • Supply Input Voltage, V <sub>CC</sub>                     | · 38V            |

|-------------------------------------------------------------|------------------|

| • GBIAS, GATE                                               | · 10V            |

| • ISW                                                       | · 1V             |

| • ISP, ISN                                                  | - 54V            |

| DCTL, ACTL, OVP Pin Voltage                                 | 8V (Note 6)      |

| • EN Pin Voltage                                            | - 20V            |

| • Power Dissipation, P <sub>D</sub> @ T <sub>A</sub> = 25°C |                  |

| SOP-16                                                      | · 1.176W         |

| WQFN-16L 3x3                                                | · 1.471W         |

| Package Thermal Resistance (Note 2)                         |                  |

| SOP-16, $\theta_{JA}$                                       | - 85°C/W         |

| WQFN-16L 3x3, $\theta_{JA}$                                 | - 68°C/W         |

| WQFN-16L 3x3, $\theta_{JC}$                                 | · 7.5°C/W        |

| • Junction Temperature                                      | · 150°C          |

| • Lead Temperature (Soldering, 10 sec.)                     | - 260°C          |

| Storage Temperature Range                                   | - −65°C to 150°C |

| ESD Susceptibility (Note 3)                                 |                  |

| HBM (Human Body Mode)                                       | · 2kV            |

| MM (Machine Mode)                                           | - 200V           |

| Recommended Operating Conditions (Note 4)                   |                  |

• Supply Input Voltage Range, V<sub>CC</sub> ------ 4.5V to 36V

# • Junction Temperature Range ----- –40°C to 125°C

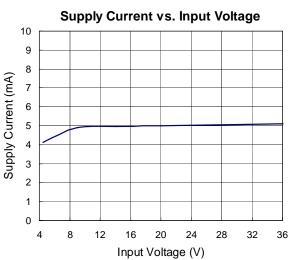

**Electrical Characteristics** (V<sub>CC</sub> = 24V, No Load on any Output, T<sub>A</sub> = 25°C, unless otherwise specified)

| Parameter                                              |            | Symbol                              | Test Conditions                                                                   | Min | Тур | Max | Unit |

|--------------------------------------------------------|------------|-------------------------------------|-----------------------------------------------------------------------------------|-----|-----|-----|------|

| Overall                                                |            | •                                   |                                                                                   | •   |     |     |      |

| Supply Current                                         |            | lvcc                                | VC ≤ 0.4V (Switching off)                                                         |     | 6   | 7.2 | mA   |

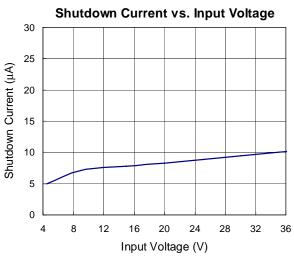

| Shutdown Current                                       |            | I <sub>SHDN</sub>                   | V <sub>EN</sub> ≤ 0.7V                                                            |     | 12  |     | μА   |

| EN Threshold<br>Voltage                                | Logic-High | V <sub>IH</sub>                     |                                                                                   | 2   |     |     | V    |

|                                                        | Logic-Low  | V <sub>IL</sub>                     | 1                                                                                 |     |     | 0.5 |      |

| EN Input Current                                       |            |                                     | V <sub>EN</sub> ≤ 3V                                                              |     |     | 1.2 | μА   |

| Current Sense A                                        | mplifier   |                                     |                                                                                   |     |     |     |      |

| Input Threshold (V <sub>ISP</sub> – V <sub>ISN</sub> ) |            |                                     | 12V ≤ common mode ≤ 36V                                                           | 180 | 190 | 200 | mV   |

| ISP / ISN Input Current                                |            | I <sub>ISP</sub> / I <sub>ISN</sub> | $4.5V \le V_{ISP} = V_{ISN} \le 48V$                                              |     | 140 |     | μΑ   |

| VC Output Current                                      |            | I <sub>VC</sub>                     | $V_{ISP} - V_{ISN} = 190 \text{mV},$<br>$0.5 \text{V} \le V_{C} \le 2.4 \text{V}$ |     | ±20 |     | μА   |

| VC Threshold for PWM Switch Off                        |            |                                     |                                                                                   |     | 0.7 |     | V    |

| LED Dimming                                            |            |                                     |                                                                                   |     |     |     |      |

| Analog Dimming ACTL Pin<br>Input Current               |            | 1                                   | V <sub>ACTL</sub> = 1.2V                                                          |     | 1   |     | μА   |

|                                                        |            | I <sub>ACTL</sub>                   | $V_{ACTL} = 0.2V$                                                                 |     | 10  |     |      |

To be continued

| Parameter                             | Symbol                | Test Conditions             | Min | Тур  | Max | Unit     |  |

|---------------------------------------|-----------------------|-----------------------------|-----|------|-----|----------|--|

| LED Current Off Threshold at ACTL     | V <sub>ACTL_OFF</sub> |                             |     | 0.3  |     | <b>V</b> |  |

| DCTL Input Current                    | I <sub>DCTL</sub>     | $0.3V \le V_{DCTL} \le 6V$  |     |      | 0.5 | μА       |  |

| PWM Control                           |                       |                             |     |      |     |          |  |

| Switching Frequency                   | f <sub>SW</sub>       |                             | 280 | 350  | 420 | kHz      |  |

| Minimum Off Time (Note 5)             |                       |                             | 1   | 250  | -   | ns       |  |

| Switch Gate Driver                    |                       |                             |     |      |     |          |  |

| GBIAS Voltage                         | V <sub>GBIAS</sub>    | I <sub>GBIAS</sub> = 20mA   |     | 8.5  |     | V        |  |

| Coto Voltago High                     |                       | I <sub>Gate</sub> = -50mA   |     | 7.2  |     | V        |  |

| Gate Voltage High                     | V <sub>Gate_H</sub>   | $I_{Gate} = -100 \mu A$     |     | 7.8  |     |          |  |

| Coto Valtago I au                     | V <sub>Gate_L</sub>   | I <sub>Gate</sub> = 50mA    |     | 0.25 |     | V        |  |

| Gate Voltage Low                      |                       | I <sub>Gate</sub> = 100μA   |     | 0.1  |     |          |  |

| GATE Drive Rise and Fall Time         |                       | 1nF Load at GATE            |     | 15   |     | ns       |  |

| PWM Switch Current Limit<br>Threshold | I <sub>SW_LIM</sub>   |                             | 1   | 110  | 1   | mV       |  |

| OVP and Soft-Start                    |                       |                             |     |      |     |          |  |

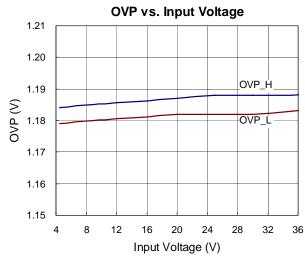

| OVP Threshold                         | V <sub>OVP_th</sub>   |                             | -   | 1.18 | -   | V        |  |

| OVP Input Current                     | love                  | $0.7V \le V_{OVP} \le 1.5V$ |     |      | 0.1 | μΑ       |  |

| Soft-Start Pin Current                | I <sub>SS</sub>       | $V_{SS} \le 2V$             |     | 6    |     | μΑ       |  |

| Thermal Protection                    |                       |                             |     |      |     |          |  |

| Thermal Shutdown Temperature          | T <sub>SD</sub>       |                             | -   | 145  | -   | °C       |  |

| Thermal Shutdown Recovery             | $\Delta T_{SD}$       |                             |     | 10   |     | °C       |  |

- **Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- Note 2.  $\theta_{JA}$  is measured in natural convection at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board of JEDEC 51-7 thermal measurement standard. The measurement case position of  $\theta_{JC}$  is on the exposed pad of the SOP package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- **Note 5.** When the natural maximum duty cycle of 350kHz switching frequency is reached, the switching cycle will be skipped (not reset) as the operating condition requires to effectively stretch and achieve higher on cycle than the natural maximum duty cycle set by the 350kHz switching frequency.

- Note 6. If connected with a  $20k\Omega$  serial resistor, ACTL and DCTL can go up to 36V.

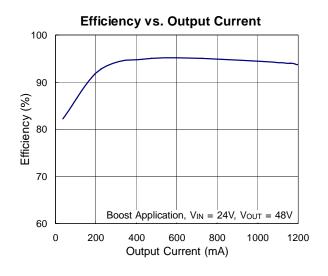

# **Typical Operating Characteristics**

### **Applications Information**

The RT8482 is a current mode PWM controller designed to drive an external MOSFET for high current LED applications. The LED current can be programmed by an external resistor. The input voltage range of the RT8482 can be up to 36V and the output voltage can be up to 48V. The RT8482 provides analog and PWM dimming to achieve LED current control.

#### **GBIAS Regulator and Bypass Capacitor**

The GBIAS pin requires a capacitor for stable operation and to store the charge for the large GATE switching currents. Choose a 10V rated low ESR, X7R or X5R ceramic capacitor for best performance. A  $1\mu F$  capacitor will be adequate for most applications.

Place the capacitor close to the IC to minimize the trace length to the GBIAS pin and also to the IC ground. An internal current limit on the GBIAS output protects the RT8482 from excessive on chip power dissipation.

The GBIAS pin has its own Under Voltage Lockout (UVLO) set to 4.3V (typical) to protect the external FETs from excessive power dissipation caused by not being fully enhanced. If the input voltage, VIN, does not exceed 8V, then the GBIAS pin should be connected to the input supply. Be aware if GBIAS supply is used to drive extra circuits in addition to the RT8482. Typically, the extra GBIAS load should be limited to less than 10mA.

#### **Loop Compensation**

The RT8482 uses an internal error amplifier via the compensation pin (VC) to optimize the loop response for specific application. The external inductor, output capacitor, and compensation resistor and capacitor determine the loop stability. The inductor and output capacitor are chosen based on performance, size and cost. The compensation resistor and capacitor at VC are selected to optimize control loop response and stability. For typical LED applications, a 3.3nF compensation capacitor at VC is adequate. A series resistor should always be used to increase the slew rate on the VC pin to maintain tighter regulation of LED current during fast transients on the input supply to the converter. An external resistor in series with a capacitor is connected from the VC pin to GND to provide

a pole and a zero for proper loop compensation. The typical compensation for the RT8482 is  $10k\Omega$  and 3.3nF.

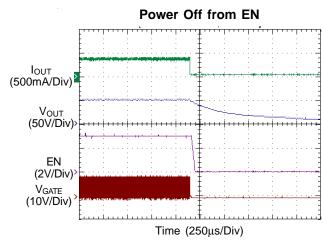

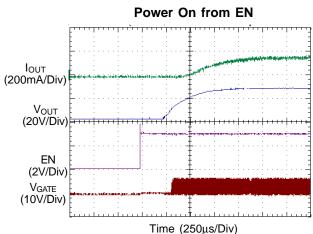

#### Soft-Start

The soft-start of the RT8482 can be achieved by connecting a capacitor from the SS pin to GND. The built-in soft-start circuit reduces the start-up current spike and output voltage overshoot. The soft-start time is determined by the external capacitor charged by an internal  $6\mu A$  constant charging current. The SS pin directly limits the rate of voltage rise on the VC pin, which in turn limits the peak switch current.

The soft-start interval is set by the soft-start capacitor selection according to the equation :

$$t_{SS} = C_{SS} \times \frac{2.4V}{6\mu A}$$

A typical value for the soft-start capacitor is  $0.1\mu F$ . The soft-start capacitor is discharged when EN/UVLO falls below its threshold, during an over-temperature event or during a GBIAS under-voltage event.

#### **LED Current Setting**

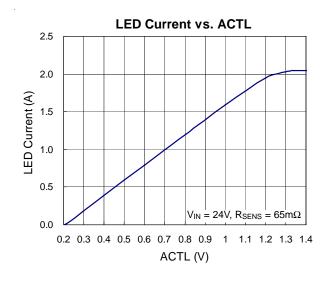

The LED current is programmed by placing an appropriate valued current sense resistor between the ISP and ISN pins. Typically, sensing of the current should be done at the top of the LED string. The ACTL pin should be tied to a voltage higher than 1.2V to get the full-scale 190mV (typical) threshold across the sense resistor. The ACTL pin can also be used to dim the LED current to zero, although relative accuracy decreases with the decreasing voltage sense threshold. When the ACTL pin voltage is less than 1.2V, the LED current is:

$$I_{LED} = \frac{(V_{ACTL} - 0.2) \times 0.19}{R_{SENSE}}$$

where.

$\mathbf{R}_{\text{SENSE}}$  is the resistor between ISP and ISN.

When the voltage of ACTL is higher than 1.2V, the LED current is regulated to :

$$I_{LED(MAX)} = \frac{190mV}{R_{SENSE}}$$

The ACTL pin can also be used in conjunction with a thermistor to provide over-temperature protection for the

DS8482-00 August 2010

be set by the following equation.

**RT8482** RICHTEK

LED load, or with a resistive voltage divider to V<sub>IN</sub> to reduce output power and switching current when V<sub>IN</sub> is low. The presence of a time varying differential voltage signal (ripple) across ISP and ISN at the switching frequency is expected.

The amplitude of this signal is increased by high LED load current, low switching frequency and/or a smaller value output filter capacitor. The compensation capacitor on the VC pin filters the signal so the average difference between ISP and ISN is regulated on the user-programmed value.

#### **Dimming Control**

For LED applications where a wide dimming range is required, two competing methods are available: analog dimming and PWM dimming. The easiest method is to simply vary the DC current through the LED by analog dimming.

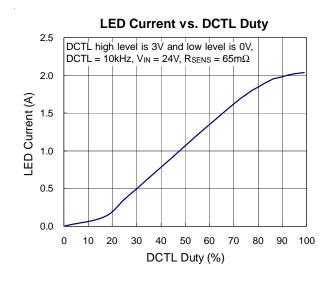

However, the better dimming method is PWM dimming, which switches the LED on and off by different duty cycle to control the average LED current. The PWM dimming offers several advantages over analog dimming and is much preferred by LED manufacturers. One advantage is the chromatic ity of the LEDs which remains unchanged in this scheme since the LED current is either zero or at programmed current. Another advantage of PWM dimming over analog dimming is that a wider dimming range is possible.

The RT8482 features both analog and digital dimming control. Analog dimming is linearly controlled by an external voltage (0.2V < V<sub>ACTL</sub> < 1.2V). With an on-chip output clamping amplifier and a resistor. PWM dimming signal fed at the DCTL pin can be easily low-pass filtered to an analog dimming signal with one external capacitor from the ACTL pin to GND for noise-free PWM dimming. A very high contrast ratio true digital PWM dimming can be achieved by driving the ACTL pin with a PWM signal from 100Hz to10kHz.

#### **Output Over Voltage Setting**

The RT8482 is equipped with an Over Voltage Protection (OVP) function. When the voltage at the OVP pin exceeds a threshold of approximately 1.18V, the power switch is turned off. The power switch can be turned on again once the voltage at the OVP pin drops below 1.18V. For Boost and Buck-Boost applications, the output voltage can be set by the following equation:

$$V_{OUT,\ OVP} = 1.18 \times \left(1 + \frac{R1}{R2}\right)$$

R1 and R2 are the voltage divider resistors from V<sub>OUT</sub> to GND with the divider center node connected to the OVP pin.

#### ISW Sense Resistor Selection

The resistor, R<sub>SW</sub>, between the source of the external N-MOSFET and GND should be selected to provide adequate switch current to drive the application without exceeding the 110mV (typical) current limit threshold on the ISW pin of the RT8482. For real applications, select a resistor that gives a switch current at least 30% greater than the required LED current.

For Buck application, select a resistor according to:

$$R_{SW, Buck} = \left(\frac{0.08V}{I_{OUT}}\right)$$

For Buck-Boost application, select a resistor according

$$R_{SW, Buck-Boost} = \left(\frac{V_{IN} \times 0.08V}{(V_{IN} + V_{OUT}) \times I_{OUT}}\right)$$

For Boost application, select a resistor according to:

$$R_{SW, Boost} = \left(\frac{V_{IN} \times 0.08V}{V_{OUT} \times I_{OUT}}\right)$$

The placement of R<sub>SW</sub> should be close to the source of the N-MOSFET and GND of the RT8482. The ISW pin input to the RT8482 should be a Kelvin connection to the positive terminal of R<sub>SW</sub>.

#### **Over Temperature Protection**

The RT8482 has an Over Temperature Protection (OTP) function to prevent excessive power dissipation from overheating the device. The OTP function will shut down switching operation when the die junction temperature exceeds 150°C. The chip will automatically start to switch again when the die junction temperature cools off.

#### Inductor Selection

The inductor used with the RT8482 should have a saturation current rating appropriate to the maximum

DS8482-00 August 2010

switch current selected with the  $R_{SW}$  resistor. Choose an inductor value based on operating frequency, input and output voltage to provide a current mode ramp of approximately 20mV magnitude on the ISW pin during the switch on-time of approximately 20mV magnitude. The following equations are useful to estimate the inductor value. For Buck application :

$$L_{Buck} = \frac{R_{SW} \times V_{OUT} \times (V_{IN} - V_{OUT})}{0.02 \times V_{IN} \times f_{SW}}$$

For Boost application

$$L_{Boost} = \frac{R_{SW} \times V_{IN} \times \left(V_{OUT} - V_{IN}\right)}{0.02 \times V_{OUT} \times f_{SW}}$$

For Buck-Boost application

$$L_{Buck-Boost} = \frac{R_{SW} \times V_{IN} \times V_{OUT}}{0.02 \times \left(V_{IN} + V_{OUT}\right) \times f_{SW}}$$

#### **Power MOSFET Selection**

For applications operating at high input or output voltages, the power N-MOSFET switch is typically chosen for drain voltage,  $V_{DS}$ , rating and low gate charge. Consideration of switch on-resistance,  $R_{DS(ON)}$ , is usually secondary because switching losses dominate power loss. The GBIAS regulator on the RT8482 has a fixed current limit to protect the IC from excessive power dissipation at high VIN, so the N-MOSFET should be chosen such that the product of Qg at 5V and switching frequency does not exceed the GBIAS current limit.

#### **Schottky Diode Selection**

The Schottky diode, with their low forward voltage drop and fast switching speed, is necessary for the RT8482 applications. In addition, power dissipation, reverse voltage rating and pulsating peak current are also important parameters for the Schottky diode selection. Choose a suitable Schottky diode with reverse voltage rating greater than the maximum output voltage. The diode's average current rating must exceed the average output current. The diode conducts current only when the power switch is turned off (typically less than 50% duty cycle). If using the PWM feature for dimming, it is important to consider diode leakage, which increases with temperature, from the output during the PWM low interval. Therefore, a Schottky diode with sufficiently low leakage current is suggested.

#### **Capacitor Selection**

The input capacitor reduces current spikes from the input supply and minimizes noise injection to the converter. For most of the RT8482 applications, a  $10\mu F$  ceramic capacitor is sufficient. A value higher or lower may be used depending on the noise level from the input supply and the input current to the converter.

In Boost application, the output capacitor is typically a ceramic capacitor and is selected based on the output voltage ripple requirements. The minimum value of the output capacitor,  $C_{\text{OUT}}$ , is approximately given by the following equation:

$$C_{OUT} = \frac{I_{OUT} \times V_{OUT}}{V_{IN} \times V_{RIPPLE} \times f_{SW}}$$

For LED applications, the equivalent resistance of the LED is typically low and the output filter capacitor should be sized to attenuate the current ripple. Use of X7R type ceramic capacitors is recommended. Lower operating frequencies will require proportionately higher capacitor values.

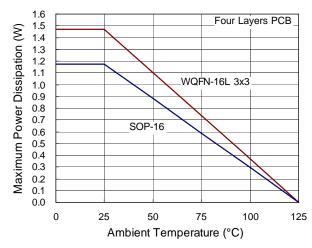

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum operation junction temperature. The maximum power dissipation depends on the thermal resistance of IC package, PCB layout, the rate of surroundings airflow and temperature difference between junction to ambient. The maximum power dissipation can be calculated by following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

Where  $T_{J(MAX)}$  is the maximum operation junction temperature,  $T_A$  is the ambient temperature and the  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating conditions specification of RT8482, The maximum junction temperature is 125°C. The junction to ambient thermal resistance  $\theta_{JA}$  is layout dependent. For WQFN-16L 3x3 packages, the thermal resistance  $\theta_{JA}$  is 68°C/W on the standard JEDEC 51-7 four layers thermal test board. For SOP-16 packages, the thermal resistance  $\theta_{JA}$  is 85°C/W on the standard JEDEC 51-7 four layers thermal test board. The maximum power dissipation at  $T_A$  = 25°C can be calculated by following formula :

DS8482-00 August 2010

13

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (68^{\circ}C/W) = 1.471W$  for WQFN-16L 3x3 packages

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (85^{\circ}C/W) = 1.176W$  for SOP-16 packages

The maximum power dissipation depends on operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance  $\theta_{JA}$ . For RT8482 packages, the Figure 5 of derating curves allows the designer to see the effect of rising ambient temperature on the maximum power allowed.

Figure 5. Derating Curves for RT8482 Packages

#### **Layout Consideration**

PCB layout is very important when designing power switching converter circuits. Some recommended layout guidelines are suggested as follows:

- ▶ The power components L1, D1, C<sub>IN</sub>, M1 and C<sub>OUT</sub> must be placed as close to each other as possible to reduce the ac current loop area. The PCB trace between power components must be as short and wide as possible due to large current flow through these traces during operation.

- $\blacktriangleright$  The input capacitor  $C_{\text{VCC}}$  must be placed as close to VCC pin as possible.

- Place the compensation components as close to VC pin as possible to avoid noise pick up.

- Connect GND pin and Exposed Pad to a large ground plane for maximum power dissipation and noise reduction.

Place these components as close to each other as possible Locate input capacitor as close to VCC as possible GBIAS □ 16 □ GND □ VCC 15 □ OVP NC [ 14 00 GND SW [ 00 13 □ EN 00 12 NC [ 5 ISP □ 6 ⊐ ss ≤R<sub>SENS</sub> ISN □ □ DCTL ☐ ACTL 0000 0000 Locate the compensation components as close to VC pin as possible

Figure 6. PCB Layout Guide

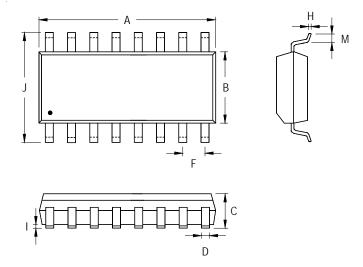

# **Outline Dimension**

| Cumbal | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

| Symbol | Min          | Max           | Min                  | Max   |  |

| А      | 9.804        | 10.008        | 0.386                | 0.394 |  |

| В      | 3.810        | 3.988         | 0.150                | 0.157 |  |

| С      | 1.346        | 1.753         | 0.053                | 0.069 |  |

| D      | 0.330        | 0.508         | 0.013                | 0.020 |  |

| F      | 1.194        | 1.346         | 0.047                | 0.053 |  |

| Н      | 0.178        | 0.254         | 0.007                | 0.010 |  |

| I      | 0.102        | 0.254         | 0.004                | 0.010 |  |

| J      | 5.791        | 6.198         | 0.228                | 0.244 |  |

| М      | 0.406        | 1.270         | 0.016                | 0.050 |  |

16-Lead SOP Plastic Package

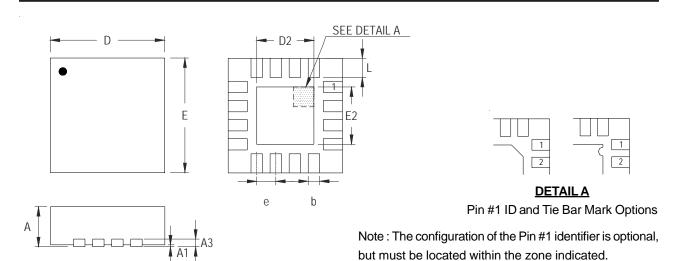

**Dimensions In Millimeters Dimensions In Inches** Symbol Min Max Min Max 0.700 0.800 0.028 0.031 Α **A1** 0.000 0.050 0.000 0.002 0.250 A3 0.175 0.007 0.010 b 0.180 0.300 0.007 0.012 D 2.950 3.050 0.116 0.120 D2 1.300 1.750 0.051 0.069 Ε 2.950 3.050 0.116 0.120 E2 1.300 1.750 0.051 0.069 0.500 0.020 е

W-Type 16L QFN 3x3 Package

0.450

#### **Richtek Technology Corporation**

L

0.350

Headquarter

5F, No. 20, Taiyuen Street, Chupei City

Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789 Fax: (8863)5526611

### **Richtek Technology Corporation**

Taipei Office (Marketing)

8F, No. 137, Lane 235, Paochiao Road, Hsintien City

0.018

Taipei County, Taiwan, R.O.C.

0.014

Tel: (8862)89191466 Fax: (8862)89191465

Email: marketing@richtek.com

Information that is provided by Richtek Technology Corporation is believed to be accurate and reliable. Richtek reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. No third party intellectual property infringement of the applications should be guaranteed by users when integrating Richtek products into any application. No legal responsibility for any said applications is assumed by Richtek.