# MC56F825x/4x Reference Manual

Supports the MC56F8257, MC56F8256, MC56F8255, MC56F8247, MC56F8246, and MC56F8245

Document Number: MC56F825XRM Rev. 2, 10/2010

Preliminary

2

## Contents

| See | ction N | Number Title                                      | Page |

|-----|---------|---------------------------------------------------|------|

|     |         | Chapter 1<br>Device Overview                      |      |

| 1.1 | Introdu | uction                                            |      |

| 1.2 | Feature | 'es                                               |      |

| 1.3 | Core B  | Block Diagram                                     |      |

| 1.4 | Periph  | ieral Subsystem                                   |      |

| 1.5 | Clock   | Generation and Distribution                       |      |

|     |         | Chapter 2<br>Analog-to-Digital Converter (ADC)    |      |

| 2.1 | Introdu | uction                                            |      |

|     | 2.1.1   | Overview                                          |      |

|     | 2.1.2   | Features                                          |      |

|     | 2.1.3   | Block Diagram                                     |      |

| 2.2 | Signal  |                                                   |      |

|     | 2.2.1   | Overview                                          |      |

|     | 2.2.2   | External Signal Descriptions                      |      |

|     |         | 2.2.2.1 Analog Input Pins (ANA[0:7] and ANB[0:7]) | 41   |

|     |         | 2.2.2.2 Voltage Reference Pins (VREFH and VREFLO) |      |

| 2.3 | Memor   | bry Map and Registers                             |      |

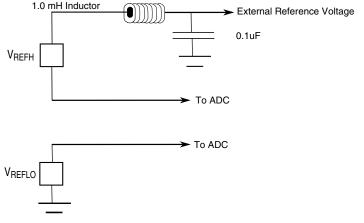

|     | 2.3.1   | ADC Control Register 1 (ADCCTRL1)                 | 47   |

|     | 2.3.2   | ADC Control Register 2 (ADCCTRL2)                 |      |

|     | 2.3.3   | ADC Zero Crossing Control Register (ADCZXCTRL)    |      |

|     | 2.3.4   | ADC Channel List Register 1 (ADCCLIST1)           |      |

|     | 2.3.5   | ADC Channel List Register 2 (ADCCLIST2)           |      |

|     | 2.3.6   | ADC Channel List Register 3 (ADCCLIST3)           |      |

|     | 2.3.7   | ADC Channel List Register 4 (ADCCLIST4)           |      |

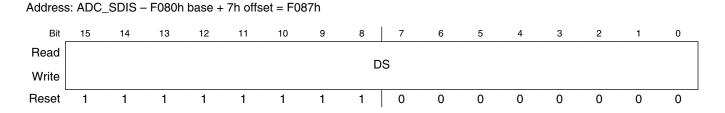

|     | 2.3.8   | ADC Sample Disable Register (ADCSDIS)             |      |

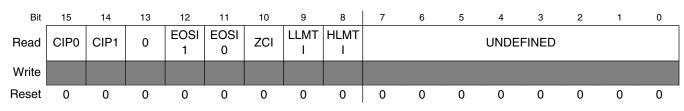

|     | 2.3.9   | ADC Status Register (ADCSTAT)                     |      |

|     |         |                                                   |      |

#### MC56F825x/4x Reference Manual, Rev. 2, 10/2010

Downloaded from **Elcodis.com** electronic components distributor

| Section | on Nu   | Imber Title                                         | Page |

|---------|---------|-----------------------------------------------------|------|

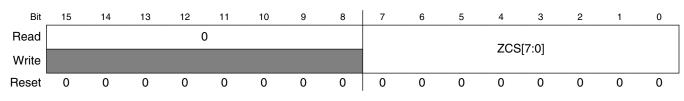

| 2.      | 3.10    | ADC Ready Register (ADCRDY)                         | 64   |

| 2.      | 3.11    | ADC Limit Status Register (ADCLIMSTAT)              | 65   |

| 2.      | 3.12    | ADC Zero Crossing Status Register (ADCZXSTAT)       | 65   |

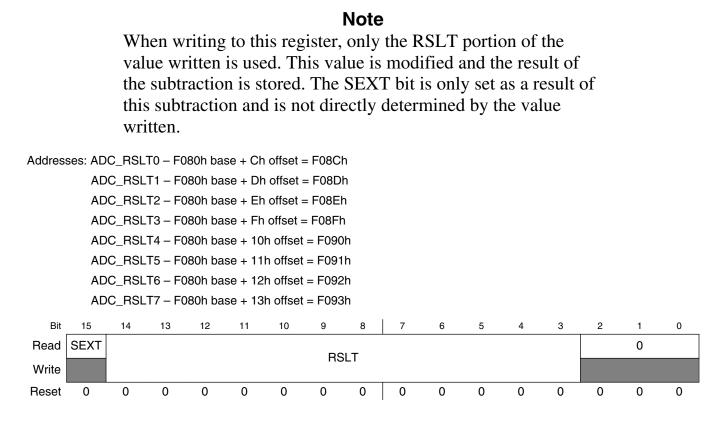

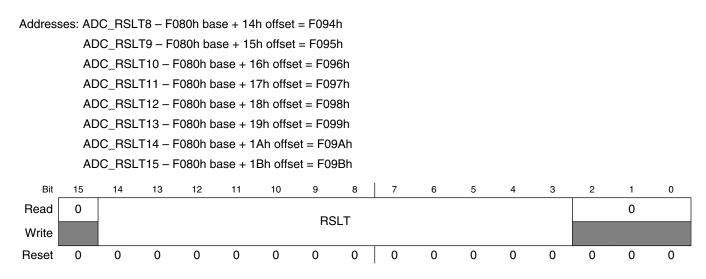

| 2.      | 3.13    | ADC Result Registers with sign extension (ADCRSLTn) | 66   |

| 2.      | 3.14    | ADC Result Registers (ADCRSLTn)                     | 67   |

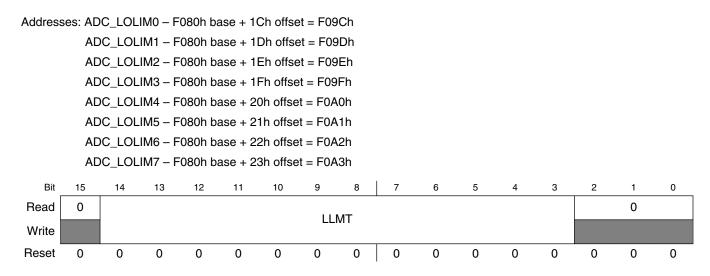

| 2.      | 3.15    | ADC Low Limit Registers (ADCLOLIMn)                 |      |

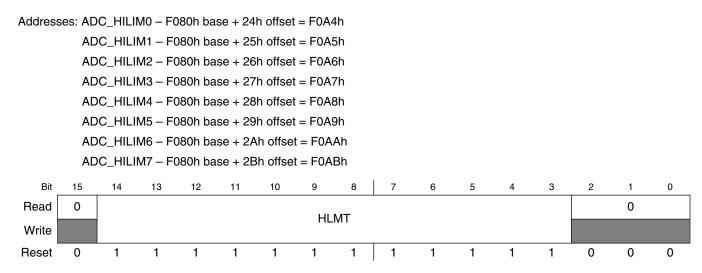

| 2.      | 3.16    | ADC High Limit Registers (ADCHILIMn)                | 69   |

| 2.      | 3.17    | ADC Offset Registers (ADCOFFSTn)                    | 69   |

| 2.      | 3.18    | ADC Power Control Register (ADCPWR)                 | 70   |

| 2.      | 3.19    | ADC Calibration Register (ADCCAL)                   | 73   |

| 2.      | 3.20    | Gain Control 1 Register (ADCGC1)                    | 74   |

| 2.      | 3.21    | Gain Control 2 Register (ADCGC2)                    | 76   |

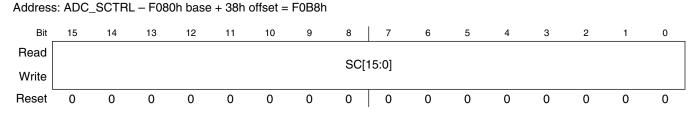

| 2.      | 3.22    | ADC Scan Control Register (ADCSCTRL)                |      |

| 2.      | 3.23    | ADC Power Control Register (ADCPWR2)                | 79   |

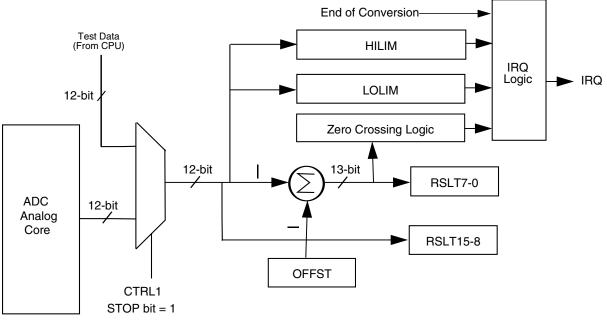

| 2.4 Fu  | unction | al Description                                      | 79   |

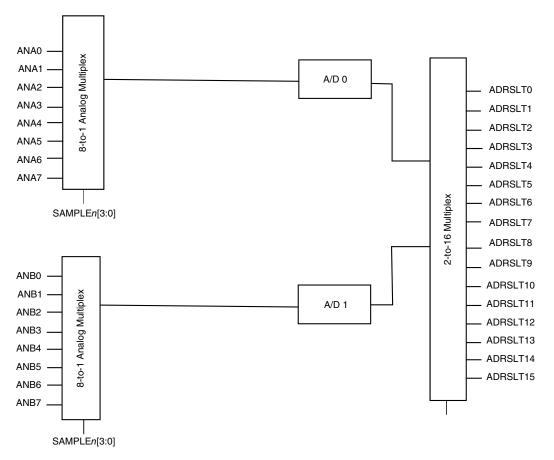

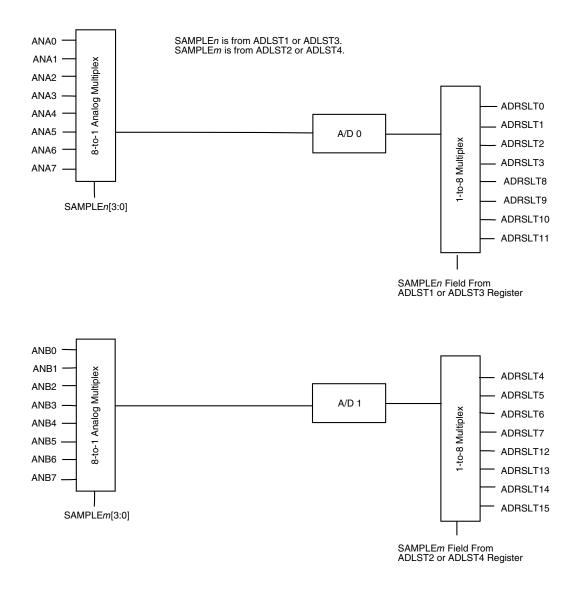

| 2.      | 4.1     | Input Multiplex Function                            |      |

| 2.4     | 4.2     | ADC Sample Conversion Operating Modes               | 85   |

|         |         | 2.4.2.1 Normal Mode Operation                       |      |

|         |         | 2.4.2.1.1 Single-Ended Samples                      |      |

|         |         | 2.4.2.1.2 Differential Samples                      |      |

| 2.      | 4.3     | ADC Data Processing                                 |      |

| 2.4     | 4.4     | Sequential Versus Parallel Sampling                 |      |

| 2.      | 4.5     | Scan Sequencing                                     |      |

| 2.4     | 4.6     | Power Management                                    | 91   |

|         |         | 2.4.6.1 Low Power Modes                             | 91   |

|         |         | 2.4.6.2 Startup in Different Power Modes            |      |

|         |         | 2.4.6.3 Stop Mode of Operation                      | 93   |

| 2.5 Re  | eset    |                                                     | 94   |

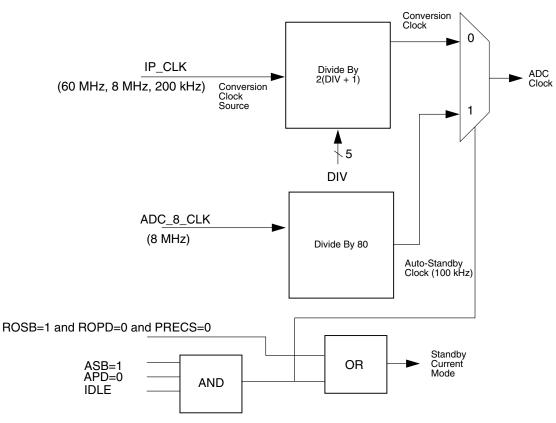

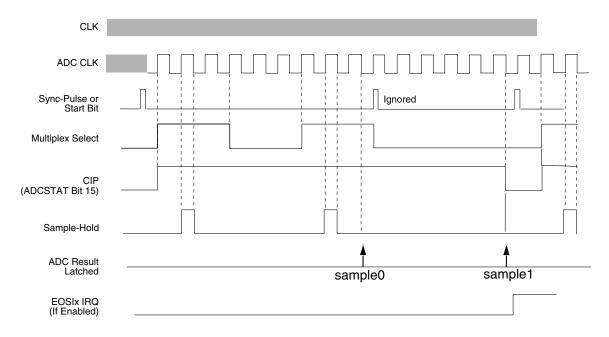

| 2.6 Cl  | locks   |                                                     |      |

4

#### Preliminary

# Dar

| Section Number |                                         |            | Title                                      | Page |

|----------------|-----------------------------------------|------------|--------------------------------------------|------|

| 2.7            | Interruj                                | pts        |                                            |      |

| 2.8            | Timing                                  | Specificat | tions                                      |      |

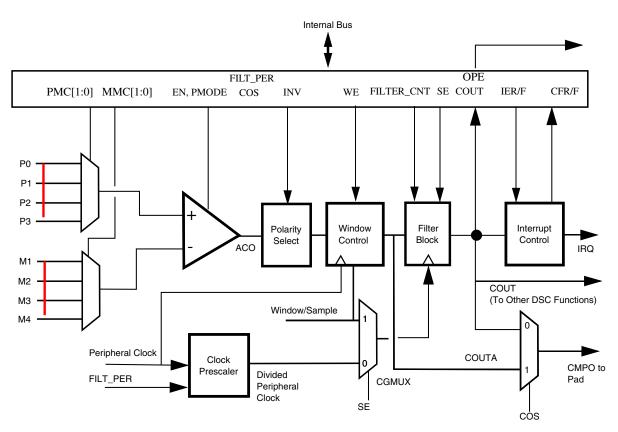

|                |                                         |            | Chapter 3<br>High Speed Comparator (HSCMP) |      |

| 3.1            | Introdu                                 | ction      |                                            |      |

| 3.2            | Feature                                 | S          |                                            |      |

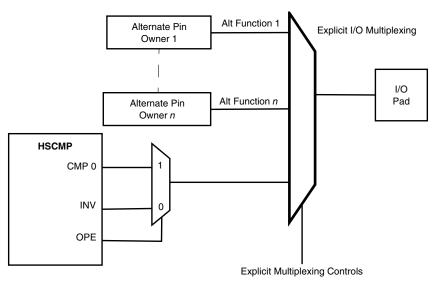

| 3.3            | Block I                                 | Diagram    |                                            |      |

| 3.4            | Pin De                                  | scriptions |                                            |      |

|                | 3.4.1                                   | External   | Pins                                       |      |

| 3.5            | Memor                                   | y Map and  | Register Definitions                       |      |

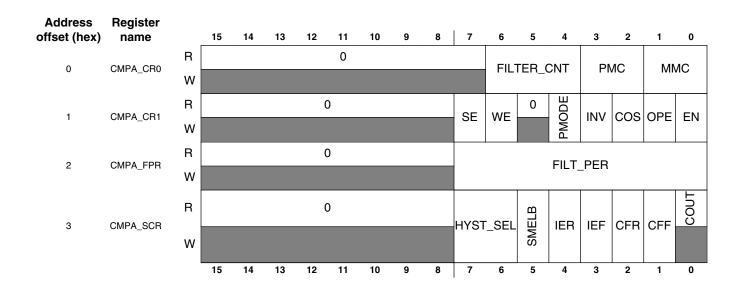

|                | 3.5.1                                   | Control I  | Register 0 (CMPx_CR0)                      |      |

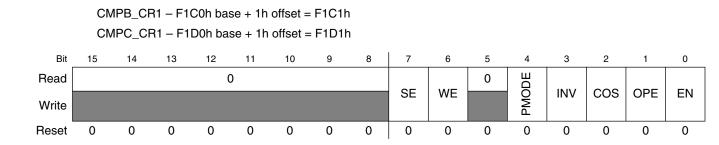

|                | 3.5.2                                   | Control 1  | Register 1 (CMPx_CR1)                      |      |

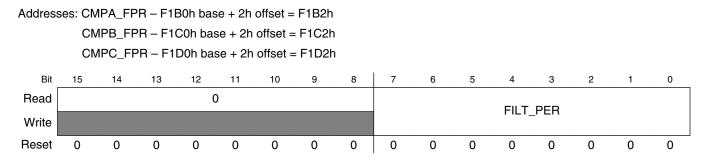

|                | 3.5.3 Filter Period Register (CMPx_FPR) |            |                                            |      |

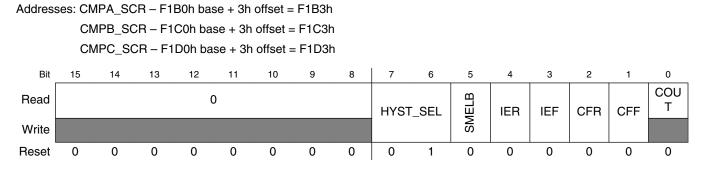

|                | 3.5.4                                   | Status ar  | nd Control Register (CMPx_SCR)             |      |

| 3.6            | Functional Description                  |            |                                            |      |

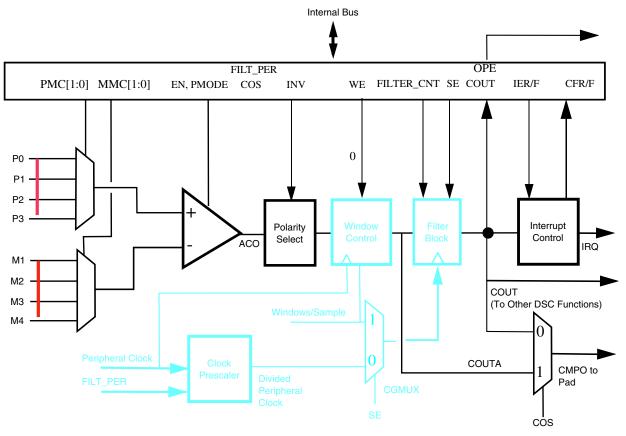

|                | 3.6.1                                   | HSCMP      | Functional Modes                           |      |

|                |                                         | 3.6.1.1    | Disabled Mode (1)                          |      |

|                |                                         | 3.6.1.2    | Continuous Mode (2A and 2B)                |      |

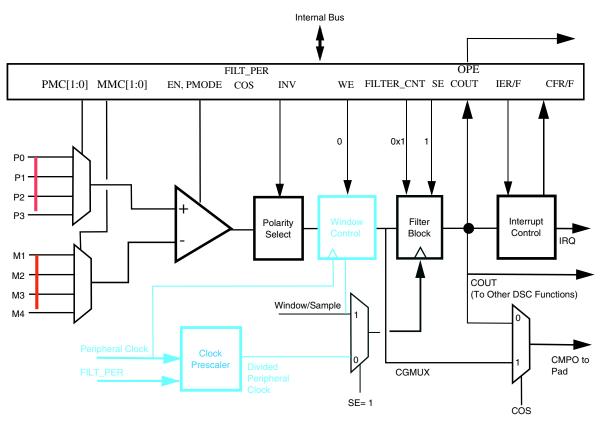

|                |                                         | 3.6.1.3    | Sampled, Non-Filtered Mode (3A and 3B)     |      |

|                |                                         | 3.6.1.4    | Sampled, Filtered Mode (4A and 4B)         |      |

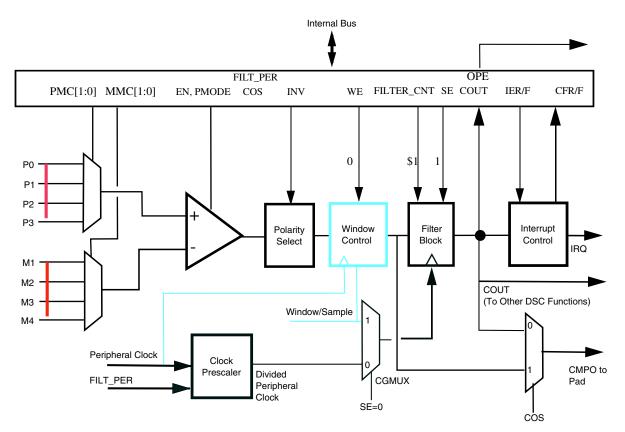

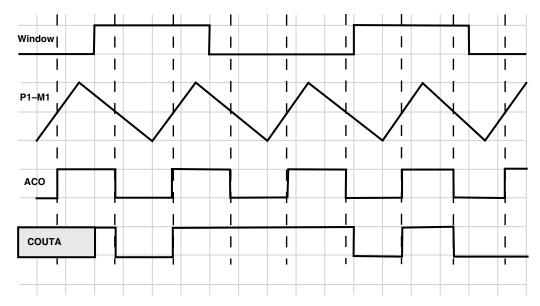

|                |                                         | 3.6.1.5    | Windowed Mode (5A and 5B)                  |      |

|                |                                         | 3.6.1.6    | Windowed/Resampled Mode (6)                |      |

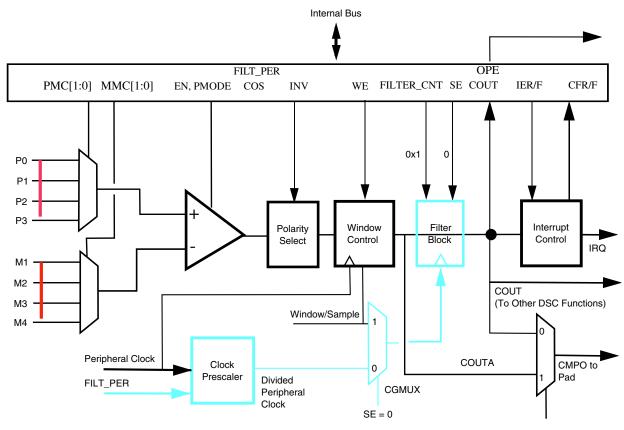

|                |                                         | 3.6.1.7    | Windowed/Filtered Mode (7)                 |      |

|                | 3.6.2                                   | Power M    | lodes                                      |      |

|                |                                         | 3.6.2.1    | Wait Mode Operation                        |      |

|                |                                         | 3.6.2.2    | Stop Mode Operation                        |      |

|                |                                         | 3.6.2.3    | Debug Mode Operation                       |      |

|                | 3.6.3                                   | Hysteres   | sis                                        |      |

|                | 3.6.4                                   | Startup a  | and Operation                              |      |

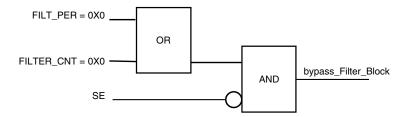

|     | 3.6.5   | Low Pass | s Filter              | 120 |

|-----|---------|----------|-----------------------|-----|

|     |         | 3.6.5.1  | Introduction          | 120 |

|     |         | 3.6.5.2  | Enabling Filter Modes | 120 |

|     |         | 3.6.5.3  | Latency Issues        | 121 |

| 3.7 | Interru | pts      |                       | 122 |

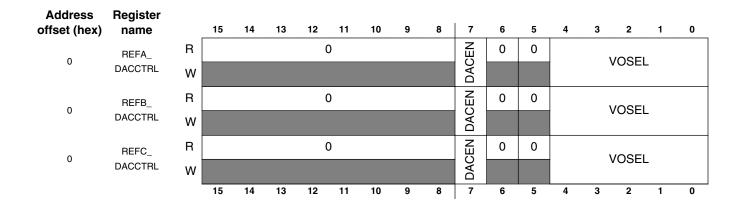

#### Chapter 4 5-Bit Voltage Reference Digital-to-Analog Converter (VREF\_DAC)

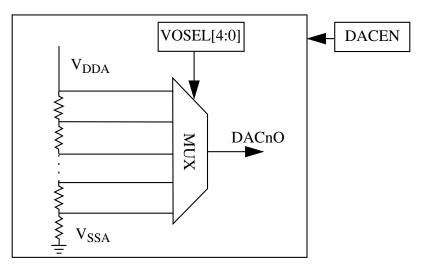

| 4.1 | Introduction |                                                       |      |  |  |

|-----|--------------|-------------------------------------------------------|------|--|--|

|     | 4.1.1        | Overview                                              | .123 |  |  |

|     | 4.1.2        | Features                                              | .123 |  |  |

|     | 4.1.3        | Block Diagram                                         | .124 |  |  |

| 4.2 | Memory       | V Map and Registers                                   | .124 |  |  |

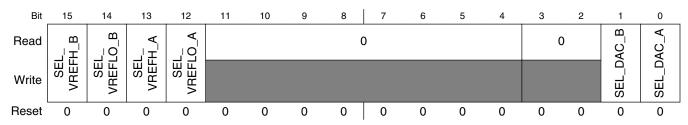

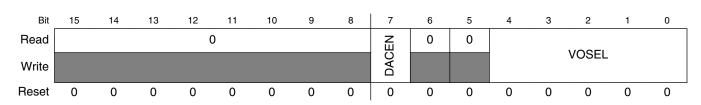

|     | 4.2.1        | Voltage Reference DAC Control Register (REFx_DACCTRL) | .125 |  |  |

| 4.3 | Function     | nal Description                                       | .125 |  |  |

|     | 4.3.1        | Operation                                             | .125 |  |  |

| 4.4 | Resets       |                                                       |      |  |  |

| 4.5 | Clocks       |                                                       | .126 |  |  |

| 4.6 | Interrupts   |                                                       |      |  |  |

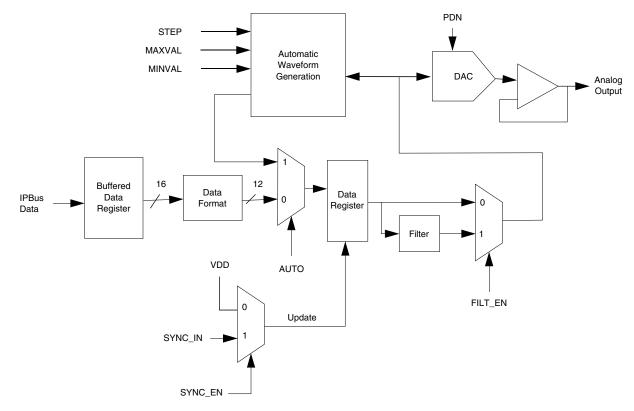

#### Chapter 5 12-Bit Digital-to-Analog Converter (DAC)

| 5.1 | 1 Introduction |                                             |      |  |  |

|-----|----------------|---------------------------------------------|------|--|--|

|     | 5.1.1          | Overview                                    | 127  |  |  |

|     | 5.1.2          | Features                                    | 127  |  |  |

|     | 5.1.3          | Block Diagram                               | 128  |  |  |

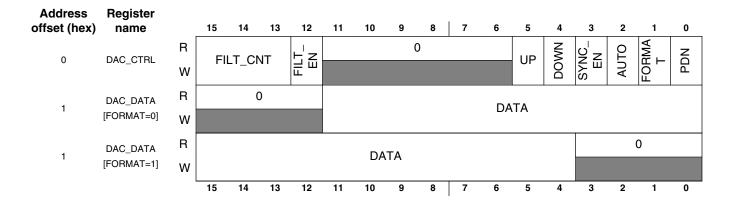

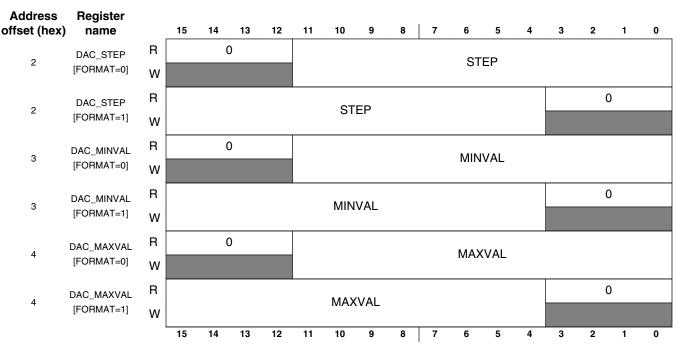

| 5.2 | Memory         | Memory Map and Registers                    |      |  |  |

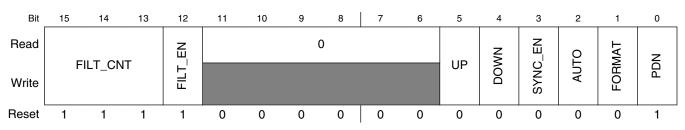

|     | 5.2.1          | Control Register (DACCTRL)                  | 129  |  |  |

|     | 5.2.2          | Buffered Data Register (DACDATA [FORMAT=0]) | .131 |  |  |

|     | 5.2.3          | Buffered Data Register (DACDATA [FORMAT=1]) | .131 |  |  |

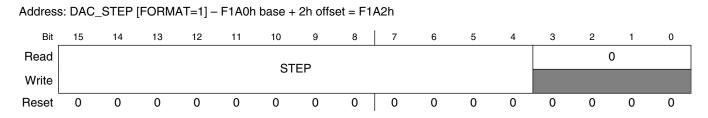

|     | 5.2.4          | Step Size Register (DACSTEP [FORMAT=0])     | 132  |  |  |

#### MC56F825x/4x Reference Manual, Rev. 2, 10/2010

Page

**Section Number**

| Section Number |          | umber       | Title                                   | Page |

|----------------|----------|-------------|-----------------------------------------|------|

|                | 5.2.5    | Step Size   | Register (DACSTEP [FORMAT=1])           |      |

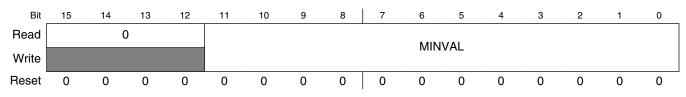

|                | 5.2.6    | Minimum     | n Value Register (DACMINVAL [FORMAT=0]) |      |

|                | 5.2.7    | Minimum     | n Value Register (DACMINVAL [FORMAT=1]) |      |

|                | 5.2.8    | Maximun     | n Value Register (DACMAXVAL [FORMAT=0]) |      |

|                | 5.2.9    | Maximun     | n Value Register (DACMAXVAL [FORMAT=1]) |      |

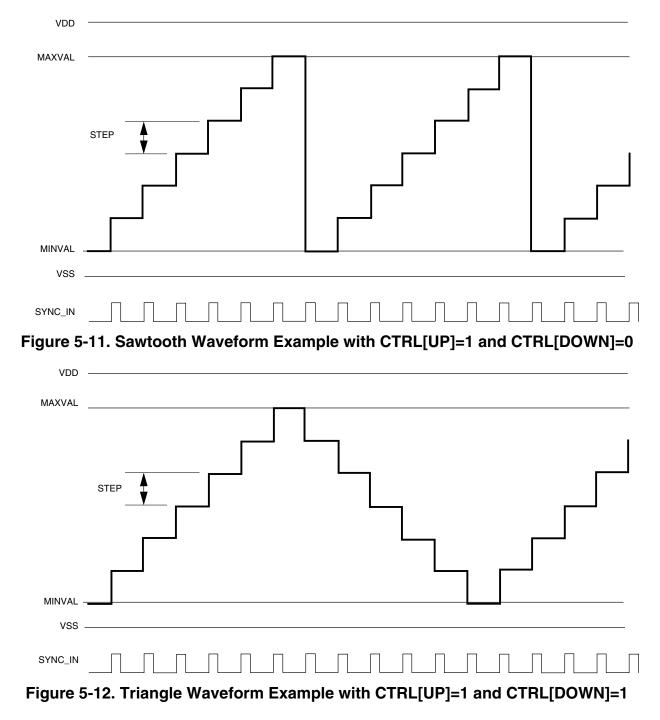

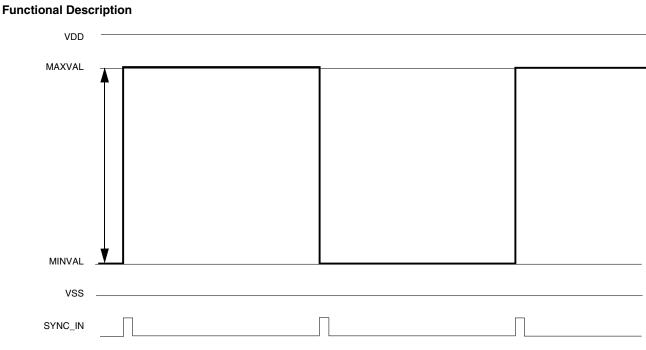

| 5.3            | Functio  | nal Descrip | otion                                   |      |

|                | 5.3.1    | Conversio   | on modes                                |      |

|                |          | 5.3.1.1     | Asynchronous conversion mode            |      |

|                |          | 5.3.1.2     | Synchronous conversion mode             |      |

|                | 5.3.2    | Operation   | n Modes                                 |      |

|                |          | 5.3.2.1     | Normal Mode                             |      |

|                |          | 5.3.2.2     | Automatic Mode                          |      |

|                | 5.3.3    | DAC sett    | ling time                               |      |

|                | 5.3.4    | Waveforr    | n Programming Example                   |      |

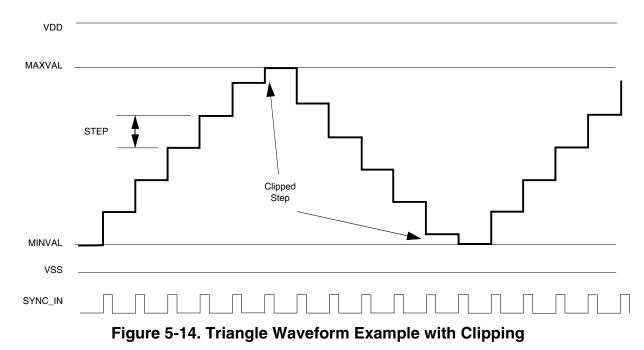

|                | 5.3.5    | Sources of  | of Waveform Distortion                  |      |

|                |          | 5.3.5.1     | Switching Glitches                      |      |

|                |          | 5.3.5.2     | Slew Effects                            |      |

|                |          | 5.3.5.3     | Clipping Effects (Automatic Mode Only)  |      |

| 5.4            | Resets   |             |                                         |      |

| 5.5            | Clocks.  |             |                                         | 141  |

| 5.6            | Interrup | ts          |                                         |      |

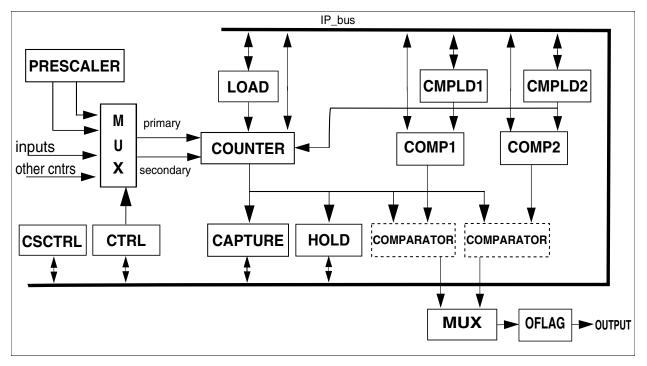

# Chapter 6 Quad Timer (TMR)

| 6.1 | Overview                                                     | 143 |

|-----|--------------------------------------------------------------|-----|

| 6.2 | Features                                                     | 143 |

| 6.3 | Modes of Operation                                           | 144 |

| 6.4 | Block Diagram                                                | 144 |

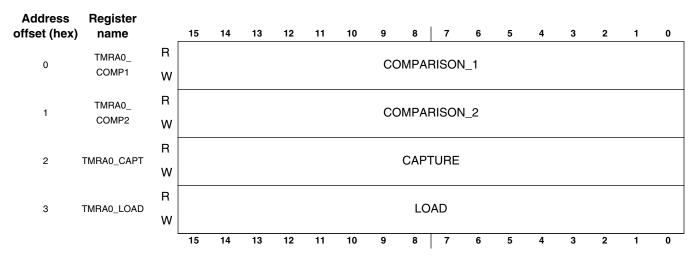

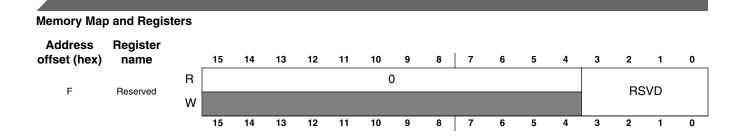

| 6.5 | Memory Map and Registers                                     | 145 |

|     | 6.5.1 Timer Channel Compare Register 1 (TMR <i>x</i> _COMP1) | 152 |

| Section Nu   | umber Title                                                        | Page |  |

|--------------|--------------------------------------------------------------------|------|--|

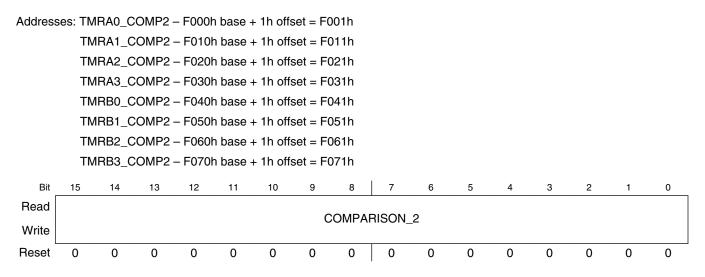

| 6.5.2        | Timer Channel Compare Register 2 (TMR <i>x</i> _COMP2)             | 153  |  |

| 6.5.3        | Timer Channel Capture Register (TMRx_CAPT)                         | 153  |  |

| 6.5.4        | Timer Channel Load Register (TMRx_LOAD)                            | 154  |  |

| 6.5.5        | Timer Channel Hold Register (TMRx_HOLD)                            | 155  |  |

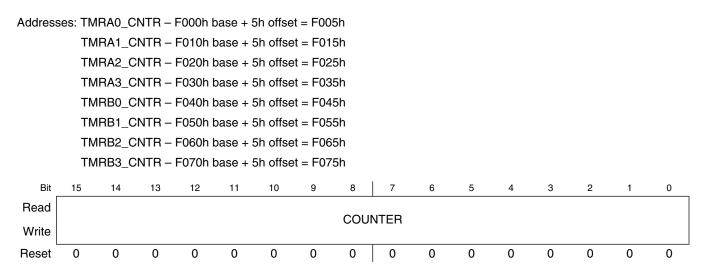

| 6.5.6        | Timer Channel Counter Register (TMRx_CNTR)                         | 155  |  |

| 6.5.7        | Timer Channel Control Register (TMRx_CTRL)                         |      |  |

| 6.5.8        | Timer Channel Status and Control Register (TMRx_SCTRL)             |      |  |

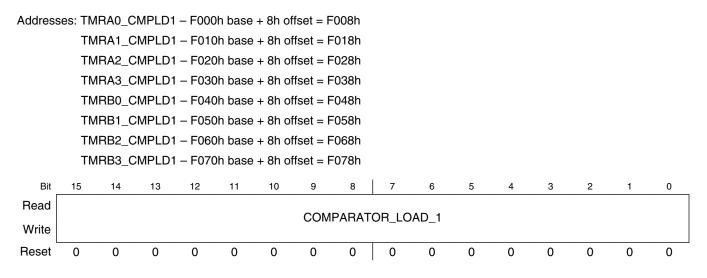

| 6.5.9        | Timer Channel Comparator Load Register 1 (TMRx_CMPLD1)             |      |  |

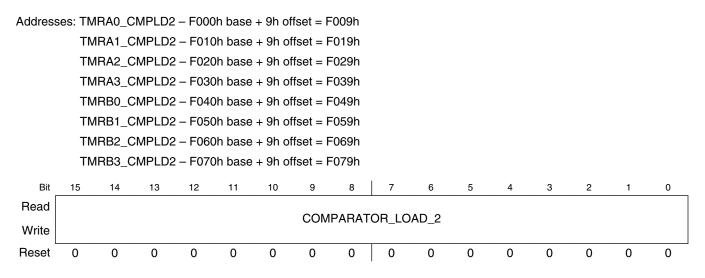

| 6.5.10       | Timer Channel Comparator Load Register 2 (TMR <i>x</i> _CMPLD2)    | 161  |  |

| 6.5.11       | Timer Channel Comparator Status and Control Register (TMRx_CSCTRL) | 161  |  |

| 6.5.12       | Timer Channel Input Filter Register (TMR <i>x</i> _FILT)           | 163  |  |

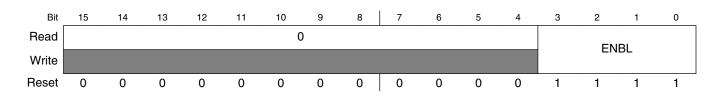

| 6.5.13       | Timer Channel Enable Register (TMRx_ENBL)                          | 165  |  |

| 6.6 Function | al Description                                                     | 165  |  |

| 6.6.1        | General                                                            | 165  |  |

| 6.6.2        | Functional Modes                                                   | 167  |  |

|              | 6.6.2.1 Stop Mode                                                  | 167  |  |

MC56F825x/4x Reference Manual, Rev. 2, 10/2010

8

**Section Number**

#### **Section Number**

#### Title

|          | 6.6.2.2    | Count Mode                                                                 | 167 |

|----------|------------|----------------------------------------------------------------------------|-----|

|          | 6.6.2.3    | Edge-Count Mode                                                            | 168 |

|          | 6.6.2.4    | Gated-Count Mode                                                           | 169 |

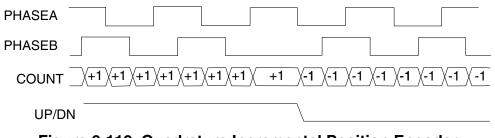

|          | 6.6.2.5    | Quadrature-Count Mode                                                      | 169 |

|          | 6.6.2.6    | Quadrature-Count Mode with Index Input                                     | 170 |

|          | 6.6.2.7    | Signed-Count Mode                                                          | 171 |

|          | 6.6.2.8    | Triggered-Count Mode 1                                                     | 172 |

|          | 6.6.2.9    | Triggered-Count Mode 2                                                     | 173 |

|          | 6.6.2.10   | One-Shot Mode                                                              | 174 |

|          | 6.6.2.11   | Cascade-Count Mode                                                         | 175 |

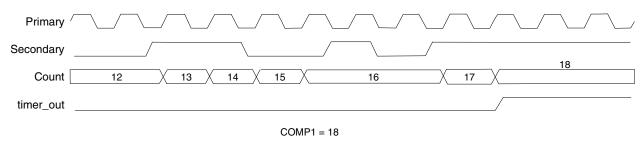

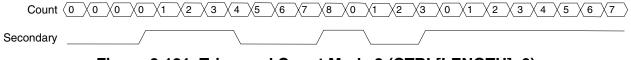

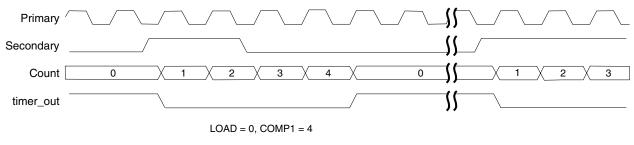

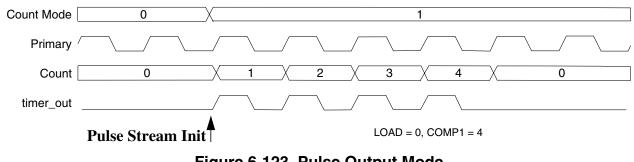

|          | 6.6.2.12   | Pulse-Output Mode                                                          | 176 |

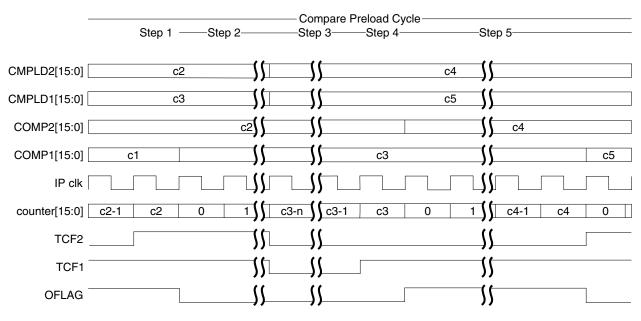

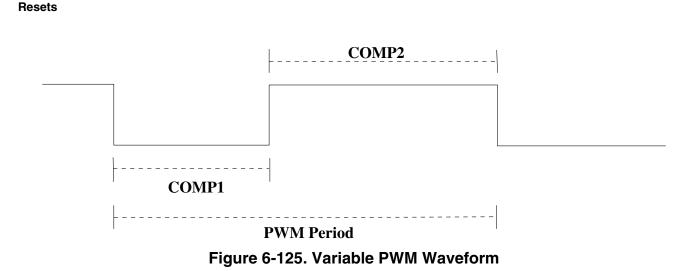

|          | 6.6.2.13   | Fixed-Frequency PWM Mode                                                   | 178 |

|          | 6.6.2.14   | Variable-Frequency PWM Mode                                                | 179 |

|          | 6.6.2.15   | Usage of Compare Registers                                                 | 182 |

|          | 6.6.2.16   | Usage of Compare Load Registers                                            | 183 |

|          | 6.6.2.17   | Usage of the Capture Register                                              | 184 |

| Resets   |            |                                                                            | 184 |

| 6.7.1    | General    |                                                                            | 184 |

| Clocks.  |            |                                                                            | 185 |

| 6.8.1    | General    |                                                                            | 185 |

| Interrup | ots        |                                                                            | 185 |

| 6.9.1    | General    |                                                                            | 185 |

| 6.9.2    | Descriptio | on of Interrupt Operation                                                  | 186 |

|          | 6.9.2.1    | Timer Compare Interrupts                                                   | 186 |

|          |            | 6.9.2.1.1 Timer Compare 1 Interrupts (Available with Compare Load Feature) | 186 |

|          |            | 6.9.2.1.2 Timer Compare 2 Interrupts (Available with Compare Load Feature) | 186 |

|          | 6.9.2.2    | Timer Overflow Interrupts                                                  | 186 |

|          | 6.9.2.3    | Timer Input Edge Interrupts                                                | 187 |

#### MC56F825x/4x Reference Manual, Rev. 2, 10/2010

Downloaded from **Elcodis.com** electronic components distributor

6.7

6.8

6.9

**Section Number**

#### Title

#### Chapter 7 Enhanced Flex Pulse Width Modulator (eFlexPWM)

| 7.1 | Introdu  | Juction                                                     |     |  |  |

|-----|----------|-------------------------------------------------------------|-----|--|--|

|     | 7.1.1    | Features                                                    |     |  |  |

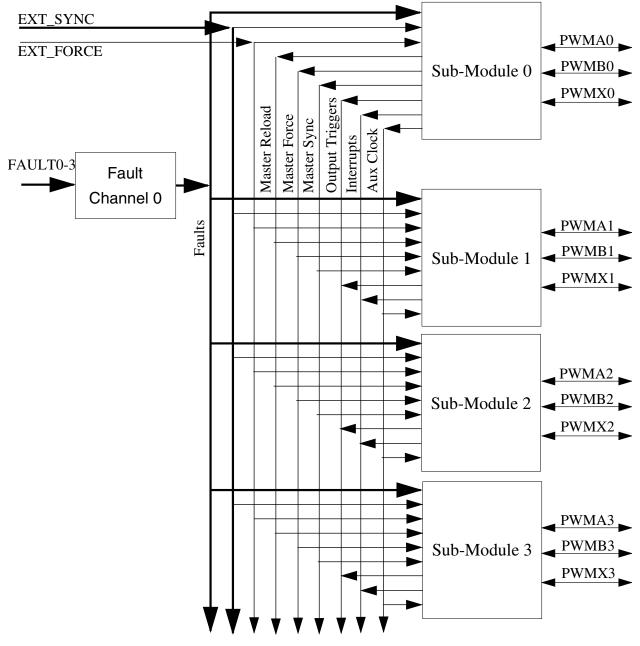

|     |          | 7.1.1.1 Inter-Module Connections                            | 190 |  |  |

|     |          | 7.1.1.2 Submodules and Fault Channel                        | 190 |  |  |

|     | 7.1.2    | Modes of Operation                                          | 190 |  |  |

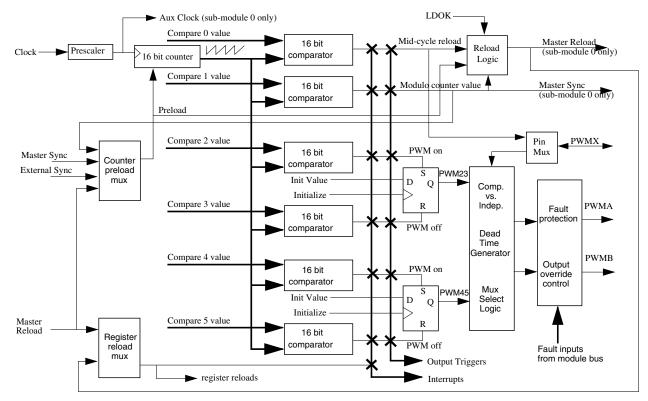

|     | 7.1.3    | Block Diagram                                               | 191 |  |  |

|     |          | 7.1.3.1 PWM Submodule                                       | 192 |  |  |

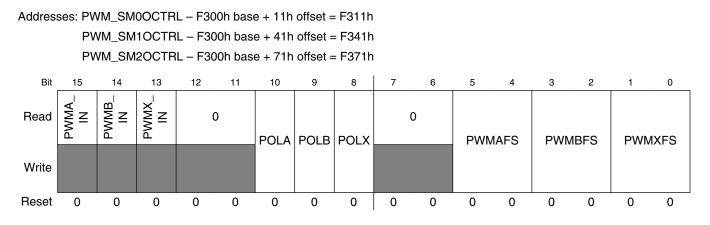

| 7.2 | Signal l | Descriptions                                                |     |  |  |

|     | 7.2.1    | PWM Signals and Crossbar Module                             |     |  |  |

|     | 7.2.2    | PWM[n]A and PWM[n]B - External PWM Pair                     | 194 |  |  |

|     | 7.2.3    | PWM[n]X - Auxiliary PWM signal                              | 194 |  |  |

|     | 7.2.4    | FAULT[n] - Fault inputs                                     | 194 |  |  |

|     | 7.2.5    | PWM[n]_EXT_SYNC - External Synchronization Signal           | 194 |  |  |

|     | 7.2.6    | EXT_FORCE - External Output Force Signal                    | 194 |  |  |

|     | 7.2.7    | PWM[n]_EXTA and PWM[n]_EXTB - Alternate PWM Control Signals | 194 |  |  |

|     | 7.2.8    | PWM[n]_OUT_TRIG0 and PWM[n]_OUT_TRIG1 - Output Triggers     |     |  |  |

|     | 7.2.9    | EXT_CLK - External Clock Signal                             | 195 |  |  |

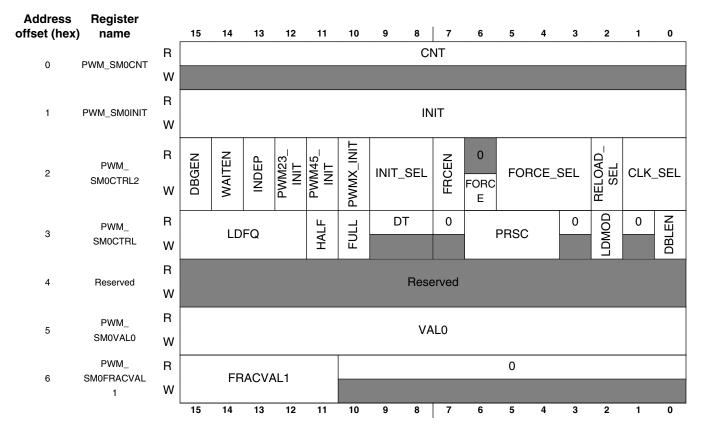

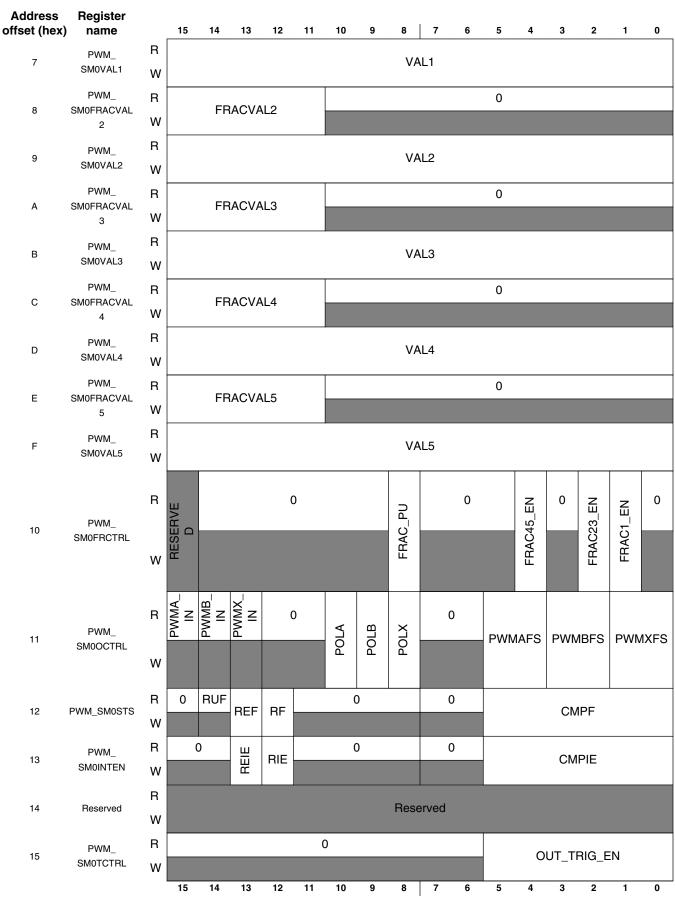

| 7.3 | Memor    | ry Map and Registers                                        |     |  |  |

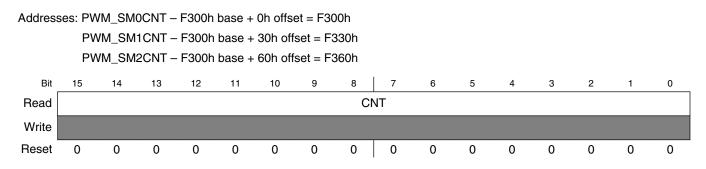

|     | 7.3.1    | PWM SMx Counter Register (PWMSMnCNT)                        |     |  |  |

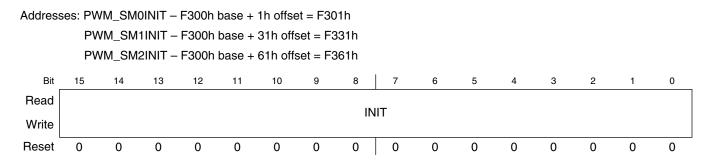

|     | 7.3.2    | PWM SMx Initial Count Register (PWMSMnINIT)                 |     |  |  |

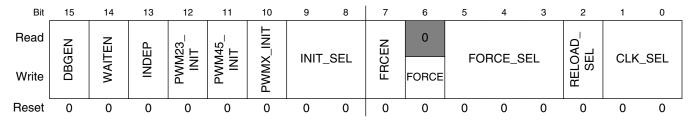

|     | 7.3.3    | PWM SMx Control 2 Register (PWMSMnCTRL2)                    |     |  |  |

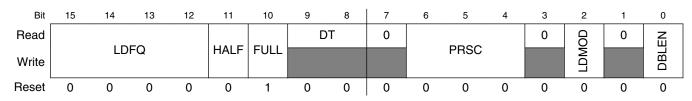

|     | 7.3.4    | PWM SMx Control Register (PWMSMnCTRL)                       |     |  |  |

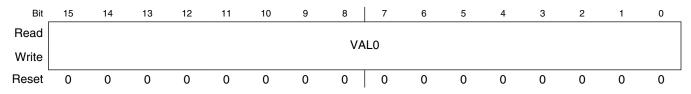

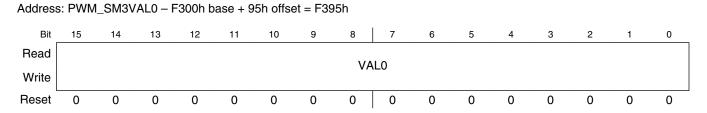

|     | 7.3.5    | PWM SMx Value Register 0 (PWMSMnVAL0)                       |     |  |  |

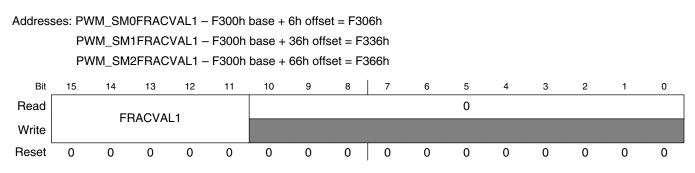

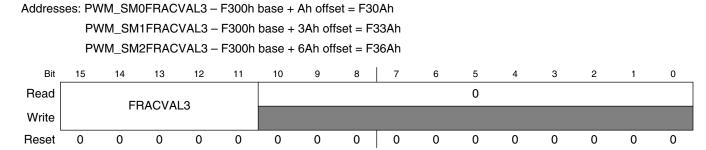

|     | 7.3.6    | PWM SMx Fractional Value Register 1 (PWMSMnFRACVAL1)        |     |  |  |

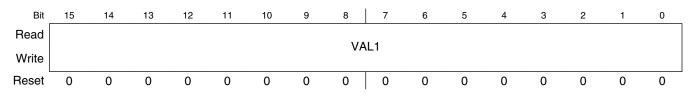

|     | 7.3.7    | PWM SMx Value Register 1 (PWMSMnVAL1)                       | 210 |  |  |

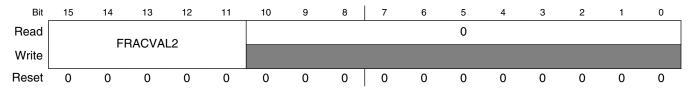

|     | 7.3.8    | PWM SMx Fractional Value Register 2 (PWMSMnFRACVAL2)        | 211 |  |  |

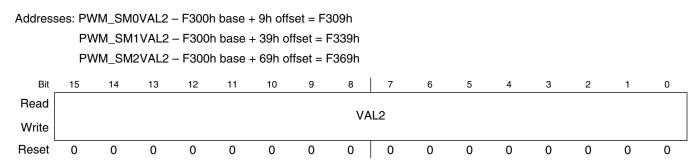

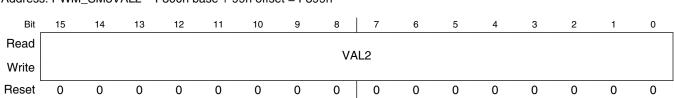

|     | 7.3.9    | PWM SMx Value Register 2 (PWMSMnVAL2)                       | 211 |  |  |

#### MC56F825x/4x Reference Manual, Rev. 2, 10/2010

10

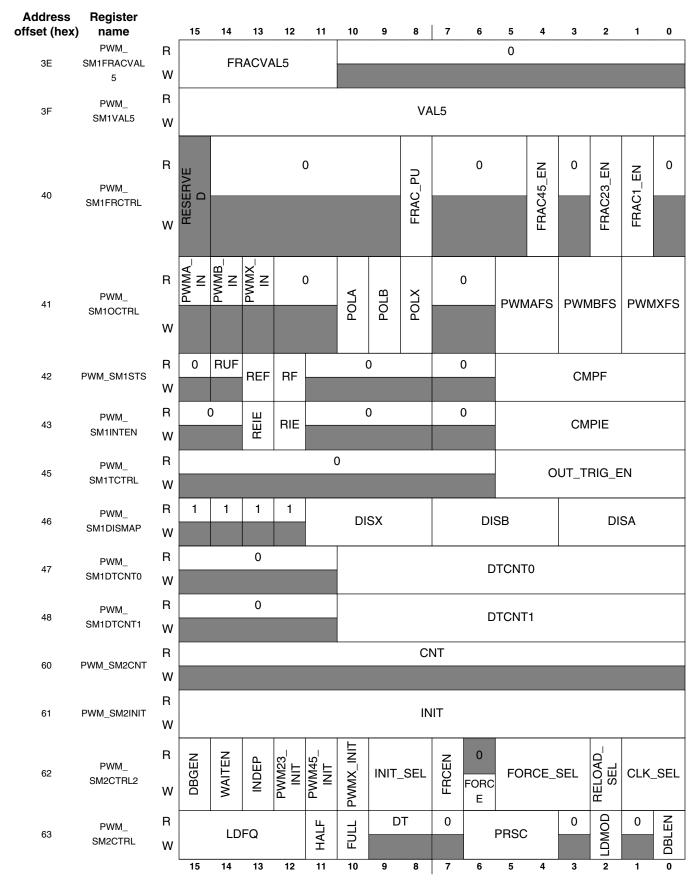

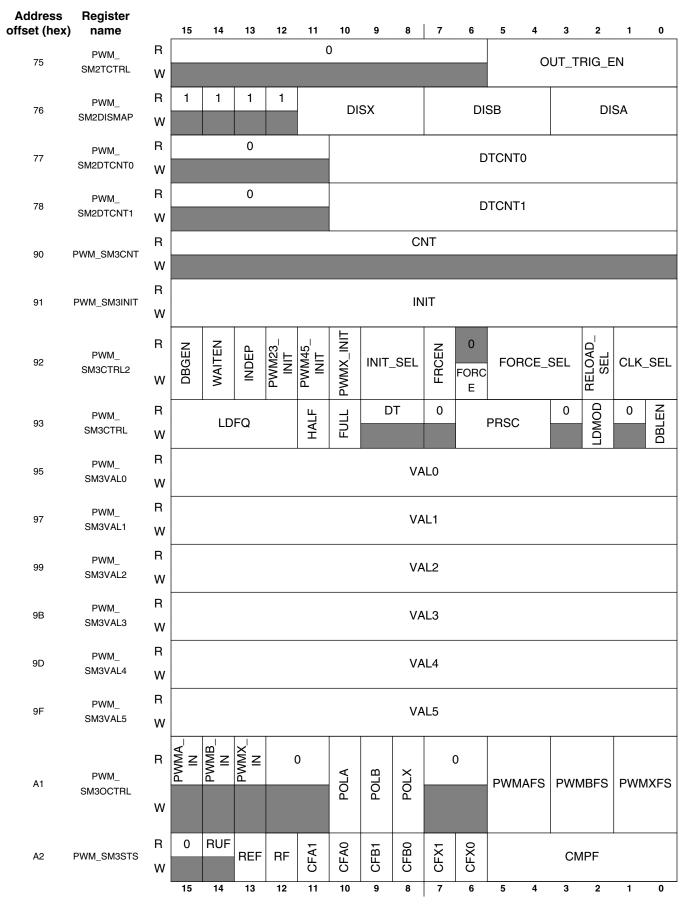

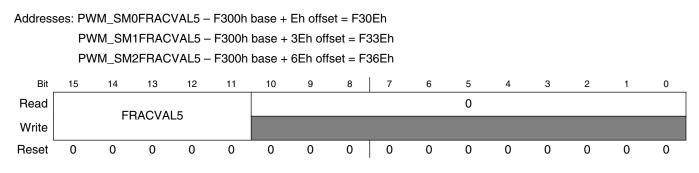

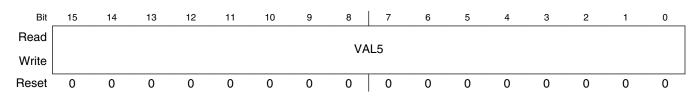

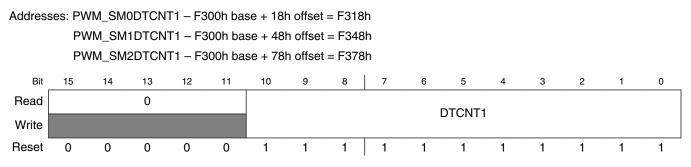

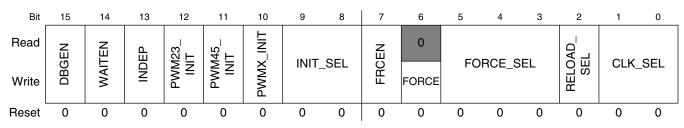

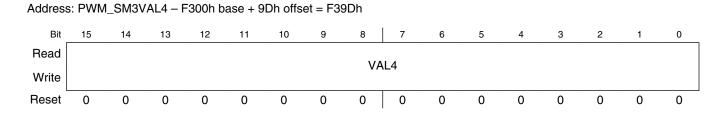

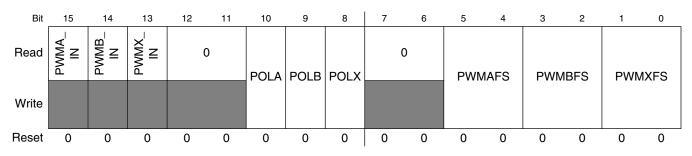

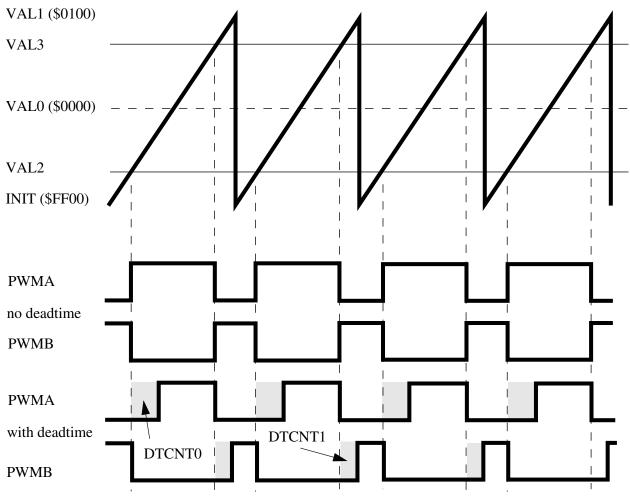

#### 7.3.10 7.3.11 PWM SMx Fractional Value Register 4 (PWMSMnFRACVAL4)......213 7.3.12 7.3.13 7.3.14 PWM SMx Fractional Value Register 5 (PWMSMnFRACVAL5)......214 7.3.15 7.3.16 7.3.17 7.3.18 7.3.19 7.3.20 7.3.21 7.3.22 PWM SMx Deadtime Count Register 0 (PWMSMnDTCNT0)......223 7.3.23 PWM SMx Deadtime Count Register 1 (PWMSMnDTCNT1).....223 7.3.24 7.3.25 7.3.26 7.3.27 7.3.28 7.3.29 7.3.30 7.3.31 7.3.32 7.3.33 7.3.34 7.3.35 7.3.36 7.3.37 7.3.38

Title

#### MC56F825x/4x Reference Manual, Rev. 2, 10/2010

**Section Number**

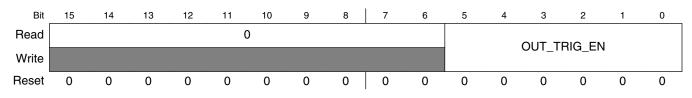

#### 7.3.39 PWM SM3 Deadtime Count Register 0 (PWMSM3DTCNT0)......239 7.3.40 PWM SM3 Deadtime Count Register 1 (PWMSM3DTCNT1)......239 7.3.41 7.3.42 PWM SM3 Capture Compare A Register (PWMSM3CAPTCOMPA)......242 7.3.43 PWM SM3 Capture Control B Register (PWMSM3CAPTCTRLB)......242 7.3.44 7.3.45 7.3.46 PWM SM3 Capture Compare X Register (PWMSM3CAPTCOMPX)......246 7.3.47 7.3.48 PWM SM3 Capture Value 1 Register (PWMSM3CVAL1)......247 PWM SM3 Capture Value 2 Register (PWMSM3CVAL2)......247 7.3.49 7.3.50 7.3.51 7.3.52 7.3.53 7.3.54 7.3.55 7.3.56 7.3.57 7.3.58 7.3.59 7.3.60 7.3.61 7.4 7.4.1 7.4.1.1 7.4.1.2 7.4.1.3 7.4.1.4

#### MC56F825x/4x Reference Manual, Rev. 2, 10/2010

12

**Section Number**

#### Preliminary

Title

| Section Number |          | Title                                          | Page |

|----------------|----------|------------------------------------------------|------|

|                | 7.4.1.5  | ADC Triggering                                 |      |

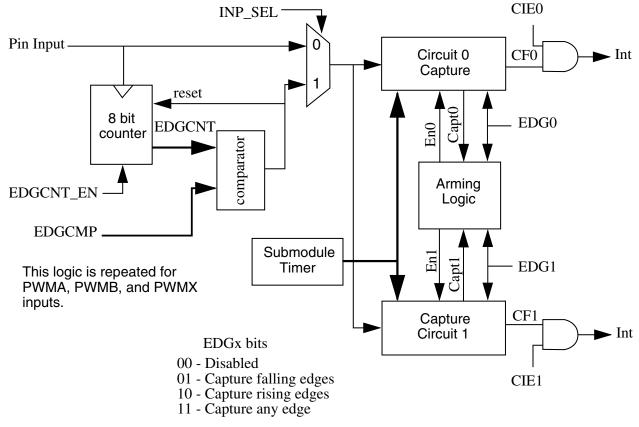

|                | 7.4.1.6  | Enhanced Capture Capabilities (E-Capture)      |      |

|                | 7.4.1.7  | Synchronous Switching of Multiple Outputs      |      |

| 7.4.2          | Function | al Details                                     |      |

|                | 7.4.2.1  | PWM Clocking                                   |      |

|                | 7.4.2.2  | Register Reload Logic                          |      |

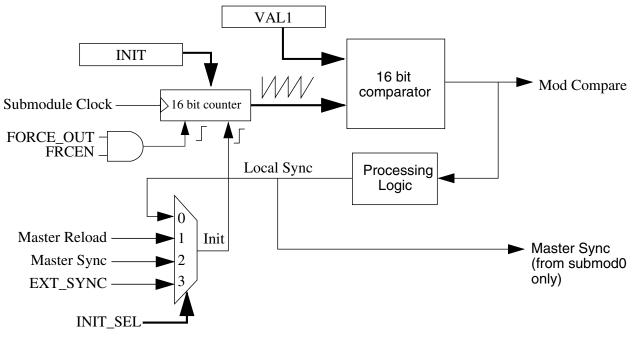

|                | 7.4.2.3  | Counter Synchronization                        |      |

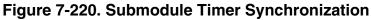

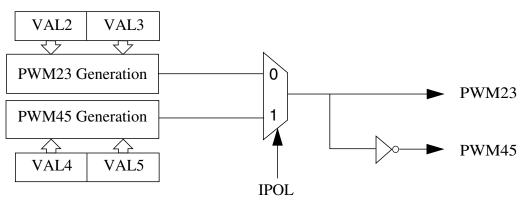

|                | 7.4.2.4  | PWM Generation                                 |      |

|                | 7.4.2.5  | Output Compare Capabilities                    |      |

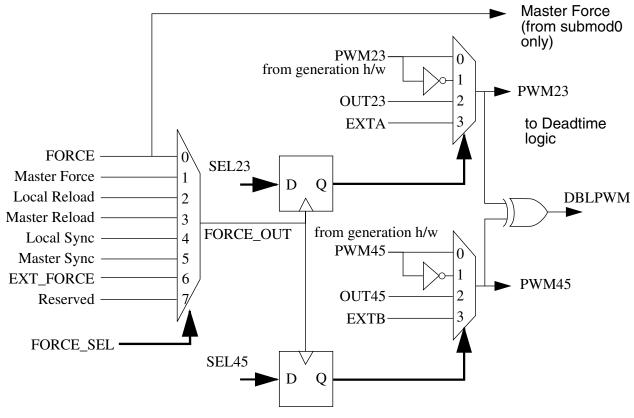

|                | 7.4.2.6  | Force Out Logic                                |      |

|                | 7.4.2.7  | Independent or Complementary Channel Operation |      |

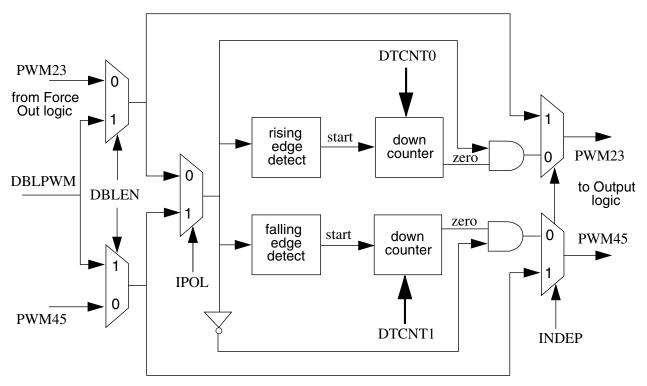

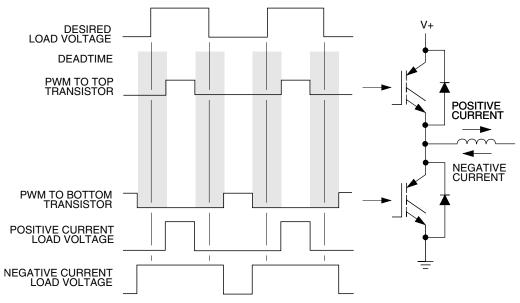

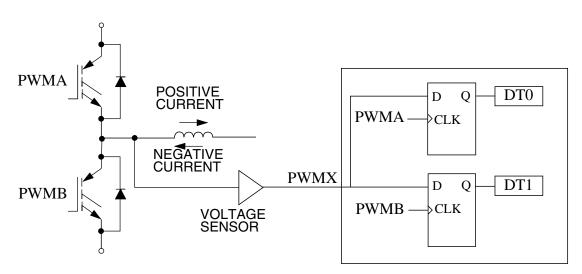

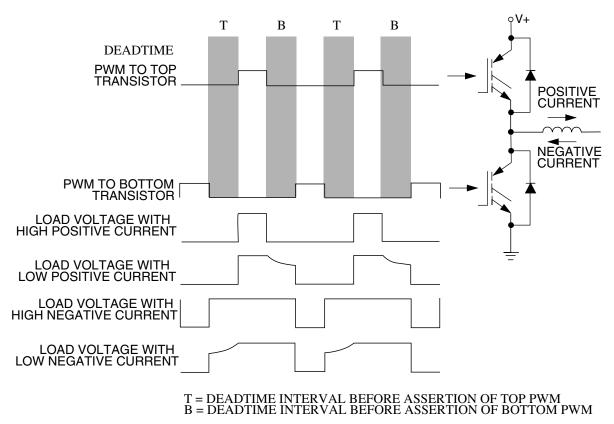

|                | 7.4.2.8  | Deadtime Insertion Logic                       |      |

|                |          | 7.4.2.8.1 Top/Bottom Correction                |      |

|                |          | 7.4.2.8.2 Manual Correction                    |      |

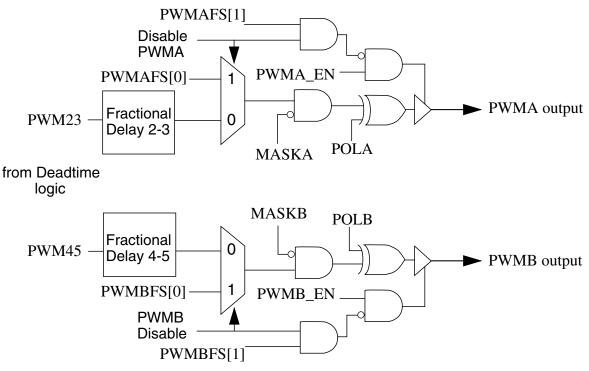

|                | 7.4.2.9  | Fractional Delay Logic                         |      |

|                | 7.4.2.10 | Output Logic                                   |      |

|                | 7.4.2.11 | E-Capture                                      |      |

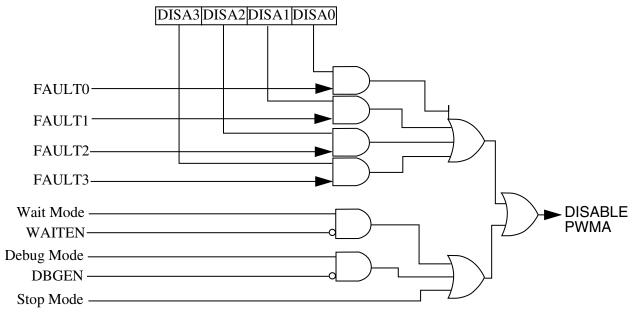

|                | 7.4.2.12 | Fault Protection                               |      |

|                |          | 7.4.2.12.1 Fault Pin Filter                    |      |

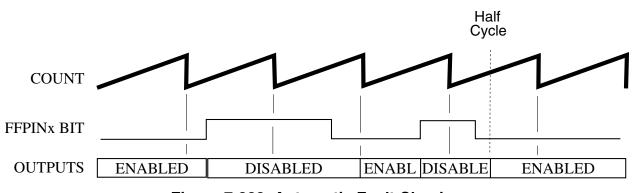

|                |          | 7.4.2.12.2 Automatic Fault Clearing            |      |

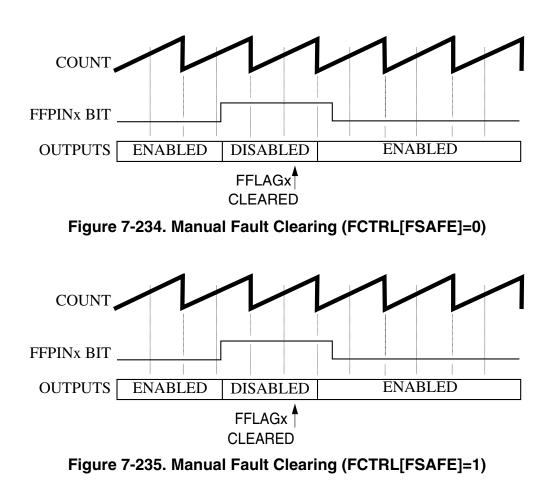

|                |          | 7.4.2.12.3 Manual Fault Clearing               |      |

|                |          | 7.4.2.12.4 Fault Testing                       |      |

| 7.4.3          | PWM Ge   | enerator Loading                               |      |

|                | 7.4.3.1  | Load Enable                                    |      |

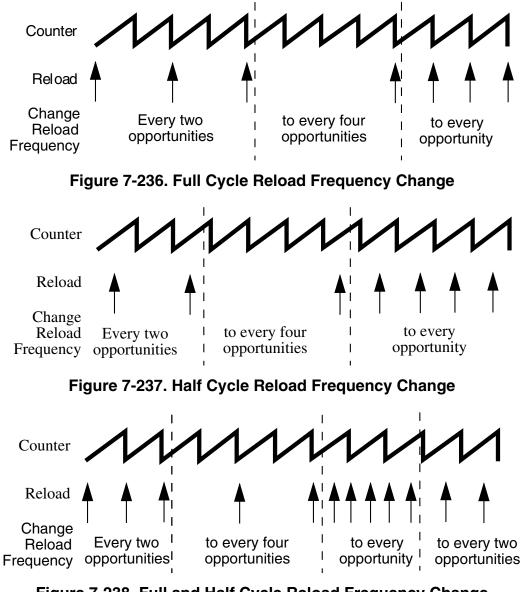

|                | 7.4.3.2  | Load Frequency                                 |      |

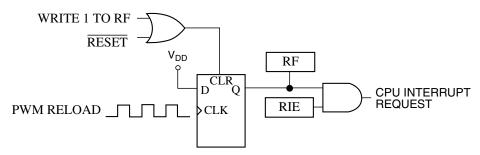

|                | 7.4.3.3  | Reload Flag                                    |      |

|                | 7.4.3.4  | Reload Errors                                  |      |

|                | 7.4.3.5  | Initialization                                 |      |

| 7.5 Resets     |          |                                                |      |

#### MC56F825x/4x Reference Manual, Rev. 2, 10/2010

Downloaded from **Elcodis.com** electronic components distributor

**Section Number**

| Section Number |          | on Number Title                      |  |

|----------------|----------|--------------------------------------|--|

| 7.6            | Interruj | pts                                  |  |

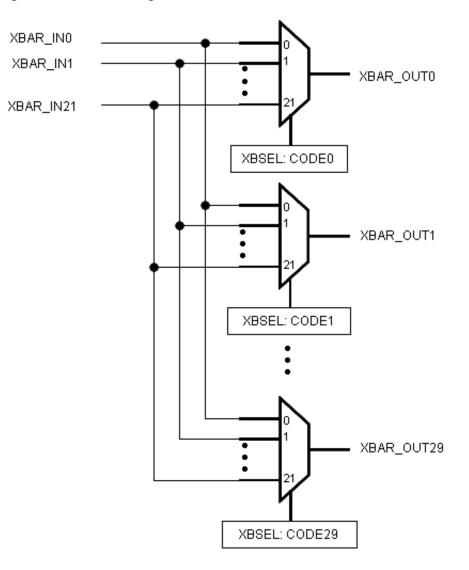

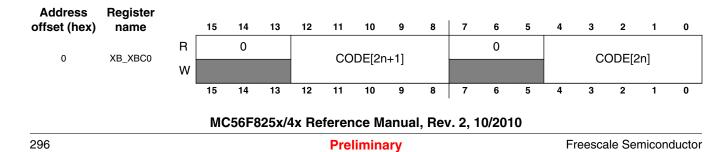

|                |          | Chapter 8<br>Crossbar Switch (XBAR)  |  |

| 8.1            | Introdu  | iction                               |  |

|                | 8.1.1    | Overview                             |  |

|                | 8.1.2    | Features                             |  |

|                | 8.1.3    | Block Diagram                        |  |

| 8.2            | Memor    | ry Map and Registers                 |  |

|                | 8.2.1    | Crossbar Control Register n (XBXBCn) |  |

| 8.3            | Functio  | onal Description                     |  |

| 8.4            | Clocks   | and Resets                           |  |

| 8.5            | Interru  | pts                                  |  |

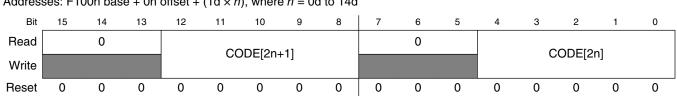

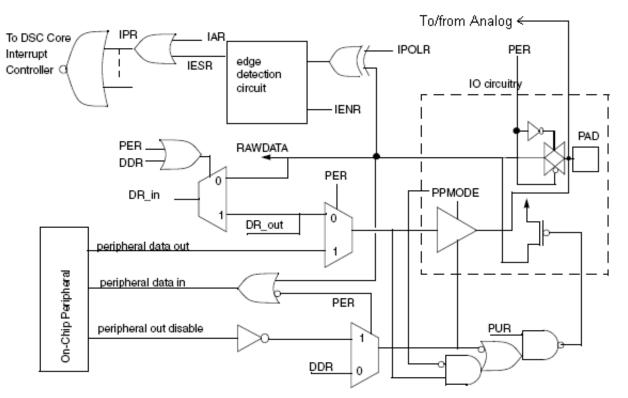

#### Chapter 9 General-Purpose Input/Output (GPIO)

| 9.1 | Overvie                 | W                                                    | 301 |

|-----|-------------------------|------------------------------------------------------|-----|

|     | 9.1.1                   | Features                                             | 301 |

|     | 9.1.2                   | Modes of Operation                                   | 302 |

| 9.2 | Memory                  | y Map and Registers                                  | 302 |

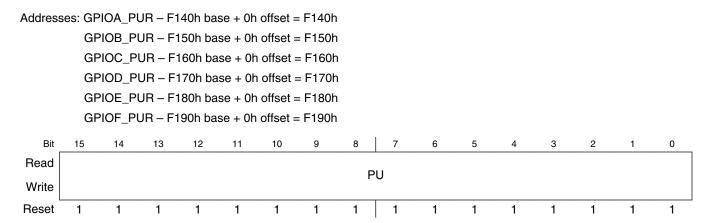

|     | 9.2.1                   | GPIO Pullup Enable Register (GPIOxA_PUR)             | 307 |

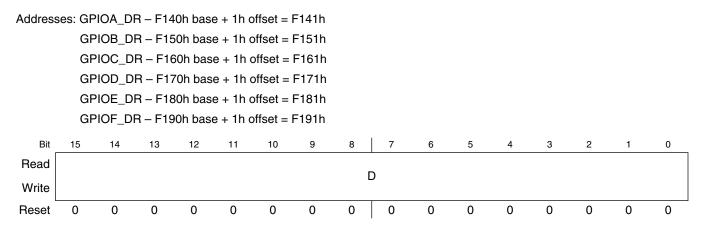

|     | 9.2.2                   | GPIO Data Register (GPIOxA_DR)                       | 308 |

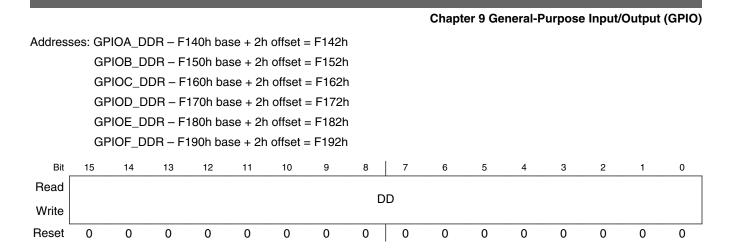

|     | 9.2.3                   | GPIO Data Direction Register (GPIOxA_DDR)            | 308 |

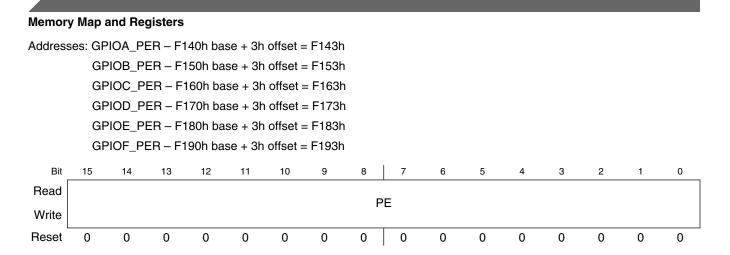

|     | 9.2.4                   | GPIO Peripheral Enable Register (GPIOxA_PER)         | 309 |

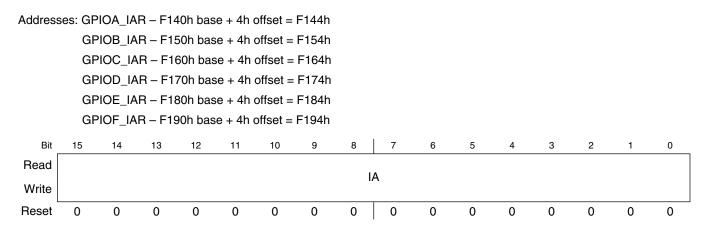

|     | 9.2.5                   | GPIO Interrupt Assert Register (GPIOxA_IAR)          | 310 |

|     | 9.2.6                   | GPIO Interrupt Enable Register (GPIOxA_IENR)         | 311 |

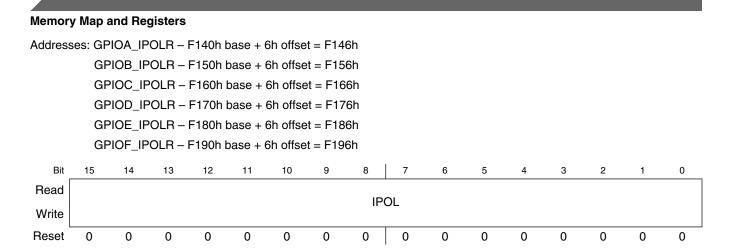

|     | 9.2.7                   | GPIO Interrupt Polarity Register (GPIOxA_IPOLR)      | 311 |

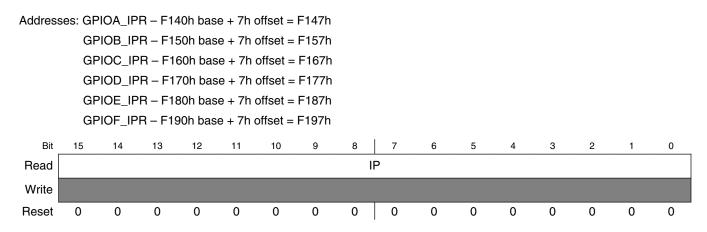

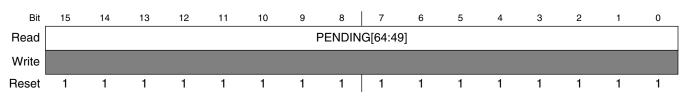

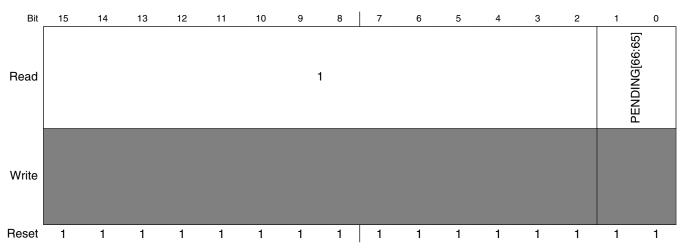

|     | 9.2.8                   | GPIO Interrupt Pending Register (GPIOxA_IPR)         | 312 |

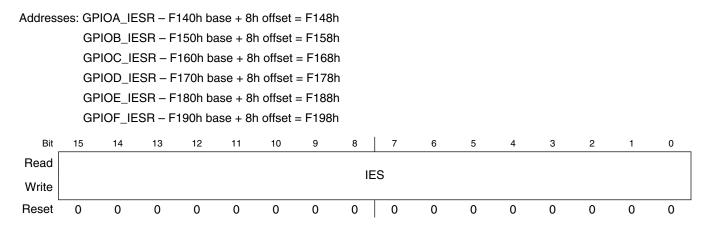

|     | 9.2.9                   | GPIO Interrupt Edge Sensitive Register (GPIOxA_IESR) | 313 |

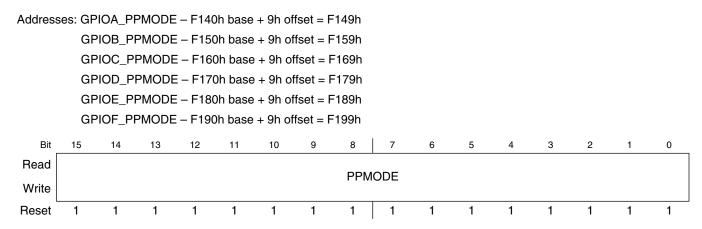

|     | 9.1.2Modes of Operation |                                                      | 313 |

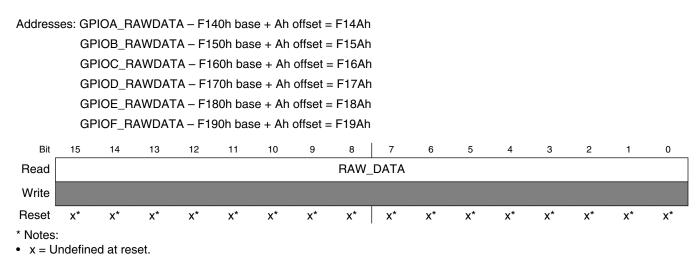

|     | 9.2.11                  | GPIO Raw Data Register (GPIOxA_RAWDATA)              | 314 |

#### MC56F825x/4x Reference Manual, Rev. 2, 10/2010

14

| Section | on Num            | nber Title                                              | Page |

|---------|-------------------|---------------------------------------------------------|------|

| 9.      | .2.12 GP          | PIO Drive Strength Control Register (GPIOxA_DRIVE)      | 315  |

| 9.3 Fi  | unctional I       | Description                                             | 315  |

| 9.4 In  | nterrupts         |                                                         | 316  |

| 9.5 C   | Clocks and        | Resets                                                  | 317  |

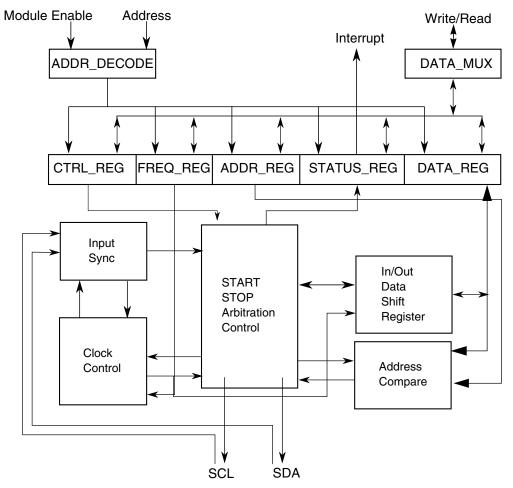

|         |                   | Chapter 10<br>Inter-Integrated Circuit (I2C)            |      |

| 10.1 In | ntroduction       | n                                                       | 319  |

| 10      | 0.1.1 Fea         | eatures                                                 | 319  |

| 10      | 0.1.2 Mo          | odes of Operation                                       | 320  |

| 10      | 0.1.3 Blo         | lock Diagram                                            | 320  |

| 10.2 Si | ignal Desc        | criptions                                               | 321  |

| 10      | 0.2.1 Set         | erial Clock Line (SCL)                                  | 321  |

| 10      | 0.2.2 Set         | erial Data Line (SDA)                                   | 321  |

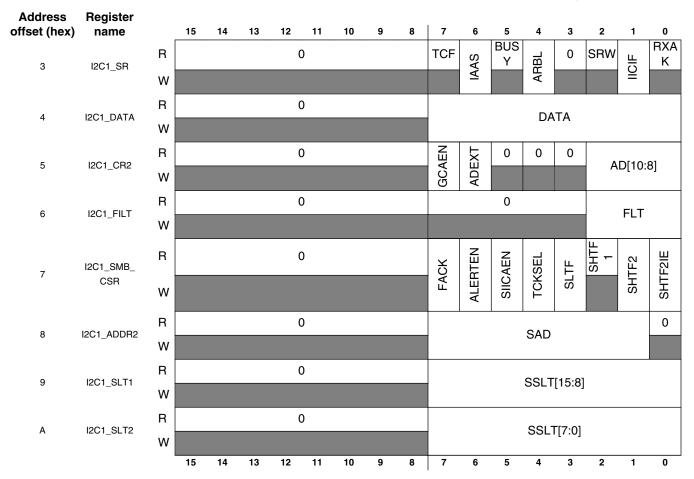

| 10.3 M  | Iemory Ma         | ap and Registers                                        | 322  |

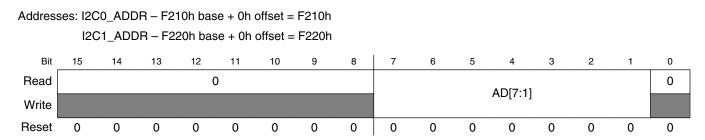

| 10      | 0.3.1 I20         | C Address Register 1 (I2Cx_ADDR)                        | 323  |

| 10      | 0.3.2 I2C         | C Frequency Divider register (I2Cx_FREQDIV)             | 324  |

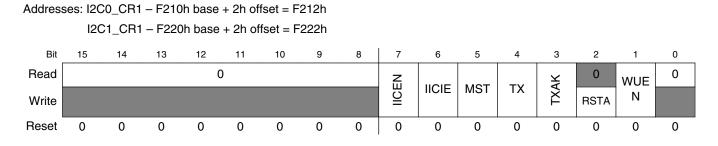

| 10      | 0.3.3 I20         | C Control Register 1 (I2Cx_CR1)                         | 325  |

| 10      | 0.3.4 I20         | C Status Register (I2Cx_SR)                             | 326  |

| 10      | 0.3.5 I2C         | C Data I/O register (I2Cx_DATA)                         | 328  |

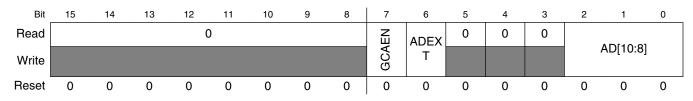

| 10      | 0.3.6 I2C         | C Control Register 2 (I2Cx_CR2)                         | 329  |

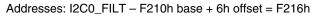

| 10      | 0.3.7 I2C         | C Programmable Input Glitch Filter register (I2Cx_FILT) | 330  |

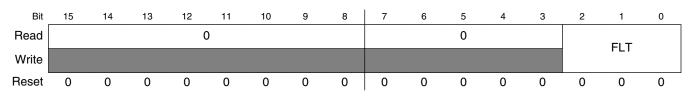

| 10      | 0.3.8 I2C         | C SMBus Control and Status Register (I2Cx_SMB_CSR)      | 330  |

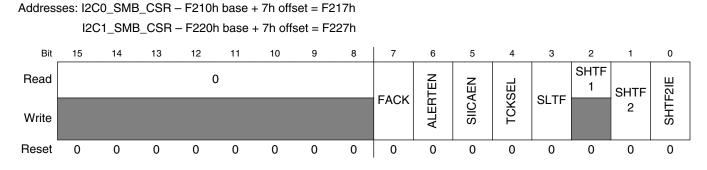

| 10      | 0.3.9 I2 <b>C</b> | C Address Register 2 (I2Cx_ADDR2)                       | 332  |

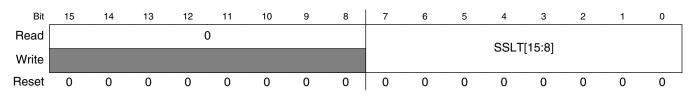

| 10      | 0.3.10 I2C        | C SCL Low Timeout register High (I2Cx_SLT1)             | 333  |

| 10      | 0.3.11 I20        | C SCL Low Timeout register Low (I2Cx_SLT2)              | 333  |

| 10.4 Fi | unctional I       | Description                                             | 333  |

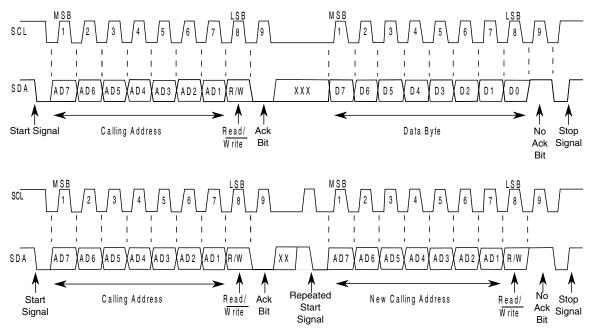

| 10      | 0.4.1 I2 <b>C</b> | C Protocol                                              | 334  |

|         | 10.               | 0.4.1.1 START Signal                                    | 334  |

|         | 10.               | 0.4.1.2 Slave Address Transmission                      | 335  |

#### Downloaded from Elcodis.com electronic components distributor

#### 10.4.1.3 10.4.1.4 10.4.1.5 10.4.1.6 10.4.1.7 10.4.1.8 10.4.1.9 10.4.2 10.4.2.1 10.4.2.2 10.4.3 10.4.4 10.4.4.1 10.4.5 10.4.6 10.4.6.1 10.4.6.2 10.4.6.3 10.4.6.4 10.4.6.5 10.4.6.6 10.4.6.7

Title

MC56F825x/4x Reference Manual, Rev. 2, 10/2010

Section Number

**Preliminary**

#### Chapter 11 Queued Serial Communications Interface (QSCI)

| 11.1 | Introduc | tion        |                                | 351 |

|------|----------|-------------|--------------------------------|-----|

|      | 11.1.1   | Features    |                                | 351 |

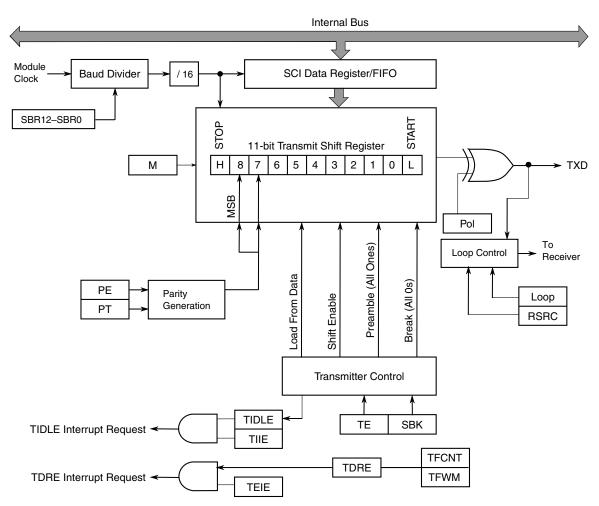

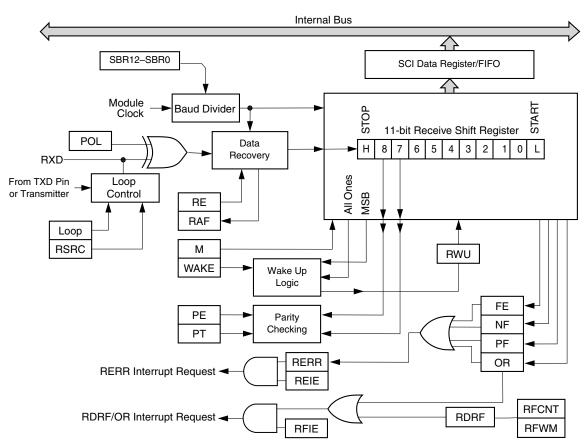

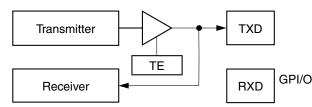

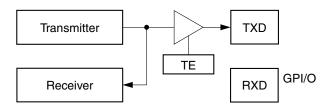

|      | 11.1.2   | SCI Block   | k Diagram                      |     |

| 11.2 | External | Signal De   | escriptions                    |     |

|      | 11.2.1   | TXD —T      | 'ransmit Data                  |     |

|      | 11.2.2   | RXD —R      | Receiver Data                  |     |

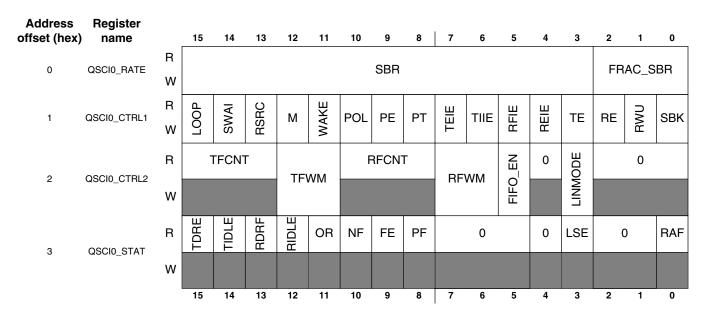

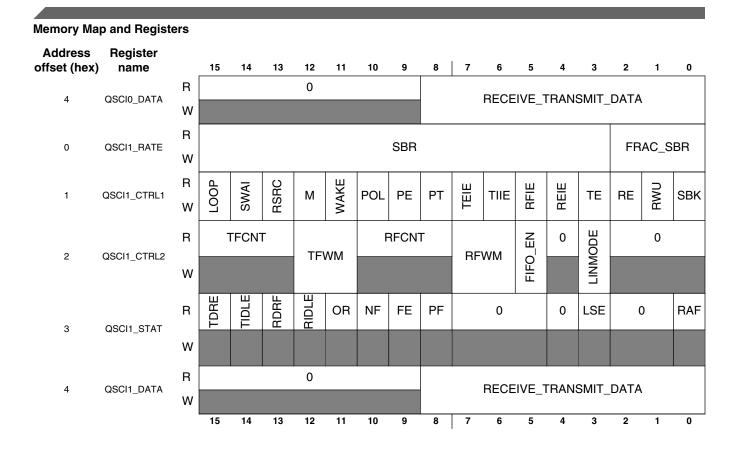

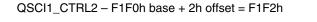

| 11.3 | Memory   | Map and I   | Registers                      |     |

|      | 11.3.1   | QSCI Bau    | ud Rate Register (QSCIx_RATE)  |     |

|      | 11.3.2   | QSCI Cor    | ntrol Register 1 (QSCIx_CTRL1) |     |

|      | 11.3.3   | QSCI Cor    | ntrol Register 2 (QSCIx_CTRL2) |     |

|      | 11.3.4   | QSCI Stat   | tus Register (QSCLx_STAT)      |     |

|      | 11.3.5   | QSCI Dat    | ta Register (QSCLx_DATA)       |     |

| 11.4 | Function | nal Descrip | tion                           |     |

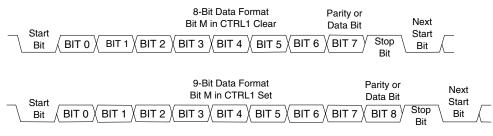

|      | 11.4.1   | Data Fran   | ne Format                      |     |

|      | 11.4.2   | Baud-Rate   | e Generation                   |     |

|      | 11.4.3   | Transmitt   | er                             |     |

|      |          | 11.4.3.1    | Character Length               |     |

|      |          | 11.4.3.2    | Character Transmission         |     |

|      |          | 11.4.3.3    | Break Characters               |     |

|      |          | 11.4.3.4    | Preambles                      |     |

|      | 11.4.4   | Receiver.   |                                |     |

|      |          | 11.4.4.1    | Character Length               |     |

|      |          | 11.4.4.2    | Character Reception            |     |

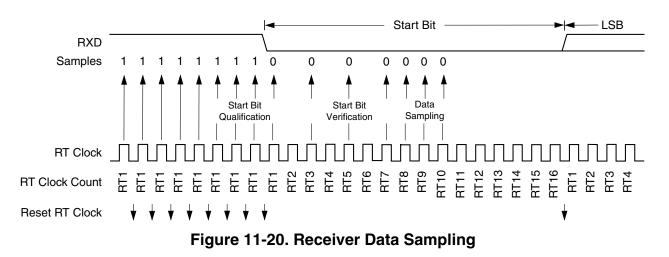

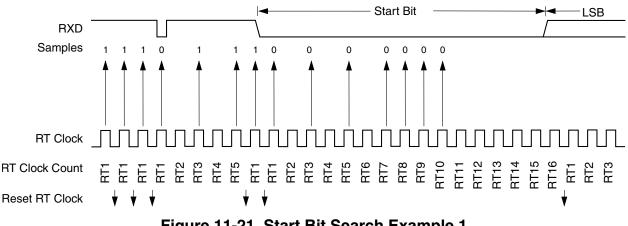

|      |          | 11.4.4.3    | Data Sampling                  |     |

|      |          | 11.4.4.4    | Framing Errors                 |     |

|      |          | 11.4.4.5    | Baud-Rate Tolerance            |     |

|      |          | 11.4.4.6    | Slow Data Tolerance            |     |

| Section Number |          | umber      | Title                       | Page |

|----------------|----------|------------|-----------------------------|------|

|                |          | 11.4.4.7   | Fast Data Tolerance         |      |

|                |          | 11.4.4.8   | Receiver Wakeup             |      |

|                |          | 11.4.4.9   | Single-Wire Operation       |      |

|                |          | 11.4.4.10  | Loop Operation              |      |

|                | 11.4.5   | LIN Slave  | Operation                   |      |

|                | 11.4.6   | Low-Powe   | er Options                  |      |

|                |          | 11.4.6.1   | Run Mode                    |      |

|                |          | 11.4.6.2   | Wait Mode                   |      |

|                |          | 11.4.6.3   | Stop Mode                   |      |

| 11.5           | Resets   |            |                             |      |

| 11.6           | Clocks.  |            |                             |      |

| 11.7           | Interrup | ots        |                             |      |

|                | 11.7.1   | Descriptio | on of Interrupt Operation   |      |

|                |          | 11.7.1.1   | Transmitter Empty Interrupt |      |

|                |          | 11.7.1.2   | Transmitter Idle Interrupt  |      |

|                |          | 11.7.1.3   | Receiver Full Interrupt     |      |

|                |          | 11.7.1.4   | Receive Error Interrupt     |      |

|                | 11.7.2   | Recovery   | from Wait and Stop Mode     |      |

#### Chapter 12 Queued Serial Peripheral Interface (QSPI)

| 12.1 I  | Introduc | tion         |                            | 385 |

|---------|----------|--------------|----------------------------|-----|

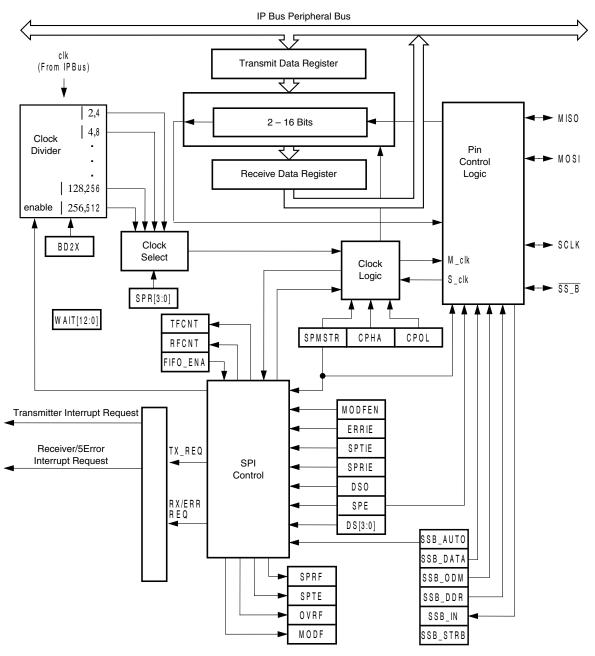

| 1       | 12.1.1   | Overview     |                            | 385 |

| 1       | 12.1.2   | Block Dia    | gram                       | 386 |

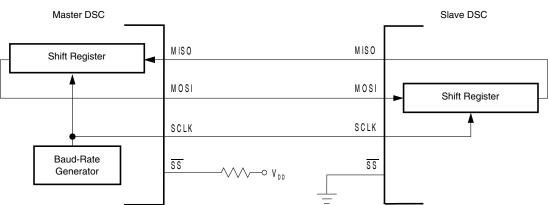

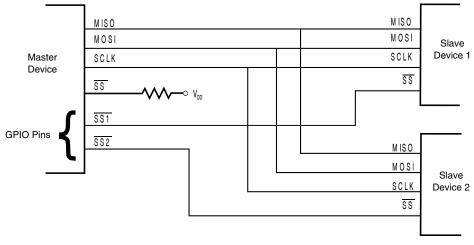

| 12.2 \$ | Signal D | Descriptions | 5                          | 387 |

| 1       | 12.2.1   | External I   | /O Signals                 | 387 |

|         |          | 12.2.1.1     | MISO (Master In/Slave Out) | 387 |

|         |          | 12.2.1.2     | MOSI (Master Out/Slave In) | 387 |

|         |          | 12.2.1.3     | SCLK (Serial Clock)        | 388 |

|         |          | 12.2.1.4     | SS (Slave Select)          | 388 |

#### MC56F825x/4x Reference Manual, Rev. 2, 10/2010

18

| Section N     | lumber       | Title                                       | Page |

|---------------|--------------|---------------------------------------------|------|

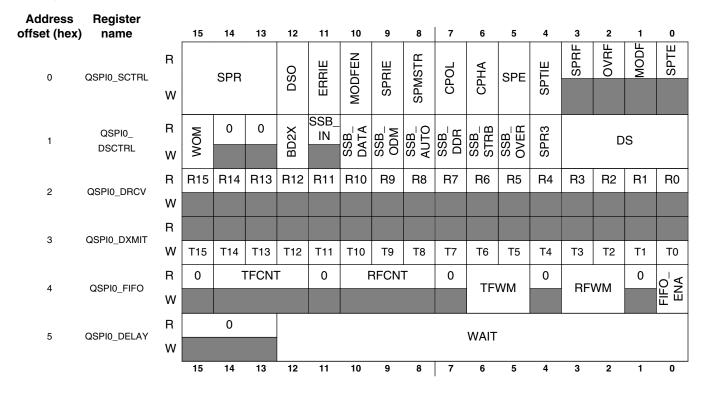

| 12.3 Memor    | y Map Reg    | isters                                      |      |

| 12.3.1        | SPI Statu    | as and Control Register (QSPI0SCTRL)        |      |

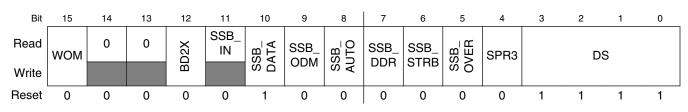

| 12.3.2        | SPI Data     | Size and Control Register (QSPI0DSCTRL)     |      |

| 12.3.3        | SPI Data     | Receive Register (QSPI0DRCV)                |      |

| 12.3.4        | SPI Data     | Transmit Register (QSPI0DXMIT)              |      |

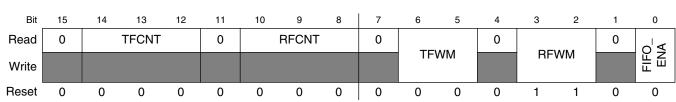

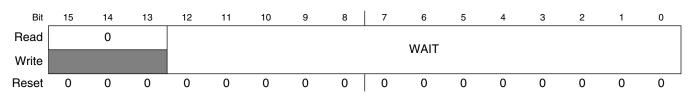

| 12.3.5        | SPI FIFO     | O Control Register (QSPI0FIFO)              |      |

| 12.3.6        | SPI Word     | d Delay Register (QSPI0DELAY)               |      |

| 12.4 Function | onal Descrip | ption                                       |      |

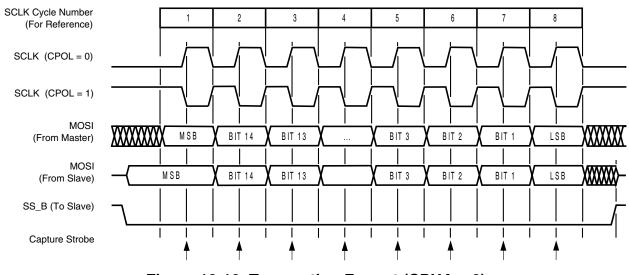

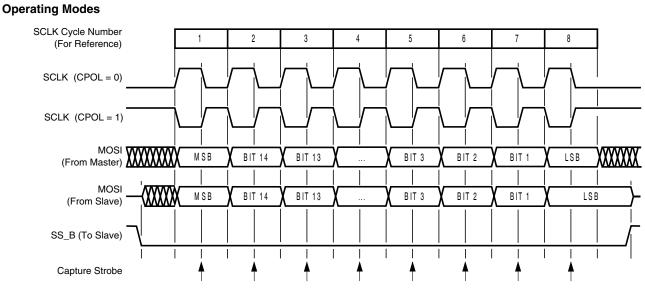

| 12.4.1        | Operating    | g Modes                                     |      |

|               | 12.4.1.1     | Master Mode                                 |      |

|               | 12.4.1.2     | Slave Mode                                  |      |

|               | 12.4.1.3     | Wired-OR Mode                               |      |

| 12.4.2        | Transacti    | ion Formats                                 |      |

|               | 12.4.2.1     | Data Transaction Length                     |      |

|               | 12.4.2.2     | Data Shift Ordering                         |      |

|               | 12.4.2.3     | Clock Phase and Polarity Controls           |      |

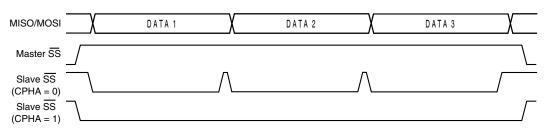

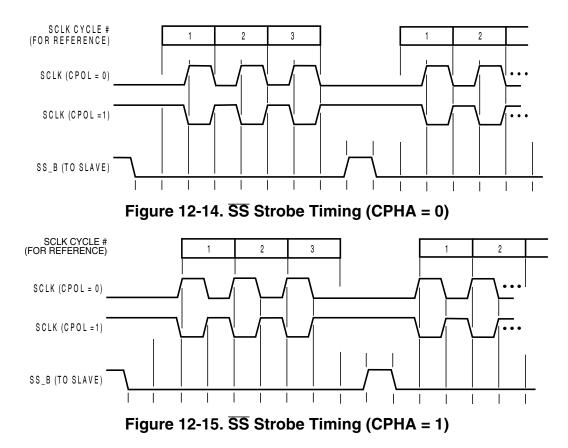

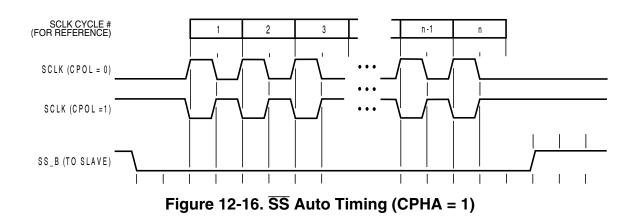

|               | 12.4.2.4     | Transaction Format When CPHA = 0            |      |

|               | 12.4.2.5     | Transaction Format When CPHA = 1            |      |

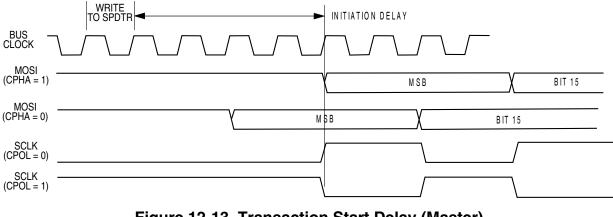

|               | 12.4.2.6     | Transaction Initiation Latency              |      |

|               | 12.4.2.7     | SS Hardware-Generated Timing in Master Mode |      |

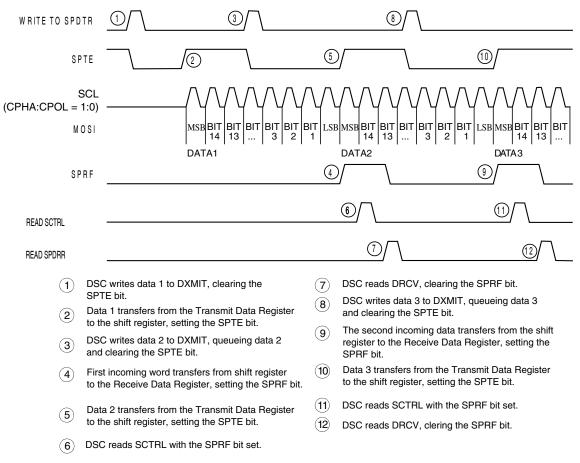

| 12.4.3        | Transmis     | sion Data                                   |      |

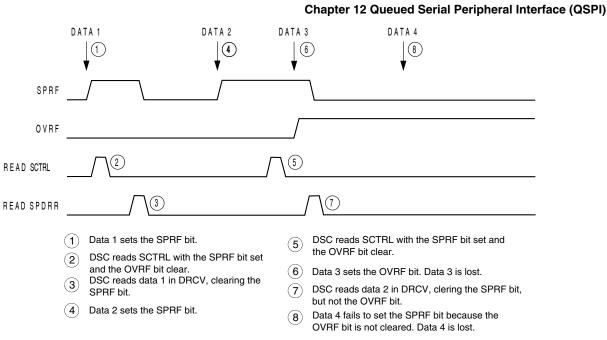

| 12.4.4        | Error Cor    | nditions                                    | 410  |

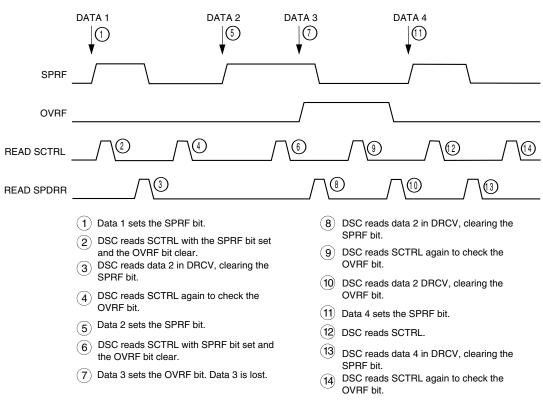

|               | 12.4.4.1     | Overflow Error                              | 410  |

|               | 12.4.4.2     | Mode Fault Error                            |      |

|               |              | 12.4.4.2.1 Master Mode Fault                |      |

|               |              | 12.4.4.2.2 Slave Mode Fault                 |      |

| 12.4.5        | Resetting    | g the SPI                                   | 414  |

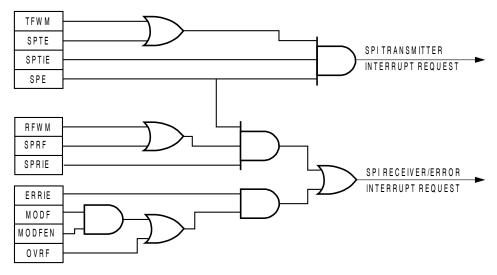

| 12.5 Interru  | pts          |                                             |      |

Downloaded from **Elcodis.com** electronic components distributor

**Section Number**

#### Title

Page

#### Chapter 13 Freescale's Scalable Controller Area Network (MSCAN)

| 13.1 | Introduc | tion                                                           | 417 |

|------|----------|----------------------------------------------------------------|-----|

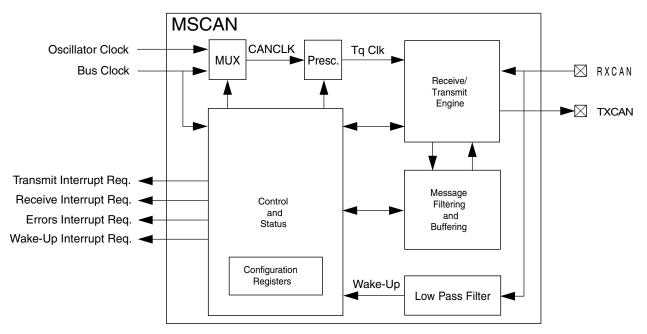

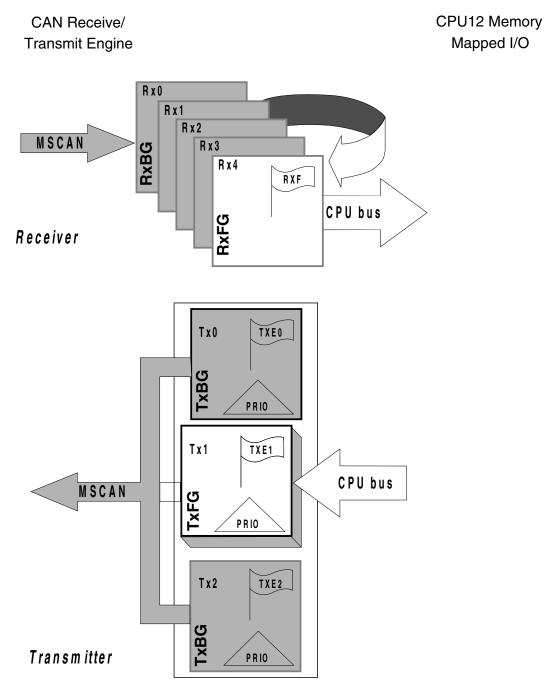

|      | 13.1.1   | Block Diagram                                                  | 417 |

|      | 13.1.2   | Features                                                       | 418 |

|      | 13.1.3   | Modes of Operation                                             | 419 |

| 13.2 | External | Signal Description                                             | 419 |

|      | 13.2.1   | RXCAN — CAN Receiver Input Pin                                 | 419 |

|      | 13.2.2   | TXCAN — CAN Transmitter Output Pin                             | 419 |

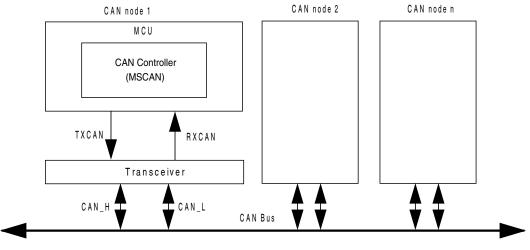

|      | 13.2.3   | CAN System                                                     | 420 |

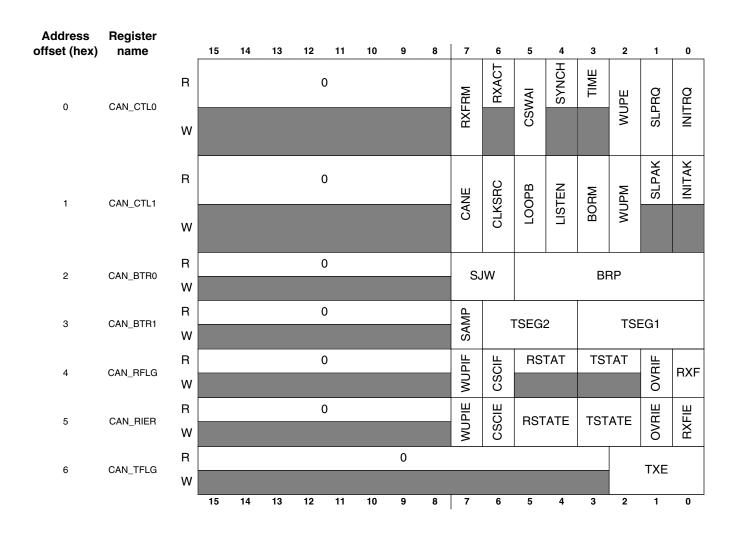

| 13.3 | Memory   | Map and Register Definition                                    | 420 |

|      | 13.3.1   | Programmer's Model of Message Storage                          | 420 |

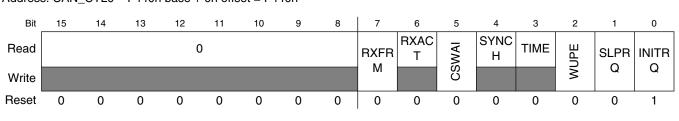

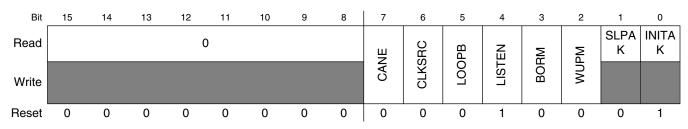

|      | 13.3.2   | MSCAN Control Register 0 (CANCTL0)                             | 427 |

|      | 13.3.3   | MSCAN Control Register 1 (CANCTL1)                             | 430 |

|      | 13.3.4   | MSCAN Bus Timing Register 0 (CANBTR0)                          | 432 |

|      | 13.3.5   | MSCAN Bus Timing Register 1 (CANBTR1)                          | 433 |

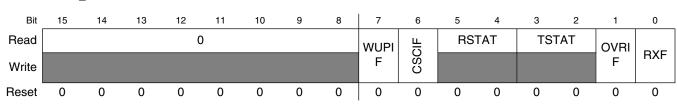

|      | 13.3.6   | MSCAN Receiver Flag Register (CANRFLG)                         | 434 |

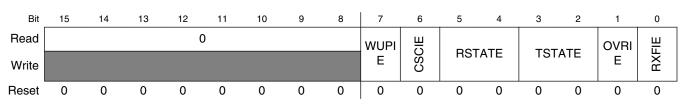

|      | 13.3.7   | MSCAN Receiver Interrupt Enable Register (CANRIER)             | 436 |

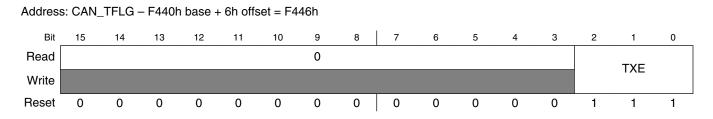

|      | 13.3.8   | MSCAN Transmitter Flag Register (CANTFLG)                      | 437 |

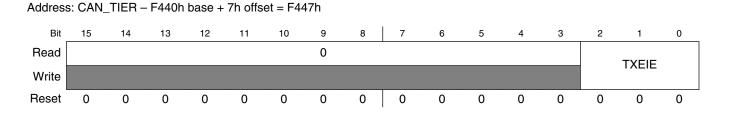

|      | 13.3.9   | MSCAN Transmitter Interrupt Enable Register (CANTIER)          | 438 |

|      | 13.3.10  | MSCAN Transmitter Message Abort Request Register (CANTARQ)     | 439 |

|      | 13.3.11  | MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK) | 440 |

|      | 13.3.12  | MSCAN Transmit Buffer Selection Register (CANTBSEL)            | 441 |

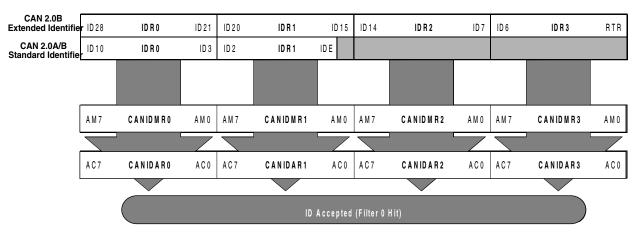

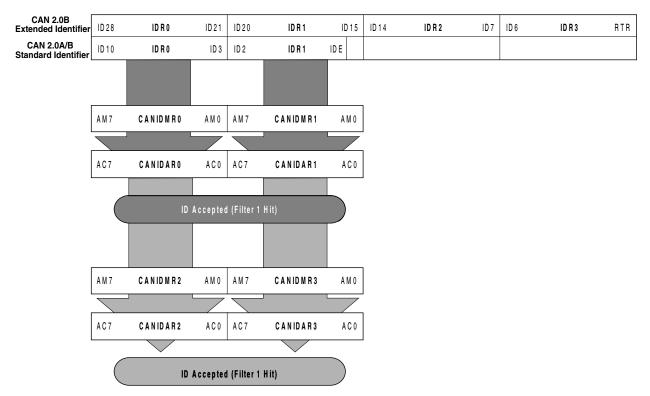

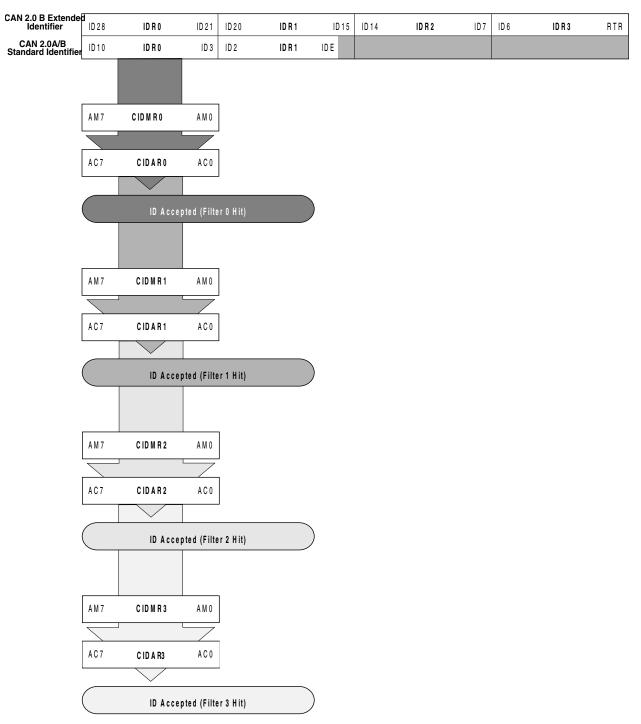

|      | 13.3.13  | MSCAN Identifier Acceptance Control Register (CANIDAC)         | 442 |

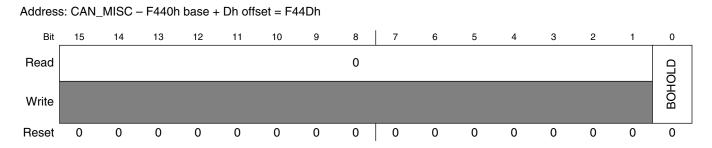

|      | 13.3.14  | CANMISC                                                        | 442 |

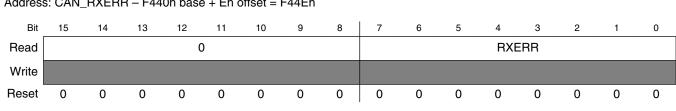

|      | 13.3.15  | MSCAN Receive Error Counter Register (CANRXERR)                | 443 |

|      | 13.3.16  | MSCAN Transmit Error Counter Register (CANTXERR)               | 444 |

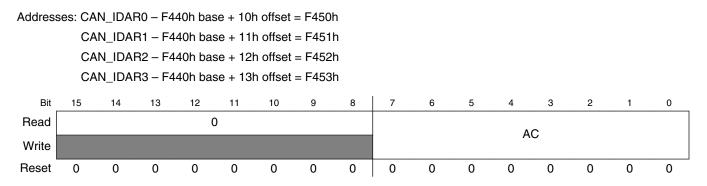

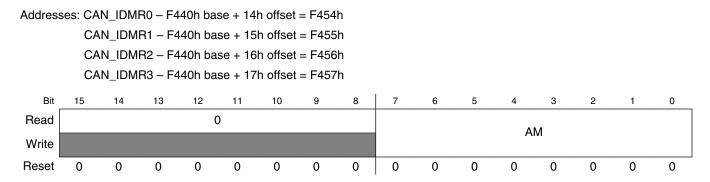

|      | 13.3.17  | MSCAN Identifier Acceptance Registers (First Bank) (CANIDARn)  | 445 |

|      | 13.3.18  | MSCAN Identifier Mask Registers (First Bank) (CANIDMRn)        | 446 |

#### MC56F825x/4x Reference Manual, Rev. 2, 10/2010 Preliminary

20

#### **Section Number**

#### Title

## Page

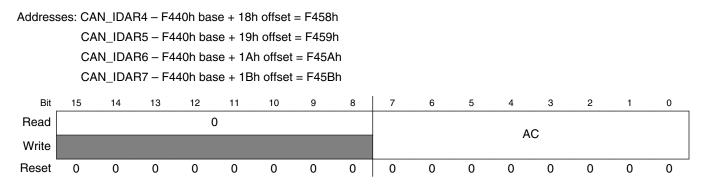

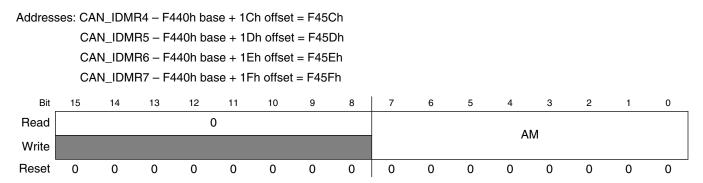

|      | 13.3.19  | MSCAN Identifier Acceptance Registers (Second Bank) (CANIDARn)                                                  | 447 |

|------|----------|-----------------------------------------------------------------------------------------------------------------|-----|

|      | 13.3.20  | MSCAN Identifier Mask Registers (Second Bank) (CANIDMRn)                                                        | 448 |

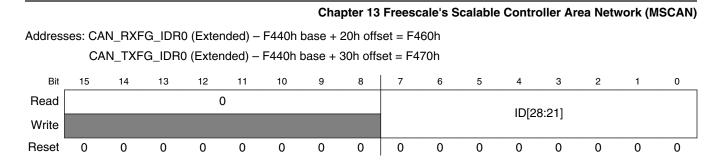

|      | 13.3.21  | MSCAN Receive and Transmit Buffer Identifier Register 0 - Extended Identifer Mapping (CANnXFG_IDR0 (Extended))  | 448 |

|      | 13.3.22  | MSCAN Receive and Transmit Buffer Identifier Register 0 - Standard Identifer Mapping (CANnXFG_IDR0 (Standard))  | 449 |

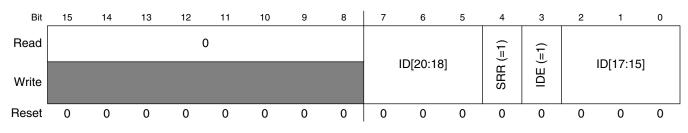

|      | 13.3.23  | MSCAN Receive and Transmit Buffer Identifier Register 1 - Extended Identifer Mapping (CANnXFG_IDR1 (Extended))  | 450 |

|      | 13.3.24  | MSCAN Receive and Transmit Buffer Identifier Register 1 - Standard Identifier Mapping (CANnXFG_IDR1 (Standard)) | 451 |

|      | 13.3.25  | MSCAN Receive and Transmit Buffer Identifier Register 2 - Extended Identifer Mapping (CANnXFG_IDR2 (Extended))  | 452 |

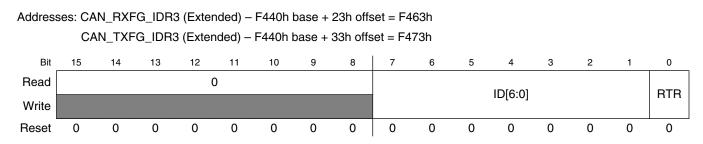

|      | 13.3.26  | MSCAN Receive and Transmit Buffer Identifier Register 3 - Extended Identifier Mapping (CANnXFG_IDR3 (Extended)) | 452 |

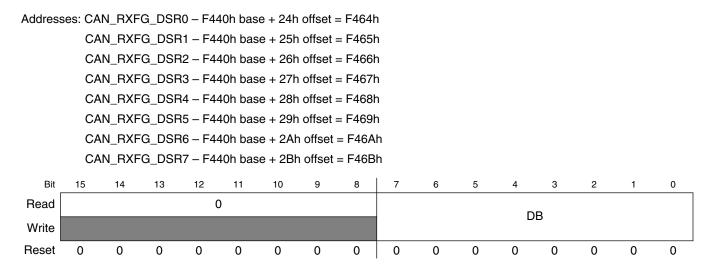

|      | 13.3.27  | Receive Buffer Data Segment Registers (CANRXFG_DSRn)                                                            | 453 |

|      | 13.3.28  | MSCAN Receive Buffer Data Length Register (CANRXFG_DLR)                                                         | 454 |

|      | 13.3.29  | Receive Buffer Time Stamp Register - High Byte (CANRXFG_TSRH)                                                   | 454 |

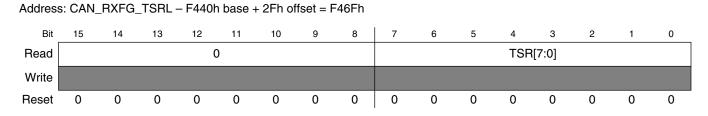

|      | 13.3.30  | Receive Buffer Time Stamp Register - Low Byte (CANRXFG_TSRL)                                                    | 455 |

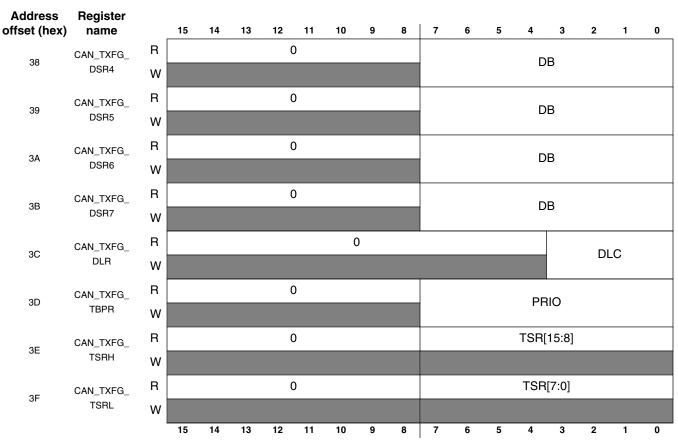

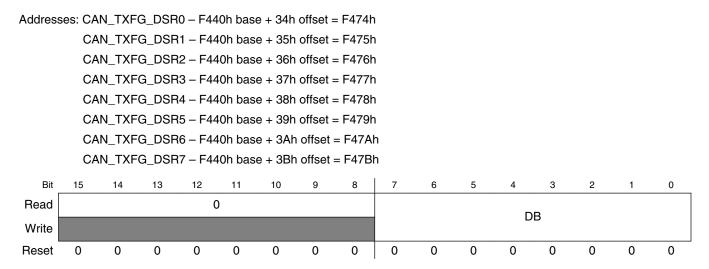

|      | 13.3.31  | Transmit Buffer Data Segment Registers (CANTXFG_DSRn)                                                           | 456 |

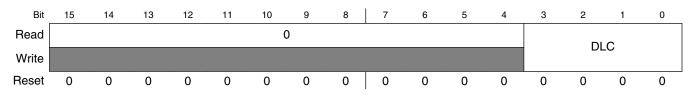

|      | 13.3.32  | MSCAN Transmit Buffer Data Length Register (CANTXFG_DLR)                                                        | 457 |

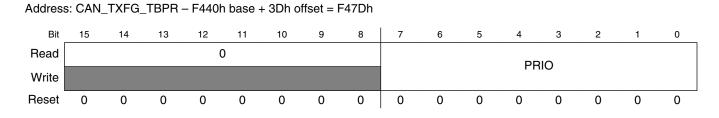

|      | 13.3.33  | MSCAN Transmit Buffer Priority Register (CANTXFG_TBPR)                                                          | 457 |

|      | 13.3.34  | Transmit Buffer Time Stamp Register - High Byte (CANTXFG_TSRH)                                                  | 458 |

|      | 13.3.35  | Transmit Buffer Time Stamp Register - Low Byte (CANTXFG_TSRL)                                                   | 459 |

| 13.4 | Function | nal Description                                                                                                 | 460 |

|      | 13.4.1   | General                                                                                                         | 460 |

|      | 13.4.2   | Message Storage                                                                                                 | 461 |

|      |          | 13.4.2.1 Message Transmit Background                                                                            | 462 |

|      |          | 13.4.2.2 Transmit Structures                                                                                    | 462 |

|      |          | 13.4.2.3 Receive Structures                                                                                     | 464 |

MC56F825x/4x Reference Manual, Rev. 2, 10/2010

Downloaded from **Elcodis.com** electronic components distributor

| Sec  | tion N    | umber       | Title                              | Page |

|------|-----------|-------------|------------------------------------|------|

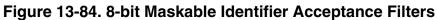

|      | 13.4.3    | Identifier  | Acceptance Filter                  |      |

|      |           | 13.4.3.1    | Protocol Violation Protection      |      |

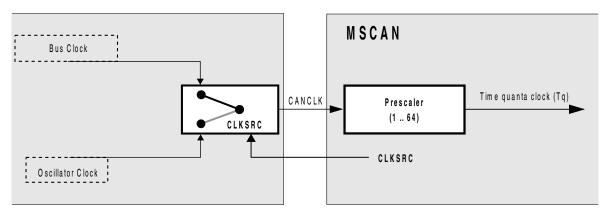

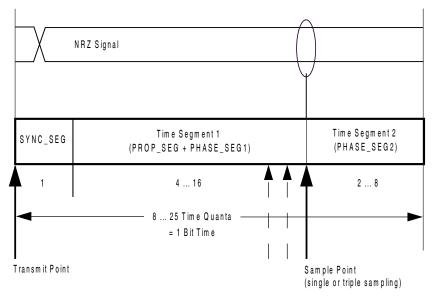

|      |           | 13.4.3.2    | Clock System                       |      |

|      | 13.4.4    | Modes of    | f Operation                        |      |

|      |           | 13.4.4.1    | Normal Modes                       |      |

|      |           | 13.4.4.2    | Special Modes                      |      |

|      |           | 13.4.4.3    | Emulation Modes                    |      |

|      |           | 13.4.4.4    | Listen-Only Mode                   |      |

|      |           | 13.4.4.5    | Security Modes                     |      |

|      | 13.4.5    | Low-Pow     | ver Options                        |      |

|      |           | 13.4.5.1    | Operation in Run Mode              | 474  |

|      |           | 13.4.5.2    | Operation in Wait Mode             |      |

|      |           | 13.4.5.3    | Operation in Stop Mode             |      |

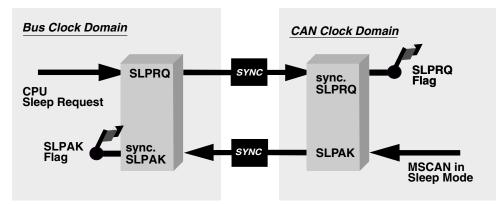

|      |           | 13.4.5.4    | MSCAN Sleep Mode                   |      |

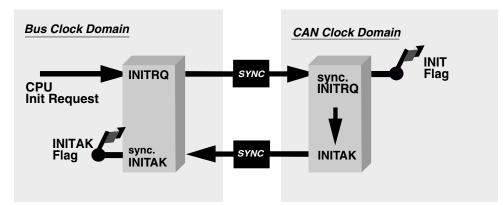

|      |           | 13.4.5.5    | MSCAN Initialization Mode          |      |

|      |           | 13.4.5.6    | MSCAN Power Down Mode              |      |

|      |           | 13.4.5.7    | Programmable Wake-Up Function      |      |

|      | 13.4.6    | Reset Init  | tialization                        |      |

|      | 13.4.7    | Interrupts  | 5                                  |      |

|      |           | 13.4.7.1    | Description of Interrupt Operation |      |

|      |           | 13.4.7.2    | Transmit Interrupt                 |      |

|      |           | 13.4.7.3    | Receive Interrupt                  |      |

|      |           | 13.4.7.4    | Wakeup Interrupt                   |      |

|      |           | 13.4.7.5    | Error Interrupt                    |      |

|      |           | 13.4.7.6    | Interrupt Acknowledge              |      |

|      |           | 13.4.7.7    | Recovery from Stop or Wait         |      |

| 13.5 | Initializ | ation Appli | ication Information                |      |

|      | 13.5.1    | MSCAN       | initialization                     |      |

|      | 13.5.2    | Bus-Off I   | Recovery                           |      |

#### MC56F825x/4x Reference Manual, Rev. 2, 10/2010 **Preliminary**

#### 22

# Section Number

#### Page

#### Chapter 14 Interrupt Controller (INTC)

| 14.1 | I Introduction |                                                            |     |

|------|----------------|------------------------------------------------------------|-----|

|      | 14.1.1         | References                                                 | 483 |

|      | 14.1.2         | Features                                                   | 483 |

|      | 14.1.3         | Modes of Operation                                         | 483 |

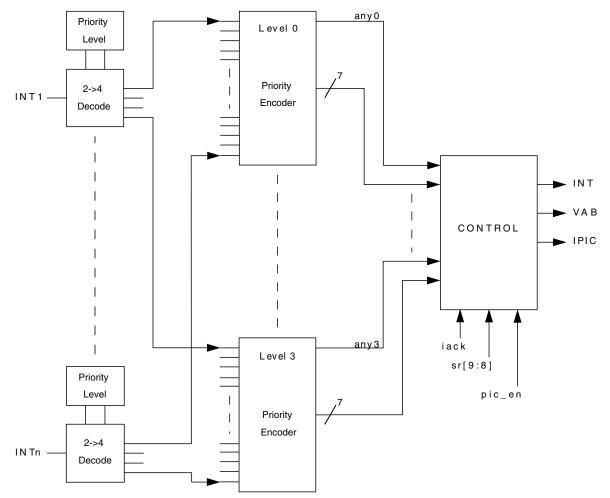

|      | 14.1.4         | Block Diagram                                              | 484 |

| 14.2 | Memory         | Map and Registers                                          | 485 |

|      | 14.2.1         | Interrupt Priority Register 0 (INTCIPR0)                   | 487 |

|      | 14.2.2         | Interrupt Priority Register 1 (INTCIPR1)                   | 489 |

|      | 14.2.3         | Interrupt Priority Register 2 (INTCIPR2)                   | 491 |

|      | 14.2.4         | Interrupt Priority Register 3 (INTCIPR3)                   | 492 |

|      | 14.2.5         | Interrupt Priority Register 4 (INTCIPR4)                   | 494 |

|      | 14.2.6         | Interrupt Priority Register 5 (INTCIPR5)                   | 496 |

|      | 14.2.7         | Interrupt Priority Register 6 (INTCIPR6)                   | 498 |

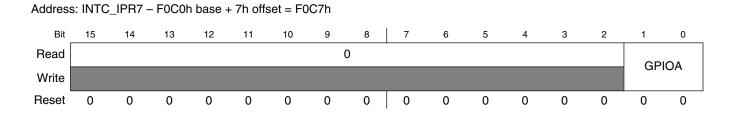

|      | 14.2.8         | Interrupt Priority Register 7 (INTCIPR7)                   | 499 |

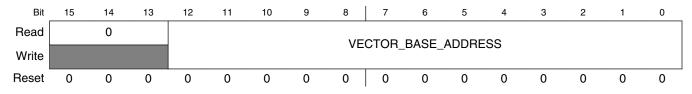

|      | 14.2.9         | Vector Base Address Register (INTCVBA)                     | 500 |

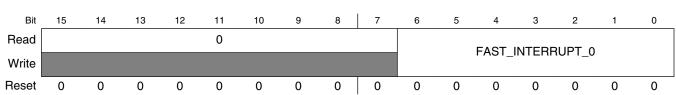

|      | 14.2.10        | Fast Interrupt 0 Match Register (INTCFIM0)                 | 501 |

|      | 14.2.11        | Fast Interrupt 0 Vector Address Low Register (INTCFIVAL0)  | 501 |

|      | 14.2.12        | Fast Interrupt 0 Vector Address High Register (INTCFIVAH0) | 502 |

|      | 14.2.13        | Fast Interrupt 1 Match Register (INTCFIM1)                 | 502 |

|      | 14.2.14        | Fast Interrupt 1 Vector Address Low Register (INTCFIVAL1)  | 503 |

|      | 14.2.15        | Fast Interrupt 1 Vector Address High Register (INTCFIVAH1) | 503 |

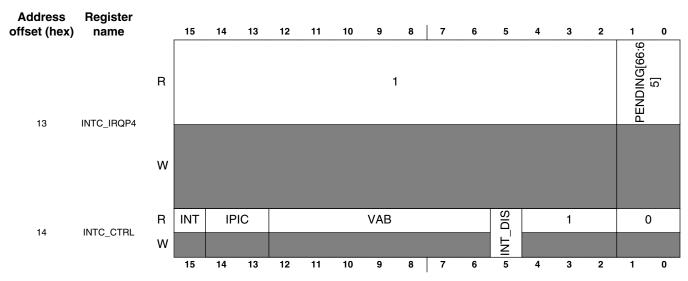

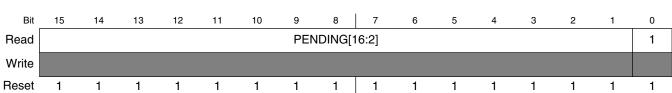

|      | 14.2.16        | IRQ Pending Register 0 (INTCIRQP0)                         | 504 |

|      | 14.2.17        | IRQ Pending Register 1 (INTCIRQP1)                         | 504 |

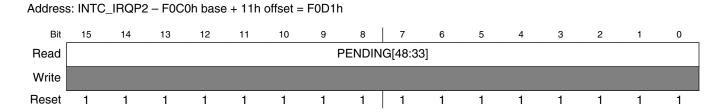

|      | 14.2.18        | IRQ Pending Register 2 (INTCIRQP2)                         | 505 |

|      | 14.2.19        | IRQ Pending Register 3 (INTCIRQP3)                         | 505 |

|      | 14.2.20        | IRQ Pending Register 4 (INTCIRQP4)                         | 506 |

|      | 14.2.21        | Control Register (INTCCTRL)                                | 506 |

| 14.3 | Function | nal Description           | 507 |

|------|----------|---------------------------|-----|

|      |          | Normal Interrupt Handling |     |

|      | 14.3.2   | Interrupt Nesting         | 508 |

|      | 14.3.3   | Fast Interrupt Handling   | 508 |

| 14.4 | Resets   |                           | 509 |

|      | 14.4.1   | INTC after Reset          | 509 |

#### Chapter 15 On-Chip Clock Synthesis (OCCS)

| 15.1 | Introduction                 |                                                   |     |  |  |

|------|------------------------------|---------------------------------------------------|-----|--|--|

|      | 15.1.1                       | Overview                                          | 511 |  |  |

|      | 15.1.2                       | Features                                          | 511 |  |  |

| 15.2 | 15.2 Modes of Operation      |                                                   |     |  |  |

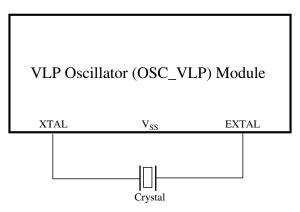

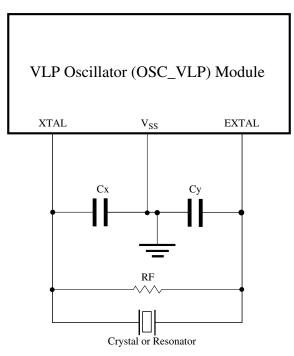

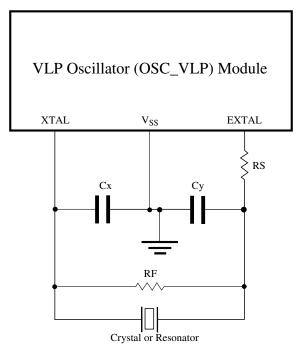

|      | 15.2.1                       | Internal Clock Source                             | 513 |  |  |

|      | 15.2.2                       | Crystal (or Ceramic Resonator) Oscillator         | 513 |  |  |

|      | 15.2.3                       | External Clock Source - Clock In (CLKIN)          | 515 |  |  |

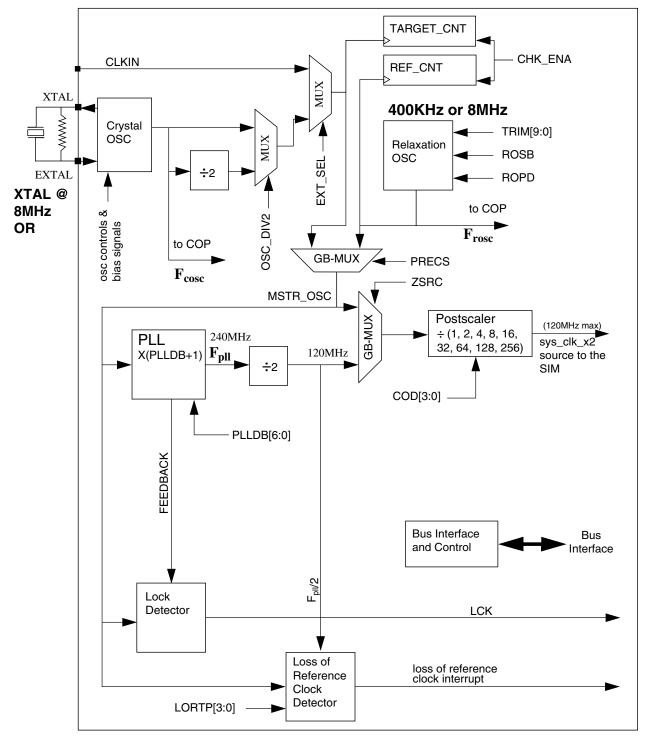

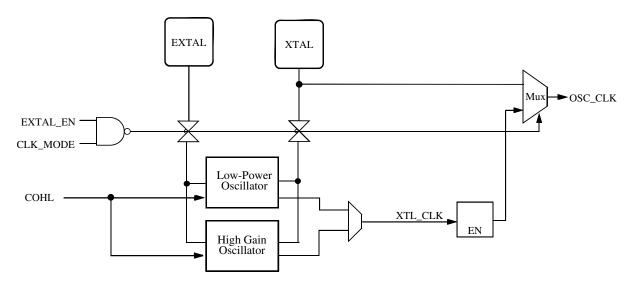

| 15.3 | Block D                      | Diagram                                           | 516 |  |  |

| 15.4 | Pin Des                      | Pin Descriptions                                  |     |  |  |

|      | 15.4.1                       | External Reference                                | 517 |  |  |

|      | 15.4.2                       | Oscillator Inputs (XTAL, EXTAL)                   | 517 |  |  |

|      | 15.4.3                       | CLKO                                              | 517 |  |  |

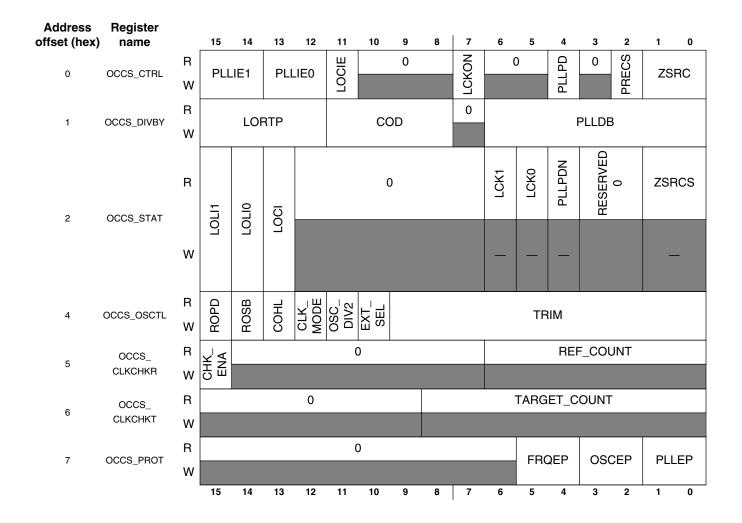

| 15.5 | 5.5 Memory Map and Registers |                                                   |     |  |  |

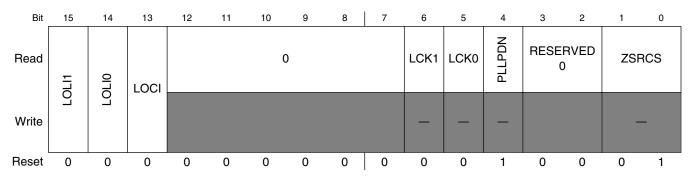

|      | 15.5.1                       | OCCS PLL Control Register (OCCSCTRL)              | 518 |  |  |

|      | 15.5.2                       | OCCS PLL Divide-By Register (OCCSDIVBY)           | 520 |  |  |

|      | 15.5.3                       | OCCS PLL Status Register (OCCSSTAT)               | 521 |  |  |

|      | 15.5.4                       | OCCS Oscillator Control Register (OCCSOSCTL)      | 522 |  |  |

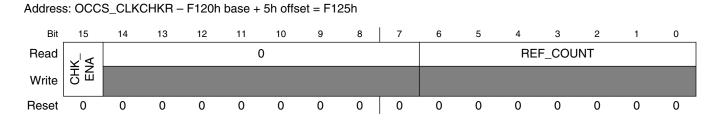

|      | 15.5.5                       | OCCS External Clock Check Reference (OCCSCLKCHKR) | 524 |  |  |

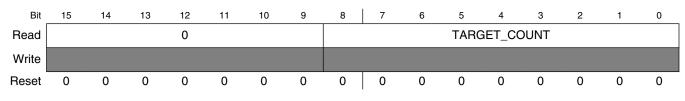

|      | 15.5.6                       | OCCS External Clock Check Target (OCCSCLKCHKT)    | 525 |  |  |

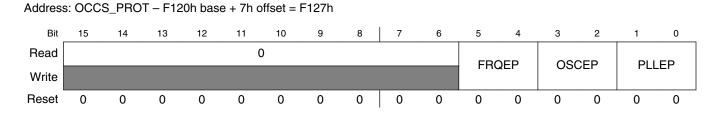

|      | 15.5.7                       | OCCS Protection Register (OCCSPROT)               | 525 |  |  |

| 15.6 | Functional Description       |                                                   |     |  |  |

#### MC56F825x/4x Reference Manual, Rev. 2, 10/2010

24

**Section Number**

| 15.7 | External Reference |                                    |     |  |

|------|--------------------|------------------------------------|-----|--|

| 15.8 | Crystal Oscillator |                                    |     |  |

|      | 15.8.1             | Switching Clock Sources            | 531 |  |

| 15.9 | Phase Lo           | ocked Loop                         | 532 |  |

|      | 15.9.1             | PLL Recommended Range of Operation | 532 |  |

|      | 15.9.2             | PLL Frequency Lock Detector Block  | 533 |  |

|      | 15.9.3             | Loss of Reference Clock Detector   | 533 |  |

|      | 15.9.4             | Resets                             | 534 |  |

|      | 15.9.5             | Clocks                             | 534 |  |

|      |                    |                                    |     |  |

#### Chapter 16 System Integration Module (SIM)

| 16.1 Introduction |         |                                              | 535 |

|-------------------|---------|----------------------------------------------|-----|

|                   | 16.1.1  | Overview                                     | 535 |

|                   | 16.1.2  | Features                                     | 535 |

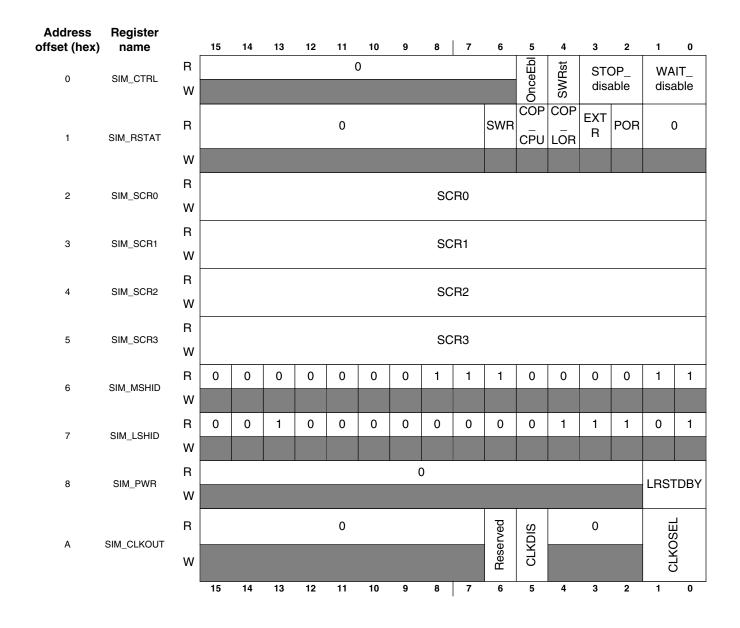

| 16.2              | Memory  | Map and Registers                            | 537 |

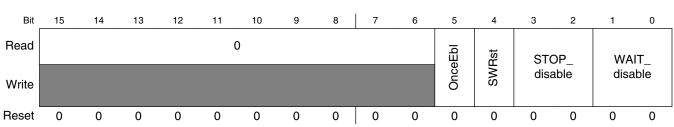

|                   | 16.2.1  | Control Register (SIMCTRL)                   | 539 |

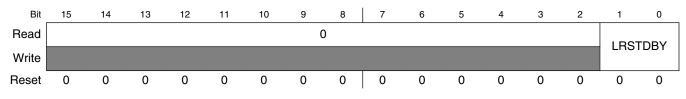

|                   | 16.2.2  | Reset Status Register (SIMRSTAT)             | 540 |

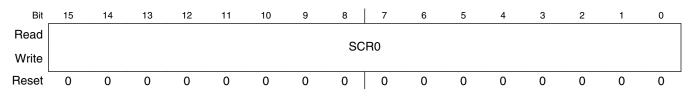

|                   | 16.2.3  | Software Control Register (SIMSCR0)          | 541 |

|                   | 16.2.4  | Software Control Register (SIMSCR1)          | 541 |

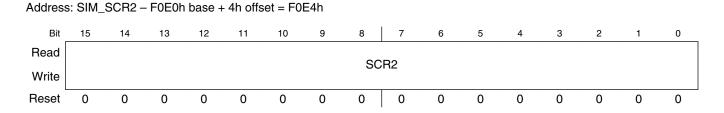

|                   | 16.2.5  | Software Control Register (SIMSCR2)          | 542 |

|                   | 16.2.6  | Software Control Register (SIMSCR3)          | 542 |

|                   | 16.2.7  | Most Significant Half of JTAG ID (SIMMSHID)  | 542 |

|                   | 16.2.8  | Least Significant Half of JTAG ID (SIMLSHID) | 544 |

|                   | 16.2.9  | Power Control Register (SIMPWR)              | 545 |

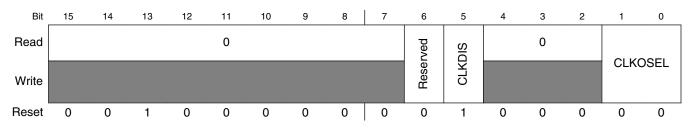

|                   | 16.2.10 | Clock Output Select Register (SIMCLKOUT)     | 545 |

|                   | 16.2.11 | Peripheral Clock Rate Register (SIMPCR)      | 547 |

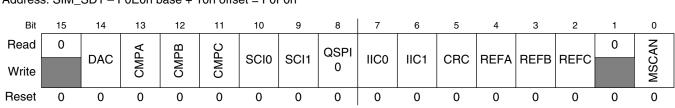

|                   | 16.2.12 | Peripheral Clock Enable Register 0 (SIMPCE0) | 548 |

|                   | 16.2.13 | Peripheral Clock Enable Register 1 (SIMPCE1) | 549 |

|                   | 16.2.14 | Peripheral Clock Enable Register 2 (SIMPCE2) | 550 |

#### MC56F825x/4x Reference Manual, Rev. 2, 10/2010

**Section Number**

|      | 16.2.15    | STOP Disable Register 0 (SIMSD0)                  | 551 |  |

|------|------------|---------------------------------------------------|-----|--|

|      | 16.2.16    | Peripheral Clock STOP Disable Register 1 (SIMSD1) | 552 |  |

|      | 16.2.17    | Peripheral Clock STOP Disable Register 2 (SIMSD2) | 554 |  |

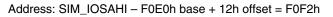

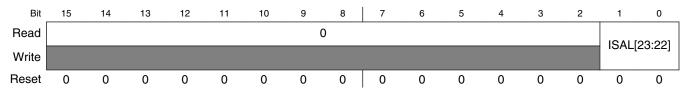

|      | 16.2.18    | I/O Short Address Location Register (SIMIOSAHI)   | 554 |  |

|      | 16.2.19    | I/O Short Address Location Register (SIMIOSALO)   | 555 |  |

|      | 16.2.20    | Protection Register (SIMPROT)                     | 556 |  |

|      | 16.2.21    | GPIO Peripheral Select Register 0 (SIMGPS0)       | 557 |  |

|      | 16.2.22    | GPIO Peripheral Select Register 1 (SIMGPS1)       | 558 |  |

|      | 16.2.23    | GPIO Peripheral Select Register 2 (SIMGPS2)       | 560 |  |

|      | 16.2.24    | GPIO Peripheral Select Register 3 (SIMGPS3)       | 561 |  |

| 16.3 | Function   | nal Description                                   | 563 |  |

|      | 16.3.1     | Clock Generation Overview                         | 563 |  |

|      | 16.3.2     | Power Down Modes Overview                         | 563 |  |

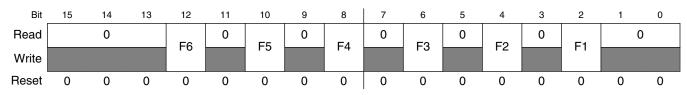

|      | 16.3.3     | Stop and Wait Mode Disable Function               | 565 |  |

| 16.4 | Resets     |                                                   | 565 |  |

| 16.5 | Interrupts |                                                   |     |  |

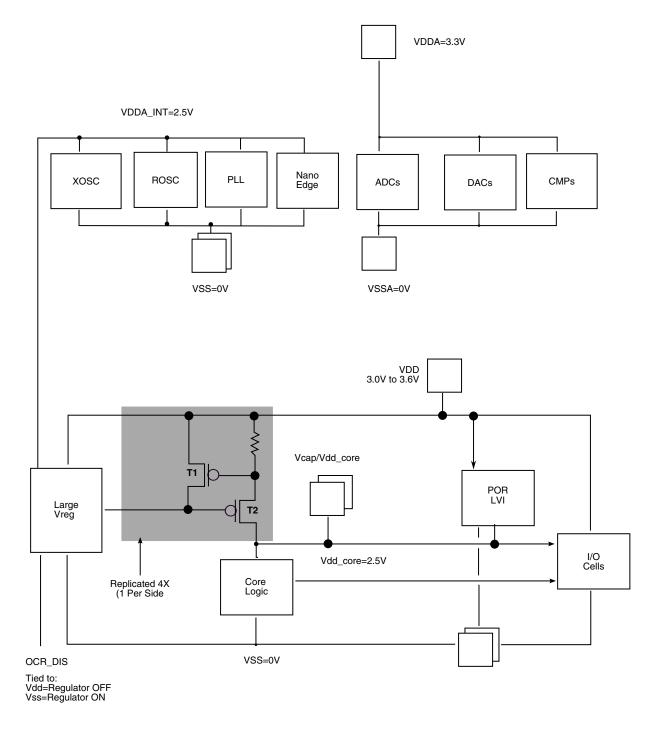

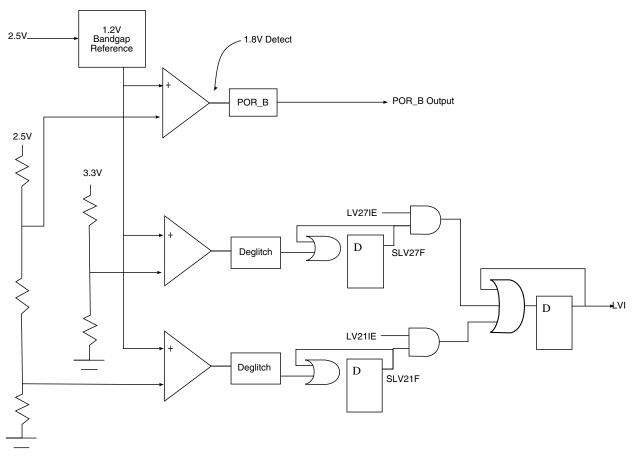

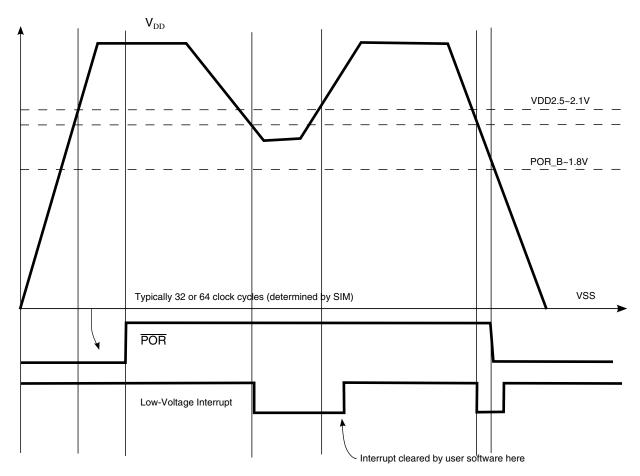

#### Chapter 17 Power Supervisor (PS)

| 17.1 | Introduction    |                                            |     |  |

|------|-----------------|--------------------------------------------|-----|--|

|      | 17.1.1 Overview |                                            |     |  |

|      | 17.1.2          | Features                                   | 569 |  |

|      | 17.1.3          | Modes of Operation                         | 570 |  |

|      | 17.1.4          | Block Diagram                              | 572 |  |

| 17.2 | Function        | nal Description                            | 573 |  |

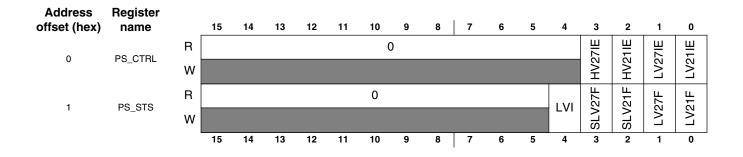

| 17.3 | Memory          | v Map and Registers                        | 574 |  |

|      | 17.3.1          | Power Supervisor Control Register (PSCTRL) | 574 |  |

|      | 17.3.2          | Power Supervisor Status Register (PSSTS)   | 575 |  |

| 17.4 | Resets          |                                            | 576 |  |

| 17.5 | Clocks          |                                            | 576 |  |

#### MC56F825x/4x Reference Manual, Rev. 2, 10/2010

Downloaded from Elcodis.com electronic components distributor

**Section Number**

| Sec  | tion N   | umber Title                                     | Page |  |  |

|------|----------|-------------------------------------------------|------|--|--|

| 17.6 | Interrup | .S                                              |      |  |  |

|      |          | Chapter 18<br>Computer Operating Properly (COP) |      |  |  |

| 18.1 | Introduc | tion                                            |      |  |  |

|      | 18.1.1   | Features                                        |      |  |  |

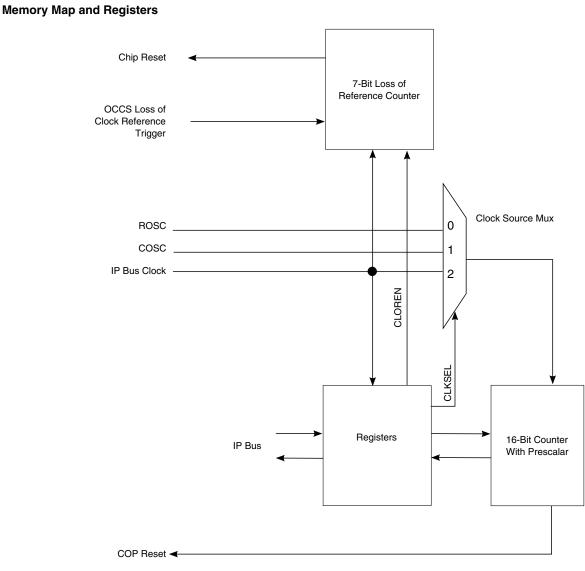

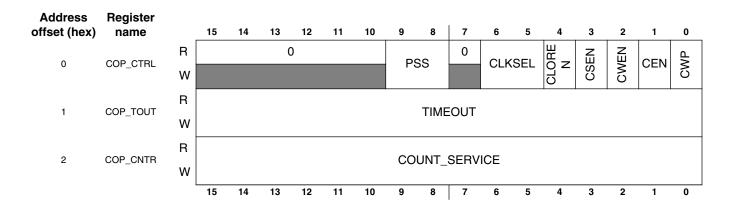

|      | 18.1.2   | Block Diagram                                   |      |  |  |

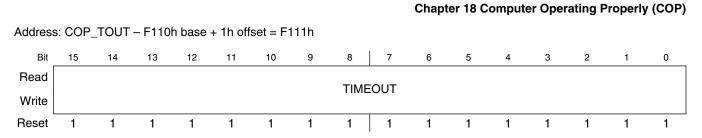

| 18.2 | Memory   | Map and Registers                               |      |  |  |

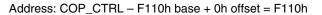

|      | 18.2.1   | COP Control Register (COPCTRL)                  |      |  |  |

|      | 18.2.2   | COP Timeout Register (COPTOUT)                  |      |  |  |

|      | 18.2.3   | COP Counter Register (COPCNTR)                  |      |  |  |

| 18.3 | Function | al Description                                  |      |  |  |

|      | 18.3.1   | COP after Reset                                 |      |  |  |

|      | 18.3.2   | Wait Mode Operation                             |      |  |  |

|      | 18.3.3   | Stop Mode Operation                             |      |  |  |

|      | 18.3.4   | Debug Mode Operation                            |      |  |  |

|      | 18.3.5   | Loss of Reference Operation                     |      |  |  |

| 18.4 | Resets   |                                                 |      |  |  |

| 18.5 | Clocks   |                                                 |      |  |  |

| 18.6 | Interrup | S                                               |      |  |  |

|      |          | Chapter 19                                      |      |  |  |

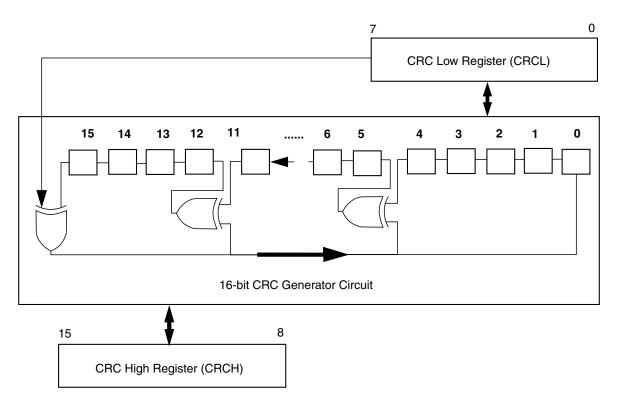

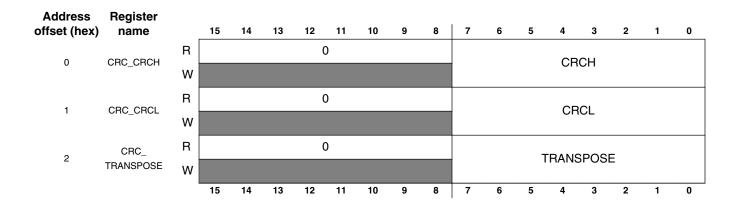

# Cyclic Redundancy Check Generator (CRC)

| 19.1 | 1 Introduction |                             |     |

|------|----------------|-----------------------------|-----|

|      | 19.1.1         | Features                    | 587 |

|      | 19.1.2         | Modes of Operation          | 587 |

|      | 19.1.3         | Block Diagram               | 588 |

| 19.2 | External       | Signal Description          | 588 |

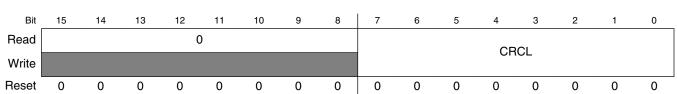

| 19.3 | Memory         | Map and Registers           | 589 |

|      | 19.3.1         | CRC High Register (CRCCRCH) | 589 |

|      | 19.3.2         | CRC Low Register (CRCCRCL)  | 590 |

#### MC56F825x/4x Reference Manual, Rev. 2, 10/2010

**Preliminary**

# 19.3.3CRC Transpose Register (CRCTRANSPOSE)59019.4Functional Description59119.4.1ITU-T (CCITT) Recommendations and Expected CRC Results59119.4.2Transpose feature59219.5Initialization Information593

Title

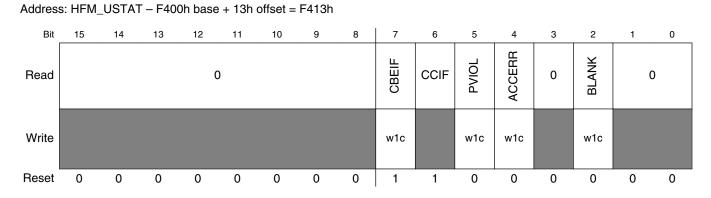

#### Chapter 20 Flash Memory (HFM)

| 20.1 | 1 Overview |                                          |     |

|------|------------|------------------------------------------|-----|

|      | 20.1.1     | Features                                 | 595 |

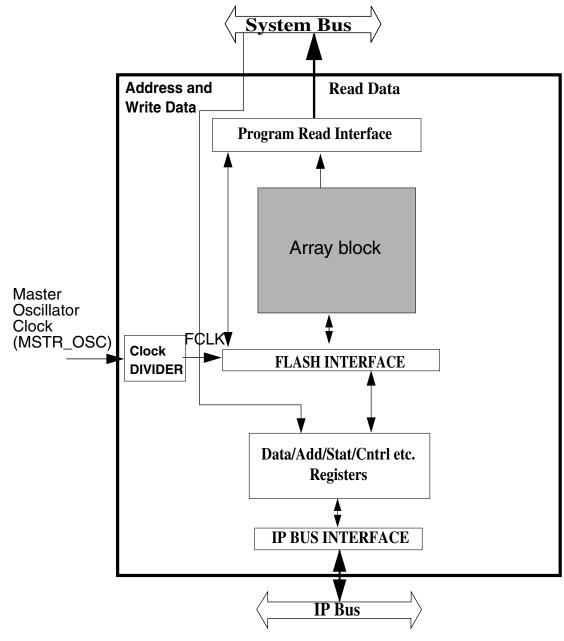

|      | 20.1.2     | Block Diagram                            | 596 |

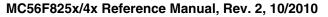

|      | 20.1.3     | Memory Array Organization                | 597 |

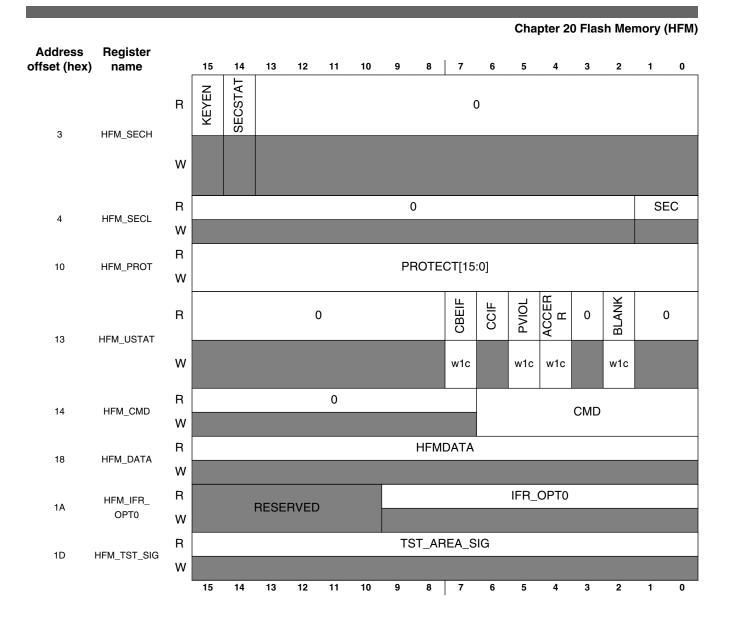

| 20.2 | Memory     | Map and Registers                        | 598 |

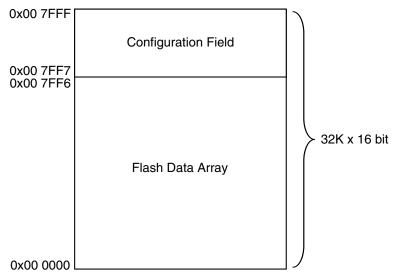

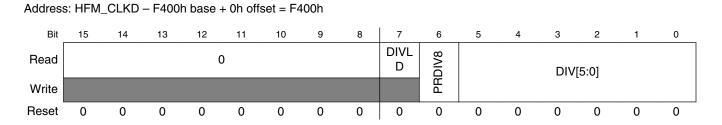

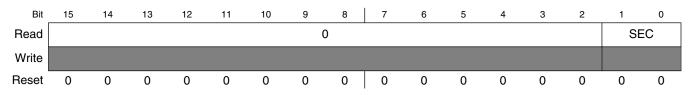

|      | 20.2.1     | HFM Clock Divider Register (HFMCLKD)     | 599 |

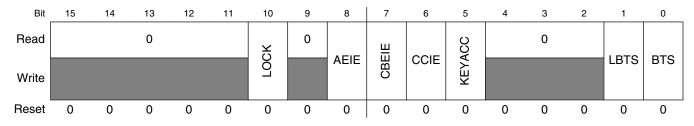

|      | 20.2.2     | HFM Configuration Register (HFMCR)       | 600 |

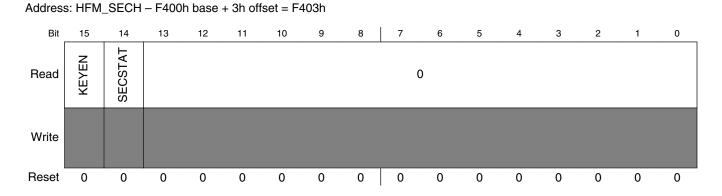

|      | 20.2.3     | HFM Security Register High (HFMSECH)     | 602 |

|      | 20.2.4     | HFM Security Register Low (HFMSECL)      | 603 |

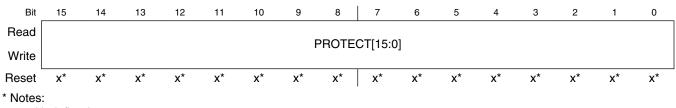

|      | 20.2.5     | HFM Protection Register (HFMPROT)        | 604 |

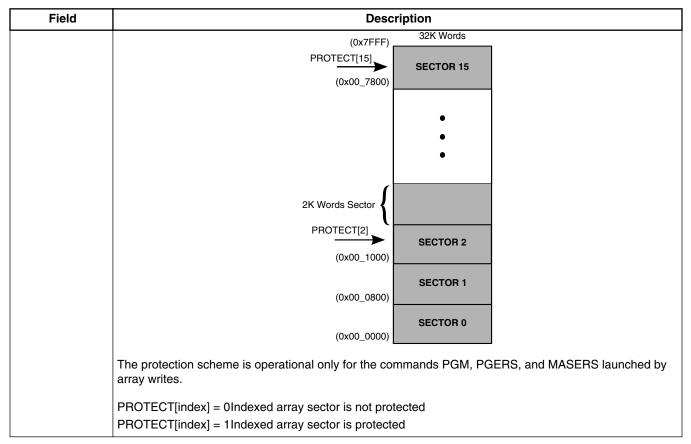

|      | 20.2.6     | HFM User Status Register (HFMUSTAT)      | 605 |

|      | 20.2.7     | HFM Command Register (HFMCMD)            | 607 |

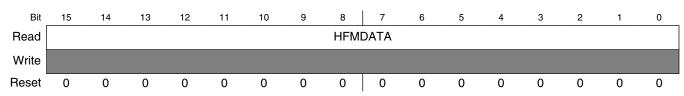

|      | 20.2.8     | HFM Data Register (HFMDATA)              | 608 |

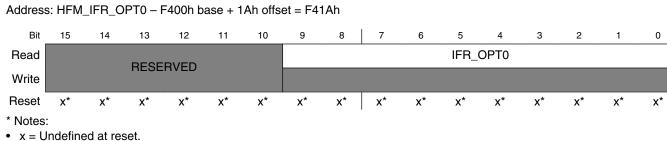

|      | 20.2.9     | HFM IFR Option Register 0 (HFMIFR_OPT0)  | 608 |

|      | 20.2.10    | HFM Test Array Signature (HFMTST_SIG)    | 609 |

| 20.3 | Function   | nal Description                          | 609 |

|      | 20.3.1     | Read Operation                           | 610 |

|      | 20.3.2     | Write Operation                          | 610 |

|      | 20.3.3     | Erase Operation                          | 610 |

|      | 20.3.4     | Flash Commands                           | 611 |

|      | 20.3.5     | Set the Flash Program/Erase Clock (FCLK) | 612 |

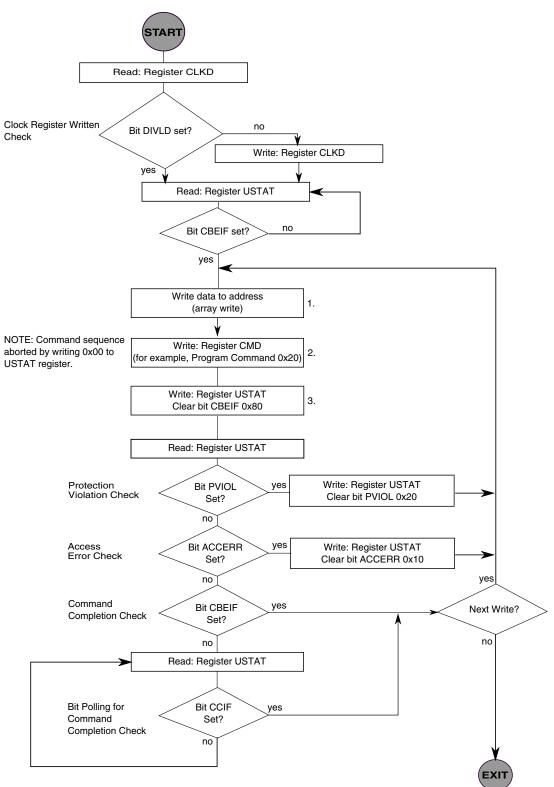

|      | 20.3.6     | Command Sequence                         | 613 |

#### MC56F825x/4x Reference Manual, Rev. 2, 10/2010

28

**Section Number**

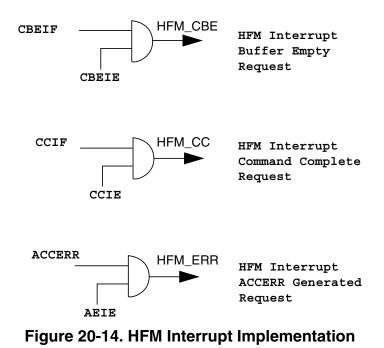

#### 20.3.7 20.3.8 20.3.9 20.5.1 20.5.2

Title

#### Chapter 21 Joint Test Action Group (JTAG) Port

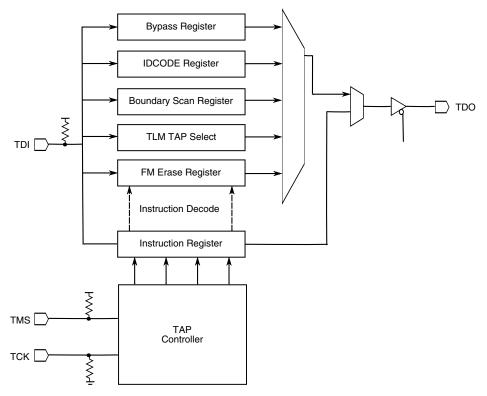

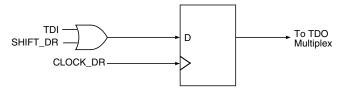

| 21.1 | Introduc | Introduction |                             |     |  |  |

|------|----------|--------------|-----------------------------|-----|--|--|

|      | 21.1.1   | Features     |                             | 621 |  |  |

|      | 21.1.2   | Block Dia    | gram                        | 621 |  |  |

| 21.2 | External | l Signal De  | scription                   | 622 |  |  |

| 21.3 | Memory   | / Map        |                             | 623 |  |  |

| 21.4 | Function | nal Descrip  | tion                        | 623 |  |  |

|      | 21.4.1   | JTAG Por     | TAG Port Architecture       |     |  |  |

|      | 21.4.2   | Master TA    | AP Instructions             | 623 |  |  |

|      |          | 21.4.2.1     | Bypass Instruction (BYPASS) | 624 |  |  |

|      |          | 21.4.2.2     | IDCODE                      | 624 |  |  |

|      |          | 21.4.2.3     | TLM_SEL                     | 624 |  |  |

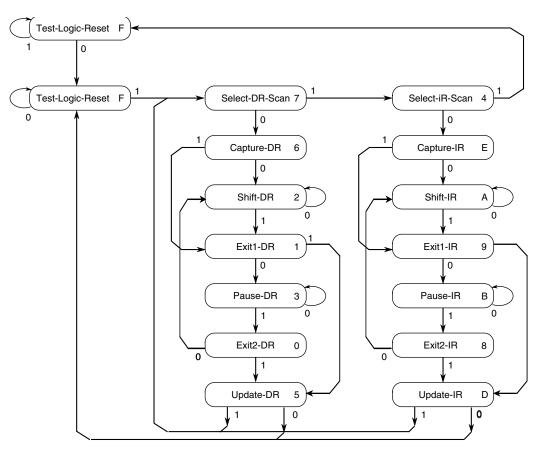

|      |          | 21.4.2.4     | TAP Controller              | 625 |  |  |

| 21.5 | Clocks   |              |                             | 627 |  |  |

| 21.6 | Interrup | ts           |                             | 628 |  |  |

MC56F825x/4x Reference Manual, Rev. 2, 10/2010

Downloaded from Elcodis.com electronic components distributor

Section Number

Preliminary

# Chapter 1 Device Overview

# 1.1 Introduction

The MC56F825x/MC56F824x is a member of the 56800E core-based family of Digital Signal Controllers (DSCs). It combines, on a single chip, the processing power of a DSP and the functionality of a microcontroller with a flexible set of peripherals to create a cost-effective solution. Because of its low cost, configuration flexibility, and compact program code, the MC56F825x/MC56F824x is well-suited for many consumer and industrial applications.

The 56800E core is based on a dual Harvard-style architecture consisting of three execution units operating in parallel, allowing as many as six operations per instruction cycle. The MCU-style programming model and optimized instruction set allow straightforward generation of efficient, compact DSP and control code. The instruction set is also highly efficient for C compilers to enable rapid development of optimized control applications.

# 1.2 Features

The MC56F825x/MC56F824x includes many peripherals that are especially useful for industrial control, motion control, home appliances, general purpose inverters, smart sensors, fire and security systems, switched-mode power supply, power management, and medical monitoring applications.

The MC56F825x/MC56F824x Digital Signal Controller includes up to 64 KB of program flash and up to 8 KB of unified data/program RAM. The page size of on-chip flash is 1024 words. It can be independently bulk erased or erased in pages.

A comprehensive set of programmable peripherals—including a PWM, dual high-speed ADCs, queued SCIs, a queued SPI, I2Cs, an MSCAN, an inter-module Crossbar Switch, Quad Timers, a CRC block, DACs, analog comparators, and on-chip and off-chip clock

#### Features

sources—supports various applications. Each peripheral can be independently shut down to save the power. Any pin in these peripherals can also be used as General Purpose Input/Outputs (GPIOs).

Feature highlights follow:

- Highly efficient hybrid DSP core

- 60 MHz operation frequency

- Efficient 56800E Digital Signal Processor (DSP) engine with dual Harvard architecture

- Three internal address buses

- Four internal data buses

- 155 basic instructions in conjunction with up to 20 address modes

- 32-bit internal primary data buses supporting 8-bit, 16-bit, and 32-bit data movement, addition, subtraction, and logical operation

- Single-cycle 16 x 16-bit parallel Multiplier-Accumulator (MAC)

- Four 36-bit accumulators, including extension bits

- 32-bit arithmetic and logic multi-bit shifter

- Parallel instruction set with unique DSP addressing modes

- Hardware DO and REP loops

- Instruction set that supports both DSP and controller functions

- Controller-style addressing modes and instructions for compact code

- Efficient C compiler and local variable support

- Software subroutine and interrupt stack with depth limited only by memory

- JTAG/Enhanced On-Chip Emulation (EOnCE) for unobtrusive, processor-speedindependent, real-time debugging

- On-chip memory

- Dual Harvard architecture that permits as many as three simultaneous accesses to program and data memory

- Data RAM that supports byte, word, and double-word address modes

- EEPROM emulation capability using flash

- Flash security and protection that prevent unauthorized users from gaining access to the internal flash

- System and power management

- Dual clock sources

- External crystal, resonator, external clock source

- Internal 8 MHz/400 kHz relaxation oscillator

- On-Chip Clock Synthesis (OCCS) module

- On-chip Power Reset and Brown-Out Reset

- On-chip low voltage detection

- Computer Operating Properly (COP) watchdog timer with multi-clock source selection

- Wait and stop modes with fast wakeup

- Single supply

- Interrupt Controller (INTC)

- Five interrupt priority levels

- One non-maskable interrupt for core-related interrupts

- Three user-programmable priority levels for each interrupt source: levels 0, 1, and 2

- Lowest-priority software interrupt: LP

- Support for hardware nested interrupts

- Support for two programmable fast interrupts that can be assigned to any interrupt source

- Peripherals

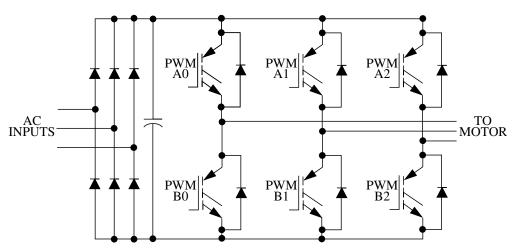

- One Enhanced Flex Pulse Width Modulator (eFlexPWM)

- 6-channel with WanoEdge<sup>TM</sup> placement; 520 ps PWM resolution

- 3-channel with enhanced capture functionality

- Two Quad Timers with a total of eight 16-bit timers and up to 120 MHz operation clock

- Two 12-bit ADCs with up to 16 channels

- One 12-bit DAC

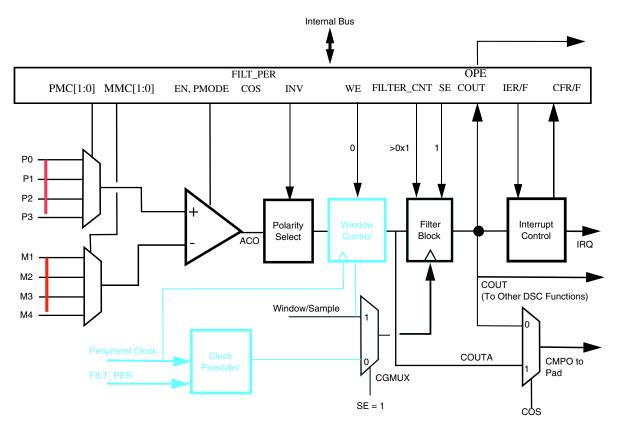

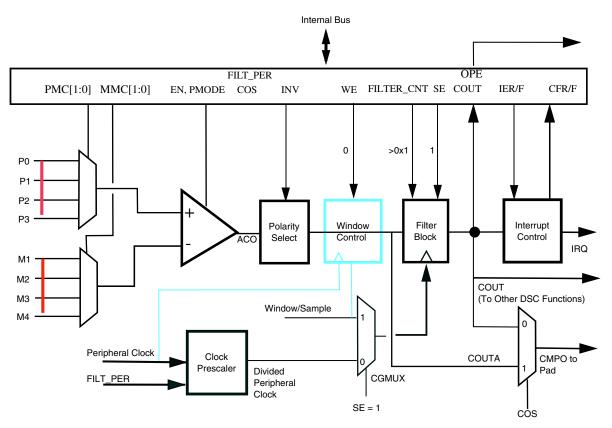

- Three analog High Speed Comparators (HSCMPs) with integrated digital output filtering and windowing features

- Three 5-bit reference DACs (32-tap voltage reference) for HSCMPs

- One Queued Serial Peripheral Interface (QSPI) module with 4-word FIFO

- Two high speed Queued Serial Communication Interface (QSCI) modules with 4-byte FIFO and up to 120 MHz operation clock

- Two Inter-Integrated Circuit (I2C) ports with SMBus support

- One Scalable Controller Area Network (MSCAN) module

- Cyclic Redundancy Check (CRC) Generator

- Inter-module Crossbar Switch (XBAR) that provides the programmable internal module connections between and among the PWM, ADCs, Quad Timers, 12-bit DAC, HSCMPs, and package pins

- Up to 54 general purpose I/O (GPIO)

- 5 V tolerance

- Configurable push-pull and open-drain output

- Ability to generate interrupt with programmable rising or falling edge and software interrupt

- Configurable drive strength: 4 mA/8 mA

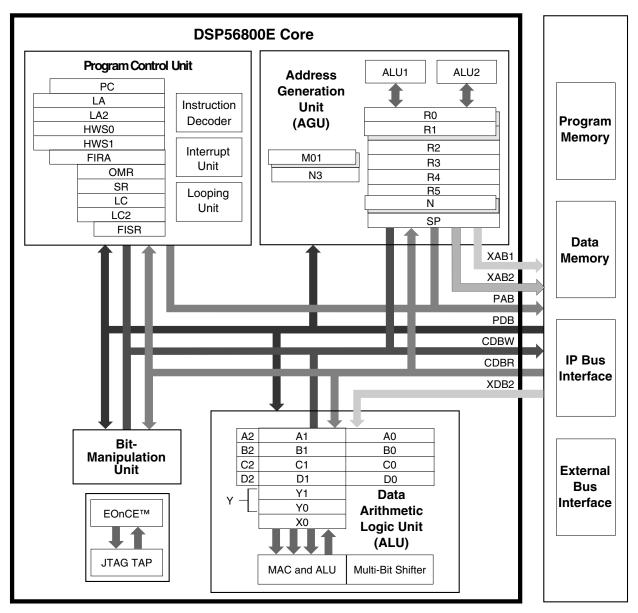

## 1.3 Core Block Diagram

The DSC core is composed of several independent functional units. The program controller, address generation unit (AGU) and data arithmetic logic unit (ALU) contain their own register sets and control logic, allowing them to operate independently and in parallel, increasing throughput. There is also an independent bit manipulation unit, which provides for efficient bit-manipulation operations. Each functional unit interfaces with the other units, memory, and the memory-mapped peripherals over the core's internal address and data buses, and through the IP bus bridge (off core).

MC56F825x/4x Reference Manual, Rev. 2, 10/2010

Downloaded from Elcodis.com electronic components distributor

Figure 1-1. DSP56800E Core Block Diagram

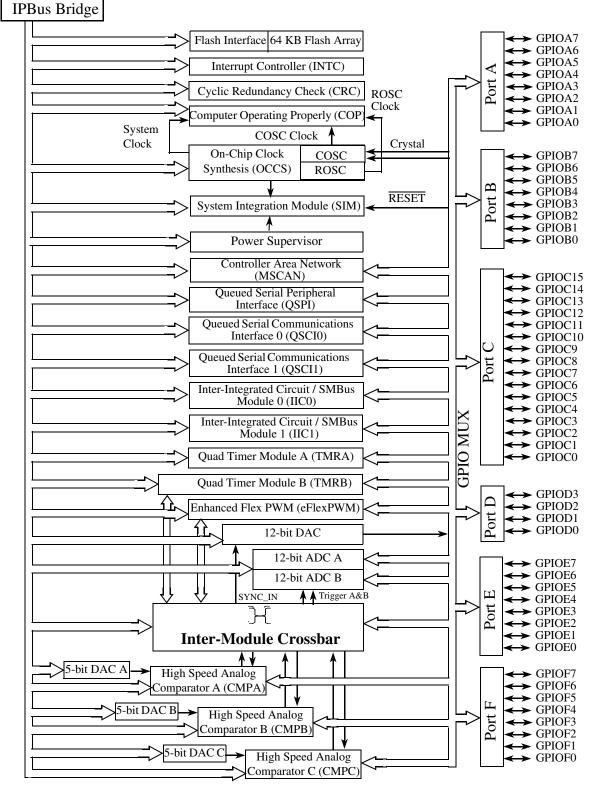

# 1.4 Peripheral Subsystem

All functional pins on this device are multiplexed with one of the GPIO ports. To use one of the pins as a peripheral pin, enable the peripheral function by programming the corresponding bit in the GPIO port's peripheral enable register. If a pin is multiplexed with different peripheral functions, control the selection of the peripheral function by using one of the GPIO peripheral select registers in the System Integration Module (SIM).

Figure 1-2. Peripheral Subsystem

Downloaded from Elcodis.com electronic components distributor

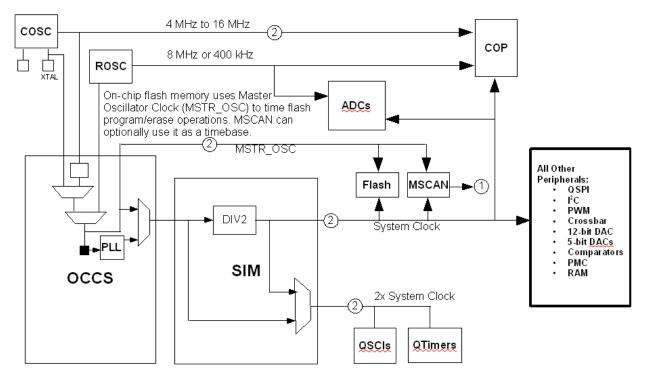

## **1.5 Clock Generation and Distribution**

The MC56F825x/MC56F824x's CPU and most peripherals can be run at clock rates up to (and including) 60 MHz. Additionally, the Serial Communication Interface (SCI) modules and quad timers can optionally be run at 120 MHz.

The device is equipped with an internal relaxation oscillator, with modes for 400 kHz and 8 MHz (default at reset). In addition, the crystal oscillator module supports external crystals and resonators ranging from 4 MHz to 16 MHz in operation.

### NOTE

A crystal or resonator is recommended when using the MSCAN module.

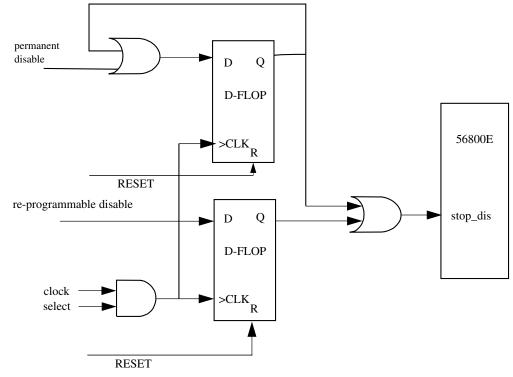

The following diagram presents the system clock distribution. Additional clock information appears in descriptions of the On-Chip Clock Synthesis module (OCCS) and System Integration Module (SIM).

Figure 1-3. System Clock Distribution

When the external clock is chosen as the master clock source, its frequency should not exceed 60 MHz for the following cases:

- 1. The operation being performed is a flash programming/erase operation.

- 2. The CLKSRC bit of the MSCAN CANCTL1 register is set to 0.

#### MC56F825x/4x Reference Manual, Rev. 2, 10/2010

**Clock Generation and Distribution**

MC56F825x/4x Reference Manual, Rev. 2, 10/2010

# Chapter 2 Analog-to-Digital Converter (ADC)

## 2.1 Introduction

## 2.1.1 Overview

The analog-to-digital converter (ADC) is one dual 12-bit ADC in which each ADC converter has a separate voltage reference and control block.

## 2.1.2 Features

The analog-to-digital (ADC) converter function consists of two separate analog-to-digital converters, each with eight analog inputs and its own sample and hold circuit. A common digital control module configures and controls the functioning of the converters. ADC features include:

- 12-bit resolution

- Maximum ADC clock frequency of 15 MHz with 100 ns period

- Sampling rate up to 3.33 million samples per second<sup>1</sup>

- Single conversion time of 8.5 ADC clock cycles  $(8.5 \times 100 \text{ ns} = 850 \text{ ns})$

- Additional conversion time of 6 ADC clock cycles ( $6 \times 100 \text{ ns} = 600 \text{ ns}$ )

- Eight conversions in 26.5 ADC clock cycles ( $26.5 \times 100 \text{ ns} = 2.65 \mu s$ ) using parallel mode

- Can be synchronized to the PWM through the SYNC0/1 input signal if the integration permits the PWM to trigger a timer channel connected to that input

<sup>1.</sup> In loop mode, the time between each conversion is 6 ADC clock cycles (600 ns). Using simultaneous conversion, two samples can be obtained in 600 ns. Samples per second is calculated according to 600 ns per two samples or 3,333,333 samples per second.

#### Introduction

- Sequentially scans and stores up to sixteen measurements

- Scans and stores up to eight measurements each on two ADC converters operating simultaneously and in parallel

- Scans and stores up to eight measurements each on two ADC converters operating asynchronously to each other in parallel

- A scan can pause and await new SYNC input prior to continuing

- Gains the input signal by x1, x2, or x4

- Optional interrupts at end of scan if an out-of-range limit is exceeded or there is a zero crossing

- Optional sample correction by subtracting a pre-programmed offset value

- Signed or unsigned result

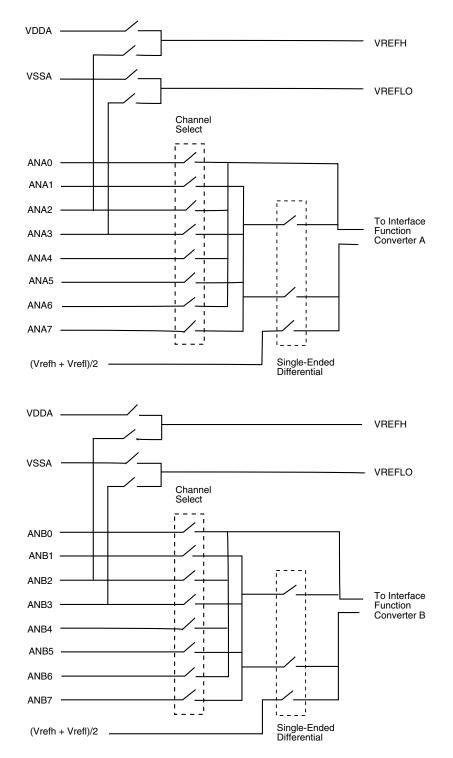

- Single-ended or differential inputs

- PWM outputs with hysteresis for three of the analog inputs

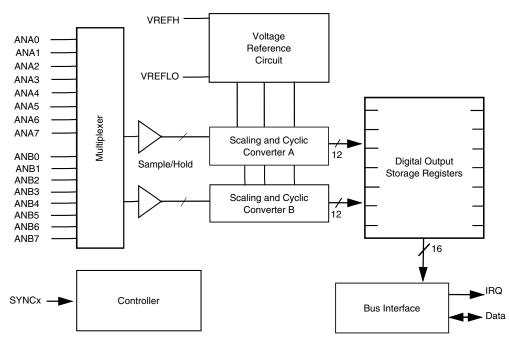

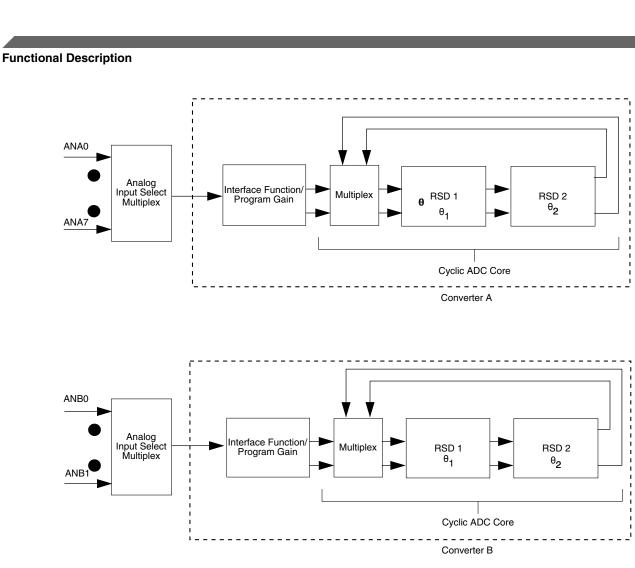

### 2.1.3 Block Diagram

The following figure illustrates the dual ADC configuration.

Figure 2-1. Dual ADC Block Diagram

## 2.2 Signal Descriptions

## 2.2.1 Overview

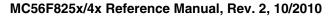

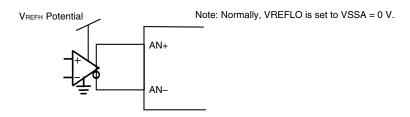

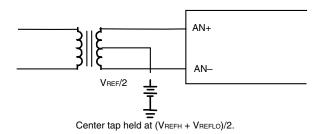

| Name      | I/О Туре | Function              | Reset State | Notes                            |

|-----------|----------|-----------------------|-------------|----------------------------------|

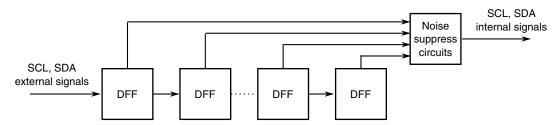

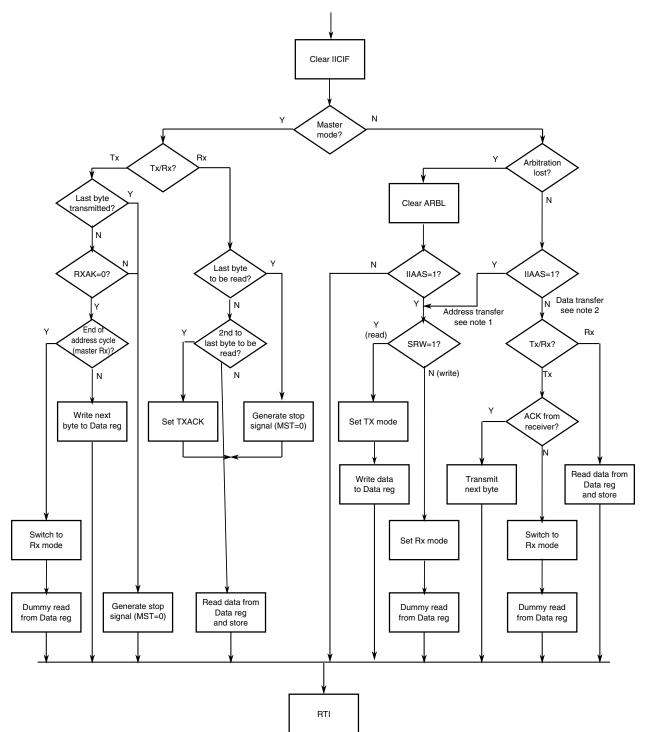

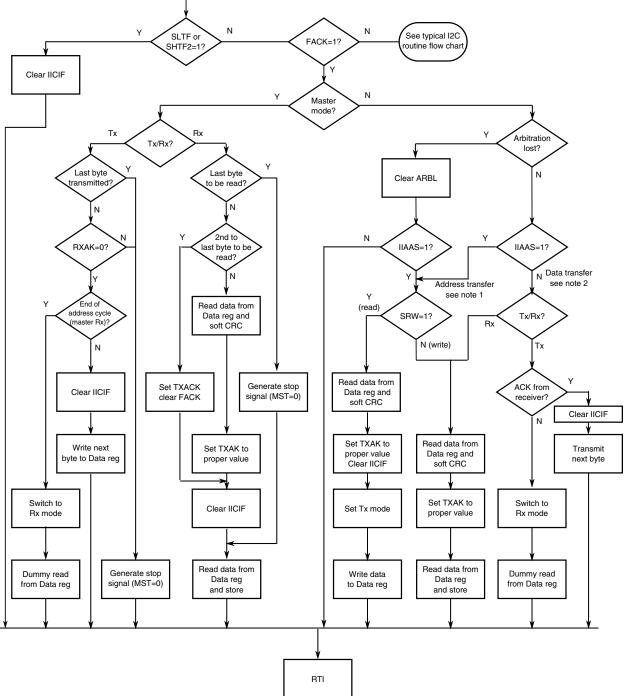

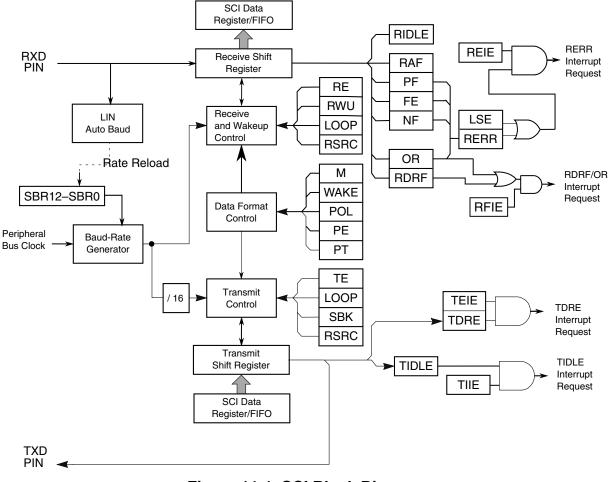

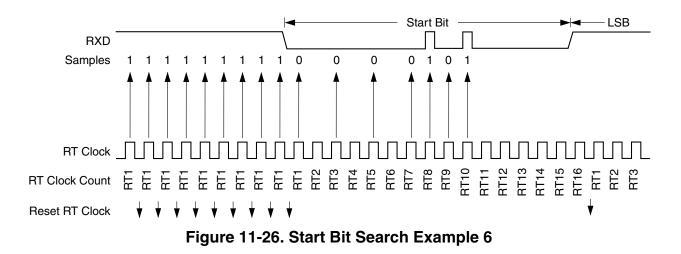

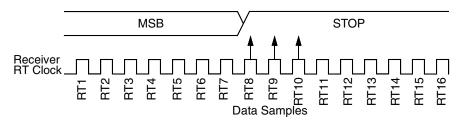

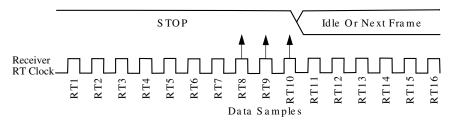

| ANA0–ANB7 | Input    | Analog Input Pins     | n/a         | —                                |