# SIPHYTM MULTI-RATE SONET/SDH CLOCK AND DATA RECOVERY IC

#### **Features**

Complete high-speed, low-power, CDR solution includes the following:

- Supports OC-48/12/3, STM-16/4/1, Gigabit Ethernet, and 2.7 Gbps FEC

- Low Power—270 mW (TYP OC-48)■

- Small footprint: 4 x 4 mm

- DSPLL<sup>TM</sup> eliminates external loop filter components

- 3.3 V tolerant control inputs

- Exceeds all SONET/SDH jitter specifications

- Jitter generation2.9 mUI<sub>rms</sub> (Typ)

- Device powerdown

- Loss-of-lock indicator

- Single 2.5 V Supply

## **Applications**

- SONET/SDH/ATM routers

- Add/drop multiplexers

- Digital cross connects

- Gigabit Ethernet interfaces

- SONET/SDH test equipment

- Optical transceiver modules

- SONET/SDH regenerators

- Board level serial links

## **Description**

The Si5020 is a fully-integrated low-power clock and data recovery (CDR) IC designed for high-speed serial communication systems. It extracts timing information and data from a serial input at OC-48/12/3, STM-16/4/1, or Gigabit Ethernet (GbE) rates. Support for 2.7 Gbps data streams is also provided for OC-48/STM-16 applications that employ forward error correction (FEC). DSPLL technology eliminates sensitive noise entry points, making the PLL less susceptible to board-level interaction and helping to ensure optimal jitter performance.

The Si5020 represents a new standard in low jitter, low power, and small size for high-speed CDRs. It operates from a single 2.5 V supply over the industrial temperature range (–40 to 85 °C).

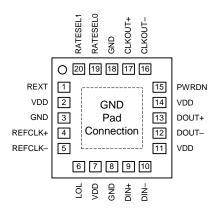

#### Pin Assignments Si5020 GND O 20 19 18 17 16 REXT 1 PWRDN 15 VDD 2 14 VDD **GND** 3 DOUT+ GND 13 Pad Connection REFCLK+ 4 12 DOUT-REFCLK-VDD 6 7 8 9 10 **Top View**

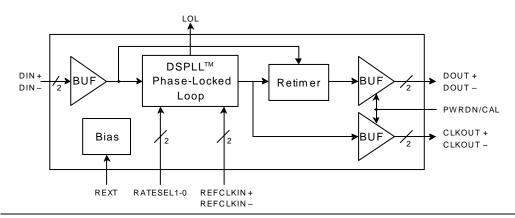

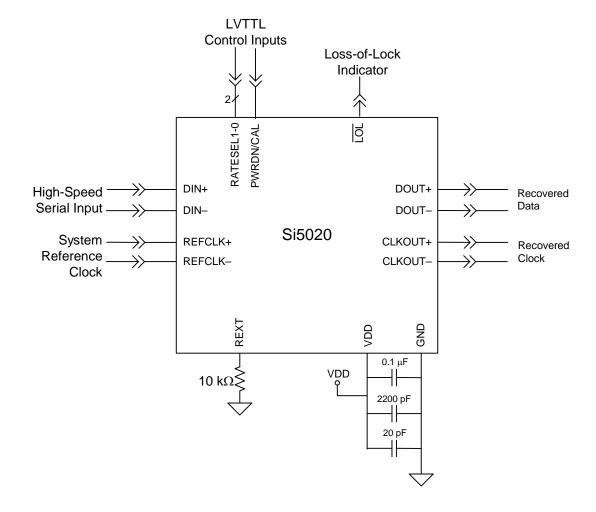

#### **Functional Block Diagram**

# TABLE OF CONTENTS

| <u>Section</u>                           | <u>Page</u> |

|------------------------------------------|-------------|

| 1. Detailed Block Diagram                |             |

| 2. Electrical Specifications             | 5           |

| 3. Typical Application Schematic         |             |

| 4. Functional Description                |             |

| 4.1. DSPLL <sup>®</sup>                  |             |

| 4.2. PLL Self-Calibration                |             |

| 4.3. Multi-Rate Operation                |             |

| 4.4. Reference Clock Detect              |             |

| 4.5. Lock Detect                         |             |

| 4.6. PLL Performance                     |             |

| 4.7. Powerdown                           |             |

| 4.8. Device Grounding                    |             |

| 4.9. Bias Generation Circuitry           |             |

| 4.10. Differential Input Circuitry       |             |

| 4.11. Differential Output Circuitry      |             |

| 5. Pin Descriptions: Si5010              |             |

| 6. Ordering Guide                        | 16          |

| 7. Top Mark                              |             |

| 8. Package Outline: Si5010-BM/GM         |             |

| 9. 4x4 mm 20L QFN Recommended PCB Layout |             |

| Document Change List                     |             |

| Contact Information                      |             |

# 1. Detailed Block Diagram

# 2. Electrical Specifications

**Table 1. Recommended Operating Conditions**

| Parameter                          | Symbol          | Test Condition | Min <sup>1</sup> | Тур | Max <sup>1</sup> | Unit |

|------------------------------------|-----------------|----------------|------------------|-----|------------------|------|

| Ambient Temperature                | T <sub>A</sub>  |                | -40              | 25  | 85               | °C   |

| Si5020 Supply Voltage <sup>2</sup> | V <sub>DD</sub> |                | 2.375            | 2.5 | 2.625            | V    |

#### Notes:

- 1. All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise stated.

- 2. The Si5020 specifications are guaranteed when using the recommended application circuit (including component tolerance) shown in "Typical Application Schematic" on page 10.

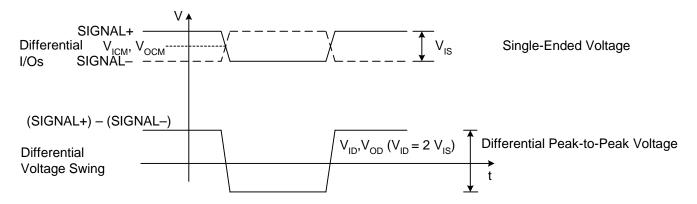

Figure 1. Differential Voltage Measurement (DIN, REFCLK, DOUT, CLKOUT)

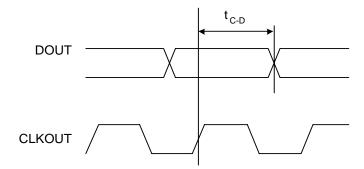

Figure 2. Differential Clock to Data Timing

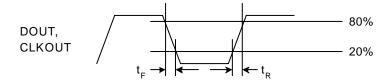

Figure 3. Differential DOUT and CLKOUT Rise/Fall Times

# Si5020

### **Table 2. DC Characteristics**

$(V_{DD} = 2.5 \text{ V } \pm 5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                            | Symbol             | Test Condition                | Min   | Тур                    | Max        | Unit             |

|------------------------------------------------------|--------------------|-------------------------------|-------|------------------------|------------|------------------|

| Supply Current                                       | I <sub>DD</sub>    |                               |       | 400                    | 100        | A                |

| OC-48 and FEC (2.7 GHz)<br>GbE                       |                    |                               | _     | 108<br>113             | 122<br>127 | mA               |

| OC-12                                                |                    |                               | _     | 117                    | 131        |                  |

| OC-3                                                 |                    |                               | _     | 124                    | 138        |                  |

| Power Dissipation                                    | P <sub>D</sub>     |                               |       |                        |            |                  |

| OC-48 and FEC (2.7 GHz)                              |                    |                               | _     | 270                    | 320        | mW               |

| GbE                                                  |                    |                               | _     | 283                    | 333        |                  |

| OC-12<br>OC-3                                        |                    |                               | _     | 293<br>310             | 344<br>362 |                  |

| Common Mode Input Voltage                            | \/                 | varios with \/                |       |                        | 302        | V                |

| (DIN, REFCLK)*                                       | V <sub>ICM</sub>   | varies with V <sub>DD</sub>   |       | .80 x V <sub>DD</sub>  |            | V                |

| Single-Ended Input Voltage (DIN, REFCLK)*            | V <sub>IS</sub>    | See Figure 1                  | 200   | _                      | 750        | $mV_{PP}$        |

| Differential Input Voltage Swing (DIN, REFCLK)*      | V <sub>ID</sub>    | See Figure 1                  | 200   | _                      | 1500       | $mV_{PP}$        |

| Input Impedance (DIN, REFCLK)*                       | R <sub>IN</sub>    | Line-to-Line                  | 84    | 100                    | 116        | Ω                |

| Differential Output Voltage Swing (DOUT) OC48/12/3   | V <sub>OD</sub>    | 100 Ω Load<br>Line-to-Line    | 780   | 990                    | 1260       | mV <sub>PP</sub> |

| Differential Output Voltage Swing (CLKOUT) OC48/12/3 | V <sub>OD</sub>    | 100 Ω Load<br>Line-to-Line    | 550   | 900                    | 1260       | $mV_{PP}$        |

| Output Common Mode Voltage<br>(DOUT,CLKOUT)          | V <sub>OCM</sub>   | 100 Ω Load<br>Line-to-Line    | _     | V <sub>DD</sub> – 0.23 | _          | V                |

| Output Impedance (DOUT,CLKOUT)                       | R <sub>OUT</sub>   | Single-ended                  | 84    | 100                    | 116        | Ω                |

| Output Short to GND (DOUT,CLKOUT)                    | I <sub>SC(-)</sub> |                               |       | 25                     | 31         | mA               |

| Output Short to V <sub>DD</sub> (DOUT,CLKOUT)        | I <sub>SC(+)</sub> |                               | -17.5 | -14.5                  | _          | mA               |

| Input Voltage Low (LVTTL Inputs)                     | V <sub>IL</sub>    |                               | _     | _                      | .8         | V                |

| Input Voltage High (LVTTL Inputs)                    | V <sub>IH</sub>    |                               | 2.0   | _                      | _          | V                |

| Input Low Current (LVTTL Inputs)                     | I <sub>IL</sub>    |                               | _     | _                      | 10         | μΑ               |

| Input High Current (LVTTL Inputs)                    | I <sub>IH</sub>    |                               | _     | _                      | 10         | μΑ               |

| Output Voltage Low (LVTTL Outputs)                   | V <sub>OL</sub>    | I <sub>O</sub> = 2 mA         | _     | _                      | 0.4        | V                |

| Output Voltage High (LVTTL Outputs)                  | V <sub>OH</sub>    | I <sub>O</sub> = 2 mA         | 2.0   | _                      | _          | V                |

| Input Impedance (LVTTL Inputs)                       | R <sub>IN</sub>    |                               | 10    | _                      | _          | kΩ               |

| PWRDN/CAL Leakage Current                            | I <sub>PWRDN</sub> | $V_{PWRDN} \ge 0.8 \text{ V}$ | 15    | 25                     | 35         | μΑ               |

|                                                      |                    |                               |       | -                      |            |                  |

\*Note: The DIN and REFCLK inputs may be driven differentially or single-endedly. When driving single-endedly, the voltage swing of the signal applied to the active input must exceed the specified minimum Differential Input Voltage Swing (VID min) and the unused input must be ac coupled to ground. When driving differentially, the difference between the positive and negative input signals must exceed VID min. (Each individual input signal needs to swing only half of this range.) In either case, the voltage applied to any individual pin (DIN+, DIN-, REFCLK+, or REFCLK-) must not exceed the specified maximum Input Voltage Range (VIS max).

## Table 3. AC Characteristics (Clock & Data)

$(V_A 2.5 V \pm 5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                                             | Symbol                         | Test Condition                     | Min                              | Тур                              | Max                              | Unit     |

|-----------------------------------------------------------------------|--------------------------------|------------------------------------|----------------------------------|----------------------------------|----------------------------------|----------|

| Output Clock Rate                                                     | f <sub>CLK</sub>               |                                    | .15                              | _                                | 2.7                              | GHz      |

| Output Rise/Fall Time (differential)                                  | t <sub>R,</sub> t <sub>F</sub> | Figure 3                           | _                                | 80                               | 110                              | ps       |

| Clock to Data Delay<br>FEC (2.7 GHz)<br>OC-48<br>GbE<br>OC-12<br>OC-3 | t <sub>C-D</sub>               | Figure 2                           | 225<br>225<br>460<br>835<br>4040 | 250<br>250<br>500<br>880<br>4090 | 270<br>270<br>540<br>930<br>4140 | ps       |

| Input Return Loss                                                     |                                | 100 kHz–2.5 GHz<br>2.5 GHz–4.0 GHz | _                                | 16<br>13                         | _                                | dB<br>dB |

## **Table 4. AC Characteristics (PLL Characteristics)**

(V<sub>A</sub> 2.5 V ±5%,  $T_A = -40$  to 85 °C)

| Parameter                                                                             | Symbol                | Test Condition                | Min | Тур | Max | Unit             |

|---------------------------------------------------------------------------------------|-----------------------|-------------------------------|-----|-----|-----|------------------|

| Jitter Tolerance                                                                      | J <sub>TOL(PP)</sub>  | f = 600 Hz                    | 40  | _   | _   | Ul <sub>PP</sub> |

| (OC-48)*                                                                              |                       | f = 6000 Hz                   | 4   | _   |     | UI <sub>PP</sub> |

|                                                                                       |                       | f = 100 kHz                   | 4   | _   | _   | Ul <sub>PP</sub> |

|                                                                                       |                       | f = 1 MHz                     | 0.4 | _   | _   | Ul <sub>PP</sub> |

| Jitter Tolerance (OC-12 Mode)*                                                        | J <sub>TOL(PP)</sub>  | f = 30 Hz                     | 40  | _   | _   | Ul <sub>PP</sub> |

|                                                                                       |                       | f = 300 Hz                    | 4   | _   | _   | Ul <sub>PP</sub> |

|                                                                                       |                       | f = 25 kHz                    | 4   | _   | _   | UI <sub>PP</sub> |

|                                                                                       |                       | f = 250 kHz                   | 0.4 | _   | _   | Ul <sub>PP</sub> |

| Jitter Tolerance (OC-3 Mode)*                                                         | J <sub>TOL(PP)</sub>  | f = 30 Hz                     | 60  | _   | _   | Ul <sub>PP</sub> |

|                                                                                       |                       | f = 300 Hz                    | 6   | _   |     | UI <sub>PP</sub> |

|                                                                                       |                       | f = 6.5 kHz                   | 6   | _   |     | Ul <sub>PP</sub> |

|                                                                                       |                       | f = 65 kHz                    | 0.6 | _   | _   | UI <sub>PP</sub> |

| Jitter Tolerance (Gigabit Ethernet)<br>Receive Data Total Jitter<br>Tolerance         | T <sub>JT(PP)</sub>   | IEEE 802.3z Clause 38.68      | 600 | _   | _   | ps               |

| Jitter Tolerance (Gigabit Ethernet)<br>Receive Data Deterministic Jitter<br>Tolerance | D <sub>JT(PP)</sub>   | IEEE 802.3z Clause 38.69      | 370 | _   | _   | ps               |

| RMS Jitter Generation*                                                                | J <sub>GEN(rms)</sub> | with no jitter on serial data | _   | 2.9 | 5.0 | mUI              |

| Peak-to-Peak Jitter Generation*                                                       | J <sub>GEN(PP)</sub>  | with no jitter on serial data | _   | 25  | 55  | mUI              |

# Si5020

Table 4. AC Characteristics (PLL Characteristics) (Continued)

$(V_A 2.5 V \pm 5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                                                                                           | Symbol           | Test Condition                  | Min                     | Тур        | Max    | Unit |

|---------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------|-------------------------|------------|--------|------|

| Jitter Transfer Bandwidth <sup>*</sup>                                                                              | $J_BW$           | OC-48 Mode                      | _                       | _          | 2.0    | MHz  |

|                                                                                                                     |                  | OC-12 Mode                      |                         | _          | 500    | kHz  |

|                                                                                                                     |                  | OC-3 Mode                       |                         | _          | 130    | kHz  |

| Jitter Transfer Peaking*                                                                                            | J <sub>P</sub>   |                                 |                         | 0.03       | 0.1    | dB   |

| Acquisition Time                                                                                                    | T <sub>AQ</sub>  | After falling edge of PWRDN/CAL | 1.45                    | 1.5        | 1.7    | ms   |

|                                                                                                                     |                  | From the return of valid data   | 40                      | 60         | 150    | μS   |

| Input Reference Clock Duty Cycle                                                                                    | $C_{DUTY}$       |                                 | 40                      | 50         | 60     | %    |

| Reference Clock Range                                                                                               |                  |                                 | 19.44                   | _          | 168.75 | MHz  |

| Input Reference Clock Frequency Tolerance                                                                           | C <sub>TOL</sub> |                                 | -100                    | _          | 100    | ppm  |

| Frequency Difference at which<br>Receive PLL goes out of Lock<br>(REFCLK compared to the divided<br>down VCO clock) | LOL              |                                 | 450                     | 600        | 750    | ppm  |

| Frequency Difference at which<br>Receive PLL goes into Lock (REF-<br>CLK compared to the divided<br>down VCO clock) | LOCK             |                                 | 150                     | 300        | 450    | ppm  |

| *Note: Bellcore specifications: GR-253                                                                              | -CORE, Issu      | e 3, September 2000. Using PR   | RBS 2 <sup>23</sup> – 1 | data patte | ern.   |      |

Rev. 1.5

8

**Table 5. Absolute Maximum Ratings**

| Parameter                          | Symbol           | Value                           | Unit |

|------------------------------------|------------------|---------------------------------|------|

| DC Supply Voltage                  | V <sub>DD</sub>  | -0.5 to 2.8                     | V    |

| LVTTL Input Voltage                | $V_{DIG}$        | -0.3 to 3.6                     | V    |

| Differential Input Voltages        | V <sub>DIF</sub> | -0.3 to (V <sub>DD</sub> + 0.3) | V    |

| Maximum Current any output PIN     |                  | ±50                             | mA   |

| Operating Junction Temperature     | T <sub>JCT</sub> | -55 to 150                      | °C   |

| Storage Temperature Range          | T <sub>STG</sub> | -55 to 150                      | °C   |

| ESD HBM Tolerance (100 pf, 1.5 kΩ) |                  | 1                               | kV   |

**Note:** Permanent device damage may occur if the above absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Table 6. Thermal Characteristics**

| Parameter                              | Symbol | Test Condition | Value | Unit |

|----------------------------------------|--------|----------------|-------|------|

| Thermal Resistance Junction to Ambient | φја    | Still Air      | 38    | °C/W |

# 3. Typical Application Schematic

## 4. Functional Description

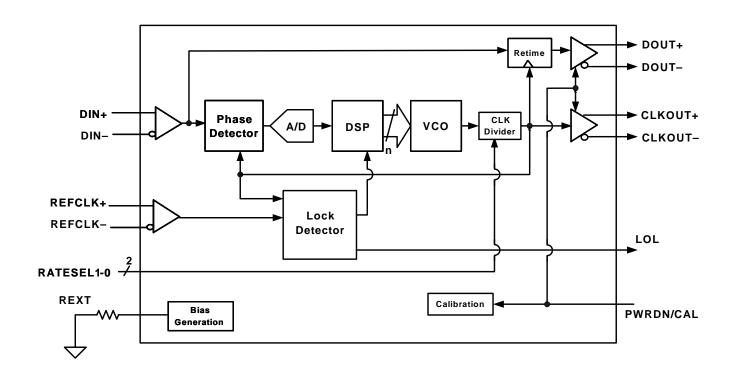

The Si5020 utilizes a phase-locked loop (PLL) to recover a clock synchronous to the input data stream. This clock is used to retime the data, and both the recovered clock and data are output synchronously via current mode logic (CML) drivers. Optimal jitter performance is obtained by using Silicon Laboratories' DSPLL technology to eliminate the noise entry points caused by external PLL loop filter components.

### 4.1. DSPLL™

The PLL structure (shown in Figure 1 on page 5) utilizes Silicon Laboratories' DSPLL technology to eliminate the need for external loop filter components found in traditional PLL implementations. This is achieved by using a digital signal processing (DSP) algorithm to replace the loop filter commonly found in analog PLL designs. This algorithm processes the phase detector error term and generates a digital control value to adjust the frequency of the voltage-controlled oscillator (VCO). Because external loop filter components are not required, sensitive noise entry points are eliminated, making the DSPLL less susceptible to board-level noise sources that make SONET/SDH jitter compliance difficult to attain.

### 4.2. PLL Self-Calibration

The Si5020 achieves optimal jitter performance by using self-calibration circuitry to set the loop gain parameters within the DSPLL. For the self-calibration circuitry to operate correctly, the power supply voltage must exceed 2.25 V when calibration occurs. For best performance, the user should force a self-calibration once the supply has stabilized on powerup.

A self-calibration can be initiated by forcing a high-to-low transition on the powerdown control input, PWRDN/CAL, while a valid reference clock is supplied to the REFCLK input. The PWRDN/CAL input should be held high at least 1 μs before transitioning low to guarantee a self-calibration. Several application circuits that could be used to initiate a power-on self-calibration are provided in Silicon Laboratories' "AN42: Controlling DSPLL™ Self-Calibration for the Si5020/5018/5010 CDR Devices and Si531x Clock Multiplier/Regenerator Devices."

## 4.3. Multi-Rate Operation

The Si5020 supports clock and data recovery for OC-48 and STM-16 data streams. In addition, the PLL was designed to operate at data rates up to 2.7 Gbps to support OC-48/STM-16 applications that employ forward error correction (FEC).

Multi-rate operation is achieved by configuring the device to divide down the output of the VCO to the desired data rate. The divide factor is configured by the RATESEL0-1 pins. The RATESEL0-1 configuration and associated data rates are given in Table 7.

**Table 7. Multi-Rate Configuration**

| RATESEL<br>[0:1] | SONET/<br>SDH | Gigabit<br>Ethernet | OC-48<br>with<br>15/14<br>FEC | CLK<br>Divider |

|------------------|---------------|---------------------|-------------------------------|----------------|

| 00               | 2.488 Gbps    | _                   | 2.67 Gbps                     | 1              |

| 10               | 1.244 Gbps    | 1.25 Gbps           | _                             | 2              |

| 01               | 622.08 Mbps   | _                   | _                             | 4              |

| 11               | 155.52 Mbps   | _                   | _                             | 16             |

#### 4.4. Reference Clock Detect

The Si5020 CDR requires an external reference clock applied to the REFCLK input for normal device operation. When REFCLK is absent, the LOL alarm will always be asserted when it has been determined that no activity exists on REFCLK, indicating the frequency lock status of the PLL is unknown. Additionally, the Si5020 uses the reference clock to center the VCO output frequency so that clock and data can be recovered from the input data stream. The device self configures for operation with one of three reference clock frequencies. This eliminates the need to externally configure the device to operate with a particular reference clock.

The reference clock centers the VCO for a nominal output of between 2.5 GHz and 2.7 GHz. The VCO frequency is centered at 16, 32, or 128 times the reference clock frequency. Detection circuitry continuously monitors the reference clock input to determine whether the device should be configured for a reference clock that is 1/16, 1/32, or 1/128 the nominal VCO output. Approximate reference clock frequencies for some target applications are given in Table 8.

**Table 8. Typical REFCLK Frequencies**

| SONET/SDH  | Gigabit<br>Ethernet | SONET/<br>SDH with<br>15/14 FEC | Ratio of VCO to REFCLK |  |

|------------|---------------------|---------------------------------|------------------------|--|

| 19.44 MHz  | 19.53 MHz           | 20.83 MHz                       | 128                    |  |

| 77.76 MHz  | 78.125 MHz          | 83.31 MHz                       | 32                     |  |

| 155.52 MHz | 156.25 MHz          | 166.63 MHz                      | 16                     |  |

## 4.5. Forward Error Correction (FEC)

The Si5020 supports FEC in SONET OC-48 (SDH STM-16) applications for data rates up to 2.7 Gbps. In FEC applications, the appropriate reference clock frequency is determined by dividing the input data rate by 16, 32, or 128. For example, if an FEC code is used that produces a 2.70 Gbps data rate, the required reference clock would be 168.75, 84.375, or 21.09 MHz.

#### 4.6. Lock Detect

The Si5020 provides lock-detect circuitry that indicates whether the PLL has achieved frequency lock with the incoming data. The circuit compares the frequency of a divided-down version of the recovered clock with the frequency of the applied reference clock (REFCLK). If the recovered clock frequency deviates from that of the reference clock by the amount specified in Table 4 on page 7, the PLL is declared out-of-lock, and the loss-oflock (LOL) pin is asserted high. In this state, the PLL will periodically try to reacquire lock with the incoming data stream. During reacquisition, the recovered clock may drift over a ±600 ppm range relative to the applied reference clock, and the LOL output alarm may toggle until the PLL has reacquired frequency lock. Due to the low noise and stability of the DSPLL, under the condition where data is removed from the inputs, there is the possibility that the PLL will not drift enough to render an out-of-lock condition.

If REFCLK is removed, the LOL output alarm will always be asserted when it has been determined that no activity exists on REFCLK, indicating the frequency lock status of the PLL is unknown.

Note: LOL is not asserted during PWRDN/CAL.

### 4.7. PLL Performance

The PLL implementation used in the Si5020 is fully compliant with the jitter specifications proposed for SONET/SDH equipment by Bellcore GR-253-CORE, Issue 2, December 1995 and ITU-T G.958.

#### 4.7.1. Jitter Tolerance

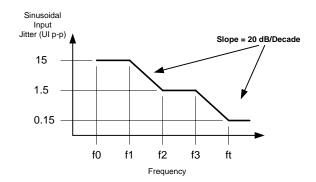

The Si5020's tolerance to input jitter exceeds that of the Bellcore/ITU mask shown in Figure 4. This mask defines the level of peak-to-peak sinusoid jitter that must be tolerated when applied to the differential data input of the device.

**Note:** There are no entries in the mask table for the data rate corresponding to OC-24 as that rate is not specified by either GR-253 or G.958.

| SONET<br>Data Rate | F0<br>(Hz) | F1<br>(Hz) | F2<br>(Hz) | F3<br>(kHz) | Ft<br>(kHz) |

|--------------------|------------|------------|------------|-------------|-------------|

| OC- 48             | 10         | 600        | 6000       | 1000        | 1000        |

| OC- 12             | 10         | 30         | 300        | 25          | 250         |

| OC- 3              | 10         | 30         | 300        | 6.5         | 65          |

Figure 4. Jitter Tolerance Specification

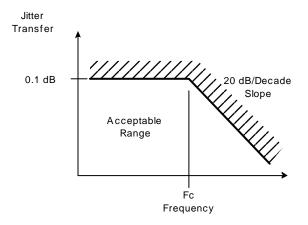

## 4.7.2. Jitter Transfer

The Si5020 is fully compliant with the relevant Bellcore/ITU specifications related to SONET/SDH jitter transfer. Jitter transfer is defined as the ratio of output signal jitter to input signal jitter as a function of jitter frequency (see Figure 5). These measurements are made with an input test signal that is degraded with sinusoidal jitter whose magnitude is defined by the mask in Figure 4.

#### 4.7.3. Jitter Generation

The Si5020 exceeds all relevant specifications for jitter generation proposed for SONET/SDH equipment. The jitter generation specification defines the amount of jitter that may be present on the recovered clock and data outputs when a jitter free input signal is provided. The Si5020 typically generates less than 3.0 mUI<sub>rms</sub> of jitter when presented with jitter-free input data.

| SONET<br>Data Rate | Fc<br>(k Hz) |

|--------------------|--------------|

| OC-48              | 2000         |

| OC-12              | 500          |

| OC-3               | 130          |

Figure 5. Jitter Transfer Specification

#### 4.8. Powerdown

The Si5020 provides a powerdown pin, PWRDN/CAL, that disables the output drivers (DOUT, CLKOUT). When the PWRDN/CAL pin is driven high, the positive and negative terminals of CLKOUT and DOUT are each tied to VDD through 100  $\Omega$  on-chip resistors. This feature is useful in reducing power consumption in applications that employ redundant serial channels.

When PWRDN/CAL is released (set to low) the digital logic resets to a known initial condition, recalibrates the DSPLL, and will begin to lock to the data stream.

## 4.9. Device Grounding

The Si5020 uses the GND pad on the bottom of the 20pin micro leaded package (MLP) for device ground. This pad should be connected directly to the analog supply ground. See Figures 10 and 11 for the ground (GND) pad location.

## 4.10. Bias Generation Circuitry

The Si5020 makes use of an external resistor to set internal bias currents. The external resistor allows precise generation of bias currents, which significantly reduces power consumption versus traditional implementations that use an internal resistor. The bias generation circuitry requires a 10 k $\Omega$  (1%) resistor connected between REXT and GND.

## 4.11. Differential Input Circuitry

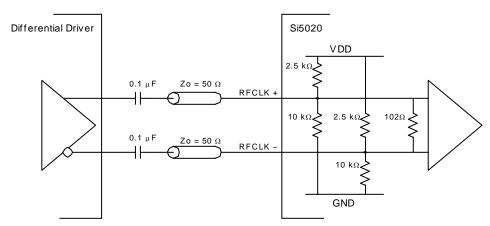

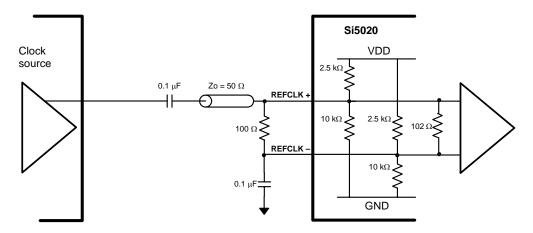

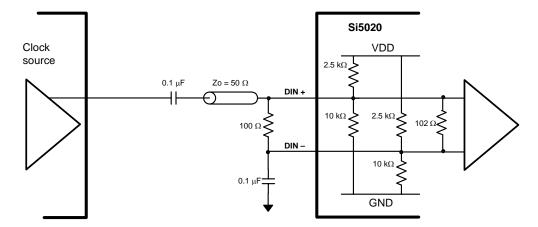

The Si5020 provides differential inputs for both the high-speed data (DIN) and the reference clock (REFCLK) inputs. An example termination for these inputs is shown in Figure 6. In applications where direct dc coupling is possible, the 0.1  $\mu F$  capacitors may be omitted. The DIN and REFCLK input amplifiers require an input signal with a minimum differential peak-to-peak voltage listed in Table 2 on page 6.

Figure 6. Input Termination for DIN and REFCLK (AC Coupled)

Figure 7. Single-Ended Input Termination for REFCLK (AC Coupled)

Figure 8. Single-Ended Input Termination for DIN (AC Coupled)

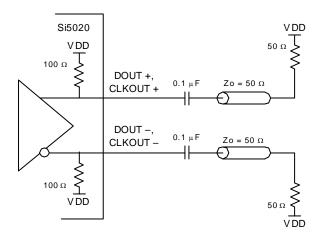

## 4.12. Differential Output Circuitry

The Si5020 utilizes a current mode logic (CML) architecture to output both the recovered clock (CLKOUT) and data (DOUT). An example of output termination with ac coupling is shown in Figure 9. In applications in which direct dc coupling is possible, the 0.1  $\mu$ F capacitors may be omitted. The differential peak-to-peak voltage swing of the CML architecture is listed in Table 2 on page 6.

Figure 9. Output Termination for DOUT and CLKOUT (AC Coupled)

# 5. Pin Descriptions: Si5020

Figure 10. Si5020 Pin Configuration

Table 9. Si5020 Pin Descriptions

| Pin #   | Pin Name     | I/O | Signal Level | Description                                                                                                                                                                                                 |

|---------|--------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | REXT         |     |              | External Bias Resistor. This resistor is used by onboard circuitry to establish bias currents within the device. This pin must be connected to GND through a 10 k $\Omega$ (1%) resistor.                   |

| 4       | REFCLK+      | I   | See Table 2  | Differential Reference Clock.                                                                                                                                                                               |

| 5       | REFCLK-      |     |              | The reference clock sets the initial operating frequency used by the onboard PLL for clock and data recovery. Additionally, the reference clock is used to derive the clock output when no data is present. |

| 6       | LOL          | 0   | LVTTL        | Loss-of-Lock. This output is driven high when the recovered clock frequency deviates from the reference clock by the amount specified in Table 4 on page 7.                                                 |

| 9<br>10 | DIN+<br>DIN- | I   | See Table 2  | Differential Data Input.  Clock and data are recovered from the differential signal present on these pins.                                                                                                  |

| 12      | DOUT-        | 0   | CML          | Differential Data Output.                                                                                                                                                                                   |

| 13      | DOUT+        |     |              | The data output signal is a retimed version of the data recovered from the signal present on DIN. It is phase aligned with CLKOUT and is updated on the rising edge of CLKOUT.                              |

Table 9. Si5020 Pin Descriptions (Continued)

| Pin#                     | Pin Name  | I/O | Signal Level | Description                                                                                                                                                                                           |

|--------------------------|-----------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15                       | PWRDN/CAL | I   | LVTTL        | Powerdown.                                                                                                                                                                                            |

|                          |           |     |              | To shut down the high-speed outputs and reduce power consumption, hold this pin high. For normal operation, hold this pin low.  Calibration.                                                          |

|                          |           |     |              | To initiate an internal self-calibration, force a high-to-low transition on this pin. (See "PLL Self-Calibration" on page 11.)  Note: This input has a weak internal pulldown.                        |

| 16                       | CLKOUT-   | 0   | CML          | Differential Clock Output.                                                                                                                                                                            |

| 17                       | CLKOUT+   | -   |              | The output clock is recovered from the data signal present on DIN. In the absence of data, the output clock is derived from REFCLK.                                                                   |

| 19                       | RATESEL0  | ı   | LVTTL        | Data Rate Select.                                                                                                                                                                                     |

| 20                       | RATESEL1  |     |              | These pins configure the onboard PLL for clock and data recovery at one of four user selectable data rates. See Table 7 for configuration settings.  Note: These inputs have weak internal pulldowns. |

| 2, 7, 11, 14             | VDD       |     | 2.5 V        | Supply Voltage. Nominally 2.5 V.                                                                                                                                                                      |

| 3, 8, 18, and<br>GND Pad | GND       |     | GND          | Supply Ground.  Nominally 0.0 V. The GND pad found on the bottom of the 20-pin micro leaded package (see Figure 11) must be connected directly to supply ground.                                      |

# 6. Ordering Guide

| Part Number Package |             | Voltage Pb-Free |     | Temperature  |  |

|---------------------|-------------|-----------------|-----|--------------|--|

| Si5020-X-GM         | 20-Lead QFN | 2.5             | Yes | –40 to 85 °C |  |

- 1. "X" denotes product revision.

- 2. Add an "R" at the end of the device to denote tape and reel option; 2500 quantity per reel.

- **3.** These devices use a NiPdAu pre-plated finish on the leads that is fully RoHS6 compliant while being fully compatible with both leaded and lead-free card assembly processes.

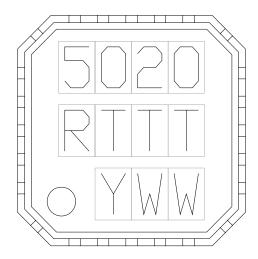

# 7. Top Mark

| Silicon Labs<br>Part Number | Die Revision (R) | Assembly Date (YWW)                             |

|-----------------------------|------------------|-------------------------------------------------|

| Si5020-B-GM                 | В                | Y = Last digit of current year<br>WW= Work week |

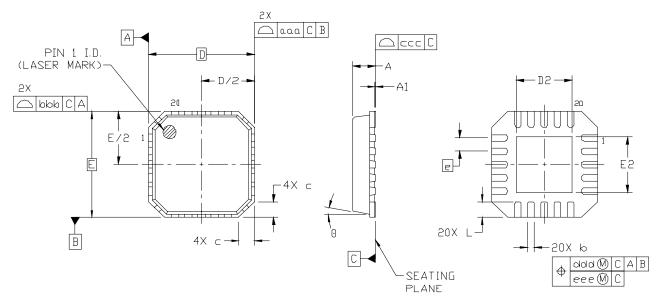

# 8. Package Outline

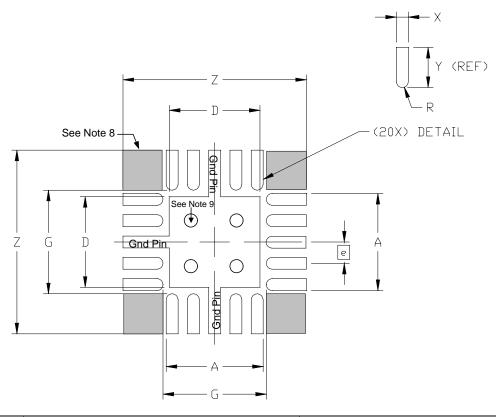

Figure 11 illustrates the package details for the Si5020. Table 10 lists the values for the dimensions shown in the illustration.

Figure 11. 20-pin Quad Flat No-Lead (QFN)

| Table 10. Package Dimension | S |

|-----------------------------|---|

|-----------------------------|---|

| Symbol | Millimeters |      |      |  |

|--------|-------------|------|------|--|

|        | Min         | Nom  | Max  |  |

| Α      | 0.80        | 0.85 | 0.90 |  |

| A1     | 0.00        | 0.02 | 0.05 |  |

| b      | 0.18        | 0.25 | 0.30 |  |

| С      | _           | _    | 0.60 |  |

| D      | 4.00 BSC    |      |      |  |

| D2     | 1.95        | 2.10 | 2.25 |  |

| е      | 0.50 BSC    |      |      |  |

| Е      | 4.00 BSC    |      |      |  |

| Symbol | Millimeters |      |      |  |  |

|--------|-------------|------|------|--|--|

|        | Min         | Nom  | Max  |  |  |

| E2     | 1.95        | 2.10 | 2.25 |  |  |

| L      | 0.50        | 0.60 | 0.70 |  |  |

| θ      | 0°          | _    | 12°  |  |  |

| aaa    | 0.10        |      |      |  |  |

| bbb    | 0.10        |      |      |  |  |

| CCC    | 0.08        |      |      |  |  |

| ddd    | ddd         |      |      |  |  |

| eee    | 0.05        |      |      |  |  |

#### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MO-220, variation VGGD-1.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

# 9. 4x4 mm 20L QFN Recommended PCB Layout

| Symbol | Parameter                   | Dimensions |          |      |

|--------|-----------------------------|------------|----------|------|

|        |                             | Min        | Nom      | Max  |

| Α      | Pad Row/Column Width/Length | 2.23       | 2.25     | 2.28 |

| D      | Thermal Pad Width/Height    | 2.03       | 2.08     | 2.13 |

| е      | Pad Pitch                   | _          | 0.50 BSC | _    |

| G      | Pad Row/Column Separation   | 2.43       | 2.46     | 2.48 |

| R      | Pad Radius                  | _          | 0.12 REF | _    |

| X      | Pad Width                   | 0.23       | 0.25     | 0.28 |

| Y      | Pad Length                  | _          | 0.94 REF | _    |

| Z      | Pad Row/Column Extents      | 4.26       | 4.28     | 4.31 |

#### Notes:

- 1. All dimensions listed are in millimeters (mm).

- 2. The perimeter pads are to be Non-Solder Mask Defined (NSMD). Solder mask openings should be designed to leave 60-75 mm separation between solder mask and pad metal, all the way around the pad.

- 3. The center thermal pad is to be Solder Mask Defined (SMD).

- 4. Thermal/Ground vias placed in the center pad should be no less than 0.2 mm (8 mil) diameter and tented from the top to prevent solder from flowing into the via hole.

- 5. The stencil aperture should match the pad size (1:1 ratio) for the perimeter pads. A 3x3 array of 0.5 mm square stencil openings, on a 0.65 mm pitch, should be used for the center thermal pad.

- 6. A stencil thickness of 5 mil is recommended. The stencil should be laser cut and electropolished, with trapezoidal walls to facilitate paste release.

- 7. A "No-Clean", Type 3 solder paste should be used for assembly. Nitrogen purge during reflow is recommended.

- 8. Do not place any signal or power plane vias in these "keep out" regions.

- 9. Suggest four 0.38 mm (15 mil) vias to the ground plane.

## **DOCUMENT CHANGE LIST**

## **Revision 1.2 to Revision 1.3**

- Added "Top Mark" on page 18.

- Updated "Package Outline" on page 19.

- Added "4x4 mm 20L QFN Recommended PCB Layout" on page 20.

## **Revision 1.3 to Revision 1.4**

Made minor note corrections to "4x4 mm 20L QFN Recommended PCB Layout" on page 20.

## **Revision 1.4 to Revision 1.5**

- Added "Top Mark" on page 18.

- Updated "Ordering Guide" on page 18.

- Updated "Package Outline" on page 19.

# Si5020

## **CONTACT INFORMATION**

Silicon Laboratories Inc.

400 West Cesar Chavez Austin, TX 7801 Tel: 1+(512) 416-8500

Fax: 1+(512) 416-9669 Toll Free: 1+(877) 444-3032 Email: HighSpeed@silabs.com Internet: www.silabs.com

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application. Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories, Silicon Labs, and DSPLL are trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.