### IES5507 d 4-Channel 2-Wire Bus Switch

**Buffered 4-Channel 2-Wire Bus Switch**

#### 1 FEATURES

- Drop-in pin compatible with other manufacturer's parts

- Each I/O is impedance isolated from all others allowing maximum capacitance on all branches.

- 30mA static sink capability on all ports.

- Works with I<sup>2</sup>C-bus<sup>(1)</sup> (Standard, Fast Mode, and FM+), SMBus (standard and high power mode), and PMbus

- · Fast switching times allow operation in excess of 1MHz

- Allows driving of large loads (eg. 5x 4nF)

- · Hysteresis on I/O increases noise immunity

- Operating voltages from 2.7 V to 5.5 V

- Uncomplicated characteristics suitable for quick implementation in most common 2-wire bus applications

#### 2 APPLICATIONS

- Large arrays of I<sup>2</sup>C components eg LED displays;

- Power Management Systems;

- Game Consoles; Computers; RAID systems;

(1) I<sup>2</sup>C-bus is a trademark of NXP B.V.

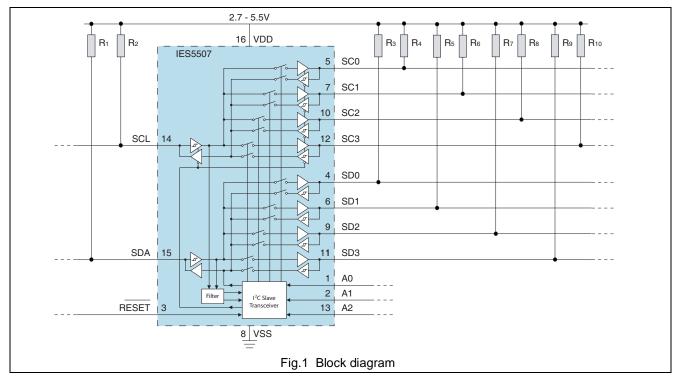

#### 4 BLOCK DIAGRAM

#### **3 GENERAL DESCRIPTION**

The IES5507 is a monolithic CMOS integrated circuit for 2-wire bus buffering and switching in applications including  $I^2C$ , SMBus, PMbus, and other systems based on similar principles.

Each of the four outputs may be independently enabled in any combination as determined by the contents of the programmable control register. Each I/O is impedance isolated from all others, thus allowing a total of five branches of 2-wire bus with the maximum specified load (e.g. 5x 400pF for I<sup>2</sup>C FM+ at 1MHz, or 5x 4nF at lower frequencies). More than one IES5507 may be used in series, providing a substantial fan-out capability.

As per the IES5505/15 simple bus buffers, the IES5507 includes a uni-directional buffer for the clock signal, and a bi-directional buffer for the data signal. The direction of the clock signal may also be set by the contents of the programmable control register. Clock stretching and timing must always be under control of the Master device.

The IES5507 has excellent application to 2-wire bus address expansion and increasing of maximum load capacitance. Very large LED displays are a perfect example.

© 2009 Hendon Semiconductors Pty. Ltd. , all rights reserved.

2009 Mar 05, Revision 1.0

Contents are subject to the Disclaimer

### IES5507 Buffered 4-Channel 2-Wire Bus Switch

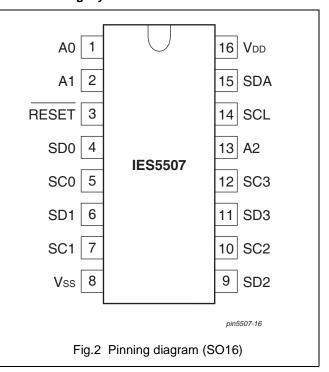

#### 5 PINNING INFORMATION

#### 5.1 Pin description

| SYMBOL          | PIN | DESCRIPTION                     |

|-----------------|-----|---------------------------------|

| A0              | 1   | Address Input 0                 |

| A1              | 2   | Address Input 1                 |

| RESET           | 3   | Active Low Reset Input          |

| SD0             | 4   | Serial Data 0                   |

| SC0             | 5   | Serial Clock 0                  |

| SD1             | 6   | Serial Data 1                   |

| SC1             | 7   | Serial Clock 1                  |

| V <sub>SS</sub> | 8   | Negative supply (ground)        |

| SD2             | 9   | Serial Data 2                   |

| SC2             | 10  | Serial Clock 2                  |

| SD3             | 11  | Serial Data 3                   |

| SC3             | 12  | Serial Clock 3                  |

| A2              | 13  | Address Input 2                 |

| SCL             | 14  | Serial Clock Line (normally in) |

| SDA             | 15  | Serial Data Line                |

| V <sub>DD</sub> | 16  | Positive supply                 |

#### 5.2 Pinning layout

#### **6** FUNCTIONAL DESCRIPTION

#### 6.1 V<sub>DD</sub>, V<sub>SS</sub> - DC supply pins

The power supply voltage for the IES5507 may be any voltage in the range 2.7 V to 5.5 V. The IC supply must be common with the supply for the bus. Hysteresis on the ports are a percentage of the IC's power supply, hence noise margin considerations should be taken into account when selecting an operating voltage.

#### 6.2 SCL - Clock Signal Input

The clock signal buffer is uni-directional, with this pin acting as the default input. However, the clock signal direction may be reversed by setting the MSB of the control register HIGH. In normal bus operations, for example the I<sup>2</sup>C bus, the Master device generates a uni-directional clock signal to the slave. For lowest cost the IES5507 combines uni-directional buffering of the clock signal with a bi-directional buffer for the data signal. Clock stretching is therefore not supported and Slave devices that may require clock stretching must be accommodated by the Master adopting an appropriate clocking when communicating with them.

The buffer includes hysteresis to ensure clean switching signals are output, especially with slow rise times on high capacitively loaded buses.

#### 6.3 SC0, SC1, SC2, SC3 - Clock Signal Outputs

The clock signal from SCL is buffered through four independent buffers, and the signal is presented at the four SC0..3 ports. Ports are open-drain type and require external pullup resistors.

When the MSB of the control register is set HIGH, the port direction is reversed. The 'AND-ed' result of the four SC0..3 lines is then used to drive the open drain output of the SCL pin.

#### 6.4 SDA, SD0..3 - Data Signal Inputs/Outputs

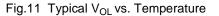

The data signal buffers are bi-directional. The port (SDA, or any one of SD0..3) which first falls low, will decide the direction of this buffer and "lock out" signals coming from the opposite side. As the "input" signal continues to fall, it will then drive the open-drain of the "output" side low. Again, hysteresis is applied to the buffer to minimise the effects of noise. Ports are open-drain type and require external pullup resistors.

# IES5507

### **Buffered 4-Channel 2-Wire Bus Switch**

At some points during the communication, the data direction will reverse - for example, when the Slave transmits an acknowledge (ACK) or responds with it's register contents. During these times, the controlling "input" side will have to rise to  $V_{LK}$  before it releases the "lock", which then allows the "output" side to gain control, and pull (what was) the "input" side low again. This will cause a "pulse" on the "input" side, which can be quite large in high capacitance buses. However, this pulse will not interfere with the actual data transmission, as it should not occur during times of clock line transition (during normal I<sup>2</sup>C and SMBus protocols), and thus data signal set-up time requirements are still met.

#### 6.5 RESET - Reset IC to Default State

The active low RESET input is used to disable the buffer, and reset it to it's default state. The IC should only be disabled when the bus is idle to avoid truncation of commands which may confuse other devices on the bus.

The RESET signal will clear the contents of the control register, which has the effect of disabling all output lines SC0..3 and SD0..3. It is the nature of the I<sup>2</sup>C protocol that devices may become 'stuck'. To help in the clearing of this condition, the IES5507 can be reset, and each port brought on-line successively to find the component holding the bus low.

#### 6.6 Power On Reset (POR)

During power-on, the IES5507 is internally held in the reset condition for a maximum of  $t_{RST}$  = 500ns. The default condition after reset is for the Control Register to be Erased (all zeros), resulting in all output channels being disabled.

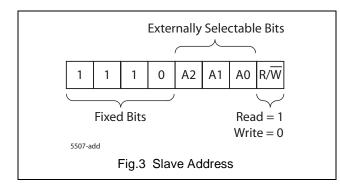

#### 6.7 A0, A1, A2 - Address lines

The slave address of the IES5507 is shown in the Figure 3. The address pins (A2..0) must be driven to a HIGH or LOW level - they are not internally pulled to a default state.

The read/write bit must be set LOW to enable a write to the control register, or HIGH to read from the control register.

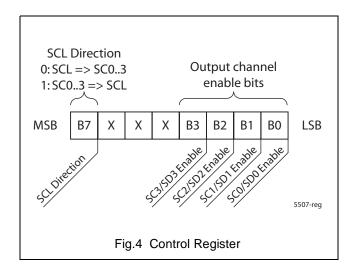

#### 6.8 Control Register

The control register of the IES5507 is shown in the Figure 4. Each of the four output channels (SCx/SDx pairs) can be enabled independently, and the direction of the clock signal can be reversed.

A LOW or zero bit (B3..0) indicates that the respective channel (SC3..0 / SD3..0) is disabled. The default reset condition of the register is all zeros, all channels disabled, forward direction. A HIGH or one bit indicates the respective channel is enabled.

Example: B3 = 1, B2 = 0, B1 = 1, B0 = 0 means channels 3 (SC3/SD3) and 1 (SC1/SD1) are enabled, and channels 2 (SC2/SD2) and 0 (SC0/SD0) are disabled.

As each channel is individually buffered, the loads on each are isolated, and therefore there is no special requirement to keep the sum of the collective capacitances below the maximum bus capacitance. Instead, each line may have up to the maximum bus capacitance and be enabled or disabled without affecting the performance of the other channels.

The Most Significant Bit (MSB) B7 is used to set the direction of the SCL (clock) signal. The default state is LOW (zero). In this state, the SCL port will act as the input, and the IC will supply a buffered signal to any of the four output channels (SC0..3) which are enabled. When B7 is set HIGH (one), the clock signal direction is reversed. The ports SC0..3 act as inputs, the AND-ed combination of their signals is buffered and output on the SCL pin.

The IES5507 is always addressable from the SCL/SDA side, regardless of the state of B7. Any device which can communicate data to the SCL/SDA pins, either by being directly attached to those pins or by transmitting through

the IES5507 (when B7=1), may address the device and change the control register's contents. The control register is only updated upon receipt of the STOP condition.

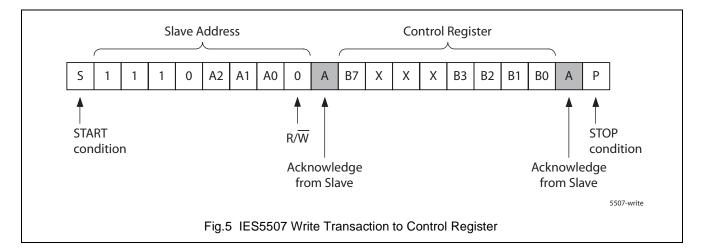

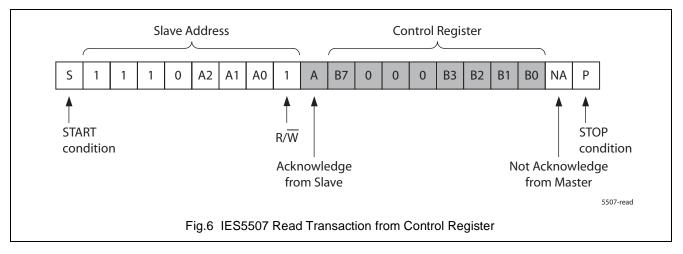

#### 7 BUS TRANSACTION

A typical I<sup>2</sup>C write transaction to the IES5507 is shown in Figure 5. A typical read transaction is shown in figure 6.

#### 8 LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134) Voltages are specified with respect to pin 8 (V<sub>SS</sub>)

| SYMBOL           | PARAMETER                                            | CONDITIONS | MIN.                 | MAX.                 | UNIT |

|------------------|------------------------------------------------------|------------|----------------------|----------------------|------|

| V <sub>DD</sub>  | Supply voltage range (V <sub>DD</sub> )              |            | -0.3                 | +7                   | V    |

| V <sub>Sxx</sub> | Voltage range (SDA <sub>X</sub> , SCL <sub>X</sub> ) |            | V <sub>SS</sub> -0.5 | V <sub>DD</sub> +0.5 | V    |

| V <sub>RST</sub> | Voltage range (RESET)                                |            | V <sub>SS</sub> -0.5 | V <sub>DD</sub> +0.5 | V    |

| V <sub>A20</sub> | Voltage range (ADDRESS pins)                         |            | V <sub>SS</sub> -0.5 | V <sub>DD</sub> +0.5 | V    |

|                  | DC current (pins other than SCx/SDx)                 |            | -                    | 20                   | mA   |

|                  | DC current (all SCx and SDx)                         |            | -                    | 40                   | mA   |

|                  | DC current (V <sub>SS</sub> pin)                     |            | -                    | 280                  | mA   |

| P <sub>tot</sub> | total power dissipation                              |            | _                    | 300                  | mW   |

| T <sub>stg</sub> | storage temperature                                  |            | -55                  | +125                 | °C   |

| T <sub>amb</sub> | operating ambient temperature                        |            | -40                  | +85                  | °C   |

#### 9 CHARACTERISTICS

All specifications apply over the full operating temperature range of  $T_{amb} = -40^{\circ}C$  to +85°C; Voltages are specified with respect to pin 8 (V<sub>SS</sub>); V<sub>DD</sub> = 5.5V unless otherwise specified

|                       |                                   | CONDITIONS                           |                     |      | -    |                      |      |

|-----------------------|-----------------------------------|--------------------------------------|---------------------|------|------|----------------------|------|

| SYMBOL                | PARAMETER                         | OTHER                                | V <sub>DD</sub> (V) | MIN. | TYP. | MAX.                 | UNIT |

| Power su              | pply                              |                                      |                     |      |      |                      |      |

| V <sub>DD</sub>       | supply voltage (operating)        |                                      |                     | 2.7  | _    | 5.5                  | V    |

| I <sub>DD</sub>       | supply current (quiescent)        | $V_{RST} = 0V$                       | 5.5                 | _    | _    | 0.1                  | μΑ   |

| I2C Ports             | (SCL / SDA / SC30 / SD30)         | •                                    |                     |      | •    | •                    |      |

| V <sub>Sxx</sub>      | Bus voltage (SDX, SCX)            |                                      |                     | _    | -    | V <sub>DD</sub> +0.3 | V    |

| V <sub>LK</sub>       | Lock-out input voltage - locked   | [2]                                  | 2.7                 | _    | _    | 1.3                  | V    |

|                       |                                   |                                      | 5.5                 | _    | _    | 3.0                  | V    |

|                       | Lock-out input voltage - unlocked | [2]                                  | 2.7                 | 2.0  | _    | _                    | V    |

|                       |                                   |                                      | 5.5                 | 4.8  | _    | _                    | V    |

| V <sub>IL</sub>       | LOW-level input voltage           | [2]                                  | 2.7                 | _    | _    | 0.4                  | V    |

|                       |                                   |                                      | 5.5                 | _    | -    | 0.5                  | V    |

| V <sub>IH</sub>       | HIGH-level input voltage          | [2]                                  | 2.7                 | 1.2  | _    | _                    | V    |

|                       |                                   |                                      | 5.5                 | 2.0  | _    | _                    | V    |

| V <sub>Sxx(hys)</sub> | Input Hysteresis                  | [2]                                  | 2.7                 | 80   | _    | -                    | mV   |

|                       |                                   |                                      | 5.5                 | 200  | _    | -                    | mV   |

| IIL                   | Input low leakage current         | $V_{Sxx} = V_{DD}$                   |                     | _    | -    | ±0.1                 | μΑ   |

| I <sub>OL</sub>       | Output low sink current           | V <sub>Sxxin</sub> < V <sub>IL</sub> |                     | 30   | -    | _                    | mA   |

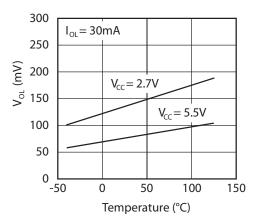

| V <sub>OL</sub>       | Output low voltage                | I <sub>OL</sub> = 30mA               | 2.7                 | _    | 110  | 300                  | mV   |

|                       |                                   |                                      | 5.5                 | _    | 80   | 250                  | mV   |

## IES5507

Buffered 4-Channel 2-Wire Bus Switch

| SYMBOL                 | DADAMETED                       | CONDITIONS                        | CONDITIONS          |      |      |      |      |

|------------------------|---------------------------------|-----------------------------------|---------------------|------|------|------|------|

|                        | PARAMETER                       | OTHER                             | V <sub>DD</sub> (V) | MIN. | TYP. | MAX. | UNIT |

| RESET                  |                                 |                                   |                     |      |      |      |      |

| V <sub>RST(hi)</sub>   | HIGH-level input voltage        |                                   | 2.7                 | 2.0  | _    | _    | V    |

|                        |                                 |                                   | 5.5                 | 4.8  | -    | _    | V    |

| V <sub>RST(lo)</sub>   | LOW-level input voltage         |                                   | 2.7                 | _    | _    | 650  | mV   |

|                        |                                 |                                   | 5.5                 | -    | _    | 900  | mV   |

| V <sub>RST(hys)</sub>  | RESET Hysteresis                |                                   | 2.7                 | 100  | _    | _    | mV   |

|                        |                                 |                                   | 5.5                 | 200  | _    | -    | mV   |

| I <sub>RST</sub>       | Input leakage current           | $V_{RST} = V_{DD}$                | $V_{RST} = V_{DD}$  |      | -    | ±0.1 | μΑ   |

| t <sub>w-RST(lo)</sub> | LOW-level reset time            | $V_{RST} < V_{IL(RST)}$ [1]       |                     | -    | 25   | -    | ns   |

| t <sub>RST</sub>       | Reset (and POR) time            | from $V_{RST} > V_{IH(RST)}$      |                     | _    | 250  | 500  | ns   |

| Address A              | A0, A1, A2                      |                                   |                     |      |      |      |      |

| V <sub>A20(hi)</sub>   | HIGH-level input voltage        |                                   | 2.7                 | 1.7  | _    | -    | V    |

|                        |                                 |                                   | 5.5                 | 3.5  | _    | _    | V    |

| V <sub>A20(lo)</sub>   | LOW-level input voltage         |                                   | 2.7                 | _    | _    | 0.7  | V    |

|                        |                                 |                                   | 5.5                 | _    | _    | 1.5  | V    |

| I <sub>A20</sub>       | Input leakage current           | $V_{A20} = V_{DD}$                |                     | -    | _    | ±0.1 | μA   |

| Timing Ch              | haracteristics (refer Figure 7) |                                   |                     |      |      | •    |      |

| td                     | Response Delay                  | R <sub>Sxx(PULLUP)</sub> = 2000hm | 2.7                 | _    | 100  | _    | ns   |

|                        |                                 |                                   | 5.5                 | _    | 70   | -    | ns   |

| tf                     | Fall Time                       | R <sub>Sxx(PULLUP)</sub> = 2000hm |                     | _    | 16   | _    | ns   |

#### Notes

[1] Guaranteed by design, not subject to test.

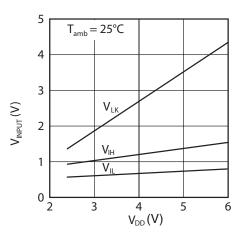

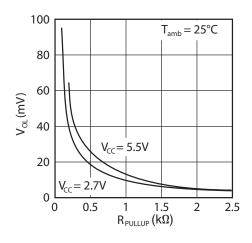

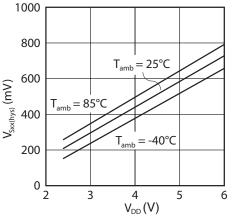

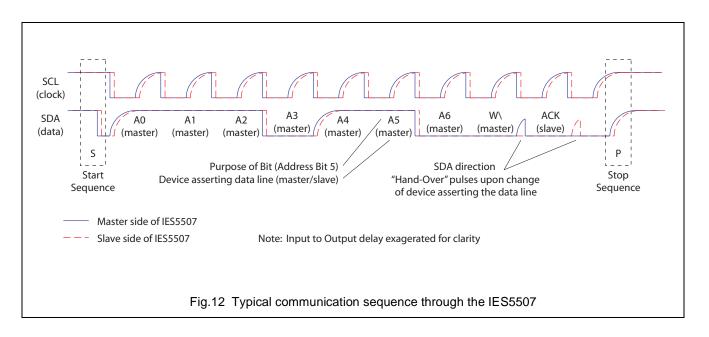

[2] Supply voltage dependant. Refer graphs for typical trend.

Fig.7 Timing Conditions

Fig.8 Typ.Input Levels vs. Supply Voltage

Fig.10 Typical  $V_{OL}$  vs. pull-up resistance

2009 Mar 05, Revision 1.0

Fig.9 Typical V<sub>IH</sub> - V<sub>IL</sub> Hysteresis vs. Supply Voltage

### IES5507 Buffered 4-Channel 2-Wire Bus Switch

#### **10 APPLICATION INFORMATION**

#### 10.1 Design Considerations

Figure 12 shows a typical data transfer through the IES5507. The IES5507 has excellent application to extending loads and expanding the address space of slave devices. Rise times are determined simply by the side of the buffer with the slowest RC time constant.

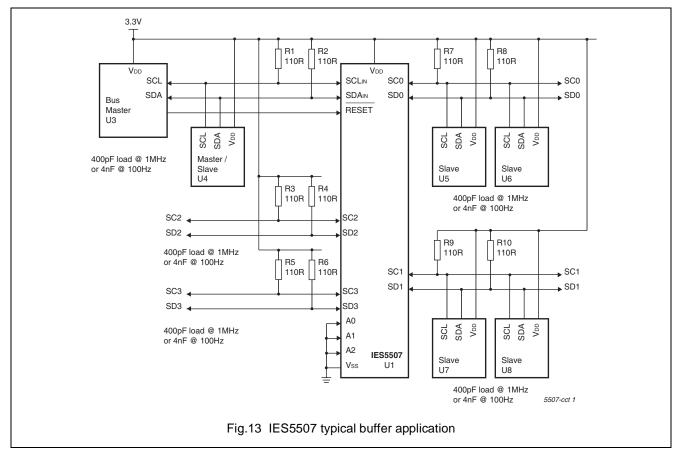

Figure 13 shows a typical application for the IES5507. Each channel can support up to the maximum permissible capacitance load, thus the maximum loading of the system can be 5x that which could be achieved with out buffering.

The channel enable function can be used to interface buses of different operating frequencies. When certain bus sections are enabled the system frequency may be limited by a bus section having a slave device specified only to 100 kHz. When that bus section is disabled, the slow slave is isolated and the remaining bus can be run at 400 kHz. The timing performance and current sinking capability will allow the IES5507 to run in excess of the 1MHz maximum limit of the I<sup>2</sup>C fast mode plus, or to run a huge 4nF of load at 100kHz.

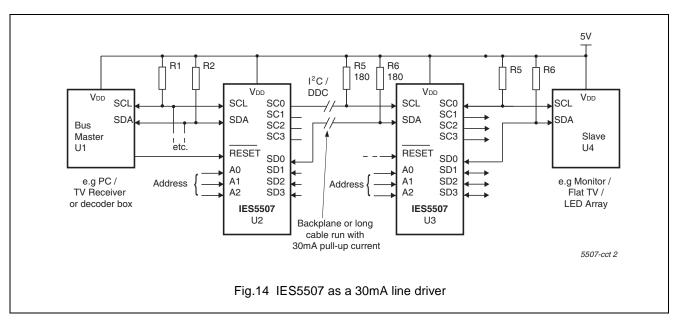

Figure 14 shows the IES5507 used as a line driver. Four such lines (only one shown) can be run from the same device. The receiving end may then again be used as a 4 way bus switch, radiating out into another four lines.

Using the address pins, this entire structure may be repeated. Thus a total of eight IES5507 "line drivers" may be connected to a single bus master (U1), allowing for 32 (8x4) long distance bus pairs to be driven from the one I<sup>2</sup>C port.

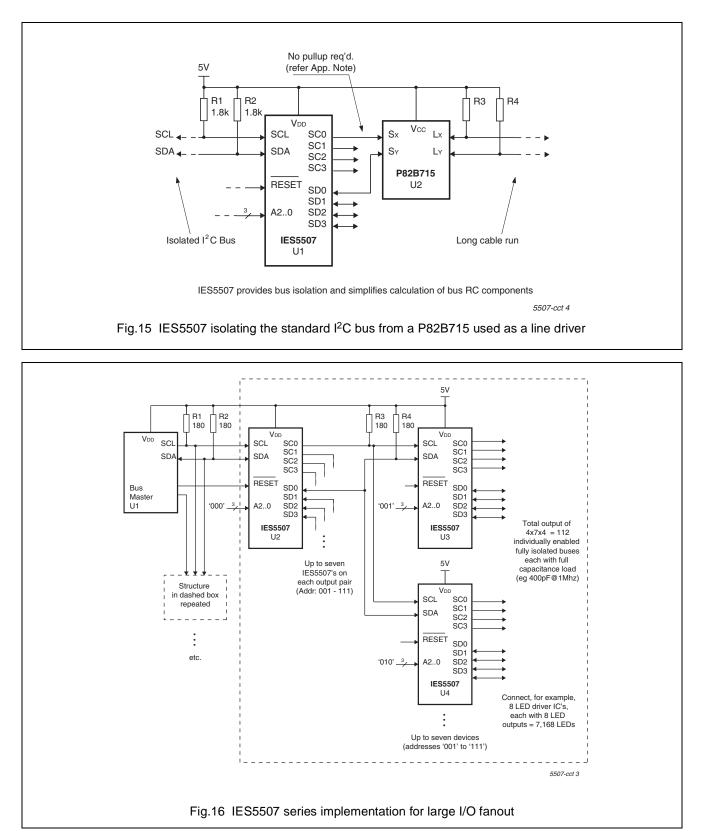

Figure 15 shows an alternative solution. In this case, the IES5507 is used to isolate a P82B715 I<sup>2</sup>C bus extender. The P82B715 provides a "10x impedance transformation"<sup>(1)</sup> but does not isolate either side of the buffer. Using the IES5507 to isolate this device greatly simplifies calculation of the pull-ups and increases the total system loading capability in extender applications. Of course, it is possible to connect a P82B715 to each of the four channels, thus allowing a significant drive capability.

The IES5507 may also be driven in series. Figure 16 shows this configuration. In this scenario, each of the four outputs of the first device (U2) has six more IES5507's connected to it. Each of those six devices has four outputs, thus giving 4x7x4 = 112 outputs. If the RESET pin on U2 was also driven from the master, it would be possible to reproduce this entire structure multiple times, giving a truly massive address space capability. Such a configuration may be applied to situations such as display drivers.

(1) P82B715 I2C bus extender datasheet, 2 December 2003, Philips Electronics N.V.

# IES5507

**Buffered 4-Channel 2-Wire Bus Switch**

#### **10.2** Application circuits

**Buffered 4-Channel 2-Wire Bus Switch**

**11 ORDERING INFORMATION**

| TYPE      | PACKAGE |                                                            |          |       |

|-----------|---------|------------------------------------------------------------|----------|-------|

| NUMBER    | NAME    | DESCRIPTION                                                | VERSION  | ROHS  |

| IES5507 T | SO16    | plastic small outline package; 16 leads; body width 3.9 mm | SOT162-1 | Yes 🗭 |

Other package options are available - contact Hendon Semiconductors for details. For more information on packages, please refer to the document "Integrated Circuit Packaging and Soldering Information" on the Hendon Semiconductors web site.

#### 12 ESD CAUTION

Electrostatic Discharge (ESD) sensitive device. ESD can cause permanent damage or degradation in the performance of this device. This device contains ESD protection structures aimed at minimising the impact of ESD. However, it is the users responsibility to ensure that proper ESD precautions are observed during the handling, placement and operation of this device.

#### **13 DOCUMENT HISTORY**

| REVISION | DATE     | DESCRIPTION     |

|----------|----------|-----------------|

| 1.0      | 20090304 | Product Release |

|          |          |                 |

|          |          |                 |

Buffered 4-Channel 2-Wire Bus Switch

#### 14 DEFINITIONS

| Data sheet status                                           |                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Engineering sample information                              | This contains draft information describing an engineering sample provided to demonstrate possible function and feasibility. Engineering samples have no guarantee that they will perform as described in all details.                                                                                                                            |

| Objective specification                                     | This data sheet contains target or goal specifications for product development.<br>Engineering samples have no guarantee that they will function as described in all details.                                                                                                                                                                    |

| Preliminary specification                                   | This data sheet contains preliminary data; supplementary data may be published later.<br>Products to this data may not yet have been fully tested, and their performance fully documented.                                                                                                                                                       |

| Product specification                                       | This data sheet contains final product specifications.                                                                                                                                                                                                                                                                                           |

| Limiting values                                             |                                                                                                                                                                                                                                                                                                                                                  |

| more of the limiting values<br>of the device at these or at | accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or<br>may cause permanent damage to the device. These are stress ratings only and operation<br>any other conditions above those given in the Characteristics sections of the specification<br>limiting values for extended periods may affect device reliability. |

| Application information                                     |                                                                                                                                                                                                                                                                                                                                                  |

Where application information is given, it is advisory and does not form part of the specification.

#### **15 COMPANY INFORMATION**

HENDON SEMICONDUCTORS PTY. LTD. ABN 17 080 879 616

Postal address:

Hendon Semiconductors PO Box 2226 Port Adelaide SA 5015 AUSTRALIA

| Telephone:      | +61 8 8348 5200                                    |

|-----------------|----------------------------------------------------|

| Facsimile:      | +61 8 8243 1048                                    |

| World Wide Web: | www.hendonsemiconductors.com<br>www.bus-buffer.com |

| Email:          | hendon.info@hendonsemiconductors.com               |

Street Address:

Hendon Semiconductors 1 Butler Drive Hendon SA 5014 AUSTRALIA

#### 16 DISCLAIMER

Hendon Semiconductors Pty. Ltd. ABN 17 080 879 616 ("Hendon") reserves the right to make changes to both its products and product data without notice.

Hendon makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Hendon assume any liability arising out of the use or application of any Hendon product. Hendon specifically disclaims any and all liability, including without limitation incidental or consequential damages. It is the responsibility of the customer to ensure that in all respects the application in which Hendon goods are used is suited to the purpose of the end user.

Typical performance figures, where quoted may depend on the application and therefore must be validated by the customer in each particular application. It is the responsibility of customers to ensure that any designs using Hendon products comply with good practice, applicable standards and approvals. Hendon accepts no responsibility for incorrect or non-compliant use of its products, failure to meet appropriate standards and approvals in the application of Hendon products, or for the correct engineering choice of other connected components, layout and operation of Hendon products.

Any customer purchasing or using Hendon product(s) for an unintended or unauthorised application shall indemnify and hold Hendon and its officers, employees, related companies, affiliates and distributors harmless against all claims, costs, damages, expenses, and reasonable legal fees arising out of, directly or indirectly, any claim of loss, personal injury or death associated with such unintended or unauthorised use, even if such claim alleges that Hendon was negligent regarding the design or manufacture of the relevant product(s).

#### Life Support Applications

Products of Hendon Semiconductors (Hendon) are not designed for use in life support appliances, devices or systems, where malfunction can result in personal injury. Customers using or selling Hendon products for use in such applications do so at their own risk and agree to fully indemnify Hendon for any damages resulting from such improper use or sale.