# PI7C21P100B 2-PORT PCI-X TO PCI-X BRIDGE

Revision 1.02

3545 NORTH FIRST STREET SAN JOSE, CA 95134 PH: 1-877-PERICOM (1-877-737-4266) FAX: 1-408-435-1100 INTERNET: HTTP://WWW.PERICOM.COM

#### LIFE SUPPORT POLICY

Pericom Semiconductor Corporation's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of PSC.

- 1) Life support devices or system are devices or systems which:

- a) Are intended for surgical implant into the body or

- b) Support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2) A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. Pericom Semiconductor Corporation reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. Pericom Semiconductor does not assume any responsibility for use of any circuitry described other than the circuitry embodied in a Pericom Semiconductor product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Pericom Semiconductor Corporation.

All other trademarks are of their respective companies.

## **REVISION HISTORY**

| Date       | Revision Number | Description                                     |  |

|------------|-----------------|-------------------------------------------------|--|

| 11/05/2004 | 1.00            | First Release of Data Sheet                     |  |

| 06/10/2005 | 1.01            | Corrected package outline drawing in section 11 |  |

| 11/21/2005 | 1.02            | Removed "Advance Information" from the title    |  |

This page intentionally left blank.

## TABLE OF CONTENTS

| 1 | DESCRIPTION                                              | 9  |

|---|----------------------------------------------------------|----|

| 2 | FEATURES                                                 | 9  |

| 3 | SIGNAL DEFINITIONS                                       | 10 |

|   | 3.1 SIGNAL TYPES                                         | 10 |

|   | 3.2 SIGNALS                                              | 10 |

|   | 3.2.1 PRIMARY BUS INTERFACE SIGNALS                      | 10 |

|   | 3.2.2 PRIMARY BUS INTERFACE SIGNALS – 64-BIT EXTENSION   | 12 |

|   | 3.2.3 SECONDARY BUS INTERFACE SIGNALS                    |    |

|   | 3.2.4 SECONDARY BUS INTERFACE SIGNALS – 64-BIT EXTENSION |    |

|   | 3.2.5 CLOCK SIGNALS                                      |    |

|   | 3.2.6 STRAPPING PINS AND MISCELLANEOUS SIGNALS           |    |

|   | 3.2.7 JTAG BOUNDARY SCAN AND TEST SIGNALS                |    |

|   | 3.2.8 TEST SIGNALS                                       |    |

|   | 3.2.9 POWER AND GROUND SIGNALS                           |    |

|   | 3.3 PIN LIST                                             |    |

| 4 | PCI BUS OPERATION                                        | 22 |

|   | 4.1 TYPES OF TRANSACTIONS                                | 22 |

|   | 4.2 WRITE TRANSACTIONS                                   |    |

|   | 4.2.1 MEMORY WRITE TRANSACTIONS                          |    |

|   | 4.2.1.1 PCI-X TO PCI-X                                   | 24 |

|   | 4.2.1.2 PCI TO PCI                                       |    |

|   | 4.2.1.3 PCI TO PCI-X                                     |    |

|   | 4.2.1.4 PCI-X TO PCI                                     |    |

|   | 4.2.2 DELAYED/SPLIT WRITE TRANSACTIONS                   |    |

|   | 4.2.3 IMMEDIATE WRITE TRANSACTIONS                       |    |

|   | 4.3 READ TRANSACTIONS                                    |    |

|   | 4.3.1 MEMORY READ TRANSACTIONS                           |    |

|   | 4.3.1.1 PCI-X TO PCI-X                                   |    |

|   | 4.3.1.2 PCI TO PCI                                       |    |

|   | 4.3.1.4 PCI-X TO PCI                                     |    |

|   | 4.3.2 I/O READ                                           |    |

|   | 4.3.3 CONFIGURATION READ                                 |    |

|   | 4.3.3.1 TYPE 1 CONFIGURATION READ                        |    |

|   | 4.3.3.2 TYPE 0 CONFIGURATION READ                        |    |

|   | 4.3.4 NON-PREFETCHABLE AND DWORD READS                   |    |

|   | 4.3.5 PREFETCHABLE READS                                 |    |

|   | 4.3.5.1 PCI-X TO PCI-X AND PCI-X TO PCI                  | 28 |

|   | 4.3.5.2 PCI TO PCI                                       | 29 |

|   | 4.3.5.3 PCI TO PCI-X                                     |    |

|   | 4.3.6 DYNAMIC PREFETCH (CONVENTIONAL PCI MODE ONLY)      |    |

|   | 4.4 CONFIGURATION TRANSACTIONS                           |    |

|   | 4.4.1 TYPE 0 ACCESS TO PI7C21P100B                       |    |

|   | 4.4.2 TYPE 1 TO TYPE 0 CONVERSION                        |    |

|   | 4.4.3 TYPE 1 TO TYPE 1 FORWARDING                        |    |

|   | 4.4.4 SPECIAL CYCLES                                     |    |

| 5 | TRANSACTION ORDERING                                     | 33 |

|   | 5.1 GENERAL ORDERING GUIDELINES                          | 33 |

|   | 5.2              | ORDERING RULES                                       | . 33 |

|---|------------------|------------------------------------------------------|------|

| 6 | CLO              | CKS                                                  | . 35 |

|   |                  | PRIMARY AND SECONDARY CLOCK INPUTS                   |      |

|   |                  | CLOCK JITTER                                         |      |

|   | 6.3              | MODE AND CLOCK FREQUENCY DETERMINATION               |      |

|   | 6.3.1            | PRIMARY BUS                                          |      |

|   | 6.3.2            | SECONDARY BUS                                        |      |

|   | 6.3.3            | CLOCK STABILITY                                      |      |

|   | 6.3.4            | DRIVER IMPEDANCE SELECTION                           | . 37 |

| 7 | RESE             | Т                                                    | . 38 |

|   |                  | PRIMARY INTERFACE RESET                              |      |

|   |                  | SECONDARY INTERFACE RESET                            |      |

|   |                  | BUS PARKING & BUS WIDTH DETERMINATION                |      |

|   |                  | SECONDARY DEVICE MASKING                             |      |

|   |                  | ADDRESS PARITY ERRORS                                |      |

|   |                  | OPTIONAL BASE ADDRESS REGISTER                       |      |

|   |                  | OPTIONAL CONFIGURATION ACCESS FROM THE SECONDARY BUS |      |

|   | 7.8              | SHORT TERM CACHING                                   | . 41 |

| 8 | CON              | FIGURATION REGISTERS                                 | . 42 |

|   | 8.1              | CONFIGURATION REGISTER SPACE MAP                     |      |

|   | 8.1.1            | SIGNAL TYPE DEFINITION                               |      |

|   | 8.1.2            | VENDOR ID REGISTER – OFFSET 00h                      |      |

|   | 8.1.3            | DEVICE ID REGISTER – OFFSET 00h                      |      |

|   | 8.1.4            | COMMAND REGISTER – OFFSET 04h                        |      |

|   | 8.1.5            | PRIMARY STATUS REGISTER – OFFSET 04h                 |      |

|   | 8.1.6            | REVISION ID REGISTER – OFFSET 08h                    |      |

|   | 8.1.7            | CLASS CODE REGISTER – OFFSET 08h                     |      |

|   | 8.1.8            | CACHE LINE SIZE REGISTER – OFFSET OCh                |      |

|   | 8.1.9            | PRIMARY LATENCY TIMER – OFFSET OCH                   |      |

|   | 8.1.10           |                                                      |      |

|   | 8.1.11           |                                                      |      |

|   | 8.1.12<br>8.1.13 |                                                      |      |

|   | 8.1.13           |                                                      |      |

|   | 8.1.15           |                                                      |      |

|   | 8.1.16           |                                                      |      |

|   | 8.1.17           |                                                      |      |

|   | 8.1.18           |                                                      |      |

|   | 8.1.19           |                                                      |      |

|   | 8.1.20           |                                                      |      |

|   | 8.1.21           |                                                      | . 48 |

|   | 8.1.22           | MEMORY LIMIT REGISTER – OFFSET 20h                   | . 48 |

|   | 8.1.23           | PREFETCHABLE MEMORY BASE REGISTER – OFFSET 24h       | . 48 |

|   | 8.1.24           |                                                      |      |

|   | 8.1.25           |                                                      |      |

|   | 8.1.26           |                                                      |      |

|   | 8.1.27           |                                                      |      |

|   | 8.1.28           |                                                      |      |

|   | 8.1.29           |                                                      |      |

|   | 8.1.30           |                                                      |      |

|   | 8.1.31           | INTERRUPT LINE REGISTER – OFFSET 3Ch                 | . 49 |

|    | 8.1.32           | INTERRUPT PIN REGISTER – OFFSET 3Ch                                                      |    |

|----|------------------|------------------------------------------------------------------------------------------|----|

|    | 8.1.33           | BRIDGE CONTROL REGISTER – OFFSET 3Ch                                                     |    |

|    | 8.1.34           | PRIMARY DATA BUFFERING CONTROL REGISTER – OFFSET 40h                                     |    |

|    | 8.1.35           | SECONDARY DATA BUFFERING CONTROL REGISTER – OFFSET 40h                                   |    |

|    | 8.1.36           | MISCELLANEOUS CONTROL REGISTER – OFFSET 44h                                              |    |

|    | 8.1.37           | EXTENDED CHIP CONTROL REGISTER 1 – OFFSET 48h                                            |    |

|    | 8.1.38           | EXTENDED CHIP CONTROL REGISTER 2 – OFFSET 48h                                            |    |

|    | 8.1.39           | ARBITER MODE REGISTER – OFFSET 50h                                                       |    |

|    | 8.1.40           | ARBITER ENABLE REGISTER – OFFSET 54h                                                     |    |

|    | 8.1.41           | ARBITER PRIORITY REGISTER - OFFSET 58h                                                   |    |

|    | 8.1.42           | SERR# DISABLE REGISTER – OFFSET 5Ch                                                      |    |

|    | 8.1.43           | PRIMARY RETRY COUNTER REGISTER - OFFSET 60h                                              |    |

|    | 8.1.44<br>8.1.45 | SECONDARY RETRY COUNTER REGISTER – OFFSET 64hDISCARD TIMER CONTROL REGISTER – OFFSET 68h |    |

|    |                  | RETRY AND TIMER STATUS REGISTER – OFFSET 6Ch                                             |    |

|    | 8.1.46<br>8.1.47 | OPAQUE MEMORY ENABLE REGISTER – OFFSET 70h                                               |    |

|    | 8.1.48           | OPAQUE MEMORI ENABLE REGISTER – OFFSET 70h<br>OPAQUE MEMORY BASE REGISTER – OFFSET 74h   |    |

|    | 8.1.49           | OPAQUE MEMORY LIMIT REGISTER – OFFSET 74h                                                |    |

|    | 8.1.50           | OPAQUE MEMORY BASE UPPER 32-BIT REGISTER – OFFSET 78h                                    |    |

|    | 8.1.51           | OPAQUE MEMORY LIMIT UPPER 32-BIT REGISTER – OFFSET 76h                                   |    |

|    | 8.1.52           | PCI-X CAPABILITY ID REGISTER – OFFSET 80h                                                |    |

|    | 8.1.53           | NEXT CAPABILITY POINTER REGISTER – OFFSET 80h                                            |    |

|    | 8.1.54           | PCI-X SECONDARY STATUS REGISTER – OFFSET 80h                                             |    |

|    | 8.1.55           | PCI-X BRIDGE PRIMARY STATUS REGISTER – OFFSET 84h                                        |    |

|    | 8.1.56           | SECONDARY BUS UPSTREAM SPLIT TRANSACTION REGISTER - OFFSET 88h.                          |    |

|    | 8.1.57           | PRIMARY BUS DOWNSTREAM SPLIT TRANSACTION REGISTER - OFFSET 8Ch                           | 62 |

|    | 8.1.58           | POWER MANAGEMENT ID REGISTER – OFFSET 90h                                                | 63 |

|    | 8.1.59           | NEXT CAPABILITIES POINTER REGISTER – OFFSET 90h                                          | 63 |

|    | 8.1.60           | POWER MANAGEMENT CAPABILITIES REGISTER – OFFSET 90h                                      |    |

|    | 8.1.61           | POWER MANAGEMENT CONTROL AND STATUS REGISTER – OFFSET 94h                                |    |

|    | 8.1.62           | PCI-TO-PCI BRIDGE SUPPORT EXTENSION REGISTER – OFFSET 94h                                |    |

|    | 8.1.63           | SECONDARY BUS PRIVATE DEVICE MASK REGISTER – OFFSET B0h                                  |    |

|    | 8.1.64           | MISCELLANEOUS CONTROL REGISTER 2 – OFFSET B8h                                            | 65 |

| 9  | IEEE 11          | 49.1 COMPATIBLE JTAG CONTROLLER                                                          | 66 |

|    | 9.1 INS          | STRUCTION REGISTER                                                                       | 66 |

|    |                  | PASS REGISTER                                                                            |    |

|    |                  | VICE ID REGISTER                                                                         |    |

|    | 9.4 BO           | UNDARY SCAN REGISTER                                                                     | 67 |

|    |                  | AG BOUNDARY REGISTER ORDER                                                               |    |

| 10 | ELECTI           | RICAL INFORMATION                                                                        | 75 |

|    | 10.1 MA          | AXIMUM RATINGS                                                                           | 75 |

|    |                  | SPECIFICATIONS                                                                           |    |

|    |                  | SPECIFICATIONS                                                                           |    |

|    |                  | WER CONSUMPTION                                                                          |    |

| 11 |                  | NICAL INFORMATION                                                                        |    |

|    |                  |                                                                                          |    |

| 12 | ORDER            | ING INFORMATION                                                                          | 78 |

9

## LIST OF TABLES

| TABLE 3-1 PIN LIST 304-PIN PBGA                           | 19 |

|-----------------------------------------------------------|----|

| TABLE 4-1 PCI AND PCI-X TRANSACTIONS                      | 22 |

| TABLE 4-2 WRITE TRANSACTION FORWARDING                    | 23 |

| TABLE 4-3 READ TRANSACTIN HANDLING                        | 25 |

| TABLE 4-4 DEVICE NUMBER TO IDSEL                          | 31 |

| TABLE 5-1 SUMMARY OF TRANSACTION ORDERING IN PCI MODE     | 35 |

| TABLE 5-2 SUMMARY OF TRANSACTION ORDERING IN PCI-X MODE   | 35 |

| TABLE 6-1 PROGRAMMABLE PULL-UP CIRCUIT                    | 37 |

| TABLE 6-2 DRIVER IMPEDANCE SELECTION                      | 38 |

| TABLE 7-1 DELAY TIMES FOR DE-ASSERTION OF S_RST#          | 39 |

| TABLE 7-2 DE-ASSERTION OF S_RST#                          | 39 |

| TABLE 8-1 CONFIGURATION SPACE MAP                         | 42 |

| TABLE 9-1 JTAG BOUNDARY SCAN REGISTER                     | 67 |

| TABLE 10-1 AC TIMING SPECIFICATIONS PCI-X MODE            |    |

| TABLE 10-2 AC TIMING SPECIFICATIONS CONVENTIONAL PCI MODE | 76 |

| LIST OF FIGURES                                           |    |

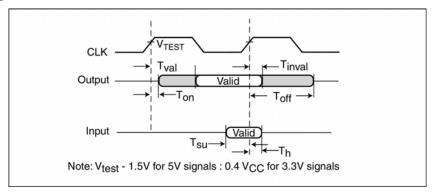

| FIGURE 10-1 PCI SIGNAL TIMING MEASUREMENTS                |    |

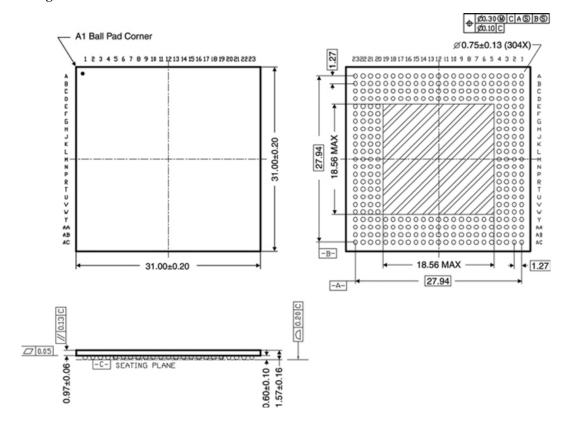

| FIGURE 11-1 PACKAGE DIAGRAM 31 X 31MM 304-PIN CSBGA       |    |

## 1 DESCRIPTION

The PI7C21P100B is a 2-port PCI-X 2.0 Bridge designed to be compliant with the *PCI-X Addendum to the Local Bus Specification* Revision 1.0a. The PI7C21P100B is able to handle 64-bit data at a maximum bus frequency of 133MHz. The PI7C21P100B is designed for high speed applications such as Ethernet, SCSI, and Fibre Channel. The PI7C21P100B may also be used for bus expansion, frequency isolations/translations, or PCI-X to PCI isolations/translations.

## 2 FEATURES

#### - INDUSTRY STANDARDS COMPLIANCE

- PCI-X Addendum to the Local Bus Specification Revision 1.0a (Mode 1 only)

- PCI Local Bus Specification Revision 2.2

- PCI-to-PCI Bridge Architecture Specification Revision 1.1

- PCI Power Management Interface Specification Revision 1.1

- Supports D0 and D3 power states

#### INTERFACE

- 3.3V signaling

- 133MHz / 64-bit operation on both buses

- Dual address cycle support

- Concurrent primary and secondary bus operation

- Primary and secondary may be run in either PCI mode or PCI-X Mode 1

- Asynchronous operation support

- Programmable internal arbiter with support for up to 6 external masters on the secondary bus

- Internal arbiter may be disabled to use an external arbiter

- IEEE 1149.1 JTAG support

#### OPERATION

- Type 0 and Type 1 configuration support

- Configuration register access from both primary and secondary buses

- 2KB of buffering for upstream memory burst read commands

- 2KB of buffering for downstream memory burst read commands

- 1KB of buffering for upstream posted memory write commands

- 1KB of buffering for downstream posted memory write commands

- Support for up to 8 active transactions in each direction

### - ADDITIONAL FEATURES

- Capabilities pointer

- Ability to define an opaque memory address

- Definable base address register

- Secondary side PCI-X device privatization

#### PACKAGING

■ 304-pin PBGA, 31 x 31 mm

## 3 SIGNAL DEFINITIONS

## 3.1 SIGNAL TYPES

| Signal Type | Description                                                                 |  |

|-------------|-----------------------------------------------------------------------------|--|

| I           | Input Only                                                                  |  |

| О           | Output Only                                                                 |  |

| P           | Power                                                                       |  |

| TS          | Tri-State bi-directional                                                    |  |

| STS         | Sustained Tri-State. Active LOW signal must be pulled HIGH for 1 cycle when |  |

|             | deasserting.                                                                |  |

| OD          | Open Drain                                                                  |  |

| IU          | Internal pull-up on signal                                                  |  |

| ID          | Internal pull-down on signal                                                |  |

## 3.2 SIGNALS

Signal names that end with "#" are active LOW.

## 3.2.1 PRIMARY BUS INTERFACE SIGNALS

| Name        | Pin #               | Type | Description                                                |

|-------------|---------------------|------|------------------------------------------------------------|

| P_AD[31:0]  | J23, M21, M22, L21, | TS   | Primary Address / Data: Multiplexed address and data       |

|             | L22, G23, K20, E23, |      | bus. Address is indicated by P_FRAME# assertion.           |

|             | K21, D23, K22, J21, |      | Write data is stable and valid when P_IRDY# is asserted    |

|             | J22, H21, H22, G21, |      | and read data is stable and valid when P_TRDY# is          |

|             | B20, G22, F20, F22, |      | asserted. Data is transferred on rising clock edges when   |

|             | D18, C19, C17, B17, |      | both P_IRDY# and P_TRDY# are asserted. During bus          |

|             | A20, C16, B16, A19, |      | idle, PI7C21P100B drives P_AD[31:0] to a valid logic       |

|             | C15, B14, C13, B13  |      | level when P_GNT# is asserted.                             |

| P_CBE[3:0]# | A15, D14, B18, A13  | TS   | Primary Command/Byte Enables: Multiplexed                  |

|             |                     |      | command field and byte enable field. During address        |

|             |                     |      | phase, the initiator drives the transaction type on these  |

|             |                     |      | pins. After that, the initiator drives the byte enables    |

|             |                     |      | during data phases. During bus idle, PI7C21P100B           |

|             |                     |      | drives P_CBE[3:0]# to a valid logic level when P_GNT#      |

|             |                     |      | is asserted.                                               |

| P_PAR       | C18                 | TS   | <b>Primary Parity.</b> P_PAR is even parity of P_AD[31:0]  |

|             |                     |      | and P_CBE[3:0] (i.e. an even number of 1's). P_PAR is      |

|             |                     |      | valid and stable one cycle after the address phase         |

|             |                     |      | (indicated by assertion of P_FRAME#) for address           |

|             |                     |      | parity. For write data phases, P_PAR is valid one clock    |

|             |                     |      | after P_IRDY# is asserted. For read data phase, P_PAR      |

|             |                     |      | is valid one clock after P_TRDY# is asserted. Signal       |

|             |                     |      | P_PAR is tri-stated one cycle after the P_AD lines are     |

|             |                     |      | tri-stated. During bus idle, PI7C21P100B drives P_PAR      |

|             |                     |      | to a valid logic level when P_GNT# is asserted.            |

| P_FRAME#    | A17                 | STS  | <b>Primary FRAME (Active LOW).</b> Driven by the           |

|             |                     |      | initiator of a transaction to indicate the beginning and   |

|             |                     |      | duration of an access. The de-assertion of P_FRAME#        |

|             |                     |      | indicates the final data phase requested by the initiator. |

|             |                     |      | Before being tri-stated, it is driven HIGH for one cycle.  |

## PI7C21P100B 2-PORT PCI-X TO PCI-X BRIDGE

| Name       | Pin # | Type | Description                                                                                                      |

|------------|-------|------|------------------------------------------------------------------------------------------------------------------|

| P IRDY#    | A16   | STS  | Primary IRDY (Active LOW). Driven by the initiator                                                               |

| _          |       |      | of a transaction to indicate its ability to complete current                                                     |

|            |       |      | data phase on the primary side. Once asserted in a data                                                          |

|            |       |      | phase, it is not de-asserted until the end of the data                                                           |

|            |       |      | phase. Before tri-stated, it is driven HIGH for one cycle.                                                       |

| P_TRDY#    | B15   | STS  | <b>Primary TRDY (Active LOW).</b> Driven by the target of                                                        |

| 1_1122111  | 310   | 515  | a transaction to indicate its ability to complete current                                                        |

|            |       |      | data phase on the primary side. Once asserted in a data                                                          |

|            |       |      | phase, it is not de-asserted until the end of the data                                                           |

|            |       |      | phase. Before tri-stated, it is driven HIGH for one cycle.                                                       |

| P DEVSEL#  | D21   | STS  | Primary Device Select (Active LOW). Asserted by the                                                              |

| 1_BE V SEE | D21   | 515  | target indicating that the device is accepting the                                                               |

|            |       |      | transaction. As a master, PI7C21P100B waits for the                                                              |

|            |       |      | assertion of this signal within 5 cycles of P_FRAME#                                                             |

|            |       |      | assertion; otherwise, terminate with master abort. Before                                                        |

|            |       |      | tri-stated, it is driven HIGH for one cycle.                                                                     |

| P_STOP#    | C4    | STS  | Primary STOP (Active LOW). Asserted by the target                                                                |

| 1_5101#    |       | 515  | indicating that the target is requesting the initiator to stop                                                   |

|            | 1     |      | the current transaction. Before tri-stated, it is driven                                                         |

|            |       |      | HIGH for one cycle.                                                                                              |

| P LOCK#    | C14   | I    | Primary LOCK (Active LOW). Asserted by an                                                                        |

| 1_LOCK#    | C14   | 1    | initiator, one clock cycle after the first address phase of a                                                    |

|            |       |      | transaction, attempting to perform an operation that may                                                         |

|            |       |      | take more than one PCI transaction to complete.                                                                  |

| P IDSEL    | B19   | I    |                                                                                                                  |

| P_IDSEL    | D19   | 1    | <b>Primary ID Select.</b> Used as a chip select line for Type 0 configuration access to PI721P100 configuration  |

|            |       |      | 8                                                                                                                |

| P PERR#    | C8    | STS  | Space.  Primary Pority France (Active LOW) Asserted when                                                         |

| P_PERK#    | Co    | 515  | <b>Primary Parity Error (Active LOW).</b> Asserted when a data parity error is detected for data received on the |

|            |       |      |                                                                                                                  |

|            |       |      | primary interface. Before being tri-stated, it is driven                                                         |

| D CEDD#    | D4    | OD   | HIGH for one cycle.                                                                                              |

| P_SERR#    | B4    | OD   | Primary System Error (Active LOW). Can be driven                                                                 |

|            |       |      | LOW by any device to indicate a system error condition.                                                          |

|            |       |      | PI7C21P100B drives this pin on:                                                                                  |

|            |       |      | Address parity error                                                                                             |

|            |       |      | Posted write data parity error on target bus                                                                     |

|            |       |      | <ul> <li>Secondary S_SERR# asserted</li> <li>Master abort during posted write transaction</li> </ul>             |

|            |       |      | Master abort during posted write transaction                                                                     |

|            |       |      | Target abort during posted write transaction                                                                     |

|            |       |      | Posted write transaction discarded     Delayed write request discarded                                           |

|            |       |      | Belayea write request discarded                                                                                  |

|            |       |      | Delayed read request discarded     Delayed transaction master timeout                                            |

|            |       |      | Belayed transaction master timeout                                                                               |

|            | 1     |      | This signal requires an external pull-up resistor for                                                            |

| D DEO#     | D21   | TO   | proper operation.                                                                                                |

| P_REQ#     | B21   | TS   | Primary Request (Active LOW): This is asserted by                                                                |

|            | 1     |      | PI7C21P100B to indicate that it wants to start a                                                                 |

|            |       |      | transaction on the primary bus. PI7C21P100B de-asserts                                                           |

|            | 1     |      | this pin for at least 2 PCI clock cycles before asserting it                                                     |

| D. CNIT!   | C20   | *    | again.                                                                                                           |

| P_GNT#     | C20   | I    | Primary Grant (Active LOW): When asserted,                                                                       |

|            | 1     |      | PI7C21P100B can access the primary bus. During idle                                                              |

|            | 1     |      | and P_GNT# asserted, PI7C21P100B will drive P_AD,                                                                |

|            |       |      | P_CBE, and P_PAR to valid logic levels.                                                                          |

| P_RST#     | E22   | I    | <b>Primary RESET (Active LOW):</b> When P_RESET# is                                                              |

|            | 1     |      | active, all PCI signals should be asynchronously tri-                                                            |

|            |       |      | stated.                                                                                                          |

## 3.2.2 PRIMARY BUS INTERFACE SIGNALS – 64-BIT EXTENSION

| Name        | Pin #                                                                                                                                                | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P_AD[63:32] | B11, D10, C10, A4,<br>B10, C9, B9, A3, B8,<br>B3, C7, B7, D6, B6,<br>B5, C2, D2, F4, E3,<br>F3, B1, F2, G3, H3,<br>H2, E1, J3, G1, H1,<br>J2, J1, L1 | TS   | Primary Upper 32-bit Address / Data: Multiplexed address and data bus providing an additional 32 bits to the primary. When a dual address command is used and P_REQ64# is asserted, the initiator drives the upper 32 bits of the 64-bit address. Otherwise, these bits are undefined and driven to valid logic levels. During the data phase of a transaction, the initiator drives the upper 32 bits of the 64-bit write data, or the target drives the upper 32 bits of the 64-bit read data, when P_REQ64# and P_ACK64# are both asserted. Otherwise, these bits are pulled up to a valid logic level through external resistors.                                                                                                                                                                                                                                                                         |

| P_CBE[7:4]# | A7, B12, C11, A5                                                                                                                                     | TS   | Primary Upper 32-bit Command/Byte Enables: Multiplexed command field and byte enable field. During address phase, when the dual address command is used and P_REQ64# is asserted, the initiator drives the transaction type on these pins. Otherwise, these bits are undefined, and the initiator drives a valid logic level onto the pins. For read and write transactions, the initiator drives these bits for the P_AD[63:32] data bits when P_REQ64# and P_ACK64# are both asserted. When not driven, these bits are pulled up to a valid logic level through external resistors.                                                                                                                                                                                                                                                                                                                         |

| P_PAR64     | A9                                                                                                                                                   | TS   | Primary Upper 32-bit Parity: P_PAR64 carries the even parity of P_AD[63:32] and P_CBE[7:4] for both address and data phases. P_PAR64 is driven by the initiator and is valid 1 cycle after the first address phase when a dual address command is used and P_REQ64# is asserted. P_PAR64 is valid 1 clock cycle after the second address phase of a dual address transaction when P_REQ64# is asserted. P_PAR64 is valid 1 cycle after valid data is driven when both P_REQ64# and P_ACK64# are asserted for that data phase. P_PAR64 is driven by the device driving read or write data 1 cycle after the P_AD lines are driven. P_PAR64 is tri-stated 1 cycle after the P_AD lines are tri-stated. Devices receive data sample P_PAR64 as an input to check for possible parity errors during 64-bit transactions. When not driven, P_PAR64 is pulled up to a valid logic level through external resistors. |

| P_REQ64#    | C12                                                                                                                                                  | STS  | Primary 64-bit Transfer Request: P_REQ64# is asserted by the initiator to indicate that the initiator is requesting a 64-bit data transfer. P_REQ64# has the same timing as P_FRAME#. When P_REQ64# is asserted LOW during reset, a 64-bit data path is supported. When P_REQ64# is HIGH during reset, PI7C21P100B drives P_AD[63:32], P_CBE[7:4], and P_PAR64 to valid logic levels. When deasserting, P_REQ64# is driven HIGH for 1 cycle and then sustained by an external pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                               |

| P_ACK64#    | A2                                                                                                                                                   | STS  | Primary 64-bit Transfer Acknowledge: P_ACK64# is asserted by the target only when P_REQ64# is asserted by the initiator to indicate the target's ability to transfer data using 64 bits. P_ACK64# has the same timing as P_DEVSEL#. When deasserting, P_ACK64# is driven HIGH for 1 cycle and then is sustained by an external pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## 3.2.3 SECONDARY BUS INTERFACE SIGNALS

| Name        | Pin #               | Type | Description                                                                                              |

|-------------|---------------------|------|----------------------------------------------------------------------------------------------------------|

| S_AD[31:0]  | N22, N21, P22, P21, | TS   | Secondary Address/Data: Multiplexed address and data                                                     |

|             | M23, P20, N23, R22, |      | bus. Address is indicated by S_FRAME# assertion.                                                         |

|             | T23, R21, W23, T22, |      | Write data is stable and valid when S_IRDY# is asserted                                                  |

|             | U22, U21, V22, V21, |      | and read data is stable and valid when S_IRDY# is                                                        |

|             | W21, V20, AA20,     |      | asserted. Data is transferred on rising clock edges when                                                 |

|             | AB18, Y18, AA16,    |      | both S_IRDY# and S_TRDY# are asserted. During bus                                                        |

|             | AB15, AC17, AA13,   |      | idle, PI7C21P100B drives S_AD[31:0] to a valid logic                                                     |

|             | AA12, AC15, AB11,   |      | level when the bridge is granted the bus.                                                                |

|             | AC11, AC9, AB9,     |      |                                                                                                          |

|             | AA9                 |      |                                                                                                          |

| S_CBE[3:0]# | AA15, AB14, AB16,   | TS   | Secondary Command/Byte Enables: Multiplexed                                                              |

|             | AB12                |      | command field and byte enable field. During address                                                      |

|             |                     |      | phase, the initiator drives the transaction type on these                                                |

|             |                     |      | pins. The initiator then drives the byte enables during                                                  |

|             |                     |      | data phases. During bus idle, PI7C21P100B drives                                                         |

|             |                     |      | S_CBE[3:0] to a valid logic level when the bridge is                                                     |

| C DAD       | A A 17              | TC   | granted the bus.                                                                                         |

| S_PAR       | AA17                | TS   | Secondary Parity: S_PAR is an even parity of                                                             |

|             |                     |      | S_AD[31:0] and S_CBE[3:0] (i.e. an even number of 1's). S_PAR is valid and stable one cycle after the    |

|             |                     |      | address phase (indicated by assertion of S FRAME#) for                                                   |

|             |                     |      | address parity. For write data phases, S PAR is valid                                                    |

|             |                     |      | one clock after S IRDY# is asserted. For read data                                                       |

|             |                     |      | phase, S PAR is valid one clock after S TRDY# is                                                         |

|             |                     |      | asserted. Signal S PAR is tri-stated one cycle after the                                                 |

|             |                     |      | S AD lines are tri-stated. During bus idle,                                                              |

|             |                     |      | PI7C21P100B drives S_PAR to a valid logic level when                                                     |

|             |                     |      | the bridge is granted the bus.                                                                           |

| S FRAME#    | AA14                | STS  | Secondary FRAME (Active LOW): Driven by the                                                              |

| _           |                     |      | initiator of a transaction to indicate the beginning and                                                 |

|             |                     |      | duration of an access. The de-assertion of S FRAME#                                                      |

|             |                     |      | indicates the final data phase requested by the initiator.                                               |

|             |                     |      | Before being tri-stated, it is driven HIGH for one cycle.                                                |

| S_IRDY#     | AC19                | STS  | Secondary IRDY (Active LOW): Driven by the                                                               |

|             |                     |      | initiator of a transaction to indicate its ability to                                                    |

|             |                     |      | complete current data phase on the secondary side. Once                                                  |

|             |                     |      | asserted in a data phase, it is not de-asserted until the end                                            |

|             |                     |      | of the data phase. Before tri-stated, it is driven HIGH                                                  |

|             |                     |      | for one cycle.                                                                                           |

| S_TRDY#     | Y14                 | STS  | Secondary TRDY (Active LOW): Driven by the target                                                        |

|             |                     |      | of a transaction to indicate its ability to complete current                                             |

|             |                     |      | data phase on the secondary side. Once asserted in a                                                     |

|             |                     |      | data phase, it is not de-asserted until the end of the data                                              |

| C DEVICE! " | A C21               | OTO  | phase. Before tri-stated, it is driven HIGH for one cycle.                                               |

| S_DEVSEL#   | AC21                | STS  | Secondary Device Select (Active LOW): Asserted by                                                        |

|             |                     |      | the target indicating that the device is accepting the                                                   |

|             |                     |      | transaction. As a master, PI7C21P100B waits for the assertion of this signal within 5 cycles of S_FRAME# |

|             |                     |      | assertion; otherwise, terminate with master abort. Before                                                |

|             |                     |      | tri-stated, it is driven HIGH for one cycle.                                                             |

| S_STOP#     | AB20                | STS  | Secondary STOP (Active LOW): Asserted by the                                                             |

| 5_5101#     | ADZV                | 515  | target indicating that the target is requesting the initiator                                            |

|             |                     |      | to stop the current transaction. Before tri-stated, it is                                                |

|             |                     |      | driven HIGH for one cycle.                                                                               |

| S LOCK#     | AC20                | STS  | Secondary LOCK (Active LOW): Asserted by an                                                              |

| J_LOCK#     | 11020               | 515  | initiator, one clock cycle after the first address phase of a                                            |

|             |                     |      | transaction, when it is propagating a locked transaction                                                 |

|             |                     |      | downstream. PI7C21P100B does not propagate locked                                                        |

|             |                     |      | transactions upstream.                                                                                   |

| L           | ı                   |      | amonoutin aponoum.                                                                                       |

### PI7C21P100B 2-PORT PCI-X TO PCI-X BRIDGE

| Name         | Pin #              | Type | Description                                                |

|--------------|--------------------|------|------------------------------------------------------------|

| S PERR#      | AB17               | STS  | Secondary Parity Error (Active LOW): Asserted              |

| _            |                    |      | when a data parity error is detected for data received on  |

|              |                    |      | the secondary interface. Before being tri-stated, it is    |

|              |                    |      | driven HIGH for one cycle.                                 |

| S SERR#      | AB19               | I    | Secondary System Error (Active LOW): Can be                |

| _            |                    |      | driven LOW by any device to indicate a system error        |

|              |                    |      | condition.                                                 |

| S_REQ[6:2]#  | AC3, AB5, AB3,     | I    | Secondary Request (Active LOW): This is asserted by        |

|              | W2, AA2            |      | an external device to indicate that it wants to start a    |

|              |                    |      | transaction on the secondary bus. The input is externally  |

|              |                    |      | pulled up through a resistor to VDD.                       |

| S_REQ[1]#    | AA23               | I    | Secondary Request (Active LOW):                            |

|              |                    |      | When the internal arbiter is enabled, this is asserted by  |

|              |                    |      | an external device to indicate that it wants to start a    |

|              |                    |      | transaction on the secondary bus. The input is externally  |

|              |                    |      | pulled up through a resistor to VDD.                       |

|              |                    |      | When the internal arbiter is disabled, this is used by     |

|              |                    |      | PI7C21P100B as its GNT input.                              |

| S GNT[6:2]#  | AC4, AB4, AC5, Y2, | TS   | Secondary Grant (Active LOW): PI7C21P100B                  |

| 5_6111[0.2]# | AB1                | 15   | asserts these pins to allow external masters to access the |

|              |                    |      | secondary bus. PI7C21P100B de-asserts these pins for       |

|              |                    |      | at least 2 PCI clock cycles before asserting it again.     |

|              |                    |      | During idle and S GNT# deasserted, PI7C21P100B will        |

|              |                    |      | drive S_AD, S_CBE, and S_PAR.                              |

| S GNT[1]#    | AA19               | TS   | Secondary Grant (Active LOW):                              |

| ,            |                    |      | When the internal arbiter is enabled, PI7C21P100B          |

|              |                    |      | asserts this pin to allow external masters to access the   |

|              |                    |      | secondary bus. PI7C21P100B de-asserts this pin for at      |

|              |                    |      | least 2 PCI clock cycles before asserting it again.        |

|              |                    |      | During idle and S_GNT# deasserted, PI7C21P100B will        |

|              |                    |      | drive S_AD, S_CBE, and S_PAR.                              |

|              |                    |      | When the internal arbiter is disabled, this is used by     |

|              |                    |      | PI7C21P100B as its REQ output.                             |

| S RST#       | U23                | 0    | Secondary RESET (Active LOW): Asserted when any            |

| 5_10111      | 023                |      | of the following conditions are met:                       |

|              |                    |      | Signal P RESET# is asserted.                               |

|              |                    |      | Secondary reset bit in bridge control register in          |

|              |                    |      | configuration space is set.                                |

|              |                    |      | 3. The chip reset bit in the chip control register in      |

|              |                    |      | configuration space is set.                                |

|              |                    |      | When asserted, all control signals are tri-stated and      |

|              |                    |      | zeroes are driven on S AD, S CBE, S PAR, and               |

|              |                    |      | S_PAR64.                                                   |

## 3.2.4 SECONDARY BUS INTERFACE SIGNALS – 64-BIT EXTENSION

| Name        | Pin #               | Type | Description                                            |

|-------------|---------------------|------|--------------------------------------------------------|

| S_AD[63:32] | AB8, AB7, AA7,      | TS   | Secondary Upper 32-bit Address/Data: Multiplexed       |

|             | AB6, AA6, AA5, Y6,  |      | address and data bus. Address is indicated by          |

|             | Y3, V2, V4, U2, U3, |      | S_FRAME# assertion. Write data is stable and valid     |

|             | T2, T3, R2, R3, P2, |      | when S_IRDY# is asserted and read data is stable and   |

|             | Y1, P3, W1, P4, U1, |      | valid when S_IRDY# is asserted. Data is transferred on |

|             | N2, N3, M2, M3, R1, |      | rising clock edges when both S_IRDY# and S_TRDY#       |

|             | L2, L3, K2, K3, K4  |      | are asserted. During bus idle, PI7C21P100B drives      |

|             |                     |      | S_AD to a valid logic level when the bridge is granted |

|             |                     |      | the bus.                                               |

## PI7C21P100B 2-PORT PCI-X TO PCI-X BRIDGE

| Name        | Pin #                   | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|-------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S_CBE[7:4]# | Y10, AB10, AA11,<br>AC8 | TS   | Secondary Upper 32-bit Command/Byte Enables: Multiplexed command field and byte enable field. During address phase, the initiator drives the transaction type on these pins. The initiator then drives the byte enables during data phases. During bus idle, PI7C21P100B drives S_CBE[7:0] to a valid logic level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| S_PAR64     | AA10                    | TS   | when the bridge is granted the bus.  Secondary Upper 32-bit Parity: S_PAR64 carries the even parity of S_AD[63:32] and S_CBE[7:4] for both address and data phases. S_PAR64 is driven by the initiator and is valid 1 cycle after the first address phase when a dual address command is used and S_REQ64# is asserted. S_PAR64 is valid 1 clock cycle after the second address phase of a dual address transaction when S_REQ64# is asserted. S_PAR64 is valid 1 cycle after valid data is driven when both S_REQ64# and S_ACK64# are asserted for that data phase. S_PAR64 is driven by the device driving read or write data 1 cycle after the S_AD lines are driven. S_PAR64 is tri-stated 1 cycle after the S_AD lines are tri-stated. Devices receive data sample S_PAR64 as an input to check for possible parity errors during 64-bit transactions. When not driven, S_PAR64 is pulled up to a valid logic level through external resistors. |

| S_REQ64#    | AB13                    | STS  | Secondary 64-bit Transfer Request: S_REQ64# is asserted by the initiator to indicate that the initiator is requesting a 64-bit data transfer. S_REQ64# has the same timing as S_FRAME#. When S_REQ64# is asserted LOW during reset, a 64-bit data path is supported. When S_REQ64# is HIGH during reset, PI7C21P100B drives S_AD[63:32], S_CBE[7:4], and S_PAR64 to valid logic levels. When deasserting, S_REQ64# is driven to a deasserted state for 1 cycle and then sustained by an external pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| S_ACK64#    | AA8                     | STS  | Secondary 64-bit Transfer Acknowledge: S_ACK64# is asserted by the target only when S_REQ64# is asserted by the initiator to indicate the target's ability to transfer data using 64 bits. S_ACK64# has the same timing as S_DEVSEL#. When deasserting, S_ACK64# is driven to a deasserted state for 1 cycle and then is sustained by an external pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## 3.2.5 CLOCK SIGNALS

| Name  | Pin # | Type | Description                                               |

|-------|-------|------|-----------------------------------------------------------|

| P_CLK | E21   | I    | Primary Clock Input: Provides timing for all              |

|       |       |      | transactions on the primary interface. For conventional   |

|       |       |      | PCI mode, the input clock frequency may be between 0      |

|       |       |      | - 66MHz. In PCI-X mode, the input clock frequency         |

|       |       |      | may be between 66 – 133MHz. See Section 6 for             |

|       |       |      | limitations.                                              |

| S_CLK | AB23  | I    | Secondary Clock Input: Provides timing for all            |

| _     |       |      | transactions on the secondary interface. For conventional |

|       |       |      | PCI mode, the input clock frequency may be between 0      |

|       |       |      | - 66MHz. In PCI-X mode, the input clock frequency         |

|       |       |      | may be between 66 – 133MHz. See Section 6 for             |

|       |       |      | limitations. If the primary bus is running at 133MHz,     |

|       |       |      | the minimum frequency that may be supplied to S_CLK       |

|       |       |      | is 33MHz.                                                 |

## 3.2.6 STRAPPING PINS AND MISCELLANEOUS SIGNALS

| Name         | Pin # | Type | Description                                                                                                     |  |

|--------------|-------|------|-----------------------------------------------------------------------------------------------------------------|--|

| S ARB#       | T21   | I    | Internal Arbiter Enable: This pin is used by                                                                    |  |

| _            |       |      | PI7C21P100B to determine whether the secondary bus                                                              |  |

|              |       |      | uses the internal arbiter or external arbiter.                                                                  |  |

|              |       |      | 0: Enable the internal arbiter                                                                                  |  |

|              |       |      | 1: Disable the internal arbiter and use an external arbiter                                                     |  |

| S SEL100     | V3    | I    | Secondary Bus Maximum Frequency: This pin is used                                                               |  |

| S_SEETOO     | , ,   |      | to determine the maximum frequency on the secondary                                                             |  |

|              |       |      | bus when in PCI-X mode. In PCI mode, the pin has no                                                             |  |

|              |       |      | function and should not be left floating.                                                                       |  |

|              |       |      |                                                                                                                 |  |

|              |       |      | 0: Set secondary interface to 133MHz                                                                            |  |

|              |       |      | 1: Set secondary interface to 100MHz                                                                            |  |

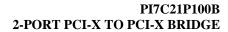

| S_PCIXCAP    | R23   | I    | Secondary Bus PCI-X Capable: This pin is used with                                                              |  |

|              |       |      | S_SEL100 to determine the frequency and mode for the                                                            |  |

|              |       |      | secondary bus. There are three conditions for this pin                                                          |  |

|              |       |      | determining the capability of the secondary bus:                                                                |  |

|              |       |      | Ground: Not capable of PCI-X mode                                                                               |  |

|              |       |      | Pull-down: PCI-X 66MHz                                                                                          |  |

|              |       |      | Not connected: PCI-X 133MHz                                                                                     |  |

| S_PCIXCAP_PU | AA1   | I    | S_PCIXCAP Pull-up Driver: This pin is used with                                                                 |  |

|              |       |      | S_PCIXAP as part of a programmable pull-up circuit to                                                           |  |

|              |       |      | determine the state of S_PCIXCAP. A 1kohm resistor                                                              |  |

|              |       |      | must be placed between this pin and S_PCIXCAP.                                                                  |  |

| S_DRVR       | AC7   | ID   | Secondary Driver Mode: This pin controls the output                                                             |  |

|              |       |      | impedance of the secondary drivers to account for the                                                           |  |

|              |       |      | number of loads on the secondary bus.                                                                           |  |

|              |       |      | 0: default impedance                                                                                            |  |

|              |       |      | 1: select alternate impedance                                                                                   |  |

|              |       |      | S T11 (26 : 1 1                                                                                                 |  |

| D DDI/D      | E2    | ID   | See Table 6-2 for impedance values.                                                                             |  |

| P_DRVR       | E2    | ID   | <b>Primary Driver Mode Control:</b> Controls the output impedance of the primary bus drivers to account for the |  |

|              |       |      | number of loads on the primary bus.                                                                             |  |

|              |       |      | named of fours of the primary ous.                                                                              |  |

|              |       |      | 0: Default impedance                                                                                            |  |

|              |       |      | 1: Select alternate impedance                                                                                   |  |

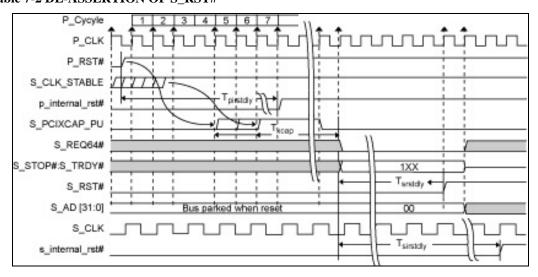

| S_CLK_STABLE | W3    | I    | S_CLK Input Stable: Determines when the S_CLK is                                                                |  |

|              |       |      | stable to resolve when S_RST# can by de-asserted.                                                               |  |

|              |       |      |                                                                                                                 |  |

|              |       |      | 0: S_CLK is not stable                                                                                          |  |

|              |       |      | 1: S_CLK is stable                                                                                              |  |

| S_IDSEL      | AA22  | I    | Initialization Device Select: S_IDSEL is used as a chip                                                         |  |

|              |       |      | select during configuration reads and writes on the                                                             |  |

|              |       |      | secondary bus. Applications that do not require access                                                          |  |

|              |       |      | to PI7C21P100B's configuration registers from the                                                               |  |

|              | Í     | İ    | secondary side should pull this pin LOW.                                                                        |  |

| CARAM DEVA  | Lyraa |   | DOLLER DESCRIPTION OF THE PROPERTY OF THE PROP |

|-------------|-------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 64BIT_DEV#  | Y22   | I | PCI-X Device Bus Width: 64BIT_DEV# sets bit 16 of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |       |   | the PCI-X Bridge Status Register to support system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |