# TISP8200HDM BUFFERED P-GATE SCR DUAL TISP8201HDM BUFFERED N-GATE SCR DUAL

### COMPLEMENTARY BUFFERED-GATE SCRS FOR DUAL POLARITY SLIC OVERVOLTAGE PROTECTION

**TISP820xHDM Overvoltage Protectors**

High Performance Protection for SLICs with +ve & -ve Battery Supplies

- **TISP8200HDM Negative Overvoltage Protector**

- Wide -20 to -110 V Programming Range

- Low +15 mA Max. Gate Triggering Current

- High -150 mA Min. Holding Current

**TISP8201HDM Positive Overvoltage Protector**

- Wide +20 to +110 V Programming Range

- Low -15 mA Max. Gate Triggering Current

- +20 mA Min. Holding Current

**Rated for International Surge Wave Shapes**

| Wave Shape | Standard         | I <sub>PPSM</sub><br>A |

|------------|------------------|------------------------|

| 2/10       | GR-1089-CORE     | 500                    |

| 10/700     | ITU-T K.20/21/45 | 150                    |

| 10/1000    | GR-1089-CORE     | 100                    |

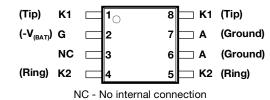

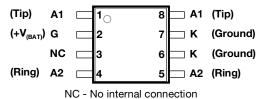

#### TISP8200HDM 8-SOIC (210 mil) Package (Top View)

Terminal typical application names shown in parenthesis

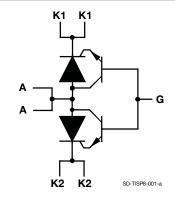

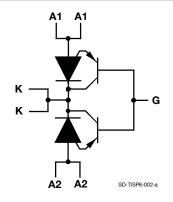

#### **TISP8200HDM Device Symbol**

#### TISP8201HDM 8-SOIC (210 mil) Package (Top View)

Terminal typical application names shown in parenthesis

#### TISP8201HDM Device Symbol

\*RoHS Directive 2002/95/EC Jan 27 2003 including Annex OCTOBER 2005 — REVISED MAY 2007 Specifications are subject to change without notice. Customers should verify actual device performance in their specific applications.

# BOURNS®

#### Description

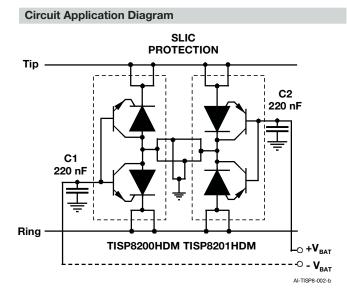

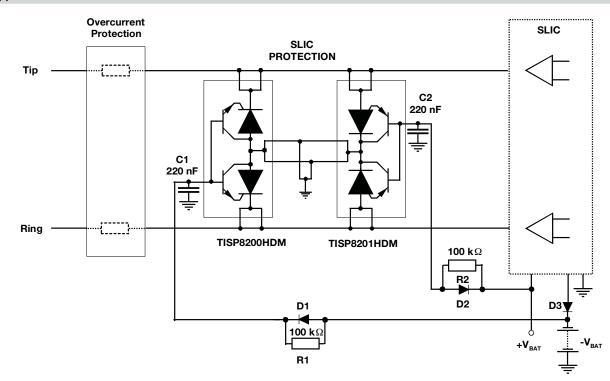

The TISP8200HDM/TISP8201HDM combination has been designed to protect dual polarity supply rail monolithic SLICs (Subscriber Line Interface Circuits) against overvoltages on the telephone line caused by lightning, a.c. power contact and induction. Protection against negative overvoltages is given by the TISP8200HDM. Protection against positive overvoltages is given by the TISP8201HDM. Both parts are in 8-SOIC (210 mil) surface mount packages.

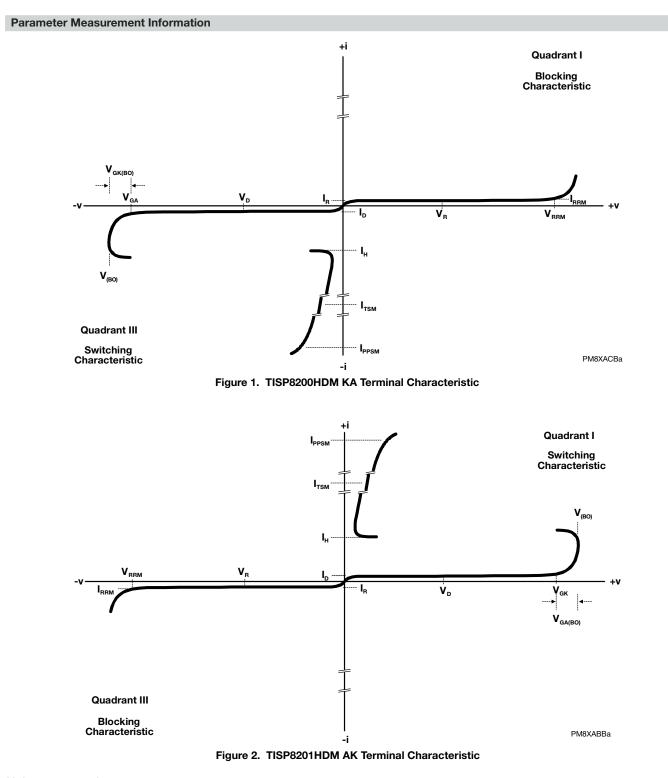

The TISP8200HDM has an array of two buffered P-gate SCRs with a common anode connection. Each SCR cathode and gate has a separate terminal connection. The NPN buffer transistors reduce the gate supply current. In use, the cathodes of the TISP8200HDM SCRs are connected to the two conductors of the POTS line. The gates are connected to the appropriate negative voltage battery feed of the SLIC driving the line conductor pair, so that the TISP8200HDM protection voltage tracks the SLIC negative supply voltage. The anode of the TISP8200HDM is connected to the SLIC common. Negative overvoltages are initially clipped close to the SLIC negative supply by emitter follower action of the NPN buffer transistor. If sufficient clipping current flows, the SCR will regenerate and switch into a low voltage on-state condition. As the overvoltage subsides the high holding current of the SCR prevents d.c. latchup.

The TISP8201HDM has an array of two buffered N-gate SCRs with a common cathode connection. Each SCR anode and gate has a separate terminal connection. The PNP buffer transistors reduce the gate supply current. In use, the anodes of the TISP8201HDM SCRs are connected to the two conductors of the POTS line. The gates are connected to the appropriate positive voltage battery feed of the SLIC driving that line pair, so that the TISP8201HDM protection voltage tracks the SLIC positive supply voltage. The cathode of the TISP8201HDM is connected to the SLIC common. Positive overvoltages are initially clipped close to the SLIC positive supply by emitter follower action of the PNP buffer transistor. If sufficient clipping current flows the SCR will regenerate and switch into a low voltage on-state condition. As the overvoltage subsides the SLIC pulls the conductor voltage down to its normal negative value and this commutates the conducting SCR into a reverse biased condition.

#### How to Order

| Device      | Package          | Carrier               | Order As       | Marking Code | Standard Quantity |

|-------------|------------------|-----------------------|----------------|--------------|-------------------|

| TISP8200HDM | 8-SOIC (210 mil) | Embossed Tape Reeled  | TISP8200HDMR-S | 8200H        | 2000              |

| TISP8201HDM | 8-3010 (2101111) | LINDOSSEU Tape neeleu | TISP8201HDMR-S | 8201H        | 2000              |

#### TISP8200HDM Absolute Maximum Ratings, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

| Rating                                                                   | Symbol            | Value       | Unit |

|--------------------------------------------------------------------------|-------------------|-------------|------|

| Repetitive peak off-state voltage, V <sub>GK</sub> = 0                   | V <sub>DRM</sub>  | -120        | V    |

| Repetitive peak reverse voltage, V <sub>GA</sub> = -70 V                 | V <sub>RRM</sub>  | 120         |      |

| Non-repetitive peak impulse current (see Notes 1, 2 and 3)               |                   |             |      |

| 2/10 μs (Telcordia GR-1089-CORE, 2/10 μs voltage wave shape)             |                   | -500        |      |

| 5/310 µs (ITU-T K.44, 10/700 µs voltage wave shape used in K.20/21/45)   | I <sub>PPSM</sub> | -150        | A    |

| 10/1000 μs (Telcordia GR-1089-CORE, 10/1000 μs voltage wave shape)       |                   | -100        |      |

| Non-repetitive peak on-state current, 50/60 Hz (see Notes 1, 2, 3 and 4) |                   |             |      |

| 10 ms                                                                    |                   | 60          |      |

| 1s                                                                       | 1                 | 14          | A    |

| 7 s                                                                      | ITSM              | 7           | A    |

| 900 s                                                                    |                   | 3.5         |      |

| Junction temperature                                                     | Тј                | -55 to +150 | °C   |

| Storage temperature range                                                | T <sub>stg</sub>  | -65 to +150 | °C   |

NOTES: 1. Initially the device must be in thermal equilibrium with T<sub>J</sub> = 25 °C. The surge may be repeated after the device returns to its initial conditions.

2. These non-repetitive rated currents are peak values. The rated current values may be applied to any cathode-anode terminal pair.

3. Rated currents only apply if pins 1 & 8 (K1,Tip) are connected together, pins 4 & 5 (K2, Ring) are connected together and pins 6 & 7 (A, Ground) are connected together.

4. These non-repetitive rated terminal currents are for the TISP8200HDM and TISP8201HDM together. Device (A)-terminal positive current values are conducted by the TISP8201HDM and (K)-terminal negative current values by the TISP8200HDM.

## BOURNS®

#### TISP8201HDM Absolute Maximum Ratings, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

| Rating                                                                   | Symbol            | Value       | Unit |

|--------------------------------------------------------------------------|-------------------|-------------|------|

| Repetitive peak off-state voltage, V <sub>GA</sub> = 0                   | V <sub>DRM</sub>  | 120         | V    |

| Repetitive peak reverse voltage, V <sub>GK</sub> = 70 V                  | V <sub>RRM</sub>  | -120        |      |

| Non-repetitive peak impulse current (see Notes 5, 6 and 7)               |                   |             |      |

| 2/10 μs (Telcordia GR-1089-CORE, 2/10 μs voltage wave shape)             |                   | 500         |      |

| 5/310 µs (ITU-T K.44, 10/700 µs voltage wave shape used in K.20/21/45)   | I <sub>PPSM</sub> | 150         | A    |

| 10/1000 μs (Telcordia GR-1089-CORE, 10/1000 μs voltage wave shape)       |                   | 100         |      |

| Non-repetitive peak on-state current, 50/60 Hz (see Notes 5, 6, 7 and 8) |                   |             |      |

| 10 ms                                                                    |                   | 60          |      |

| 1 s                                                                      |                   | 14          | A    |

| 7 s                                                                      | ITSM              | 7           | A    |

| 900 s                                                                    |                   | 3.5         |      |

| Junction temperature                                                     | TJ                | -55 to +150 | °C   |

| Storage temperature range                                                | T <sub>stg</sub>  | -65 to +150 | °C   |

NOTES: 5. Initially the device must be in thermal equilibrium with T<sub>J</sub> = 25 °C. The surge may be repeated after the device returns to its initial conditions.

6. These non-repetitive rated currents are peak values. The rated current values may be applied to any cathode-anode terminal pair.

7. Rated currents only apply if pins 1 & 8 (A1, Tip) are connected together, pins 4 & 5 (A2, Ring) are connected together and pins 6 & 7 (K, Ground) are connected together.

8. These non-repetitive rated terminal currents are for the TISP8200HDM and TISP8201HDM together. Device (A)-terminal positive current values are conducted by the TISP8201HDM and (K)-terminal negative current values by the TISP8200HDM.

#### **Recommended Operating Conditions**

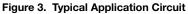

| See Figure 3                     | Min | Тур | Max | Unit |

|----------------------------------|-----|-----|-----|------|

| C1, C2 Gate decoupling capacitor |     | 220 |     | nF   |

#### TISP8200HDM Electrical Characteristics, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

|                   | Parameter                         | Test Conditions                                                                                                                                                     |                                                 | Min  | Тур | Max      | Unit |

|-------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------|-----|----------|------|

| I <sub>DRM</sub>  | Repetitive peak off-state current | $V_{\rm D} = V_{\rm DRM}, V_{\rm GK} = 0$                                                                                                                           |                                                 |      |     | -5       | μA   |

| I <sub>RRM</sub>  | Repetitive peak reverse current   | $V_{R} = V_{RRM}, V_{GA} = -70 V$                                                                                                                                   |                                                 |      |     | 5        | μA   |

| V <sub>(BO)</sub> | Breakover voltage                 | dv/dt = -250 V/ms, $R_{SOURCE}$ = 300 $\Omega$ , $V_{GA}$ = -80 V                                                                                                   |                                                 |      |     | -82      | V    |

| V <sub>(BO)</sub> | Impulse breakover voltage         | dv/dt ≤ -1000 V/µs, Linear voltage ramp,<br>Maximum ramp value = -500 V<br>di/dt = -20 A/µs, Linear current ramp,<br>Maximum ramp value = -10 A<br>$V_{GA}$ = -80 V |                                                 |      |     | -90      | ×    |

| Ι <sub>Η</sub>    | Holding current                   | (I <sub>K</sub> ) I <sub>T</sub> = -1 A, di/dt = 1 A/ms, V <sub>GA</sub> = -80 V                                                                                    |                                                 | -150 |     |          | mA   |

| I <sub>GT</sub>   | Gate trigger current              | $(I_K) I_T = -5 \text{ A}, t_{p(g)} \ge 20 \ \mu s, V_{GA} = -80 \ V$                                                                                               |                                                 |      |     | 15       | mA   |

| Co                | Off-state capacitance             | f = 1 MHz, V <sub>d</sub> = 1 V rms, Gate open                                                                                                                      | V <sub>D</sub> = -2 V<br>V <sub>D</sub> = -50 V |      |     | 65<br>30 | pF   |

OCTOBER 2005 — REVISED MAY 2007 Specifications are subject to change without notice. Customers should verify actual device performance in their specific applications.

# BOURNS®

|                   | Parameter                         | Test Conditions                                                                                                                                                |                                               | Min | Тур | Max      | Unit |

|-------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----|-----|----------|------|

| I <sub>DRM</sub>  | Repetitive peak off-state current | $V_{\rm D} = V_{\rm DRM}, V_{\rm GA} = 0$                                                                                                                      |                                               |     |     | 5        | μA   |

| I <sub>RRM</sub>  | Repetitive peak reverse current   | $V_{\rm R} = V_{\rm RRM}, V_{\rm GK} = 70 \text{ V}$                                                                                                           |                                               |     |     | -5       | μA   |

| V <sub>(BO)</sub> | Breakover voltage                 | dv/dt = 250 V/ms, $R_{SOURCE}$ = 300 $\Omega$ , $V_{GK}$ = 80 V                                                                                                |                                               |     |     | 82       | V    |

| V <sub>(BO)</sub> | Impulse breakover voltage         | dv/dt ≤ 1000 V/µs, Linear voltage ramp,<br>Maximum ramp value = 500 V<br>di/dt = 20 A/µs, Linear current ramp,<br>Maximum ramp value = 10 A<br>$V_{GK}$ = 80 V |                                               |     |     | 90       | v    |

| Ι <sub>Η</sub>    | Holding current                   | (I <sub>A</sub> ) I <sub>T</sub> = 1 A, di/dt = -1 A/ms, V <sub>GK</sub> = 80 V                                                                                |                                               | 20  |     |          | mA   |

| I <sub>GT</sub>   | Gate trigger current              | $(I_A) I_T = 5 \text{ A}, t_{p(g)} \ge 20 \ \mu\text{s}, V_{GK} = 80 \ \text{V}$                                                                               |                                               |     |     | -15      | mA   |

| C <sub>O</sub>    | Off-state capacitance             | f = 1 MHz, V <sub>d</sub> = 1 V rms, Gate open                                                                                                                 | V <sub>D</sub> = 2 V<br>V <sub>D</sub> = 50 V |     |     | 50<br>30 | pF   |

#### TISP8201HDM Electrical Characteristics, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

#### **Thermal Characteristics**

|                       | Parameter                              | Test Conditions                                                                    | Min | Тур | Max | Unit |

|-----------------------|----------------------------------------|------------------------------------------------------------------------------------|-----|-----|-----|------|

| $R_{	extsf{	heta}JA}$ | Junction to ambient thermal resistance | EIA/JESD51-7 PCB, EIA/JESD51-2 Environment, P <sub>TOT</sub> = 4 W<br>(See Note 9) |     | 55  |     | °C/W |

NOTE 9. EIA/JESD51-7 high effective thermal conductivity test board (multi-layer) connected with 0.6 mm printed wiring track widths.

### BOURNS

OCTOBER 2005 — REVISED MAY 2007 Specifications are subject to change without notice. Customers should verify actual device performance in their specific applications.

# BOURNS®

#### **Applications Information**

AI-TISP8-001-b

Figure 4. Typical Overcurrent Protection

#### **Bourns Sales Offices**

| Region        | Phone           | Fax             |

|---------------|-----------------|-----------------|

| The Americas: | +1-951-781-5500 | +1-951-781-5700 |

| Europe:       | +41-41-7685555  | +41-41-7685510  |

| Asia-Pacific: | +886-2-25624117 | +886-2-25624116 |

#### **Technical Assistance**

| Region        | Phone           | Fax             |

|---------------|-----------------|-----------------|

| The Americas: | +1-951-781-5500 | +1-951-781-5700 |

| Europe:       | +41-41-7685555  | +41-41-7685510  |

| Asia-Pacific: | +886-2-25624117 | +886-2-25624116 |

#### www.bourns.com

Bourns<sup>®</sup> products are available through an extensive network of manufacturer's representatives, agents and distributors. To obtain technical applications assistance, a quotation, or to place an order, contact a Bourns representative in your area.

**Reliable Electronic Solutions**