# PIC-P67J60 development board

**Users Manual**

Rev. C, December 2009 Copyright(c) 2009, OLIMEX Ltd, All rights reserved

Page 1

#### **INTRODUCTION:**

If you want to build your own Internet enabled device this is the board for you. It has PIC18F67J60 microcontroller which has integrated Ethernet MAC+PHY and comes pre-programmed with Microchip's free TCP-IP stack. So all you need is to add your circuit in the prototype area and you are ready! With 128K Flash memory for programs and 128KB Flash memory your application will not suffer from low memory at all.

#### **BOARD FEATURES:**

- **PIC18F67J60** microcontroller with Ethernet and 1Mbit memory for code;

- 1Mbit data Flash for data storage;

- mini ICSP/ICD connector for programming with PIC-ICD2;

- Ethernet connector with status leds;

- RS232 driver and connector;

- Complete web server and TCP-IP stack support as per Microchip's open source TCP-IP stack;

- All PIC free ports available on header close to the prototype area;

- Dimensions 100x80 mm (3.94 x 3.4");

#### **ELECTROSTATIC WARNING:**

The **PCI-P67J60** development board is shipped in protective anti-static packaging. The board must not be subject to high electrostatic potentials. General practice for working with static sensitive devices should be applied when working with this board.

#### **BOARD USE REQUIREMENTS:**

Cables:

1.8 meter USB A-B cable to connect PIC-ICD2 or PIC-ICD2-POCKET to USB host on PC, or RS232 cable, if you use PIC-ICD2-TINY. Other cables might be required in case of other programming/debugging tools. You will need a serial cable if not for programming, than for configuring the board. You will also need a LAN cable.

**Hardware:** Programmer/Debugger – **PIC-ICD2**, **PIC-ICD2-POCKET**, **PIC-ICD2-TINY** or other compatible programming/debugging tool.

!!!Warning!!! When you want to program this microcontroller with PIC-ICD2, PIC-ICD2-POCKET or PIC-ICD2-TINY, before connecting the programmer to your target board, you should first connect the programmer to your computer and open MPLAB. There, first from menu Configure – Select Device – choose the microcontroller you are about to program, then from menu Programmer – Select Programmer – choose MPLAB ICD 2, wait while MPLAB is downloading operation system, and after ICD2 is connected – check in menu Programmer – Settings – Power – there is option – Power target circuit from MPLAB ICD 2 – this

option should be forbidden, you could not select it. Now it is safe to connect the programmer to your target board.

Software: PIC-MICRO-WEB is tested with MPLAB IDE v.7.62 + MPLAB C18 C compiler. It is possible that the stack might not function properly if used with later versions of MPLAB IDE. You will also need a terminal program configured at 19 200 bps, 8N1 and no flow control.

#### **PROCESSOR FEATURES:**

The **PIC-P67J60** uses MCU PIC67j60 which has the following features:

- IEEE 802.3 Compatible Ethernet Controller

- Integrated MAC and 10Base-T PHY

- 8-Kbyte Transmit/Receive Packet Buffer SRAM

- Supports One 10Base-T Port

- Programmable Automatic Retransmit on Collision

- Programmable Padding and CRC Generation

- Programmable Automatic Rejection of Erroneous Packets

- Activity Outputs for 2 LED Indicators

- Buffer:

- Configurable transmit/receive buffer size

- Hardware-managed circular receive FIFO

- Byte-wide random and sequential access

- Internal DMA for fast memory copying

- Hardware assisted checksum calculation for various protocols

- MAC:

- Support for Unicast, Multicast and Broadcast packets

- Programmable Pattern Match of up to 64 bytes within packet at user-defined offset

- Programmable wake-up on multiple packet formats

- PHY:

- Wave shaping output filter

- Selectable System Clock derived from Single 25 MHz External Source:

- 2.778 to 41.667 MHz

- Internal 31 kHz Oscillator

- Secondary Oscillator using Timer1 @ 32 kHz

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if oscillator stops

- Two-Speed Oscillator Start-up

- High-Current Sink/Source: 25 mA/25 mA on PORTB and PORTC

- Five Timer modules (Timer0 to Timer4)

- Four External Interrupt pins

- Two Capture/Compare/PWM (CCP) modules

- Three Enhanced Capture/Compare/PWM (ECCP) modules:

- One, two or four PWM outputs

- Selectable polarity

- Programmable dead time

- Auto-shutdown and auto-restart

- Up to Two Master Synchronous Serial Port (MSSP) modules supporting SPI (all 4 modes) and I<sup>2</sup>C™ Master and Slave modes

- Up to Two Enhanced USART modules:

- Supports RS-485, RS-232 and LIN 1.2

- Auto-wake-up on Start bit

- Auto-Baud Detect (ABD)

- 10-Bit, Up to 16-Channel Analog-to-Digital Converter module (A/D):

- Auto-acquisition capability

- Conversion available during Sleep

- Dual Analog Comparators with Input Multiplexing

- 5.5V Tolerant Inputs (digital-only pins)

- Low-Power, High-Speed CMOS Flash Technology:

- Self-reprogrammable under software control

- C compiler Optimized Architecture for Reentrant Code

- Power Management Features:

- Run: CPU on, peripherals on

- Idle: CPU off, peripherals on

- Sleep: CPU off, peripherals off

- Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 134s

- Single-Supply 3.3V In-Circuit Serial Programming (ICSP™) via Two Pins

- In-Circuit Debug (ICD) with 3 Breakpoints via Two Pins

- Operating Voltage Range of 2.35V to 3.6V (3.1V to 3.6V using Ethernet module)

- On-Chip 2.5V Regulator

### **BLOCK DIAGRAM**

FIGURE 1-1: PIC18F66J60/66J65/67J60 (64-PIN) BLOCK DIAGRAM Data Bus<8> Table Pointer<21> PORTA Data Latch 8 8 inc/dec logic RA0:RA5<sup>(1)</sup> Data Memory (3808 Bytes) PCLATU PCLATH 21 20 Address Latch PCU PCH PCL Program Counter 12 PORTB Data Address<12> RB0:RB7<sup>(1)</sup> 4 BSR 31 Level Stack /12 Address Latch Access Bank FSR0 STKPTR Program Memory FSR1 (64, 96, 128 Kbytes) FSR2 12 Data Latch PORTC RC0:RC7<sup>(1)</sup> inc/dec logic Table Latch Address ROM Latch Instruction Bus <16> Decode PORTD RD0:RD2<sup>(1)</sup> 8 State Machine Instruction Control Signals Decode and Control PRODH PRODL PORTE RE0:RE5<sup>(1)</sup> 8 x 8 Multiply Power-up OSC2/CLKO OSC1/CLKI Timing Generation Timer BITOP  $\boxtimes \longleftrightarrow$ Oscillator 8 Start-up Time: INTRC PORTF Oscillator Power-on RF1:RF7<sup>(1)</sup> Reset Precision ALÚ<8> Watchdog Timer Band Gap Reference 8 ENVREG Brown-out Reset<sup>(2)</sup> Voltage Regulator  $\boxtimes$ PORTG  $\boxtimes$ RG4<sup>(1)</sup>  $\times$  $\boxtimes$ VDDCORE/VCAP VDD, VSS MCLR ADC Timer0 Timer1 Timer2 Timer3 Timer4 Comparators 10-Bit MSSP1 Ethernet CCP4 CCP5 EUSART1 ECCP1 ECCP2 ECCP3 Note 1: See Table 1-4 for I/O port pin descriptions. BOR functionality is provided when the on-board voltage regulator is enabled.

Page 5

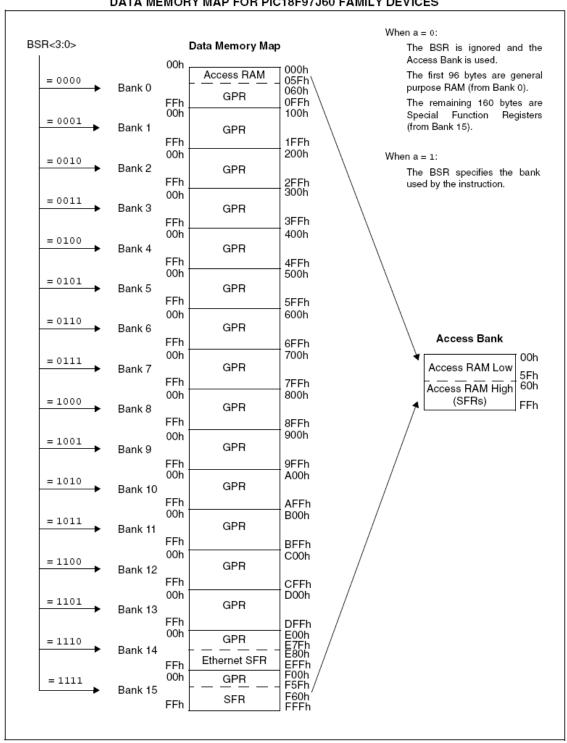

#### **MEMORY MAP:**

#### DATA MEMORY MAP FOR PIC18F97J60 FAMILY DEVICES

Page 6

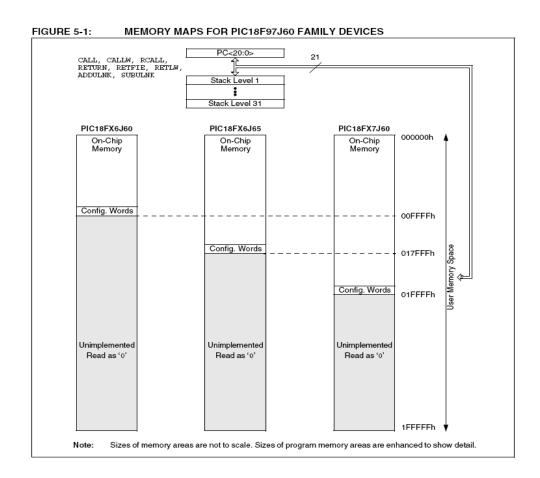

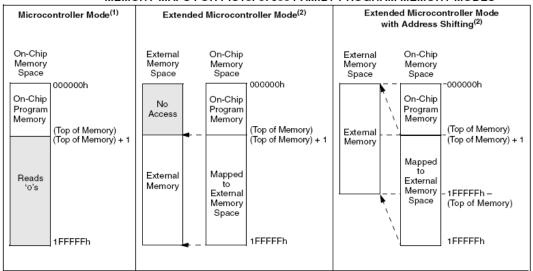

#### MEMORY MAPS FOR PIC18F97J60 FAMILY PROGRAM MEMORY MODES

**Legend:** (Top of Memory) represents upper boundary of on-chip program memory space (see Figure 5-1 for device-specific values). Shaded areas represent unimplemented or inaccessible areas depending on the mode.

Note 1: This mode is the only available mode on 64-pin and 80-pin devices and the default on 100-pin devices.

2: These modes are only available on 100-pin devices.

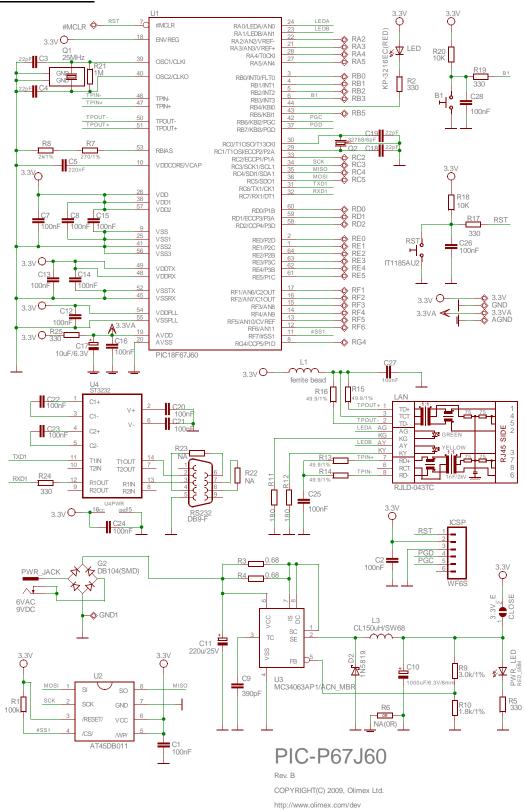

### **SCHEMATIC:**

Page 9

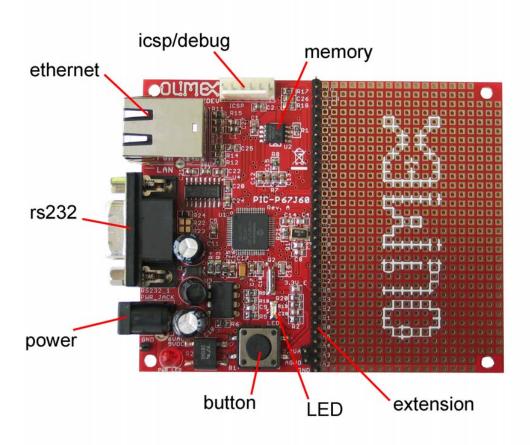

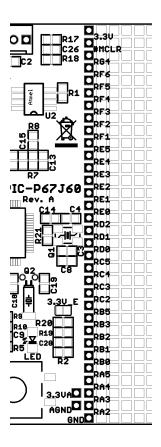

## **BOARD LAYOUT:**

## **POWER SUPPLY CIRCUIT:**

**PIC-P67J60** can take power only from power connector PWR, where (9-12) VDC or 6VAC external power supply have to be applied.

The board power consumption is: about 80 mA with all peripherals and MCU running at full speed.

## **RESET CIRCUIT:**

**PIC-P67J60** reset circuit is made with the pull-up R18 (10K), R17 (330 $\Omega$ ) and C31 (100nF).

## **CLOCK CIRCUIT:**

Quartz crystal 25 MHz is connected to **PIC18F67J60** pin 39 clock in (OSC1/CLKI) and pin 40 clock out (OSC2/CLKO).

Quartz crystal 32.768 kHz is connected to **PIC18F67J60** pin 29 (T1OSI) and pin 30 (T1OSO) and supplies the Timer1.

## **JUMPER DESCRIPTION:**

3.3V\_E

4

enables 3.3 V power supply for the PIC18F67J60 and all other devices.

Default state is closed.

## **INPUT/OUTPUT:**

One **user button** with name **BUT1** – connected to PIC18F67J60 pin 6 RB3/INT3;

One **LED** named **LED**(red) connected to PIC18F67J60 pin 44 RB4/KBI0;

**Power supply red LED** with name **PWR\_LED** – indicates that power supply 3.3V is present.

## **EXTERNAL CONNECTOR DESCRIPTION:**

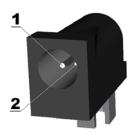

### **PWR:**

| Pin # | Signal Name  |

|-------|--------------|

| 1     | 9VDC or 6VAC |

| 2     | GND          |

The power input should be +9VDC/6VAC.

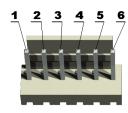

## **ICSP**:

| Pin # | Signal Name |

|-------|-------------|

| 1     | RST         |

| 2     | VCC         |

| 3     | GND         |

| 4     | PGD         |

| 5     | PGC         |

| 6     | NC          |

PGD I/O Program Data. Serial data for programming.

PGC Input Program Clock. Clock used for transferring the serial data (output from ICSP, input for the MCU).

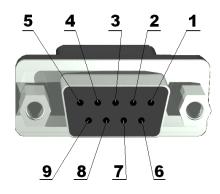

## RS232:

|      | ·                   |  |

|------|---------------------|--|

| Pin# | Signal Name         |  |

| 1    | NC                  |  |

| 2    | TXD                 |  |

| 3    | RXD                 |  |

| 4    | to pin 6 via R23/NC |  |

| 5    | GND                 |  |

Page 12

| 6 | to pin 4 via R23/NC |

|---|---------------------|

| 7 | to pin 8 via R22/NC |

| 8 | to pin 7 via R22/NC |

| 9 | NC                  |

**TXD** Output **Transmit Data.** This is the asynchronous serial data output (RS232) for the shift register on the UART controller.

**RXD** Input **Receive Data.** This is the asynchronous serial data input (RS232) for the shift register on the UART controller.

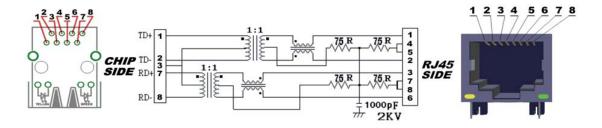

## LAN:

| Pin# | Signal Name Chip Side | Pin# | Signal Name Chip Side |

|------|-----------------------|------|-----------------------|

| 1    | TPOUT+                | 5    | Not Connected (NC)    |

| 2    | TPOUT-                | 6    | Not Connected (NC)    |

| 3    | 3.3V                  | 7    | TPIN+                 |

| 4    | Not Connected (NC)    | 8    | TPIN-                 |

| LED   | Color  | Usage                         |

|-------|--------|-------------------------------|

| Right | Yellow | Activity                      |

| Left  | Green  | 100MBits/s (Half/Full duplex) |

# **PROTOAREA:**

| Pin # | Signal Name        |

|-------|--------------------|

| 3.3V  | 3.3V               |

| #MCLR | RST                |

| RG4   | RG4/CCP5/P1D       |

| RF6   | RF6/AN11           |

| RF5   | RF5/AN10/CVREF     |

| RF4   | RF4/AN9            |

| RF3   | RF3/AN8            |

| RF2   | RF2/AN7/C1OUT      |

| RF1   | RF1/AN6/C2OUT      |

| RE5   | RE5/P1C            |

| RE4   | RE4/P3B            |

| RE3   | RE3/P3C            |

| RE2   | RE2/P2B            |

| RE1   | RE1/P2C            |

| RE0   | RE0/P2D            |

| RD2   | RD2/CCP4/P3D       |

| RD1   | RD1/ECCP3/P3A      |

| RD0   | RD0/P1B            |

| RC5   | RC5/SDO1/MOSI      |

| RC4   | RC4/SDI1/SDA1/MISO |

| RC3   | RC3/SCK1/SCL1/SCK  |

| RC2   | RC2/ECCP1/P1A      |

| RB5   | RB5/KBI0           |

| RB3   | RB3/INT3/B1        |

| RB2   | RB2/INT2           |

| RB1   | RB1/INT1           |

| RB0   | RB0/INT0/FLT0      |

| RA5   | RA5/AN4            |

| RA4   | RA4/TOCKI          |

| RA3   | RA3/AN3/VREF+      |

| RA2   | RA2/AN2/VREF-      |

| 3.3VA | 3.3V ANALOG        |

| AGND  | ANALOG GND         |

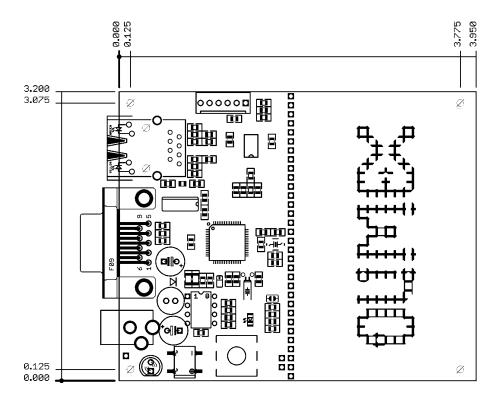

# **MECHANICAL DIMENSIONS:**

All dimensions are in inches.

# **AVAILABLE DEMO SOFTWARE:**

You could find information about PIC-P67J60 board, Microchip TCP/IP stack and how to change and configure the software in **Understanding PIC WEB boards** on www.olimex.com/dev.

## **ORDER CODE:**

**PIC-P67J60** – completely assembled and tested with PIC18F67J60 on board.

How to order?

You can order to us directly or by any of our distributors.

Check our web <a href="https://www.olimex.com/dev">www.olimex.com/dev</a> for more info.

Pb-free, Green All boards produced by Olimex are RoHS compliant

#### **Revision history:**

REV. B - created December 2009

#### Disclaimer:

© 2009 Olimex Ltd. All rights reserved. Olimex®, logo and combinations thereof, are registered trademarks of Olimex Ltd. Other terms and product names may be trademarks of others.

The information in this document is provided in connection with Olimex products. No license, express or implied or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Olimex products.

Neither the whole nor any part of the information contained in or the product described in this document may be adapted or reproduced in any material from except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous development and improvements. All particulars of the product and its use contained in this document are given by OLIMEX in good faith. However all warranties implied or expressed including but not limited to implied warranties of merchantability or fitness for purpose are excluded.

This document is intended only to assist the reader in the use of the product. OLIMEX Ltd. shall not be liable for any loss or damage arising from the use of any information in this document or any error or omission in such information or any incorrect use of the product.