# **GRAPHICS**

# S1D13748

### October 2007

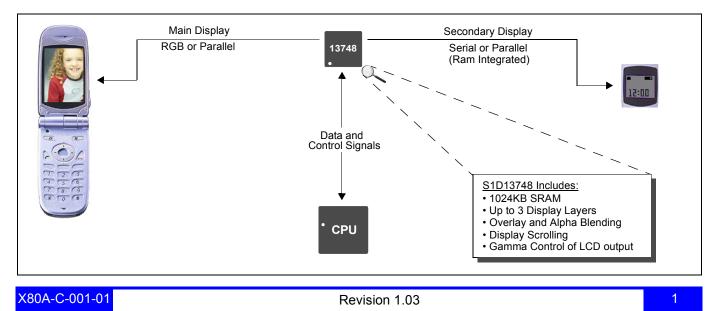

## S1D13748 Mobile Graphics Engine

The S1D13748 is a low cost, low power Mobile Graphics Engine providing multiple LCD support for embedded and mobile products requiring up to WVGA resolution. Supporting up to three display layers, the S1D13748 provides the Host processor with flexibility in handling multiple image sources. It's ability to receive high speed Host writes, combined with it's support for a wide variety of LCD panels, makes the S1D13748 an excellent choice for a multitude of LCD applications.

The S1D13748 includes a pixel doubling feature which allows easy migration to larger panel sizes using existing image data. The feature set includes independent resizing of PIP window image data using the bi-cubic scaler, scrolling control for each layer, and LCD output manipulation such as gamma control and optional dithering. This allows the Host processor to provide image data, but off-loads the image processing requirement from the Host. The S1D13748 also incorporates LCD Bypass Mode which allows the Host to exercise direct control over parallel or serial RAM-based panels.

The S1D13748 contains 1024K bytes of embedded SRAM which is used to store image data for up to three layers for LCD1 and image data for LCD2. This feature set provides a low cost, low power single chip solution to meet the demands of embedded markets requiring up to WVGA resolution, such as Mobile Communications devices.

### ■ FEATURES

- Embedded 1024K byte SRAM

- Low Operating Voltage

- 16-bit Indirect Host Interface

- High Speed Host Writes

- Rectangular, Rotated, and Mirror Host Write Modes

- Input Formats: YUV 4:2:2, 4:2:0 and RGB 5:6:5

- Supports up to 2 LCD panels (LCD2 must be RAM integrated)

- Support for RGB, Serial, and Parallel I/F panels

- LCD Bypass Mode

- Support for up to 3 display layers with overlay and alpha blending

- Main Layer image can be doubled in size

- PIP1 Layer can be resized from 8x to 1/8x

- PIP2 Layer can be resized from 8x to 1/8x

- Independent scrolling control for each layer

- Look-up Table for gamma control of LCD output

- Optional dithering of LCD output

- Internal PLL or Digital Clock Input

- Software Initiated Power Save Mode

- PFBGA 121-pin or QFP20 144-pin packages

## SYSTEM BLOCK DIAGRAM

# **GRAPHICS**

# S1D13748

### DESCRIPTION

#### Memory

1024K bytes of embedded SRAM

#### **CPU Interface**

- 16-bit Indirect Host Interface

- Supports High Speed Host Writes

- · Integrated Host interface Write Controller supports:

- Rectangular Write Mode

- Rotated Write Mode

- Mirror Write Mode

- LCD Bypass Mode allows direct control of serial and parallel LCD panels by the Host CPU

#### **Panel Support**

- 9/12/16/18/24-bit RGB interface panels

- 8/16/18/24-bit Parallel interface panels (RAM Integrated)

- 8/16-bit Serial interface panels (RAM Integrated)

- Supports up to 2 LCD panels (LCDs cannot be refreshed simultaneously)

- LCD1: RGB, LCD2: Serial w/ RAM

- LCD1: Parallel w/ RAM, LCD2: Serial w/RAM

- LCD1: Parallel w/RAM, LCD2: Parallel w/RAM

- LCD1: RGB, LCD2: Parallel w/RAM

#### Input Formats

- Host can input image data as:

- YUV 4:2:2

- YUV 4:2:0

- RGB 5:6:5

#### **Display Features**

- Supports up to 3 layers with Overlay and Alpha Blending functions:

- Main Layer features:

- Image can be stored as RGB 5:6:5

- Pixel Doubling which doubles the size of the display image (independent horizontal/vertical)

- PIP1 Layer features:

- Image can be stored as RGB 5:6:5 or YUV 4:2:2

- Bi-Cubic Scaler can resize image from 8x 1/8x

- Edge Enhancement support

- PIP2 Layer features:

- Image can be stored as RGB 5:6:5 or YUV 4:2:2

- Bi-Cubic Scaler can resize image from 8x 1/8x

- Panorama function allows variable vertical scaling

- Edge Enhancement support

- LUT (Look-Up Table) for independent gamma control of PIP2 window

- Independent Display Scrolling for each Layer (Main, PIP1, PIP2)

- LUT (Look-Up Table) for gamma control of the LCD output

- Optional dithering for the LCD output

#### Miscellaneous

- Internal PLL or digital clock input (CLKI)

- Software initiated power save mode

- General Purpose IO pins

- CORE<sub>VDD</sub> 1.5 volts and IO<sub>VDD</sub> 1.80, 2.80, or 3.30 volts

- Packages:

- PFBGA 121-pin (10 x 10 x 1.2mm) (0.8mm pitch)

- QFP20 144-pin (20 x 20 x 1.4mm) (0.5mm pitch)

### CONTACT YOUR SALES REPRESENTATIVE FOR THESE COMPREHENSIVE DESIGN TOOLS

North America

2580 Orchard Parkway

Tel: (408) 922-0200

Fax: (408) 922-0238

Europe

Riesstrasse 15

Tel: 089-14005-0

Fax: 089-14005-110

San Jose, CA 95131, USA

http://www.eea.epson.com/

80992 Munich, Germany

Epson Europe Electronics GmbH

http://www.epson-electronics.de/

S1D13748 Technical Documentation

Seiko Epson Corporation

421-8, Hino, Hino-shi

Tel: 042-587-5812

Fax: 042-587-5564

Hong Kong

Tokyo 191-8501, Japan

http://www.epson.co.jp/

Epson Hong Kong Ltd.

20/F.. Harbour Centre

Wanchai, Hong Kong

http://www.epson.com.hk/

25 Harbour Road

Tel: 2585-4600

Fax: 2827-4346

IC International Sales Group

Japan

CPU Independent Software Utilities S1D137

Boards

Epson Electronics America, Inc.

S1D13748 Evaluation Boards  Royalty Free source level driver code

Taiwan Epson Taiwan Technology & Trading Ltd. 14F, No. 7 Song Ren Road Taipei 110 Tel: 02-8786-6688 Fax: 02-8786-6677 http://www.epson.com.tw/

http://www.epson.com.tw/ Singapore

Epson Singapore Pte Ltd 1 HarbourFront Place #03-02 HarbourFront Tower One Singapore, 098633 Tel: (65) 6586-5500 Fax: (65) 6271-3182 http://www.epson.com.sg/

© SEIKO EPSON CORPORATION 2006-2007. All rights reserved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws. EPSON is a registered trademark of Seiko Epson Corporation. All other trademarks are the property of their respective owners.