## **Cortina Systems<sup>®</sup> IXF1104 4-Port Gigabit Ethernet Media Access Controller**

## Datasheet

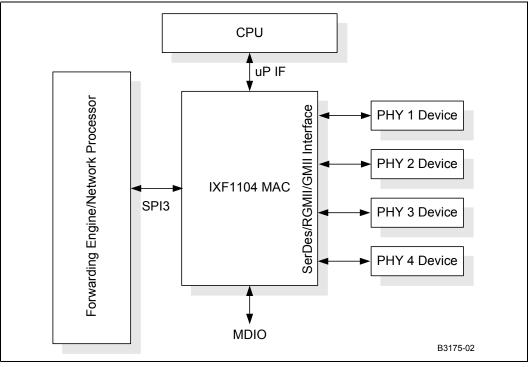

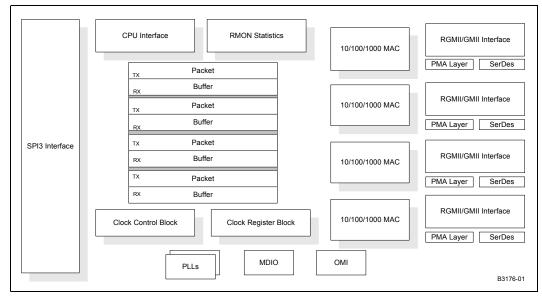

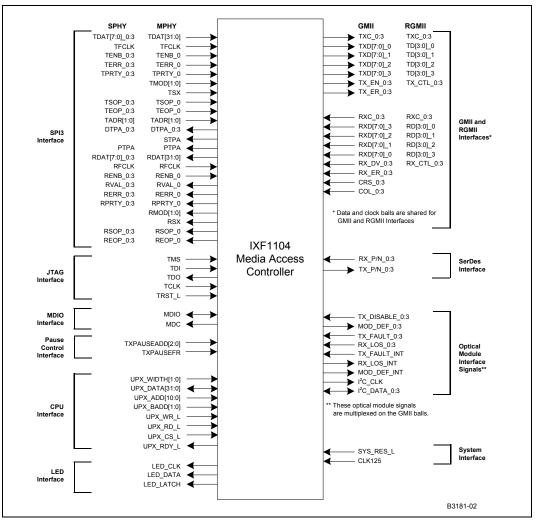

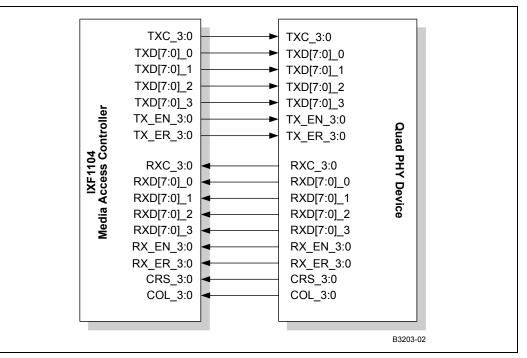

The Cortina Systems<sup>®</sup> IXF1104 4-Port Gigabit Ethernet Media Access Controller (IXF1104 MAC) supports IEEE 802.3\* 10/100/1000 Mbps applications. The IXF1104 MAC supports a System Packet Interface Phase 3 (SPI3) system interface to a network processor or ASIC, and concurrently supports copper and fiber physical layer devices (PHYs).

The copper PHY interface supports the standard and reduced pin-count Gigabit Media Independent Interface (GMII and RGMII) for high-port-count applications. For fiber applications the integrated Serializer/ Deserializer (SerDes) on each port supports direct connection to optical modules to reduce PCB area requirements and system cost.

### **Product Features**

- Four Independent Ethernet MAC Ports for Copper or Fiber Physical layer connectivity.

- IEEE 802.3 compliant

- Independent Enable/Disable of any port

- Copper Mode:

- RGMII for 10/100/1000 Mbps links

- GMII for 1000 Mbps full-duplex links

- IEEE 802.3 MDIO interface

- Fiber Mode:

- Integrated SerDes interface for direct connection to 1000BASE-X optical modules

- IEEE 802.3 auto-negotiation or forced mode

- Supports SFP MSA-compatible transceivers

- SPI3 interface supports data transfers up to 4 Gbps in both modes:

- 32-bit Multi-PHY mode (133 MHz)

- 4 x 8-bit Single-PHY mode (125 MHz)

- IEEE 802.3-compliant Flow Control

- Loss-less up to 9.6 KB packets and 5 km links

Jumbo frame support for 9.6 KB packets

- Internal per-channel FIFOs: 32 KB Rx, 10 KB Tx

- Flexible 32/16/8-bit CPU interface

- Applications

- Load Balancing Systems

- MultiService Switches

- Web Caching Appliances

- Intelligent Backplane Interfaces

- Edge Routers

- Redundant Line Cards

- Programmable Packet handling

- Filter broadcast, multicast, unicast, VLAN and errored packets

- Automatically pad undersized Tx packets

Remove CRC from Rx packets

- Performance Monitoring and Diagnostics

- RMON Statistics

- CRC calculation and error detection

- Detection of length error, runt, or overly large packets

- Counters for dropped and errored packets

- Loopback modes

- JTAG boundary scan

- .18 m CMOS process technology

- 1.8 V core, 2.5 V RGMII, GMII, OMI, and 3.3 V SPI3 and CPU

- Operating Temperature Ranges:

- Copper Mode: -40 °C to +85 °C

- Fiber Mode: 0 °C to +70 °C

- Package Options:

- 552-ball Plastic FC-BGA (Leaded)

- 552-ball Plastic FC-BGA (RoHS)

- 552-ball Ceramic BGA (contact your Cortina Sales Representative)

- Base Station Controllers and Transceivers

- Serving GPRS Support Nodes (SGSN)

- Gateway GPRS Support Nodes (GGSN)

- Packet Data Serving Nodes (PDSN)

- DSL Access Multiplexers (DSLAM)

- Cable Modem Termination Systems (CMTS)

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH CORTINA SYSTEMS<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

EXCEPT AS PROVIDED IN CORTINA'S TERMS AND CONDITIONS OF SALE OF SUCH PRODUCTS, CORTINA ASSUMES NO LIABILITY WHATSOEVER, AND CORTINA DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF CORTINA PRODUCTS, INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Cortina products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Cortina Systems<sup>®</sup> and the Cortina Systems logo are the trademarks or registered trademarks of Cortina Systems, Inc. and its subsidiaries in the U.S. and other countries. Other names and brands may be claimed as the property of others. Copyright © 2002 – 2008 Cortina Systems, Inc. All rights reserved.

## **Revision History**

#### Revision 13.2 Revision Date: 17 September 2008

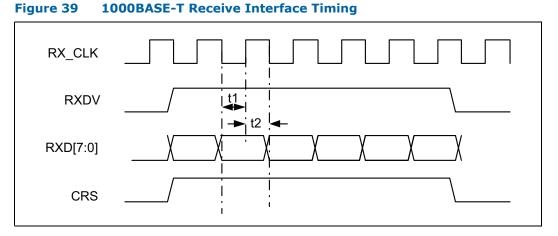

- Updated Figure 39, 1000BASE-T Receive Interface Timing, on page 137.

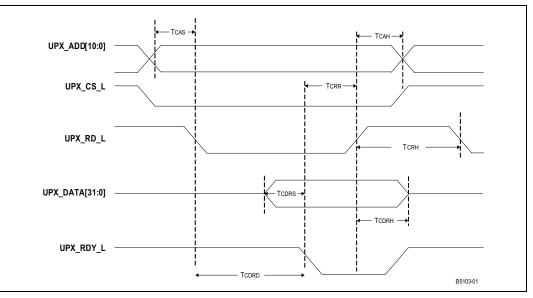

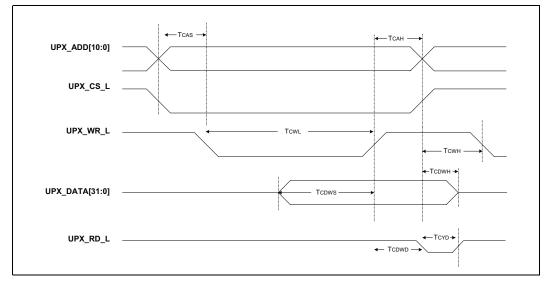

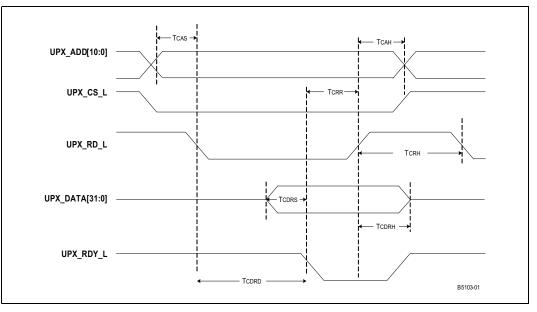

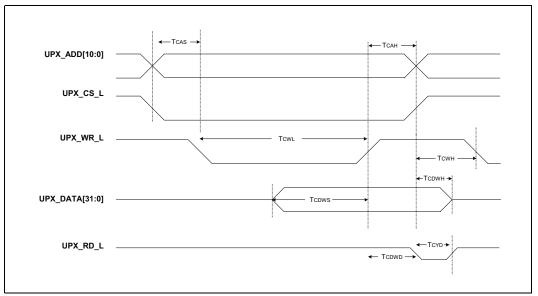

- Updated the Tcdwd and Tcdrh parameter values in Table 53, CPU Interface AC Signal Parameters, on page 143.

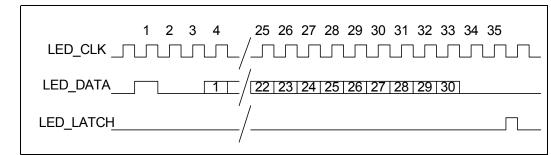

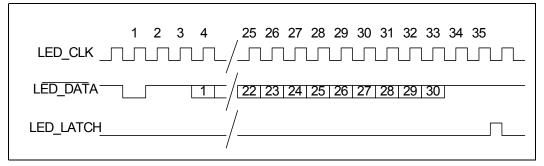

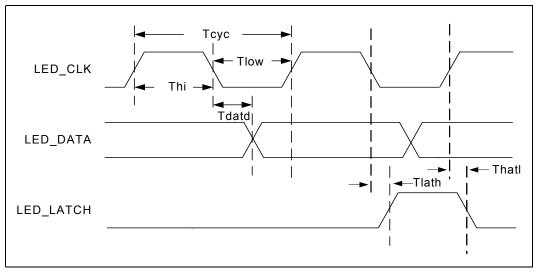

- Updated the Tdatd, Tlath and Tlatl parameter values in Table 57, LED Interface AC Timing Parameters, on page 147.

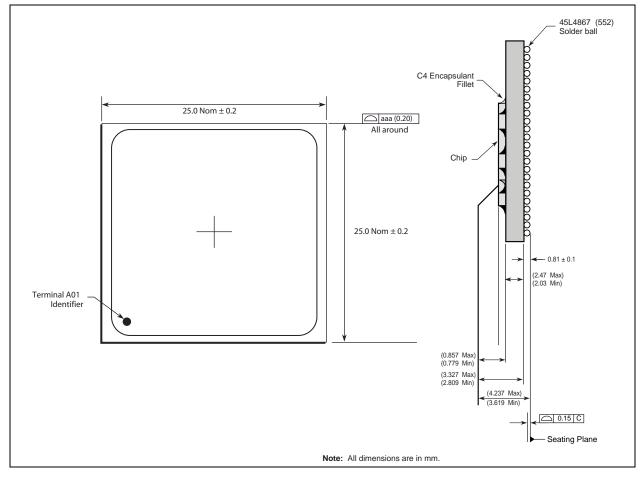

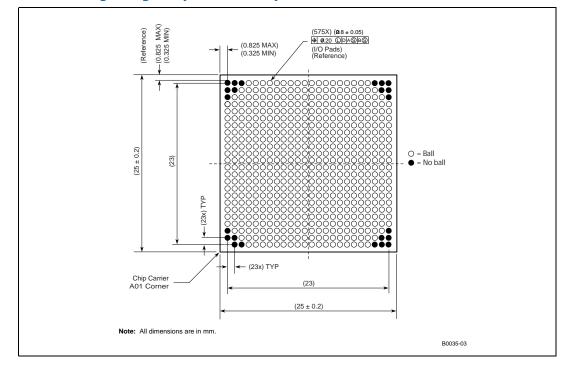

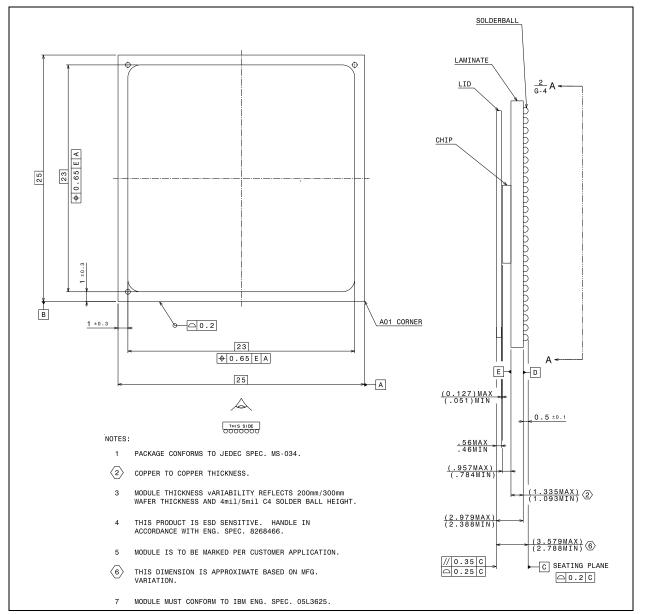

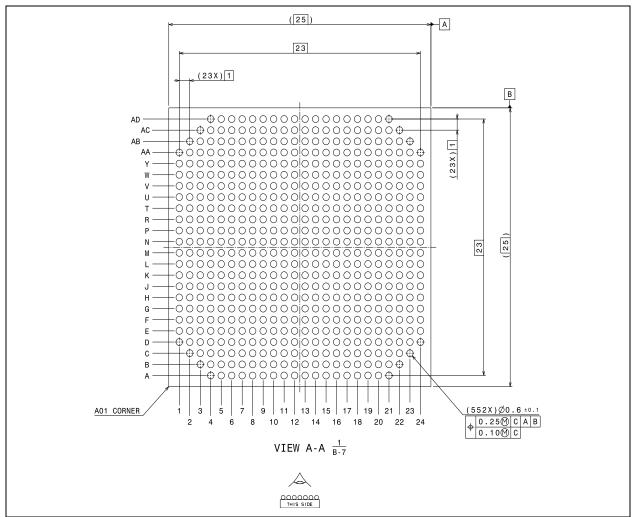

- Replaced the FC-PBGA package drawings in Section 9.3.2, Plastic Ball Grid Array Package Diagram, on page 216.

- Replaced occurences of "2.5V LVTTL" with "2.5V CMOS".

- Removed caution specifying that "IXF1104 MAC input signals are not 5 V tolerant" in Section 7.1, *DC Specifications*, on page 128 and added a note stating that "All 3.3V LVTTL input buffers are 5V tolerant, and all 2.5V CMOS input buffers are 3.3V LVTTL level tolerant.

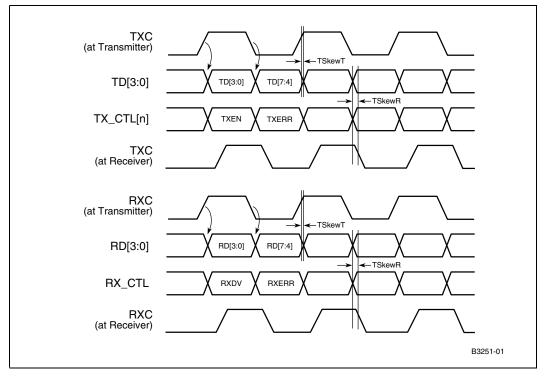

- Updated signal names shown in Figure 31, Figure 32, Figure 47and Figure 48 to match the signal tables.

#### Revision 13.1 Revision Date: 01 August 2008

Removed the ordering information from Table 156, *Package Description, on page 213*. This information is now available from www.cortina-systems.com.

#### Revision 13.0 Revision Date: 30 June 2008

Updated Section 9.0, *Mechanical Specifications, on page 213* to reflect the change to the Flip Chip-Plastic Ball Grid Array (FC-PBGA) package. This chapter includes new package dimensions, part numbers and diagrams.

#### Revision 12.2 Revision Date: 12 May 2008

- · Updated document with the new corporate logo and template.

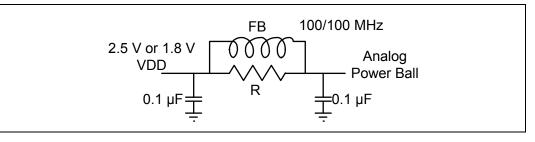

- Updated Figure 6, Analog Power Supply Filter Network, on page 63.

- Updated Figure 12, MPHY Receive Logical Timing, on page 82.

- Updated Table 40, DC Specifications, on page 128.

- Updated Figure 39, 1000BASE-T Receive Interface Timing, on page 137.

- Updated the RxRuntErrors counter description. See page 169.

#### Revision 12.1 Revision Date: 14 September 2007

Removed the marking and ordering information. This information is now available from www.cortina-systems.com.

#### Revision 12.0 Revision Date: 20 July 2007

• DC coupling is not supported and references were removed.

| Revision Number: 11.0<br>Revision Date: 24 April 2007 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Page #                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| N/A                                                   | <ul> <li>Updated the CBGA package side-view drawing (Figure 55, <i>CBGA Package Side View Diagram</i>).</li> <li>Added the FCPBGA package side-view drawing (Figure 57, <i>FC-PBGA Package Diagram (Top and Side View), on page 216</i>).</li> <li>Updated Electrical specs. on UPX_ADD, UPX_BADD, UPX_DATA, UPX_CS_L, UPX_WR_L, UPX_RD_L, UPX_RDY_L, UPX_WIDTH, TCLK, SYS_RES_L, and CLK123 (Table 7 on page 51, Table 12 on page 55, and Table 13 on page 55).</li> <li>Updated the description of the MDIO Soft Reset Register (0x506) to include a definition of a "reset" (Table 106, <i>MDIO Soft Reset (\$0x506</i>), on page 182).</li> </ul> |  |

|        | Revision Number: 10.0<br>Revision Date: 28 November 2006  |

|--------|-----------------------------------------------------------|

| Page # | Description                                               |

| N/A    | First release of this document from Cortina Systems, Inc. |

| Revision Number: 009<br>Revision Date: 27-Oct-2005 |                                                                                                                                                                                                                                   |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Page #                                             | Description                                                                                                                                                                                                                       |

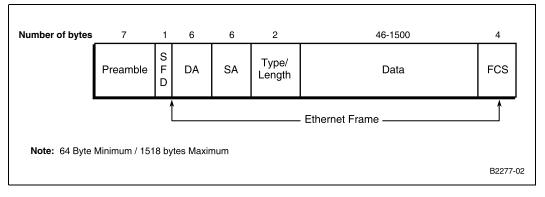

| page 69                                            | Modified Figure 8, Ethernet Frame Format [changed Preamble byte count to 7 bytes].                                                                                                                                                |

| page 130                                           | Table 44, <i>RGMII Power</i> [changed V <sub>CC</sub> to V <sub>DD in</sub> I <sub>IH</sub> and I <sub>IL</sub> ]                                                                                                                 |

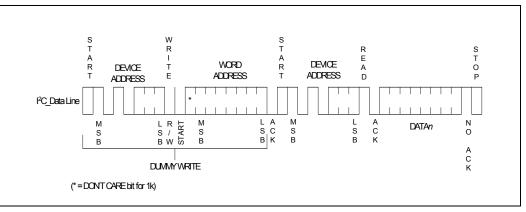

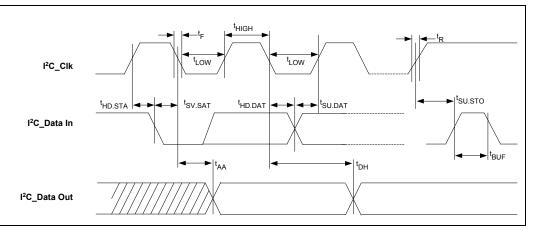

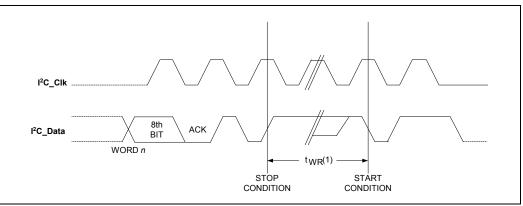

| page 105                                           | Added bullet to Section 5.7.3, <i>I</i> <sup>2</sup> <i>C Module Configuration Interface</i> : The I2 <i>C</i> interface only supports random single-byte reads and does not guarantee coherency when reading two-byte registers. |

| page 216                                           | Replaced Figure 57, FC-PBGA Package Diagram (Top and Side View), on page 216.                                                                                                                                                     |

| page 205                                           | Modified Table 146, SPI3 Receive Configuration (\$0x701).                                                                                                                                                                         |

| page 211                                           | Modified Table 153, Optical Module Control Ports 0 - 3 (\$0x79A): changed default values.                                                                                                                                         |

| page 212                                           | Modified Table 154, I <sup>2</sup> C Control Ports 0 - 3 (\$0x79B).                                                                                                                                                               |

| page 227                                           | Modified Table 213, I2C Data Ports 0 - 9 (\$0x79F) (changed address from \$0x79C to \$0x79F).                                                                                                                                     |

| N/A                                                | Added 552-ball Flip Chip-PBGA (FC-PBGA) and Product Ordering Number information.                                                                                                                                                  |

| Revision Number: 008<br>Revision Date: August 1, 2005 (Sheet 1 of 2) |                                                                                                                                                                                                                        |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Page #                                                               | Description                                                                                                                                                                                                            |

| N/A                                                                  | Added 552-ball Ceramic Ball Grid Array (CBGA) compliant with RoHS and Product Ordering Number information.                                                                                                             |

| N/A                                                                  | Added 552-ball Flip Chip-PBGA (FC-PBGA) and Product Ordering Number information.                                                                                                                                       |

| page 55                                                              | Modified Table 12, JTAG Interface Signal Descriptions: changed Standard to 3.3 V LVTTL from 2.5 V CMOS.                                                                                                                |

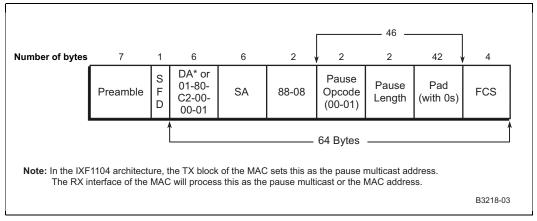

| page 69                                                              | Modified Figure 9, PAUSE Frame Format [changed Preamble byte count to 7 bytes].                                                                                                                                        |

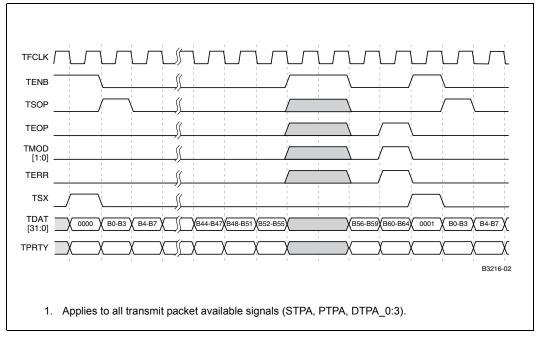

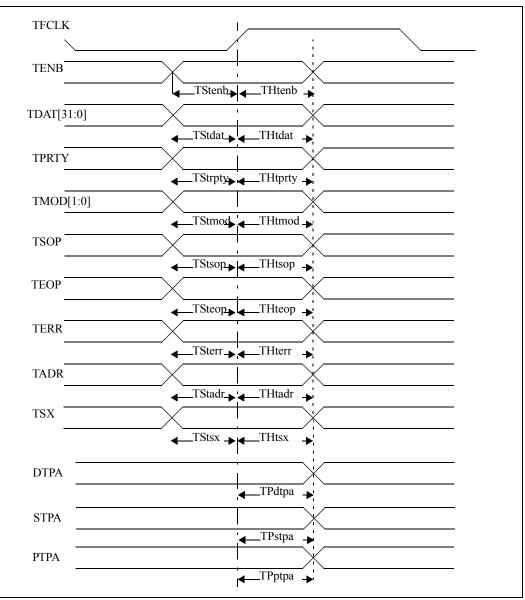

| page 82                                                              | Modified Figure 11, MPHY Transmit Logical Timing [updated TDAT[31:0]].                                                                                                                                                 |

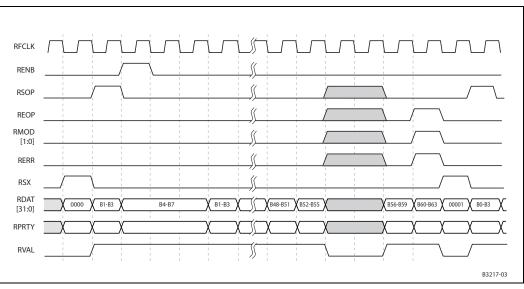

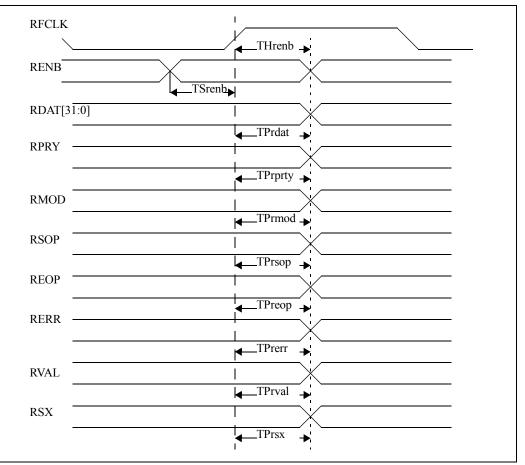

| page 82                                                              | Modified Figure 12, MPHY Receive Logical Timing [updated RDAT[31:0]].                                                                                                                                                  |

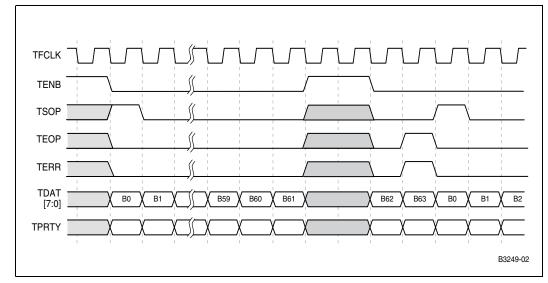

| page 85                                                              | Modified Figure 14, SPHY Transmit Logical Timing [updated TDAT[7:0]].                                                                                                                                                  |

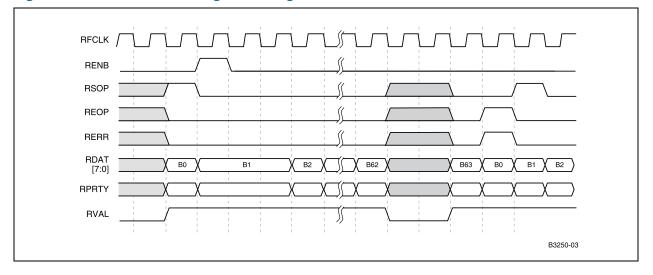

| page 85                                                              | Modified Figure 15, SPHY Receive Logical Timing [updated RDAT[7:0] and RPRTY].                                                                                                                                         |

| page 116                                                             | Modified Figure 31, <i>Read Timing Diagram - Asynchronous Interface</i> : changed uPx_ADD[12:0] to uPx_ADD[10:0].                                                                                                      |

| page 119                                                             | Added paragraphs two and three under Section 5.11, Loopback Modes.                                                                                                                                                     |

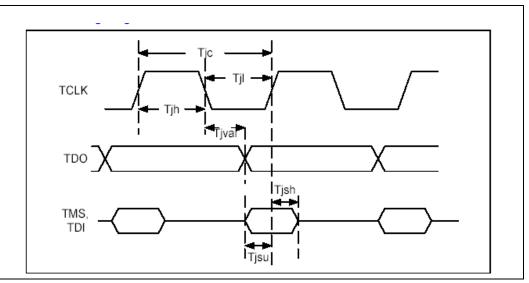

| page 122                                                             | Changed 3.3 V CMOS to 2.5 V CMOS under Section 5.12.5, JTAG Clock, on page 122.                                                                                                                                        |

| page 125                                                             | Added Section 6.2, Disable and Enable Port Sequences.                                                                                                                                                                  |

| page 130                                                             | Modified Table 44, <i>RGMII Power</i> [changed V <sub>OH</sub> , V <sub>OL</sub> , V <sub>IH</sub> , V <sub>IL</sub> minimum conditions to V <sub>DD</sub> and changed V <sub>IN</sub> value to V <sub>DD</sub> + .3]. |

| page 131                                                             | Modified Table 45, SPI3 Receive Interface Signal Parameters [changed RFCLK duty cycle to 45 min and 55 max; Changed Min for RFCLK frequency to 90].                                                                    |

| page 134                                                             | Modified Table 46, SPI3 Transmit Interface Signal Parameters [changed TFCLK duty cycle to 45 min and 55 max].                                                                                                          |

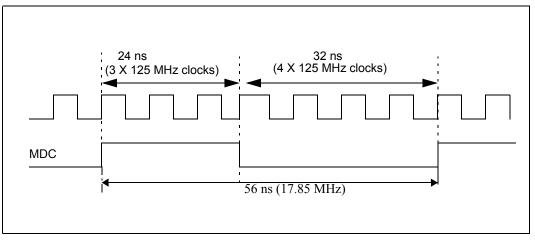

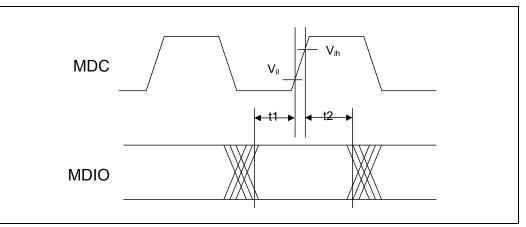

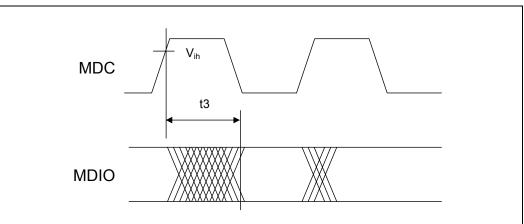

| page 140                                                             | Changed MDC to MDIO Output delay max for t3 for 2.5 MHz from 200 to 300 in Table 51, <i>MDIO Timing Parameters</i> , on page 140.                                                                                      |

| page 162                                                             | Modified Table 88, <i>TX Config Word (\$ Port_Index + 0x17)</i> [changed default value for the register from "0x0001A0" to "0x000001A0" and changed default value for bit 6 (Half Duplex) from 1 to 0].                |

|          | Revision Number: 008<br>Revision Date: August 1, 2005 (Sheet 2 of 2)                                                                                                                                                                                                                            |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Page #   | Description                                                                                                                                                                                                                                                                                     |

| page 173 | Modified Table 94, <i>PHY Control (\$ Port Index + 0x60)</i> [added "Need one-sentence descriptions of register" and register default value].                                                                                                                                                   |

| page 174 | Modified Table 95, <i>PHY Status (\$ Port Index + 0x61)</i> [added "Need one-sentence descriptions of register" and register default value].                                                                                                                                                    |

| page 175 | Modified Table 96, <i>PHY Identification 1 (\$ Port Index + 0x62)</i> [added "Need one-sentence descriptions of register" and register default value].                                                                                                                                          |

| page 175 | Modified Table 97, <i>PHY Identification 2 (\$ Port Index + 0x63)</i> [added "Need one-sentence descriptions of register" and register default value].                                                                                                                                          |

| page 176 | Modified Table 98, Auto-Negotiation Advertisement (\$ Port Index + 0x64) [added "Need one-sentence descriptions of register" and register default value].                                                                                                                                       |

| page 177 | Modified Table 99, Auto-Negotiation Link Partner Base Page Ability (\$ Port Index + 0x65) [added "Need one-<br>sentence descriptions of register" and register default value].                                                                                                                  |

| page 178 | Modified Table 100, <i>Auto-Negotiation Expansion (\$ Port Index + 0x66)</i> [added "Need one-sentence descriptions of register" and register default value].                                                                                                                                   |

| page 179 | Modified Table 101, Auto-Negotiation Next Page Transmit (\$ Port Index + 0x67) [added "Need one-sentence descriptions of register" and register default value].                                                                                                                                 |

| page 202 | Modified Table 142, <i>MDIO Single Read and Write Data (\$0x681)</i> [changed MDIO write data to "MDIO write data to external device"].                                                                                                                                                         |

| page 203 | Modified Table 145, <i>SPI3 Transmit and Global Configuration (\$0x700)</i> [changed default value for bits 3:0 from "0" to "1" and changed default value for entire register from "0x0020000F" to "0x00200000"].                                                                               |

| page 205 | Modified Table 146, <i>SPI3 Receive Configuration (\$0x701)</i> [changed default value for bits 11:8 from "0xF" to "0x1"].                                                                                                                                                                      |

| page 211 | Modified Table 153, Optical Module Control Ports 0 - 3 (\$0x79A) [changed default value for bits 16:13 from "0xF" to "0x1"].                                                                                                                                                                    |

| page 216 | Added Figure 57, FC-PBGA Package Diagram (Top and Side View), on page 216.                                                                                                                                                                                                                      |

| 229      | Added Section 9.4, "RoHS Compliance" on page 229.                                                                                                                                                                                                                                               |

|          | Revision Number: 007<br>Revision Date: March 24, 2004<br>(Sheet 1 of 5)                                                                                                                                                                                                                         |

| Page #   | Description                                                                                                                                                                                                                                                                                     |

| All      | Globally replaced GBIC with Optical Module Interface.                                                                                                                                                                                                                                           |

| All      | Globally edited signal names.                                                                                                                                                                                                                                                                   |

| All      | Globally changed SerDes and PLL analog power ball names as follows:<br>TXAVTT and RXAVTT changed to AVDD1P8_2<br>TXAV25 and RXAV25 changed to AVDD2P5_2<br>PLL1_VDDA and PLL2_VDDA changed to AVDD1P8_1<br>PLL3_VDDA changed to AVDD2P5_1<br>PLL1_GNDA, PLL2_GNDA, and PLL3_GNDA changed to GND |

| 1        | Reworded and rearranged the Product Features section on page one<br>Changed Jumbo frame support from "10 kbytes" to "9.6 KB".                                                                                                                                                                   |

| 21       | Changed heading to Section 2.0, "General Description" [was Section 2.0, "Block Diagram"].                                                                                                                                                                                                       |

| 23/37    | Reversed sections as follows:<br>Section 3.0, "Ball Assignments and Ball List Tables"<br>Section 4.0, "Ball Assignments and Signal Descriptions"                                                                                                                                                |

| Revision Number: 007<br>Revision Date: March 24, 2004<br>(Sheet 2 of 5) |                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Page #                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 24                                                                      | Modified Table 1 "Ball List in Alphanumeric Order by Signal Name":<br>Changed A10 from VCC to VDD<br>Changed C12 from VCC to VDD<br>Changed D11 from VCC to VDD<br>Changed J20 from GND to VDD<br>Changed Ball A1 from NC to No Pad.<br>Changed Balls A2, A3, A22, A23, A24, B1, B2, B23, B24, C1, C24, AB1, AB24, AC1, AC2, AC23, AC24, AD1,<br>AD2, AD3, AD22, AD23, AD24 from NC to No Ball.  |  |

| 30                                                                      | Modified Table 2 "Ball List in Alphanumeric Order by Ball Location"<br>Changed A10 from VCC to VDD<br>Changed C12 form VCC to VDD<br>Changed D11 from VCC to VDD<br>Changed J20 from GND to VDD<br>Changed Ball A1 from NC to No Pad.<br>Changed Balls A2, A3, A22, A23, A24, B1, B2, B23, B24, C1, C24, AB1, AB24, AC1, AC2, AC23, AC24, AD1,<br>AD2, AD3, AD22, AD23, AD24 from NC to No Ball. |  |

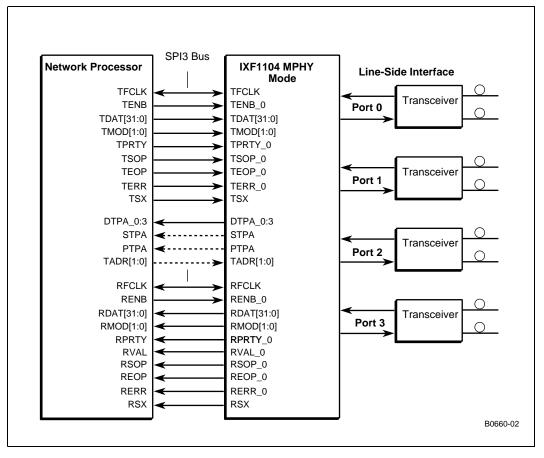

| 38                                                                      | Updated Figure 4 "Interface Signals" [modified SPI3 interface signals and added MPHY and SPHY categories; modified signal names].                                                                                                                                                                                                                                                                |  |

| 39                                                                      | Broke old Table 1, "IXF1104 Signal Descriptions" into the following:<br>Table 3 "SPI3 Interface Signal Descriptions" on page 39 through Table 14 "Power Supply Signal Descriptions"<br>on page 56                                                                                                                                                                                                |  |

| 39                                                                      | Modified Table 3 "SPI3 Interface Signal Descriptions" on page 39 [edited description for DTPA; added text to TFCLK description; added text to RFCLK description].                                                                                                                                                                                                                                |  |

| 50                                                                      | Modified Table 6 "RGMII Interface Signal Descriptions" [Added Ball Designators; added notes under descriptions].                                                                                                                                                                                                                                                                                 |  |

| 51                                                                      | Modified Table 7 "CPU Interface Signal Descriptions" [UPX_DATA[16]: deleted J10, added M10].                                                                                                                                                                                                                                                                                                     |  |

| 53                                                                      | Modified Table 9 "Optical Module Interface Signal Descriptions" [added Ball Designators].                                                                                                                                                                                                                                                                                                        |  |

| 54                                                                      | Modified Table 10 "MDIO Interface Signal Descriptions" [moved note from MDC to MDIO].                                                                                                                                                                                                                                                                                                            |  |

| 56                                                                      | Modified Table 14 "Power Supply Signal Descriptions" [added Ball Designators A4, A21, and AD21 to GND; added AVDD1P8_1, AVDD1P8_2, AVDD2P5_1, and AVDD2P5_2].                                                                                                                                                                                                                                    |  |

| 39                                                                      | Modified Section 4.3, "Signal Description Tables" [changed heading from "Signal Naming Conventions; added new headings Section 4.1.1, "Signal Name Conventions" and Section 4.1.2, "Register Address Conventions"; and added/enhanced material under headings.                                                                                                                                   |  |

| 58                                                                      | Added new Section 4.5, "Multiplexed Ball Connections" with Table 16 "Line Side Interface Multiplexed Balls" and Table 17 "SPI3 MPHY/SPHY Interface".                                                                                                                                                                                                                                             |  |

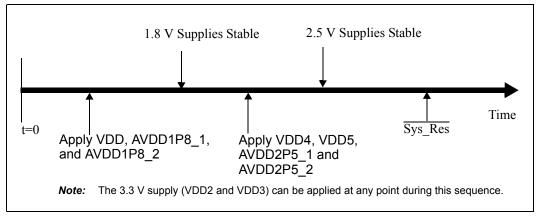

| 63                                                                      | Modified Section 4.7, "Power Supply Sequencing" [changed language under this section and added Section 4.7.1, "Power-Up Sequence" and Section 4.7.2, "Power-Down Sequence"].                                                                                                                                                                                                                     |  |

| 63                                                                      | Modified Table 5 "Power Supply Sequencing" [deleted 3.3 V Supplies Stable; changed Apply 1.8 V to VDD, AVDD1P8_1, and AVDD1P8_2; changed Apply 2.5 V to AVDD2P5_1 and AVDD2P5_2].                                                                                                                                                                                                                |  |

| 61                                                                      | Modified Table 18 "Definition of Output and Bi-directional Balls During Hardware Reset" [changed comments for Optical Modules].                                                                                                                                                                                                                                                                  |  |

| 64                                                                      | Modified Table 20 "Pull-Up/Pull-Down and Unused Ball Guidelines" [changed TRST_L to pull-down; added MDIO, UPX_RDY_L, I <sup>2</sup> C_DATA_3:0, and TX_DISABLE_3:0].                                                                                                                                                                                                                            |  |

| 64                                                                      | Added new Section 4.9, "Analog Power Filtering" [including Figure 6 "Analog Power Supply Filter Network" on page 65 and Table 21 "Analog Power Balls" on page 65].                                                                                                                                                                                                                               |  |

| 66                                                                      | Modified/edited text under Section 5.1, "Media Access Controller (MAC)" [rearranged and created new bullets].                                                                                                                                                                                                                                                                                    |  |

| 67                                                                      | Modified first paragraph under Section 5.1.1.1, "Padding of Undersized Frames on Transmit".                                                                                                                                                                                                                                                                                                      |  |

| 67                                                                      | Modified entire Section 5.1.1.3, "Filtering of Receive Packets".                                                                                                                                                                                                                                                                                                                                 |  |

| 68                                                                      | Added new Section 5.1.1.3.6, "Filter CRC Error Packets".                                                                                                                                                                                                                                                                                                                                         |  |

| Revision Number: 007<br>Revision Date: March 24, 2004<br>(Sheet 3 of 5) |                                                                                                                                                                                     |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Page #                                                                  | Description                                                                                                                                                                         |

| 69                                                                      | Added note under Table 22 "CRC Errored Packets Drop Enable Behavior".                                                                                                               |

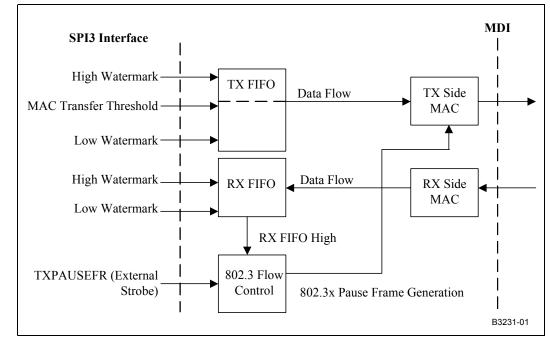

| 69                                                                      | Added new Section 5.1.2, "Flow Control" including Figure 7 "Packet Buffering FIFO", Figure 8 "Ethernet Frame Format", and Figure 9 "PAUSE Frame Format".                            |

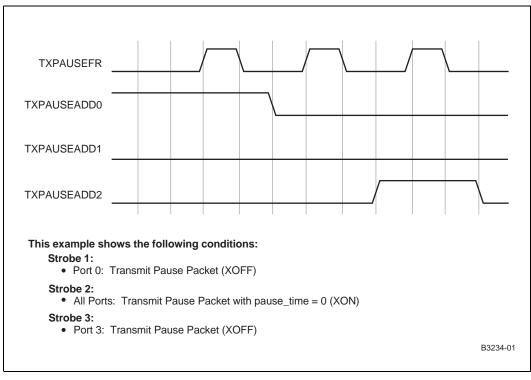

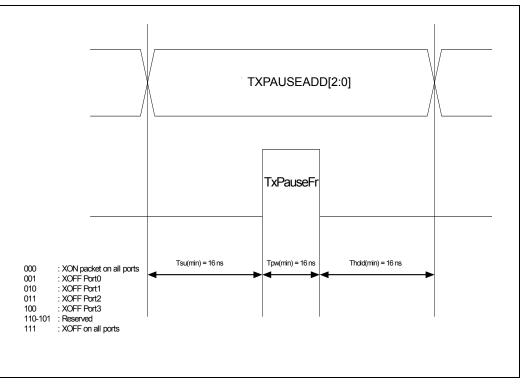

| 73                                                                      | Replaced Section 5.1.2.1.5, "Transmit Pause Control Interface" [added Table 23 "Valid Decodes for TXPAUSEADD[2:0]" and modified Table 10 "Transmit Pause Control Interface".        |

| 74                                                                      | Modified Figure 10 "Transmit Pause Control Interface"                                                                                                                               |

| 75                                                                      | Added note under Section 5.1.3.1, "Configuration".                                                                                                                                  |

| 76                                                                      | Added table note to Table 24 "Operational Mode Configuration Registers".                                                                                                            |

| 77                                                                      | Added note under Section 5.1.4.3, "Fiber Forced Mode".                                                                                                                              |

| 79                                                                      | Modified Section 5.1.6.2, "TX Statistics" [added text to third sentence in first paragraph].                                                                                        |

| 79                                                                      | Modified Section 5.1.6.3, "Loss-less Flow Control" [changed "two kilometers" to "five kilometers" in last sentence.                                                                 |

| 80                                                                      | Modified Section 5.1.7.1.2, "RX FIFO" [changed 10 KB to 9.6 KB; added text to last paragraph].                                                                                      |

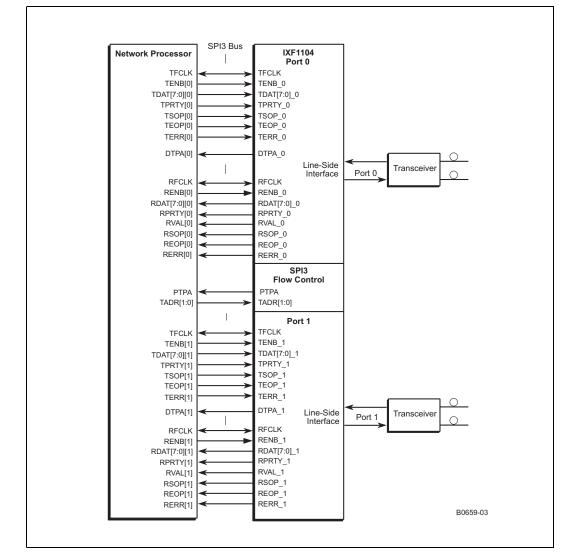

| 83                                                                      | Rewrote/replaced Section 5.2, "SPI3 Interface".                                                                                                                                     |

| 86                                                                      | Edited signal names in Figure 13 "MPHY 32-Bit Interface".                                                                                                                           |

| 90                                                                      | Edited signal names in Figure 16 "SPHY Connection for Two IXF1104 MAC Ports (8-Bit Interface)".                                                                                     |

| 91                                                                      | Added new Section 5.2.2.9, "SPI3 Flow Control".<br>[Removed old "Packet-Level and Byte-Level Transfers" section.}                                                                   |

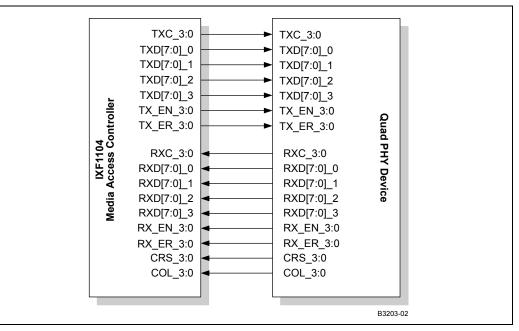

| 94                                                                      | Modified Figure 17 "MAC GMII Interconnect" [edited signal names].                                                                                                                   |

| NA                                                                      | Removed old Section 5.3.3 Electrical Requirements and Table 27 "Electrical Requirements" – changed Input high current Max from 40 to 15 and Input low current Min from -600 to -15. |

| 96                                                                      | Added a note under Section 5.4, "Reduced Gigabit Media Independent Interface (RGMII)".                                                                                              |

| 96                                                                      | Modified Figure 18 "RGMII Interface" [edited signal names].                                                                                                                         |

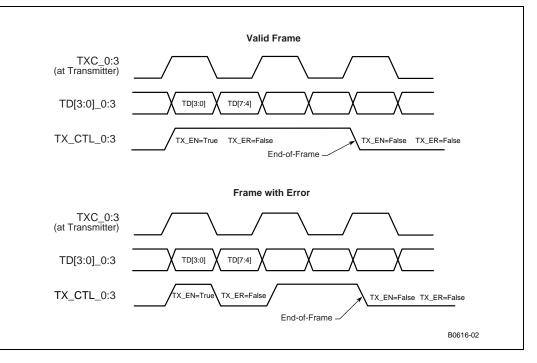

| 98                                                                      | Modified Figure 19 "TX_CTL Behavior" [changed signal names].                                                                                                                        |

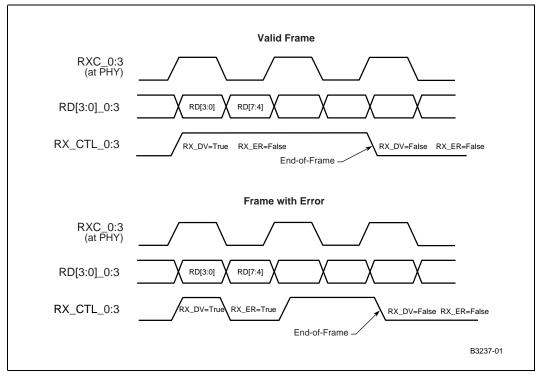

| 98                                                                      | Modified Figure 20 "RX_CTL Behavior" [changed signal names].                                                                                                                        |

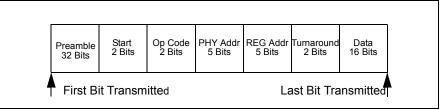

| 99                                                                      | Modified Section 5.5, "MDIO Control and Interface" [changed 3.3 us to 3.3 ms in fourth paragraph, third sentence].                                                                  |

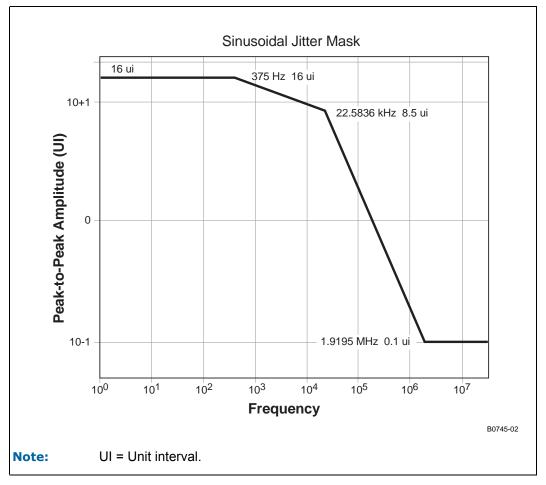

| 103                                                                     | Modified/replaced all text under Section 5.6, "SerDes Interface" on page 103 [added Table 29 "SerDes Driver TX Power Levels"].                                                      |

| NA                                                                      | Removed old Section 5.6.2.4 AC/DC Coupling.                                                                                                                                         |

| NA                                                                      | Removed old Section 5.6.2.9 System Jitter.                                                                                                                                          |

| 107                                                                     | Modified Table 30 "IXF1104 MAC-to-SFP Optical Module Interface Connections" [edited signal names].                                                                                  |

| 107                                                                     | Modified/replaced text and deleted old "Figure 19. Typical GBIC Module Functional Diagram" under Section 5.7, "Optical Module Interface"].                                          |

| 108                                                                     | Modified second sentence under Section 5.7.2.2.1, "MOD_DEF_0:3".                                                                                                                    |

| 109                                                                     | Modified second sentence under Section 5.7.2.2.3, "RX_LOS_0:3".                                                                                                                     |

| 109                                                                     | Removed third paragraph under Section 5.7.2.2.7, "RX_LOS_INT".                                                                                                                      |

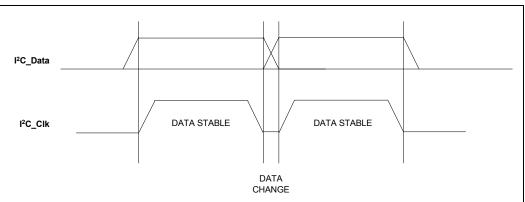

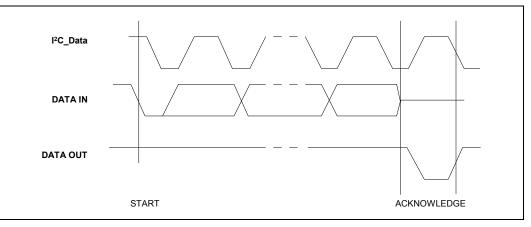

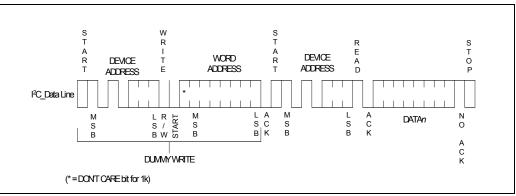

| 110                                                                     | Modified first and second paragraphs under Section 5.7.3, "I <sup>2</sup> C Module Configuration Interface".                                                                        |

| 111                                                                     | Modified Section 5.7.3.3, "I2C Write Operation" [edited portions of text].                                                                                                          |

| 116                                                                     | Modified Table 31 "LED Interface Signal Descriptions" [changed 0.5 MHz to 720 Hz for LED_CLK under Signal Description].                                                             |

| 119                                                                     | Modified Table 35 "LED Behavior (Fiber Mode)" [changed links under Description to "Link LED Enable (\$0x502)"].                                                                     |

| NA                                                                      | Removed old Figure 30 "CPU – External and Internal Connections".                                                                                                                    |

| Revision Number: 007<br>Revision Date: March 24, 2004<br>(Sheet 4 of 5) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Page #                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 123                                                                     | Modified Table 37 "Byte Swapper Behavior" [edited/added new values].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 123                                                                     | Modified second paragraph under Section 5.10, "TAP Interface (JTAG)"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

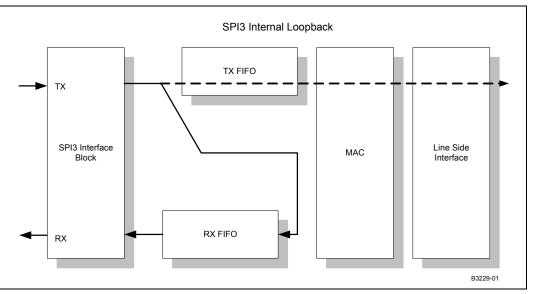

| 126                                                                     | Modified Figure 33 "SPI3 Interface Loopback Path".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

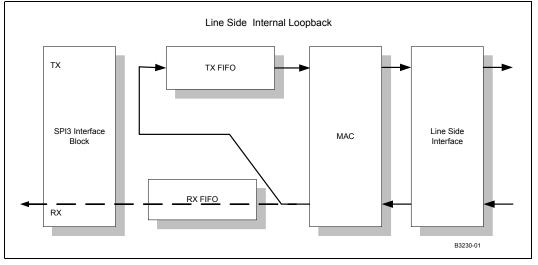

| 126                                                                     | Added note under Section 5.11.2, "Line Side Interface Loopback".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 127                                                                     | Modified Figure 34 "Line Side Interface Loopback Path".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 127                                                                     | Changed Section 5.12, "Clocks" [from GBIC output clock to I <sup>2</sup> C Clock].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 129                                                                     | Changed Section 5.12.6, "I2C Clock" [from GBIC Clock to I <sup>2</sup> C Clock].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 130                                                                     | Added new Section 6.0, "Applications".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 132                                                                     | Modified Table 39 "Absolute Maximum Ratings" [changed SerDes analog power to AVDD1P8_2 and AVDD2P5_2; changed "PLL1_VDDA and PLL2_VDDA to AVDD1P8_1; changed PLL3_VDDA to AVDD2P5_1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 133                                                                     | Modified Table 40 "Recommended Operating Conditions" [changed SerDes analog power to AVDD1P8_2 and AVDD2P5_2; changed "PLL1_VDDA and PLL2_VDDA to AVDD1P8_1; changed PLL3_VDDA to AVDD2P5_1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 134                                                                     | Modified Table 42 "SerDes Transmit Characteristics" [included SerDes power driver level information].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

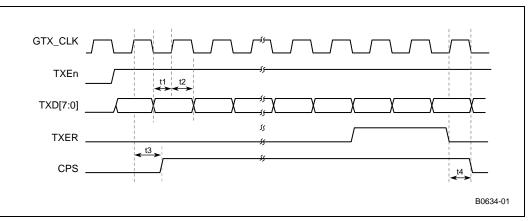

| 142                                                                     | Modified Table 49 "GMII 1000BASE-T Transmit Signal Parameters" (changed Min values for t1 and t2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 143                                                                     | Modified Table 50 "GMII 1000BASE-T Receive Signal Parameters" (changed Min values for t1 and t2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

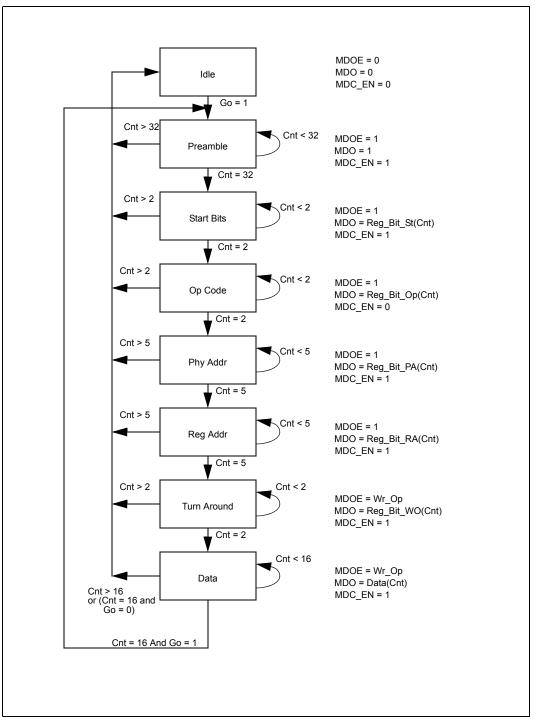

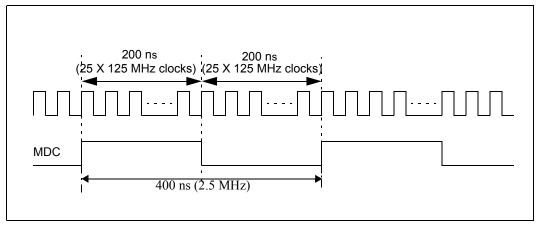

| 146                                                                     | Replaced old MDIO Timing diagram and table with Figure 43 "MDIO Write Timing Diagram", Figure 44 "MDIO Read Timing Diagram", and Table 52 "MDIO Timing Parameters".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

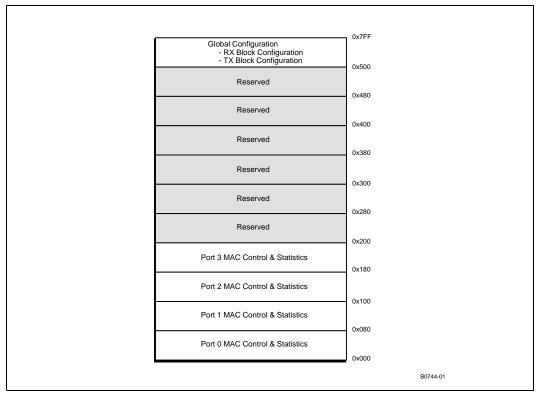

| 156                                                                     | Broke up the old Register Map into Table 59 "MAC Control Registers (\$ Port Index + Offset)", Table 60 "MAC<br>RX Statistics Registers (\$ Port Index + Offset)", Table 61 "MAC TX Statistics Registers (\$ Port Index + Offset)",<br>Table 62 "PHY Autoscan Registers (\$ Port Index + Offset)", Table 63 "Global Status and Configuration Registers<br>(\$ 0x500 - 0X50C)", Table 64 "RX FIFO Registers (\$ 0x580 - 0x5BF)", Table 65 "TX FIFO Registers (\$ 0x600 -<br>0x63E)", Table 66 "MDIO Registers (\$ 0x680 - 0x683)", Table 67 "SPI3 Registers (\$ 0x700 - 0x716)", Table 68<br>"SerDes Registers (\$ 0x780 - 0x798)", and Table 69 "Optical Module Registers (\$ 0x799 - 0x79F)". |

| 159                                                                     | Edited Table 63 "Global Status and Configuration Registers (\$ 0x500 - 0X50C)" [no offset].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 159                                                                     | Edited Table 64 "RX FIFO Registers (\$ 0x580 - 0x5BF)" [no offset].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 160                                                                     | Edited Table 65 "TX FIFO Registers (\$ 0x600 - 0x63E)" [no offset].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 161                                                                     | Edited Table 66 "MDIO Registers (\$ 0x680 - 0x683)" [no offset].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 161                                                                     | Edited Table 67 "SPI3 Registers (\$ 0x700 - 0x716)" [no offset].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 162                                                                     | Edited Table 68 "SerDes Registers (\$ 0x780 - 0x798)" [no offset].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 162                                                                     | Edited Table 69 "Optical Module Registers (\$ 0x799 - 0x79F)" [no offset].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 163                                                                     | Modified Table 71 "Desired Duplex (\$ Port_Index + 0x02)" [changed 100 Mbps to 1000 Mbps in register description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 167                                                                     | Modified Table 82 "MAC IF Mode and RGMII Speed (\$ Port_Index + 0x10)" [Added text to register description.]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 168                                                                     | Modified Table 84 "FC Enable (\$ Port_Index + 0x12)" [changed description for bits 1:0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 169                                                                     | Modified Table 88 "RX Config Word (\$ Port_Index + 0x16)" [edited Register Description text; changed description and type for bits 13:12].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 170                                                                     | Modified Table 89 "TX Config Word (\$ Port_Index + 0x17)" [edited description and type for bits 14, 13:12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 171                                                                     | Modified Table 90 "Diverse Config Write (\$ Port_Index + 0x18)" [edited description and type for bits 18:8; changed bits 3:1 to Reserved; added table note 2].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 172                                                                     | Renamed/modified Table 91 "RX Packet Filter Control (\$ Port_Index + 0x19)" [old register name - added RX to heading; added table note 2].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 174                                                                     | Modified Table 93 "MAC RX Statistics (\$ Port_Index + 0x20 - + 0x39)" [added note to RxPauseMacControlReceivedCounter description; edited note 3 and added note 4].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 178                                                                     | Modified Table 94 "MAC TX Statistics (\$ Port_Index +0x40 – +0x58)" [changed "1526-max" to "1523 - max frame size" for Txpkts1519toMaxOctets description].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Revision Number: 007<br>Revision Date: March 24, 2004<br>(Sheet 5 of 5) |                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Page #                                                                  | Description                                                                                                                                                                                                                                                                                                            |

| 193                                                                     | Modified Table 113 "RX FIFO High Watermark Port 0 (\$0x580)", Table 114 "RX FIFO High Watermark Port 1 (\$0x581)", Table 115 "RX FIFO High Watermark Port 2 (\$0x582)", and Table 116 "RX FIFO High Watermark Port 3 (\$0x583)" [changed bits 11:0 description].                                                       |

| 195                                                                     | Renamed and modified Table 121 "RX FIFO Overflow Frame Drop Counter Ports 0 - 3 (\$0x594 – 0x597)"<br>[old register name: RX FIFO Number of Frames Removed Ports 0 to 3; renamed bit names to match register<br>names; removed "This register gets updated after one cycle of sw reset is applied" under Description]. |

| 196                                                                     | Modified Table 123 "RX FIFO Errored Frame Drop Enable (\$0x59F)" [renamed bit names to match register name].                                                                                                                                                                                                           |

| 198                                                                     | Renamed/modified Table 125 "RX FIFO Errored Frame Drop Counter Ports 0 - 3 (\$0x5A2 - 0x5A5)" on page 198 [older register name: RX FIFO Dropped Packet Counter for Ports 0 to 3; renamed bit names to match register name].                                                                                            |

| 199                                                                     | Modified Table 126 "RX FIFO SPI3 Loopback Enable for Ports 0 - 3 (\$0x5B2)" [renamed heading and bit name; changed description and type for bits 7:0].                                                                                                                                                                 |

| 201                                                                     | Renamed Table 128 "RX FIFO Transfer Threshold Port 0 (\$0x5B8)" on page 201 [from "RX FIFO Jumbo Packet Size; changed bit names and edited/added text under description].                                                                                                                                              |

| 207                                                                     | Modified Table 136 "Loop RX Data to TX FIFO (Line-Side Loopback) Ports 0 - 3 (\$0x61F)" [renamed heading and bit name].                                                                                                                                                                                                |

| 208                                                                     | Modified Table 138 "TX FIFO Overflow Frame Drop Counter Ports 0 - 3 (\$0x621 – 0x624)" [renamed from TX FIFO Number of Frames Removed Ports 3 - 0].                                                                                                                                                                    |

| 209                                                                     | Modified Table 139 "TX FIFO Errored Frame Drop Counter Ports 0 - 3 (\$0x625 – 0x629)" [renamed from TX FIFO Number of Dropped Packets Ports 0-3 and text under the description].                                                                                                                                       |

| 210                                                                     | Modified Table 141 "TX FIFO Port Drop Enable (\$0x63D)" [changed description for bits 3:0].                                                                                                                                                                                                                            |

| 211                                                                     | Modified Table 142 "MDIO Single Command (\$0x680)" [changed default; changed description and default for bits 9:8; changed default for bits 4:0].                                                                                                                                                                      |

| 212                                                                     | Modified Table 144 "Autoscan PHY Address Enable (\$0x682)" [added note to register description].                                                                                                                                                                                                                       |

| 213                                                                     | Modified Table 146 "SPI3 Transmit and Global Configuration (\$0x700)" [broke out bits 19:16, 7:4, and 3:0 and changed description text].                                                                                                                                                                               |

| 215                                                                     | Modified Table 147 "SPI3 Receive Configuration (\$0x701)" [broke out bits and modified all text adding SPHY and MPHY modes].                                                                                                                                                                                           |