# Low Jitter Clock Generator with 14 LVPECL/LVDS/HSTL/29 LVCMOS Outputs

AD9523-1

#### **FEATURES**

Output frequency: <1 MHz to 1 GHz

Start-up frequency accuracy: <±100 ppm (determined by

VCXO reference accuracy)

Zero delay operation

Input-to-output edge timing: <150 ps

**Dual VCO dividers**

14 outputs: configurable LVPECL, LVDS, HSTL, and LVCMOS 14 dedicated output dividers with jitter-free adjustable delay

Adjustable delay: 63 resolution steps of  $\frac{1}{2}$  period of VCO

output divider

Output-to-output skew: <50 ps

**Duty cycle correction for odd divider settings**

Automatic synchronization of all outputs on power-up

Absolute output jitter: <150 fs at 122.88 MHz

Integration range: 12 kHz to 20 MHz

Broadband timing jitter: 124 fs

**Digital lock detect**

**Nonvolatile EEPROM stores configuration settings**

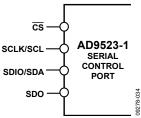

SPI- and I<sup>2</sup>C-compatible serial control port

**Dual PLL architecture**

PLL<sub>1</sub>

Low bandwidth for reference input clock cleanup with external VCXO

Phase detector rate of 300 kHz to 75 MHz

**Redundant reference inputs**

Auto and manual reference switchover modes

Revertive and nonrevertive switching

Loss of reference detection with holdover mode

Low noise LVCMOS output from VCXO used for RF/IF synthesizers

PLL2

Phase detector rate of up to 250 MHz

Integrated low noise VCO

#### **APPLICATIONS**

LTE and multicarrier GSM base stations

Wireless and broadband infrastructure

**Medical instrumentation**

Clocking high speed ADCs, DACs, DDCs, DUCs, MxFEs

Low jitter, low phase noise clock distribution

Clock generation and translation for SONET, 10Ge, 10G FC, and other 10 Gbps protocols

Forward error correction (G.710)

High performance wireless transceivers

ATE and high performance instrumentation

#### Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

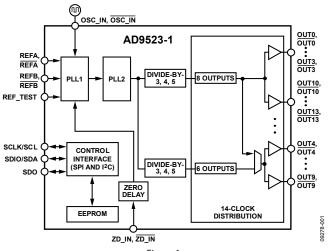

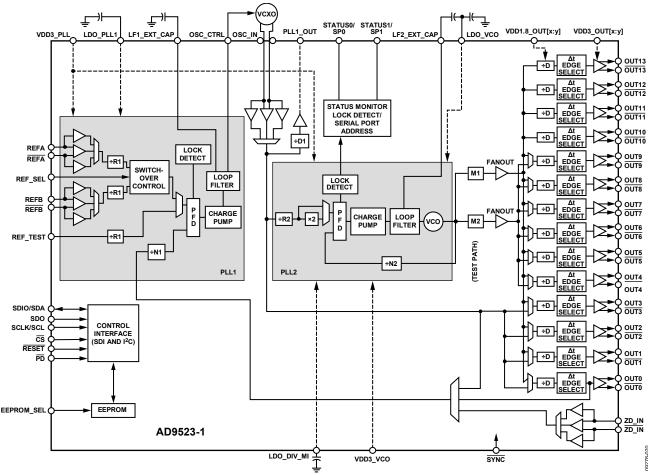

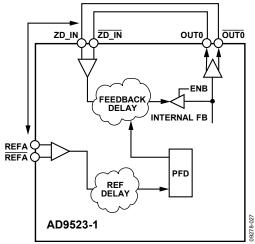

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

#### **GENERAL DESCRIPTION**

The AD9523-1 provides a low power, multi-output, clock distribution function with low jitter performance, along with an on-chip PLL and VCO with two VCO dividers. The on-chip VCO tunes from 2.94 GHz to 3.1 GHz.

The AD9523-1 is defined to support the clock requirements for long term evolution (LTE) and multicarrier GSM base station designs. It relies on an external VCXO to provide the reference jitter cleanup to achieve the restrictive low phase noise requirements necessary for acceptable data converter SNR performance.

The input receivers, oscillator, and zero delay receiver provide both single-ended and differential operation. When connected to a recovered system reference clock and a VCXO, the device generates 14 low noise outputs with a range of 1 MHz to 1 GHz, and one dedicated buffered output from the input PLL (PLL1). The frequency and phase of one clock output relative to another clock output can be varied by means of a divider phase select function that serves as a jitter-free, coarse timing adjustment in increments that are equal to half the period of the signal coming out of the VCO.

An in-package EEPROM can be programmed through the serial interface to store user-defined register settings for power-up and chip reset.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2010–2011 Analog Devices, Inc. All rights reserved.

# **TABLE OF CONTENTS**

| Features                                                | Input/Output Termination Recommendations       | 19 |

|---------------------------------------------------------|------------------------------------------------|----|

| Applications1                                           | Terminology                                    | 20 |

| Functional Block Diagram1                               | Theory of Operation                            | 21 |

| General Description1                                    | Detailed Block Diagram                         | 21 |

| Revision History                                        | Overview                                       | 21 |

| Specifications                                          | Component Blocks—Input PLL (PLL1)              | 22 |

| Conditions                                              | Component Blocks—Output PLL (PLL2)             |    |

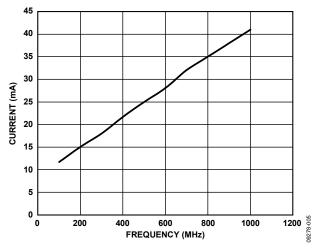

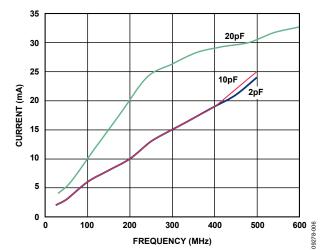

| Supply Current                                          | Clock Distribution                             |    |

| Power Dissipation                                       | Zero Delay Operation                           |    |

| REFA, REFA, REFB, REFB, OSC_IN, OSC_IN, and ZD_IN,      | Serial Control Port                            |    |

| ZD_IN Input Characteristics                             | SPI/I <sup>2</sup> C Port Selection            |    |

| OSC_CTRL Output Characteristics 6                       | I <sup>2</sup> C Serial Port Operation         |    |

| REF_TEST Input Characteristics                          | SPI Serial Port Operation                      |    |

| PLL1 Output Characteristics                             | SPI Instruction Word (16 Bits)                 |    |

| OUT0, OUT0 to OUT13, OUT13 Distribution Output          | SPI MSB/LSB First Transfers                    |    |

| Characteristics                                         | EEPROM Operations                              |    |

| Timing Alignment Characteristics 8                      | Writing to the EEPROM                          |    |

| Jitter and Noise Characteristics                        | Reading from the EEPROM                        |    |

| PLL2 Characteristics                                    | Programming the EEPROM Buffer Segment          |    |

| Logic Input Pins—PD, SYNC, RESET, EEPROM_SEL,           | Power Dissipation and Thermal Considerations   |    |

| REF_SEL9                                                | Clock Speed and Driver Mode                    |    |

| Status Output Pins—STATUS1, STATUS010                   | Evaluation of Operating Conditions             |    |

| Serial Control Port—SPI Mode10                          |                                                |    |

| Serial Control Port—I <sup>2</sup> C Mode11             | Thermally Enhanced Package Mounting Guidelines |    |

| Absolute Maximum Ratings12                              | Control Registers                              |    |

| Thermal Resistance12                                    | Control Register Map                           |    |

| ESD Caution12                                           | Control Register Map Bit Descriptions          |    |

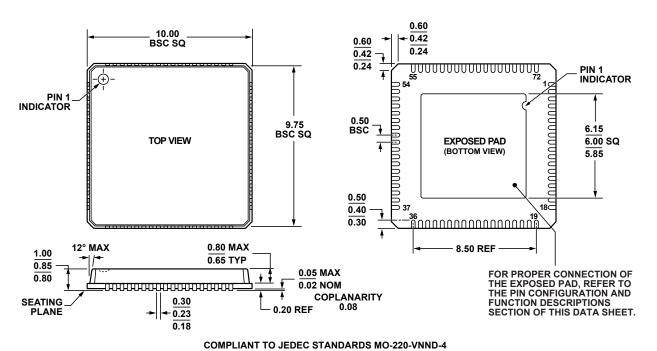

| Pin Configuration and Function Descriptions             | Outline Dimensions                             |    |

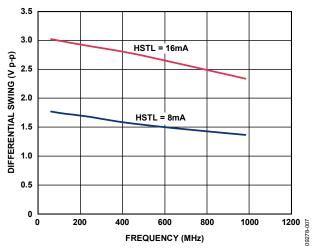

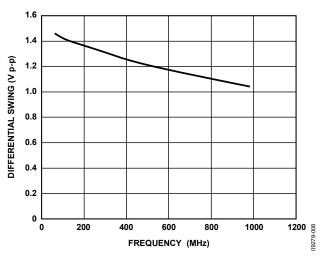

| Typical Performance Characteristics                     | Ordering Guide                                 | 58 |

| REVISION HISTORY                                        |                                                |    |

| 3/11—Rev. A to Rev. B                                   | 12/10—Rev. 0 to Rev. A                         |    |

| Added Table Summary, Table 8                            | Changes to General Description Section         | 1  |

| Changes to Figure 24                                    | Changes to Frequency Range, Table 11           |    |

| Changes to EEPROM Operations Section and Writing to the | Changes to PLL2 General Description Section    | 23 |

| EEPROM Section                                          | Changes to Table 47, Address 0x0F3, Bit 1      | 48 |

| Changes to Addr (Hex) 0x01A, Bits[4:3], Table 3040      | 10/10 P 11 0 T 11/17                           |    |

| Changes to Bits $[4\cdot3]$ . Table 40 47               | 10/10—Revision 0: Initial Version              |    |

# **SPECIFICATIONS**

$f_{VCXO} = 122.88$  MHz single-ended, REFA and REFB on differential at 30.72 MHz,  $f_{VCO} = 2949.12$  MHz, doubler is on, unless otherwise noted. Typical is given for VDD = 3.3 V  $\pm$  5%, and  $T_A = 25$ °C, unless otherwise noted. Minimum and maximum values are given over the full VDD and  $T_A = 40$ °C to +85°C) variation, as listed in Table 1.

#### **CONDITIONS**

Table 1.

| Parameter                                               | Min   | Тур | Max   | Unit | Test Conditions/Comments |

|---------------------------------------------------------|-------|-----|-------|------|--------------------------|

| SUPPLY VOLTAGE                                          |       |     |       |      |                          |

| VDD3_PLL, Supply Voltage for PLL1 and PLL2              |       | 3.3 | 3.465 | V    | 3.3 V ± 5%               |

| VDD3_VCO, Supply Voltage for VCO                        |       | 3.3 | 3.465 | V    | 3.3 V ± 5%               |

| VDD3_REF, Supply Voltage Clock Output Drivers Reference | 3.135 | 3.3 | 3.465 | V    | 3.3 V ± 5%               |

| VDD3_OUT[x:y], 1 Supply Voltage Clock Output Drivers    | 3.135 | 3.3 | 3.465 | ٧    | 3.3 V ± 5%               |

| VDD1.8_OUT[x:y],1 Supply Voltage Clock Dividers         | 1.768 | 1.8 | 1.832 | ٧    | 1.8 V ± 5%               |

| TEMPERATURE RANGE, TA                                   | -40   | +25 | +85   | °C   |                          |

<sup>1</sup> x and y are the pair of differential outputs that share the same power supply. For example, VDD3\_OUT[0:1] is Supply Voltage Clock Output OUT0, OUT0 (Pin 68 and Pin 67, respectively) and Supply Voltage Clock Output OUT1, OUT1 (Pin 65 and Pin 64, respectively).

#### **SUPPLY CURRENT**

Table 2.

| Parameter                                               | Min | Тур  | Max  | Unit | Test Conditions/Comments                                                                                                                        |

|---------------------------------------------------------|-----|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| SUPPLIES OTHER THAN CLOCK OUTPUT DRIVERS                |     |      |      |      |                                                                                                                                                 |

| VDD3_PLL, Supply Voltage for PLL1 and PLL2              |     | 37   | 41.9 | mA   | Decreases by 9 mA typical if REFB is turned off                                                                                                 |

| VDD3_VCO, Supply Voltage for VCO and VCO Divider M1     |     | 70   | 75.8 | mA   | All outputs use VCO Divider M1                                                                                                                  |

| VDD3_REF, Supply Voltage Clock Output Drivers Reference |     |      |      |      |                                                                                                                                                 |

| VCO Divider M1 Enabled                                  |     |      |      |      |                                                                                                                                                 |

| LVPECL Mode, LVDS Mode                                  |     | 4    | 5.1  | mA   | Use VCO Divider M1; only one output driver is turned on; for each additional output that is turned on, the current increments by 1.2 mA maximum |

| HSTL Mode, CMOS Mode                                    |     | 3    | 3.6  | mA   | Use VCO Divider M1; values are independent of the number of outputs turned on                                                                   |

| VCO Divider M2 Enabled                                  |     |      |      |      |                                                                                                                                                 |

| LVPECL Mode, LVDS Mode                                  |     | 26   | 30.1 | mA   | Use VCO Divider M2; only one output driver is turned on; for each additional output that is turned on, the current increments by 1.2 mA maximum |

| HSTL Mode, CMOS Mode                                    |     | 24.5 | 28.6 | mA   | Use VCO Divider M2; values are independent of the number of outputs turned on                                                                   |

| VDD1.8_OUT[x:y],1 Supply Voltage Clock Dividers         |     | 3.2  | 5.8  | mA   | Current for each divider: f = 122.88 MHz                                                                                                        |

| VDD1.8_OUT[x:y],1 Supply Voltage Clock Dividers         |     | 6.4  | 12   | mA   | Current for each divider: f = 983.04 MHz                                                                                                        |

| CLOCK OUTPUT DRIVERS—LOWER POWER MODE OFF               |     |      |      |      | Channel x control register, Bit 4 = 0                                                                                                           |

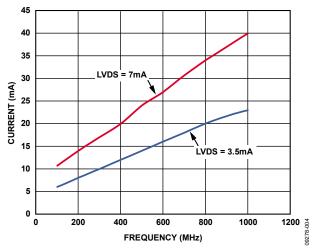

| LVDS Mode, 7 mA                                         |     |      |      |      |                                                                                                                                                 |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers     |     | 11.5 | 13.2 | mA   | f = 122.88 MHz                                                                                                                                  |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers     |     | 40   | 45   | mA   | f = 983.04 MHz                                                                                                                                  |

| LVDS Mode, 3.5 mA                                       |     |      |      |      |                                                                                                                                                 |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers     |     | 6.5  | 7.5  | mA   | f = 122.88 MHz                                                                                                                                  |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers     |     | 23   | 26.3 | mA   | f = 983.04 MHz                                                                                                                                  |

| LVPECL Mode                                             |     |      |      |      |                                                                                                                                                 |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers     |     | 13   | 14.4 | mA   | f = 122.88 MHz                                                                                                                                  |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers     |     | 41   | 46.5 | mA   | f = 983.04 MHz                                                                                                                                  |

| Parameter                                           | Min | Тур  | Max  | Unit | Test Conditions/Comments              |

|-----------------------------------------------------|-----|------|------|------|---------------------------------------|

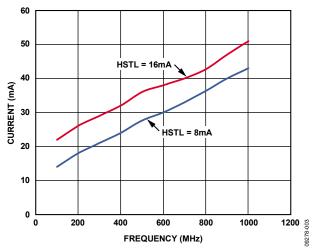

| HSTL Mode, 16 mA                                    |     |      |      |      |                                       |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers |     | 20   | 24.2 | mA   | f = 122.88 MHz                        |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers |     | 50   | 59.1 | mA   | f = 983.04 MHz                        |

| HSTL Mode, 8 mA                                     |     |      |      |      |                                       |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers |     | 14   | 16.7 | mA   | f = 122.88 MHz                        |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers |     | 42.5 | 49   | mA   | f = 983.04 MHz                        |

| CMOS Mode (Single-Ended)                            |     |      |      |      |                                       |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers |     | 2    | 2.4  | mΑ   | f = 15.36 MHz, 10 pF Load             |

| CLOCK OUTPUT DRIVERS—LOWER POWER MODE ON            |     |      |      |      | Channel x control register, Bit 4 = 1 |

| LVDS Mode, 7 mA                                     |     |      |      |      |                                       |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers |     | 10   | 10.8 | mA   | f = 122.88 MHz                        |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers |     | 27   | 29.8 | mA   | f = 983.04 MHz                        |

| LVDS Mode, 3.5 mA                                   |     |      |      |      |                                       |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers |     | 6.5  | 7.5  | mA   | f = 122.88 MHz                        |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers |     | 23   | 26.3 | mA   | f = 983.04 MHz                        |

| LVPECL Mode                                         |     |      |      |      |                                       |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers |     | 11   | 12.4 | mA   | f = 122.88 MHz                        |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers |     | 28   | 31.2 | mA   | f = 983.04 MHz                        |

| HSTL Mode, 16 mA                                    |     |      |      |      |                                       |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers |     | 20   | 24.3 | mA   | f = 122.88 MHz                        |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers |     | 50   | 59.1 | mA   | f = 983.04 MHz                        |

| HSTL Mode, 8 mA                                     |     |      |      |      |                                       |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers |     | 11   | 12.7 | mΑ   | f = 122.88 MHz                        |

| VDD3_OUT[x:y],1 Supply Voltage Clock Output Drivers |     | 27   | 31.8 | mΑ   | f = 983.04 MHz                        |

<sup>1</sup> x and y are the pair of differential outputs that share the same power supply. For example, VDD3\_OUT[0:1] is Supply Voltage Clock Output OUT0, OUT0 (Pin 68 and Pin 67, respectively) and Supply Voltage Clock Output OUT1, OUT1 (Pin 65 and Pin 64, respectively).

#### **POWER DISSIPATION**

Table 3.

| Parameter                                              | Min | Тур                  | Max           | Unit     | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------|-----|----------------------|---------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER DISSIPATION                                      |     |                      |               |          | Does not include power dissipated in termination resistors                                                                                                                                                                                                                                                                                          |

| Typical Configuration                                  |     | 898                  | 984.7         | mW       | Clock distribution outputs running as follows: 7 LVPECL at 122.88 MHz, 3 LVDS (3.5 mA) at 61.44 MHz, 3 LVDS (3.5 mA) at 245.76 MHz, 1 single-ended CMOS 10 pF load at 122.88 MHz, 1 differential input reference at 30.72 MHz; $f_{VCXO} = 122.88$ MHz, $f_{VCXO} = 2949.12$ MHz, VCO Divider M1 at 3, and VCO Divider M2 is off; PLL2 BW = 530 kHz |

| PD, Power-Down                                         |     | 74                   | 98.2          | mW       | PD pin pulled low, with typical configuration conditions                                                                                                                                                                                                                                                                                            |

| INCREMENTAL POWER DISSIPATION                          |     |                      |               |          |                                                                                                                                                                                                                                                                                                                                                     |

| Base Typical Configuration                             |     | 393                  | 434.7         | mW       | Absolute total power with clock distribution; 1 LVPECL output (OUT0) running at 122.88 MHz; 1 differential input reference at 30.72 MHz; $f_{VCXO} = 122.88$ MHz, $f_{VCXO} = 2949.12$ MHz, VCO Divider M1 at 3; VCO Divider M2 is off                                                                                                              |

| Switched to One Input,<br>Reference Single-Ended Mode  |     | -28.5                | -8            | mW       | Running at 30.72 MHz                                                                                                                                                                                                                                                                                                                                |

| Switched to Two Inputs,<br>Reference Differential Mode |     | 26                   | 44.6          | mW       | Running at 30.72 MHz                                                                                                                                                                                                                                                                                                                                |

| Switched to Two Inputs,<br>Reference Single-Ended Mode |     | -27.5                | -5.1          | mW       | Running at 30.72 MHz                                                                                                                                                                                                                                                                                                                                |

| VCO Divider M2                                         |     | 76                   | 88.3          | mW       | Incremental power increase VCO Divider M2 (OUT4) from base typical                                                                                                                                                                                                                                                                                  |

| Output Distribution, Driver On LVDS Mode               |     |                      |               |          | Incremental power increase (OUT1) from base typical                                                                                                                                                                                                                                                                                                 |

| 3.5 mA                                                 |     | 29                   | 34.8          | mW       | Single 3.5 mA LVDS output at 122.88 MHz                                                                                                                                                                                                                                                                                                             |

|                                                        |     | 88                   | 105.6         | mW       | Single 3.5 mA LVDS output at 983.04 MHz                                                                                                                                                                                                                                                                                                             |

| 7 mA                                                   |     | 43                   | 50            | mW       | Single 7 mA LVDS output at 122.88 MHz                                                                                                                                                                                                                                                                                                               |

|                                                        |     | 141                  | 164           | mW       | Single 7 mA LVDS output at 983.04 MHz                                                                                                                                                                                                                                                                                                               |

| LVPECL Mode                                            |     | 46                   | 51            | mW       | Single LVPECL output at 122.88 MHz                                                                                                                                                                                                                                                                                                                  |

|                                                        |     | 144                  | 159           | mW       | Single LVPECL output at 983.04 MHz                                                                                                                                                                                                                                                                                                                  |

| HSTL Mode                                              |     |                      |               |          |                                                                                                                                                                                                                                                                                                                                                     |

| 8 mA                                                   |     | 44                   | 51            | mW       | Single 8 mA HSTL output at 122.88 MHz                                                                                                                                                                                                                                                                                                               |

|                                                        |     | 143                  | 165           | mW       | Single 8 mA HSTL output at 983.04 MHz                                                                                                                                                                                                                                                                                                               |

| 16 mA                                                  |     | 48                   | 55            | mW       | Single 16 mA HSTL output at 122.88 MHz                                                                                                                                                                                                                                                                                                              |

|                                                        |     | 153                  | 176           | mW       | Single 16 mA HSTL output at 983.04 MHz                                                                                                                                                                                                                                                                                                              |

| CMOS Mode                                              |     | 6.6                  | 7.9           | mW       | Single 3.3 V CMOS output at 15.36 MHz                                                                                                                                                                                                                                                                                                               |

|                                                        |     | 9.9                  | 11.9          | mW       | Dual complementary 3.3 V CMOS output at 15.36 MHz                                                                                                                                                                                                                                                                                                   |

|                                                        |     | 9.9                  | 11.9          | mW       | Dual in-phase 3.3 V CMOS output at 15.36 MHz                                                                                                                                                                                                                                                                                                        |

| Output Distribution, Driver On                         |     |                      |               |          | Lower power mode on, (Channel x control register, Bit 4 = 1)                                                                                                                                                                                                                                                                                        |

| LVDS Mode                                              |     |                      |               |          |                                                                                                                                                                                                                                                                                                                                                     |

| 3.5 mA                                                 |     | 28.5                 | 33.6          | mW       | Single 3.5 mA LVDS output at 122.88 MHz                                                                                                                                                                                                                                                                                                             |

|                                                        |     | 88                   | 105.6         | mW       | Single 3.5 mA LVDS output at 983.04 MHz                                                                                                                                                                                                                                                                                                             |

| 7 mA                                                   |     | 37                   | 42.9          | mW       | Single 7 mA LVDS output at 122.88 MHz                                                                                                                                                                                                                                                                                                               |

| IV/DECLAM I                                            |     | 98                   | 113.7         | mW       | Single 7 mA LVDS output at 983.04 MHz                                                                                                                                                                                                                                                                                                               |

| LVPECL Mode                                            |     | 40.5                 | 46            | mW       | Single LVPECL output at 122.88 MHz                                                                                                                                                                                                                                                                                                                  |

| HCTI Modo                                              |     | 100                  | 110           | mW       | Single LVPECL output at 983.04 MHz                                                                                                                                                                                                                                                                                                                  |

| HSTL Mode                                              |     | 24                   | 20.1          | \^/      | Cincelo O as A LICTL a vitas et at 122 00 MHz                                                                                                                                                                                                                                                                                                       |

| 8 mA                                                   |     | 34<br>94             | 39.1<br>108.1 | mW<br>mW | Single 8 mA HSTL output at 122.88 MHz Single 8 mA HSTL output at 983.04 MHz                                                                                                                                                                                                                                                                         |

| 16 mA                                                  |     | 9 <del>4</del><br>48 | 55.2          | mW       | Single 16 mA HSTL output at 122.88 MHz                                                                                                                                                                                                                                                                                                              |

| IOTIIA                                                 |     | 46<br>153            | 55.2<br>176   | mW       | Single 16 mA HSTL output at 122.66 MHz                                                                                                                                                                                                                                                                                                              |

# REFA, REFB, REFB, OSC\_IN, OSC\_IN, AND ZD\_IN, ZD\_IN INPUT CHARACTERISTICS

Table 4.

| Parameter                                                      | Min   | Тур | Max   | Unit   | Test Conditions/Comments                                                                                                                                                        |

|----------------------------------------------------------------|-------|-----|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIFFERENTIAL MODE                                              |       |     |       |        |                                                                                                                                                                                 |

| Input Frequency Range                                          |       |     | 400   | MHz    |                                                                                                                                                                                 |

| Input Slew Rate (OSC_IN)                                       | 400   |     |       | V/µs   | Minimum limit imposed for jitter performance                                                                                                                                    |

| Common-Mode Internally<br>Generated Input Voltage              | 0.6   | 0.7 | 0.8   | V      |                                                                                                                                                                                 |

| Input Common-Mode Range                                        | 1.025 |     | 1.475 | V      | For dc-coupled LVDS (maximum swing)                                                                                                                                             |

| Differential Input Voltage,<br>Sensitivity Frequency < 250 MHz | 100   |     |       | mV p-p | Capacitive coupling required; can accommodate single-ended input by ac grounding of unused input; instantaneous voltage on either pin must not exceed the 1.8 V dc supply rails |

| Differential Input Voltage,<br>Sensitivity Frequency > 250 MHz | 200   |     |       | mV p-p | Capacitive coupling required; can accommodate single-ended input by ac grounding of unused input; instantaneous voltage on either pin must not exceed the 1.8 V dc supply rails |

| Differential Input Resistance                                  |       | 4.8 |       | kΩ     |                                                                                                                                                                                 |

| Differential Input Capacitance                                 |       | 1   |       | pF     |                                                                                                                                                                                 |

| Duty Cycle                                                     |       |     |       |        | Duty cycle limits are set by pulse width high and pulse width low                                                                                                               |

| Pulse Width Low                                                | 1     |     |       | ns     |                                                                                                                                                                                 |

| Pulse Width High                                               | 1     |     |       | ns     |                                                                                                                                                                                 |

| CMOS MODE, SINGLE-ENDED INPUT                                  |       |     |       |        |                                                                                                                                                                                 |

| Input Frequency Range                                          |       |     | 250   | MHz    |                                                                                                                                                                                 |

| Input High Voltage                                             | 2.0   |     |       | V      |                                                                                                                                                                                 |

| Input Low Voltage                                              |       |     | 0.8   | V      |                                                                                                                                                                                 |

| Input Capacitance                                              |       | 1   |       | рF     |                                                                                                                                                                                 |

| Duty Cycle                                                     |       |     |       |        | Duty cycle limits are set by pulse width high and pulse width low                                                                                                               |

| Pulse Width Low                                                | 1.6   |     |       | ns     |                                                                                                                                                                                 |

| Pulse Width High                                               | 1.6   |     |       | ns     |                                                                                                                                                                                 |

# OSC\_CTRL OUTPUT CHARACTERISTICS

#### Table 5.

| Parameter      | Min             | Тур | Max | Unit | Test Conditions/Comments        |

|----------------|-----------------|-----|-----|------|---------------------------------|

| OUTPUT VOLTAGE |                 |     |     |      |                                 |

| High           | VDD3_PLL - 0.15 |     |     | V    | $R_{LOAD} > 20 \text{ k}\Omega$ |

| Low            |                 |     | 150 | mV   |                                 |

# **REF\_TEST INPUT CHARACTERISTICS**

#### Table 6.

| Parameter             | Min | Тур | Max | Unit | Test Conditions/Comments |

|-----------------------|-----|-----|-----|------|--------------------------|

| REF_TEST INPUT        |     |     |     |      |                          |

| Input Frequency Range |     |     | 250 | MHz  |                          |

| Input High Voltage    | 2.0 |     |     | V    |                          |

| Input Low Voltage     |     |     | 0.8 | V    |                          |

#### **PLL1 OUTPUT CHARACTERISTICS**

Table 7.

| Parameter <sup>1</sup>           | Min             | Тур | Max | Unit | Test Conditions/Comments |

|----------------------------------|-----------------|-----|-----|------|--------------------------|

| MAXIMUM OUTPUT FREQUENCY         |                 | 250 |     | MHz  |                          |

| Rise Time/Fall Time (20% to 80%) |                 | 387 | 665 | ps   | 15 pF load               |

| Duty Cycle                       | 45              | 50  | 55  | %    | f = 250 MHz              |

| OUTPUT VOLTAGE HIGH              |                 |     |     |      | Output driver static     |

|                                  | VDD3_PLL - 0.25 |     |     | V    | Load current = 10 mA     |

|                                  | VDD3_PLL - 0.1  |     |     | V    | Load current = 1 mA      |

| OUTPUT VOLTAGE LOW               |                 |     |     |      | Output driver static     |

|                                  |                 |     | 0.2 | V    | Load current = 10 mA     |

|                                  |                 |     | 0.1 | V    | Load current = 1 mA      |

$<sup>^{\</sup>rm 1}$  CMOS driver strength: strong (see Table 52).

# OUT0, OUT0 TO OUT13, OUT13 DISTRIBUTION OUTPUT CHARACTERISTICS

Duty cycle performance is specified with the invert divider bit set to 1, and the divider phase bits set to 0.5. (For example, for Channel 0, 0x190[7] = 1 and 0x192[7:2] = 1.)

Table 8.

| Parameter                         | Min        | Тур       | Max        | Unit      | Test Conditions/Comments                                                 |

|-----------------------------------|------------|-----------|------------|-----------|--------------------------------------------------------------------------|

| LVPECL MODE                       |            |           |            |           |                                                                          |

| Maximum Output Frequency          |            | 1         |            | GHz       | Minimum VCO/maximum dividers                                             |

| Rise Time/Fall Time (20% to 80%)  |            | 117       | 147        | ps        | 100 $\Omega$ termination across output pair                              |

| Duty Cycle                        | 47         | 50        | 52         | %         | f < 500 MHz                                                              |

|                                   | 43         | 48        | 52         | %         | f = 500 MHz to 800 MHz                                                   |

|                                   | 40         | 49        | 54         | %         | f = 800 MHz to 1 GHz                                                     |

| Differential Output Voltage Swing | 643        | 775       | 924        | mV        | Magnitude of voltage across pins; output driver static                   |

| Common-Mode Output Voltage        | VDD – 1.5  | VDD - 1.4 | VDD - 1.25 | V         | Output driver static                                                     |

| SCALED HSTL MODE, 16 mA           |            |           |            |           |                                                                          |

| Maximum Output Frequency          |            | 1         |            | GHz       | Minimum VCO/maximum dividers                                             |

| Rise Time/Fall Time (20% to 80%)  |            | 112       | 141        | ps        | 100 $\Omega$ termination across output pair                              |

| Duty Cycle                        | 47         | 50        | 52         | %         | f < 500 MHz                                                              |

|                                   | 44         | 48        | 51         | %         | f = 500 MHz to 800 MHz                                                   |

|                                   | 40         | 49        | 54         | %         | f = 800 MHz to 1 GHz                                                     |

| Differential Output Voltage Swing | 1.3        | 1.6       | 1.7        | mV        | Nominal supply                                                           |

| Supply Sensitivity                |            | 0.6       |            | mV/<br>mV | Change in output swing vs. VDD3_OUT[x:y] (ΔV <sub>OD</sub> /ΔVDD3)       |

| Common-Mode Output Voltage        | VDD - 1.76 | VDD - 1.6 | VDD - 1.42 | V         |                                                                          |

| LVDS MODE, 3.5 mA                 |            |           |            |           |                                                                          |

| Maximum Output Frequency          |            | 1         |            | GHz       |                                                                          |

| Rise Time/Fall Time (20% to 80%)  |            | 138       | 161        | ps        | 100 $\Omega$ termination across output pair                              |

| Duty Cycle                        | 48         | 51        | 53         | %         | f < 500 MHz                                                              |

|                                   | 43         | 49        | 53         | %         | f = 500 MHz to 800 MHz                                                   |

|                                   | 41         | 49        | 55         | %         | f = 800 MHz to 1 GHz                                                     |

| Differential Output Voltage Swing |            |           |            |           |                                                                          |

| Balanced                          | 247        |           | 454        | mV        | Voltage swing between output pins; output driver static                  |

| Unbalanced                        |            |           | 50         | mV        | Absolute difference between voltage swing of normal pin and inverted pin |

| Common-Mode Output Voltage        | 1.125      |           | 1.375      | V         | Output driver static                                                     |

| Common-Mode Difference            |            |           | 50         | mV        | Voltage difference between output pins; output driver static             |

| Short-Circuit Output Current      |            | 3.5       | 24         | mA        | Output driver static                                                     |

Rev. B | Page 7 of 60

| Parameter                        | Min        | Тур | Max | Unit | Test Conditions/Comments |

|----------------------------------|------------|-----|-----|------|--------------------------|

| CMOS MODE                        |            |     |     |      |                          |

| Maximum Output Frequency         |            | 250 |     | MHz  |                          |

| Rise Time/Fall Time (20% to 80%) |            | 387 | 665 | ps   | 15 pF load               |

| Duty Cycle                       | 45         | 50  | 55  | %    | f = 250 MHz              |

| Output Voltage High              |            |     |     |      | Output driver static     |

|                                  | VDD - 0.25 |     |     | V    | Load current = 10 mA     |

|                                  | VDD - 0.1  |     |     | V    | Load current = 1 mA      |

| Output Voltage Low               |            |     |     |      | Output driver static     |

|                                  |            |     | 0.2 | V    | Load current = 10 mA     |

|                                  |            |     | 0.1 | V    | Load current = 1 mA      |

#### **TIMING ALIGNMENT CHARACTERISTICS**

Table 9.

| Parameter                                                                                             | Min | Тур | Max | Unit  | Test Conditions/Comments                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUTPUT TIMING SKEW                                                                                    |     |     |     |       | Delay off on all outputs; maximum deviation between rising edges of outputs; all outputs are on, unless otherwise noted                                                         |

| Between Outputs in Same Group <sup>1</sup>                                                            |     |     |     |       |                                                                                                                                                                                 |

| LVPECL, HSTL, and LVDS                                                                                |     |     |     |       |                                                                                                                                                                                 |

| Between LVPECL, HSTL, and LVDS Outputs                                                                |     | 30  | 183 | ps    |                                                                                                                                                                                 |

| CMOS                                                                                                  |     |     |     |       |                                                                                                                                                                                 |

| Between CMOS Outputs                                                                                  |     | 100 | 300 | ps    | Single-ended, true phase, high-Z mode                                                                                                                                           |

| Mean Delta Between Groups <sup>1</sup>                                                                |     | 50  |     |       |                                                                                                                                                                                 |

| Adjustable Delay                                                                                      | 0   |     | 63  | Steps | Resolution step; for example, $8 \times 0.5/1$ GHz                                                                                                                              |

| Resolution Step                                                                                       |     | 500 |     | ps    | ½ period of 1 GHz                                                                                                                                                               |

| Zero Delay                                                                                            |     |     |     |       |                                                                                                                                                                                 |

| Between Input Clock Edge on<br>REFA or REFB to ZD_IN Input<br>Clock Edge, External Zero<br>Delay Mode |     | 150 | 500 | ps    | PLL1 settings: PFD = 7.68 MHz, $I_{CP}$ = 63.5 μA, $R_{ZERO}$ = 10 k $\Omega$ , antibacklash pulse width is at maximum, BW = 40 Hz, REFA and ZD_IN are set to differential mode |

<sup>&</sup>lt;sup>1</sup> There are three groups of outputs. They are as follows: the top outputs group, consisting of OUT0, OUT1, OUT2, and OUT3; the right outputs group, consisting of OUT4, OUT5, OUT6, OUT7, OUT8, and OUT9; and the bottom outputs group, consisting of OUT10, OUT11, OUT12, and OUT13.

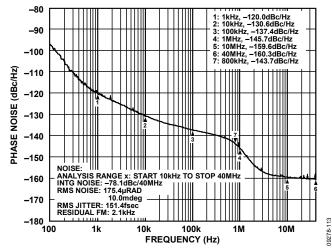

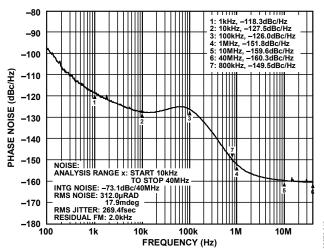

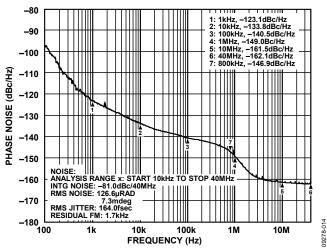

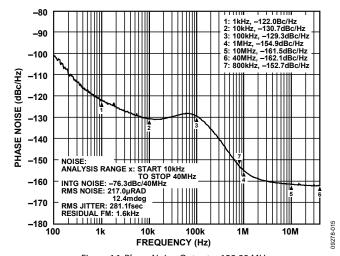

#### **JITTER AND NOISE CHARACTERISTICS**

#### Table 10.

| Parameter                         | Min | Тур | Max | Unit | Test Conditions/Comments                                                   |

|-----------------------------------|-----|-----|-----|------|----------------------------------------------------------------------------|

| OUTPUT ABSOLUTE RMS TIME JITTER   |     |     |     |      | Application example based on a typical setup (see Table 3); f = 122.88 MHz |

| LVPECL Mode, HSTL Mode, LVDS Mode |     |     |     |      |                                                                            |

|                                   |     | 109 |     | fs   | Integrated BW = 200 kHz to 5 MHz                                           |

|                                   |     | 115 |     | fs   | Integrated BW = 200 kHz to 10 MHz                                          |

|                                   |     | 150 |     | fs   | Integrated BW = 12 kHz to 20 MHz                                           |

|                                   |     | 177 |     | fs   | Integrated BW = 10 kHz to 61 MHz                                           |

|                                   |     | 187 |     | fs   | Integrated BW = 1 kHz to 61 MHz                                            |

|                                   |     | 124 |     | fs   | Integrated BW = 1 MHz to 61 MHz                                            |

#### **PLL2 CHARACTERISTICS**

#### Table 11.

| Parameter                  | Min  | Тур  | Max  | Unit   | Test Conditions/Comments |

|----------------------------|------|------|------|--------|--------------------------|

| VCO (ON CHIP)              |      |      |      |        |                          |

| Frequency Range            | 2940 |      | 3100 | MHz    |                          |

| Gain                       |      | 45   |      | MHz/V  |                          |

| PLL2 FIGURE OF MERIT (FOM) |      | -226 |      | dBc/Hz |                          |

| MAXIMUM PFD FREQUENCY      |      |      |      |        |                          |

| Antibacklash Pulse Width   |      |      |      |        |                          |

| Minimum and Low            |      |      | 250  | MHz    |                          |

| Maximum and High           |      |      | 125  | MHz    |                          |

# LOGIC INPUT PINS— $\overline{PD}$ , $\overline{SYNC}$ , $\overline{RESET}$ , $\overline{EEPROM\_SEL}$ , $\overline{REF\_SEL}$

#### Table 12.

| Parameter                                    | Min | Тур | Max  | Unit | Test Conditions/Comments                                                                                    |

|----------------------------------------------|-----|-----|------|------|-------------------------------------------------------------------------------------------------------------|

| VOLTAGE                                      |     |     |      |      |                                                                                                             |

| Input High                                   | 2.0 |     |      | ٧    |                                                                                                             |

| Input Low                                    |     |     | 0.8  | ٧    |                                                                                                             |

| INPUT LOW CURRENT                            |     | ±80 | ±250 | μΑ   | The minus sign indicates that, due to the internal pull-up resistor, current is flowing out of the AD9523-1 |

| CAPACITANCE                                  |     | 3   |      | рF   |                                                                                                             |

| RESET TIMING                                 |     |     |      |      |                                                                                                             |

| Pulse Width Low                              | 50  |     |      | ns   |                                                                                                             |

| Inactive to Start of Register<br>Programming | 100 |     |      | ns   |                                                                                                             |

| SYNC TIMING                                  |     |     |      |      |                                                                                                             |

| Pulse Width Low                              | 1.5 |     |      | ns   | High speed clock is the CLK input signal                                                                    |

# STATUS OUTPUT PINS—STATUS1, STATUS0

#### Table 13.

| Parameter   | Min  | Тур | Max | Unit | Test Conditions/Comments |

|-------------|------|-----|-----|------|--------------------------|

| VOLTAGE     |      |     |     |      |                          |

| Output High | 2.94 |     |     | V    |                          |

| Output Low  |      |     | 0.4 | V    |                          |

#### SERIAL CONTROL PORT—SPI MODE

Table 14.

| Parameter                                     | Min | Тур  | Max | Unit | Test Conditions/Comments                                          |

|-----------------------------------------------|-----|------|-----|------|-------------------------------------------------------------------|

| CS (INPUT)                                    |     |      |     |      | $\overline{CS}$ has an internal 40 k $\Omega$ pull-up resistor    |

| Voltage                                       |     |      |     |      |                                                                   |

| Input Logic 1                                 |     | 2.0  |     | V    |                                                                   |

| Input Logic 0                                 |     | 0.8  |     | V    |                                                                   |

| Current                                       |     |      |     |      |                                                                   |

| Input Logic 1                                 |     | 30   |     | μΑ   |                                                                   |

| Input Logic 0                                 |     | -110 |     | μΑ   | The minus sign indicates that, due to the                         |

|                                               |     |      |     |      | internal pull-up resistor, current is flowing out of the AD9523-1 |

| Input Capacitance                             |     | 2    |     | рF   | 01 11.07 15 75 25 1                                               |

| SCLK (INPUT) IN SPI MODE                      |     |      |     | 15.  | SCLK has an internal 40 kΩ pull-down resistor                     |

|                                               |     |      |     |      | in SPI mode but not in I <sup>2</sup> C mode                      |

| Voltage                                       |     |      |     |      |                                                                   |

| Input Logic 1                                 |     | 2.0  |     | V    |                                                                   |

| Input Logic 0                                 |     | 0.8  |     | V    |                                                                   |

| Current                                       |     |      |     |      |                                                                   |

| Input Logic 1                                 |     | 240  |     | μΑ   |                                                                   |

| Input Logic 0                                 |     | 1    |     | μΑ   |                                                                   |

| Input Capacitance                             |     | 2    |     | рF   |                                                                   |

| SDIO (WHEN INPUT IS IN BIDIRECTIONAL MODE)    |     |      |     |      |                                                                   |

| Voltage                                       |     |      |     |      |                                                                   |

| Input Logic 1                                 |     | 2.0  |     | V    |                                                                   |

| Input Logic 0                                 |     | 0.8  |     | V    |                                                                   |

| Current                                       |     |      |     |      |                                                                   |

| Input Logic 1                                 |     | 1    |     | μΑ   |                                                                   |

| Input Logic 0                                 |     | 1    |     | μΑ   |                                                                   |

| Input Capacitance                             |     | 2    |     | pF   |                                                                   |

| SDIO, SDO (OUTPUTS)                           |     |      |     |      |                                                                   |

| Output Logic 1 Voltage                        | 2.7 |      |     | V    |                                                                   |

| Output Logic 0 Voltage                        |     |      | 0.4 | V    |                                                                   |

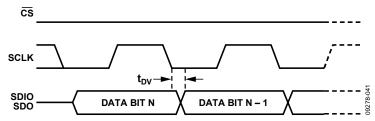

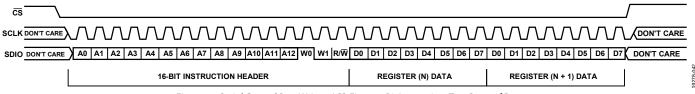

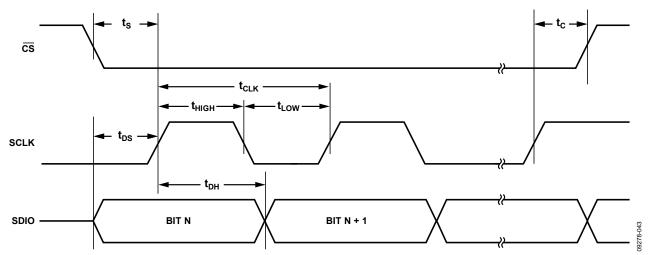

| TIMING                                        |     |      |     |      |                                                                   |

| Clock Rate (SCLK, 1/t <sub>SCLK</sub> )       |     |      | 25  | MHz  |                                                                   |

| Pulse Width High, t <sub>HIGH</sub>           | 8   |      |     | ns   |                                                                   |

| Pulse Width Low, t <sub>LOW</sub>             | 12  |      |     | ns   |                                                                   |

| SDIO to SCLK Setup, t <sub>DS</sub>           | 3.3 |      |     | ns   |                                                                   |

| SCLK to SDIO Hold, t <sub>DH</sub>            | 0   |      |     | ns   |                                                                   |

| SCLK to Valid SDIO and SDO, t <sub>DV</sub>   |     |      | 14  | ns   |                                                                   |

| CS to SCLK Setup, t₅                          | 10  |      |     | ns   |                                                                   |

| CS to SCLK Setup and Hold, ts, tc             | 0   |      |     | ns   |                                                                   |

| CS Minimum Pulse Width High, t <sub>PWH</sub> | 6   |      |     | ns   |                                                                   |

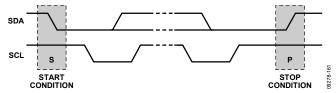

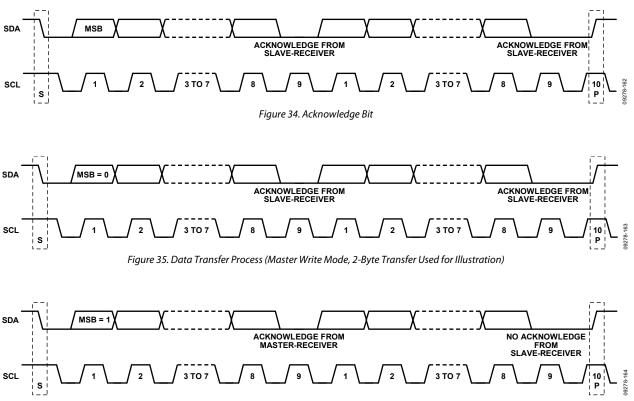

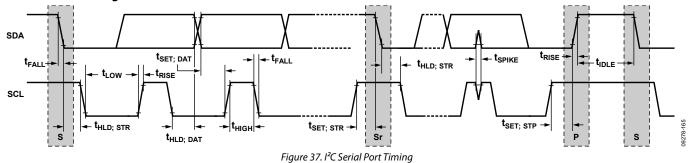

#### SERIAL CONTROL PORT—I<sup>2</sup>C MODE

VDD = VDD3\_REF, unless otherwise noted.

Table 15.

| Parameter                                                                                                  | Min                                  | Тур | Max              | Unit | Test Conditions/Comments                                                                                                              |

|------------------------------------------------------------------------------------------------------------|--------------------------------------|-----|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------|

| SDA, SCL (WHEN INPUTTING DATA)                                                                             |                                      |     |                  |      |                                                                                                                                       |

| Input Logic 1 Voltage                                                                                      | 0.7 × VDD                            |     |                  | V    |                                                                                                                                       |

| Input Logic 0 Voltage                                                                                      |                                      |     | $0.3 \times VDD$ | V    |                                                                                                                                       |

| Input Current with an Input Voltage Between $0.1 \times VDD$ and $0.9 \times VDD$                          | -10                                  |     | +10              | μΑ   |                                                                                                                                       |

| Hysteresis of Schmitt Trigger Inputs                                                                       | 0.015 × VDD                          |     |                  | V    |                                                                                                                                       |

| Pulse Width of Spikes That Must Be<br>Suppressed by the Input Filter, t <sub>SPIKE</sub>                   |                                      |     | 50               | ns   |                                                                                                                                       |

| SDA (WHEN OUTPUTTING DATA)                                                                                 |                                      |     |                  |      |                                                                                                                                       |

| Output Logic 0 Voltage at 3 mA Sink Current                                                                |                                      |     | 0.4              | V    |                                                                                                                                       |

| Output Fall Time from VIH <sub>MIN</sub> to VIL <sub>MAX</sub> with a Bus Capacitance from 10 pF to 400 pF | 20 + 0.1 C <sub>B</sub> <sup>1</sup> |     | 250              | ns   |                                                                                                                                       |

| TIMING                                                                                                     |                                      |     |                  |      | Note that all I <sup>2</sup> C timing values are referred to VIH <sub>MIN</sub> (0.3 × VDD) and VIL <sub>MAX</sub> levels (0.7 × VDD) |

| Clock Rate (SCL, f <sub>12C</sub> )                                                                        |                                      |     | 400              | kHz  |                                                                                                                                       |

| Bus Free Time Between a Stop and Start Condition, t <sub>IDLE</sub>                                        | 1.3                                  |     |                  | μs   |                                                                                                                                       |

| Setup Time for a Repeated Start Condition, $t_{\text{SET; STR}}$                                           | 0.6                                  |     |                  | μs   |                                                                                                                                       |

| Hold Time (Repeated) Start Condition, t <sub>HLD; STR</sub>                                                | 0.6                                  |     |                  | μs   | After this period, the first clock pulse is generated                                                                                 |

| Setup Time for a Stop Condition, t <sub>SET; STP</sub>                                                     | 0.6                                  |     |                  | μs   |                                                                                                                                       |

| Low Period of the SCL Clock, tLOW                                                                          | 1.3                                  |     |                  | μs   |                                                                                                                                       |

| High Period of the SCL Clock, thigh                                                                        | 0.6                                  |     |                  | μs   |                                                                                                                                       |

| SCL, SDA Rise Time, t <sub>RISE</sub>                                                                      | $20 + 0.1 C_{B}^{1}$                 |     | 300              | ns   |                                                                                                                                       |

| SCL, SDA Fall Time, t <sub>FALL</sub>                                                                      | 20 + 0.1 C <sub>B</sub> <sup>1</sup> |     | 300              | ns   |                                                                                                                                       |

| Data Setup Time, t <sub>SET; DAT</sub>                                                                     | 100                                  |     |                  | ns   |                                                                                                                                       |

| Data Hold Time, t <sub>HLD; DAT</sub>                                                                      | 100                                  |     | 880              | ns   | This is a minor deviation from the original I <sup>2</sup> C specification of 0 ns minimum <sup>2</sup>                               |

| Capacitive Load for Each Bus Line, C <sub>B</sub> <sup>1</sup>                                             |                                      |     | 400              | рF   |                                                                                                                                       |

<sup>&</sup>lt;sup>1</sup> C<sub>B</sub> is the capacitance of one bus line in picofarads (pF). <sup>2</sup> According to the original I<sup>2</sup>C specification, an I<sup>2</sup>C master must also provide a minimum hold time of 300 ns for the SDA signal to bridge the undefined region of the SCL falling edge.

# **ABSOLUTE MAXIMUM RATINGS**

Table 16.

| Parameter                                                                                                                                                                             | Rating           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| VDD3_PLL, VDD3_REF, VDD3_OUT[x:y], LDO VCO to GND                                                                                                                                     | −0.3 V to +3.6 V |

| REFA, REFA, REFB, REFB to GND                                                                                                                                                         | -0.3 V to +3.6 V |

| SCLK/SCL, SDIO/SDA, SDO, CS to GND                                                                                                                                                    | -0.3 V to +3.6 V |

| OUT0, OUT0, OUT1, OUT1, OUT2, OUT2, OUT3, OUT3, OUT4, OUT4, OUT5, OUT5, OUT6, OUT6, OUT6, OUT7, OUT7, OUT8, OUT9, OUT9, OUT10, OUT11, OUT11, OUT11, OUT12, OUT12, OUT13, OUT13 to GND | -0.3 V to +3.6 V |

| SYNC, RESET, PD, REF_SEL to GND                                                                                                                                                       | -0.3 V to +3.6 V |

| STATUS0, STATUS1 to GND                                                                                                                                                               | -0.3 V to +3.6 V |

| SP0, SP1, EEPROM_SEL to GND                                                                                                                                                           | -0.3 V to +3.6 V |

| VDD1.8_OUT[x:y], LDO_PLL1, LDO_DIV_M1 to GND                                                                                                                                          | 2 V              |

| Junction Temperature <sup>1</sup>                                                                                                                                                     | 115°C            |

| Storage Temperature Range                                                                                                                                                             | −65°C to +150°C  |

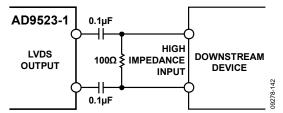

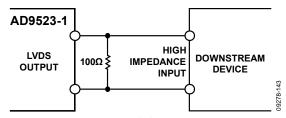

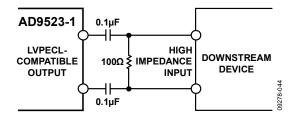

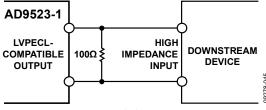

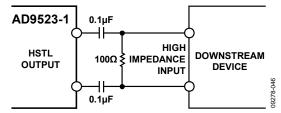

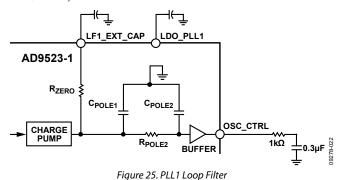

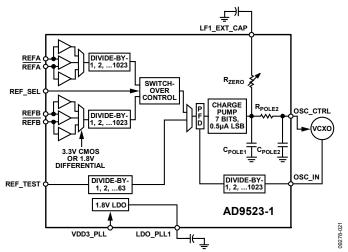

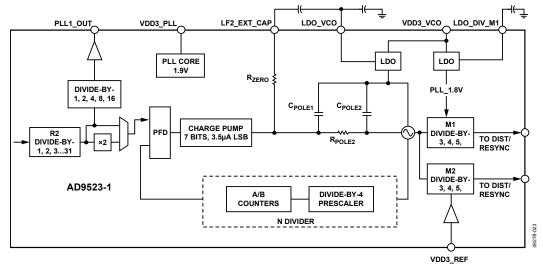

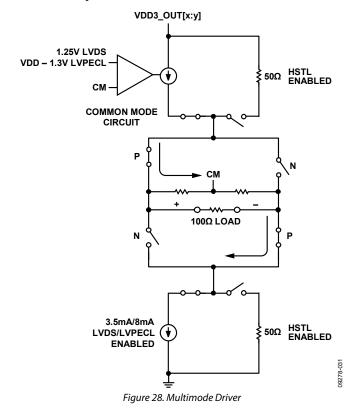

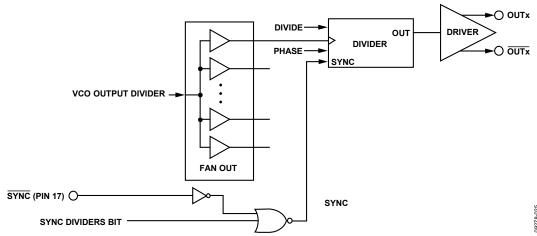

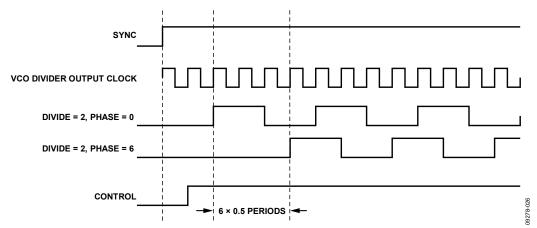

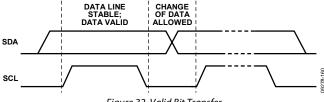

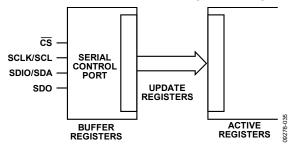

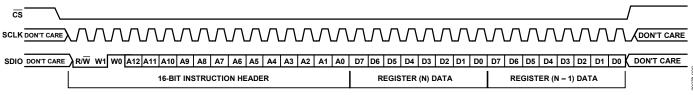

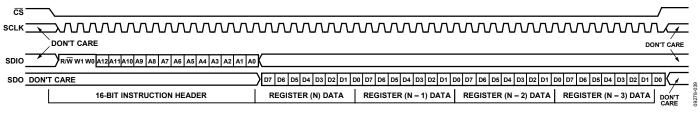

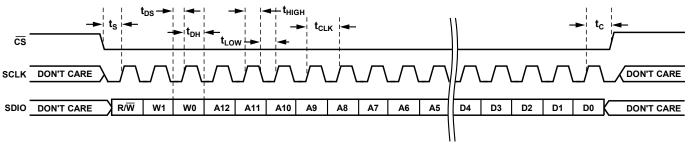

| Lead Temperature (10 sec)                                                                                                                                                             | 300°C            |