# AERO<sup>™</sup> I TRANSCEIVER FOR **GSM** AND **GPRS** WIRELESS COMMUNICATIONS

#### Features

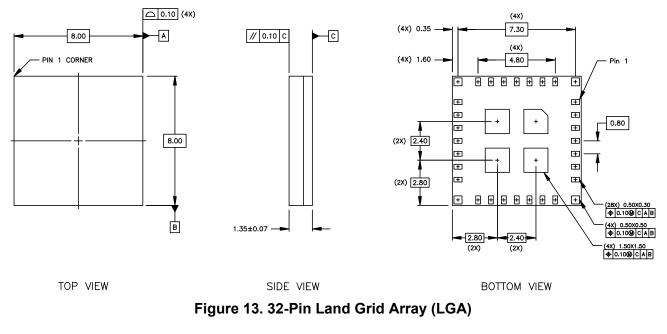

- Single 8 x 8 mm package

- CMOS process technology

- Integrated GSM/GPRS transceiver including:

- Low-IF receiver

- Universal baseband interface

- Offset-PLL transmitter

- Dual RF synthesizer

- Integrated VCOs, frequency synthesizers, and tuning inductors

#### Applications

- Multi-band GSM/GPRS digital cellular handsets

- Multi-band GSM/GPRS wireless data modems

#### Description

The Aero I transceiver is a complete RF front end for multi-band GSM and GPRS wireless communications. The transmit section interfaces between the baseband processor and the power amplifier. The receive section interfaces between the RF band-select SAW filters and the baseband processor. All sensitive components, such as RF/IF VCOs, loop filters, and tuning inductors, are completely integrated into a single compact package.

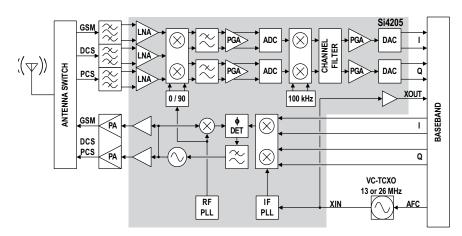

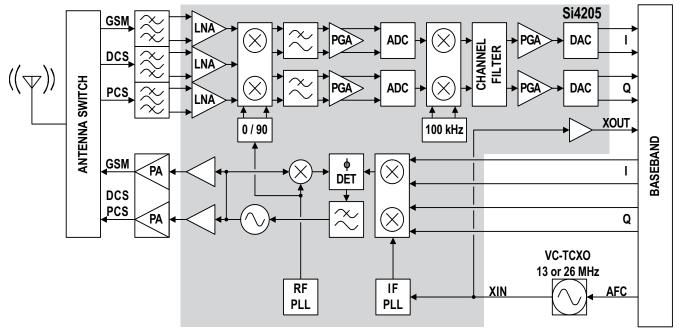

#### **Functional Block Diagram**

- GSM 850 Class 4, small MS

- E-GSM 900 Class 4, small MS

- DCS 1800 Class 1

- PCS 1900 Class 1

- GPRS Class 12 compliant

- 3-wire serial interface

- 2.7 V to 3.0 V operation

Patents pending

# TABLE OF CONTENTS

# Section

# <u>Page</u>

| Electrical Specifications   |   |

|-----------------------------|---|

| Bill of Materials           |   |

| Functional Description      | 6 |

| Receiver                    | 7 |

| Transmitter                 | 8 |

| Frequency Synthesizer       | 9 |

| Serial Interface            | 0 |

| XOUT Buffer                 | 0 |

| 2 Control Registers         | 1 |

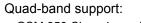

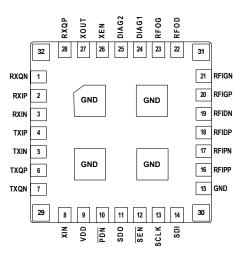

| Pin Descriptions: Si4205-BM | 3 |

| Ordering Guide              | 4 |

| Package Outline: Si4205-BM  |   |

| Document Change List        |   |

| Contact Information         |   |

# **Electrical Specifications**

## **Table 1. Recommended Operating Conditions**

| Parameter                                                                                                                                                                                                                                                                        | Symbol         | Test Condition | Min | Тур  | Max | Unit |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|-----|------|-----|------|--|--|--|--|

| Ambient Temperature                                                                                                                                                                                                                                                              | T <sub>A</sub> |                | -20 | 25   | 85  | °C   |  |  |  |  |

| DC Supply Voltage                                                                                                                                                                                                                                                                | $V_{DD}$       |                | 2.7 | 2.85 | 3.0 | V    |  |  |  |  |

| Note: All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions.<br>Typical values apply at 2.85 V and an operating temperature of 25 °C unless otherwise stated. Parameters are tested in production unless otherwise stated. |                |                |     |      |     |      |  |  |  |  |

Table 2. Absolute Maximum Ratings<sup>1,2</sup>

| Parameter                   | Symbol           | Value                           | Unit |

|-----------------------------|------------------|---------------------------------|------|

| DC Supply Voltage           | V <sub>DD</sub>  | –0.5 to 3.3                     | V    |

| Input Current <sup>3</sup>  | l <sub>iN</sub>  | ±10                             | mA   |

| Input Voltage <sup>3</sup>  | V <sub>IN</sub>  | –0.3 to (V <sub>DD</sub> + 0.3) | V    |

| Operating Temperature Range | T <sub>OP</sub>  | -40 to 95                       | °C   |

| Storage Temperature Range   | T <sub>STG</sub> | –55 to 150                      | °C   |

| RF Input Level <sup>4</sup> |                  | 10                              | dBm  |

Notes:

1. Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2. The Si4205 device is high-performance RF integrated circuit with an ESD rating of < 2 kV. Handling and assembly of this device should only be done at ESD-protected workstations.

3. For signals SCLK, SDI, SEN, PDN, XEN, and XIN.

4. At SAW filter output for all bands.

## **Table 3. DC Characteristics**

(V<sub>DD</sub> = 2.7 to 3.0 V, T<sub>A</sub> = –20 to 85 °C)

| Parameter                              | Symbol            | Test Condition                                    | Min                  | Тур | Max                 | Unit |

|----------------------------------------|-------------------|---------------------------------------------------|----------------------|-----|---------------------|------|

| Supply Current <sup>1</sup>            | I <sub>RX</sub>   | Receive mode                                      |                      | 80  | 111                 | mA   |

|                                        | I <sub>TX</sub>   | Transmit mode                                     | —                    | 82  | 107                 | mA   |

|                                        | I <sub>XOUT</sub> | PDN = 0, XEN = 1                                  | —                    | 1   | 2                   | mA   |

|                                        | I <sub>PDN</sub>  | PDN = 0, XEN = 0,<br>XBUF = 0, XPD1 = 1           |                      | 5   | 80                  | μA   |

| High Level Input Voltage <sup>2</sup>  | V <sub>IH</sub>   |                                                   | $0.7 V_{DD}$         | _   | _                   | V    |

| Low Level Input Voltage <sup>2</sup>   | V <sub>IL</sub>   |                                                   | —                    | _   | $0.3 V_{\text{DD}}$ | V    |

| High Level Input Current <sup>2</sup>  | I <sub>IH</sub>   | V <sub>IH</sub> = V <sub>DD</sub> = 3.0 V         | -10                  |     | 10                  | μA   |

| Low Level Input Current <sup>2</sup>   | I <sub>IL</sub>   | V <sub>IL</sub> = 0 V,<br>V <sub>DD</sub> = 3.0 V | -10                  | —   | 10                  | μA   |

| High Level Output Voltage <sup>3</sup> | V <sub>OH</sub>   | I <sub>OH</sub> = –500 μA                         | V <sub>DD</sub> -0.4 | _   | —                   | V    |

| Low Level Output Voltage <sup>3</sup>  | V <sub>OL</sub>   | I <sub>oL</sub> = 500 μA                          |                      | _   | 0.4                 | V    |

| High Level Output Voltage <sup>4</sup> | V <sub>OH</sub>   | I <sub>OH</sub> = -10 mA                          | V <sub>DD</sub> -0.4 |     |                     | V    |

| Low Level Output Voltage <sup>4</sup>  | V <sub>OL</sub>   | I <sub>OL</sub> = 10 mA                           |                      | _   | 0.4                 | V    |

Notes:

Measured with load on XOUT pin of 10 pF and f<sub>REF</sub> = 13 MHz. Limits with XEN = 1 guaranteed by characterization.

For pins SCLK, SDI, SEN, XEN, and PDN.

For pins SDO, XOUT.

4. For pins DIAG1, DIAG2.

## Table 4. AC Characteristics

(V<sub>DD</sub> = 2.7 to 3.0 V, T<sub>A</sub> = –20 to 85 °C)

| Parameter                                                 | Symbol            | Test Condition     | Min | Тур | Max | Unit            |

|-----------------------------------------------------------|-------------------|--------------------|-----|-----|-----|-----------------|

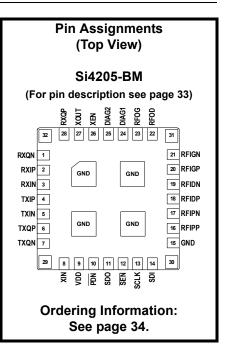

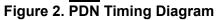

| SCLK Cycle Time                                           | t <sub>CLK</sub>  | Figures 1, 3       | 35  |     | _   | ns              |

| SCLK Rise Time                                            | t <sub>R</sub>    | Figures 1, 3       |     | _   | 50  | ns              |

| SCLK Fall Time                                            | t <sub>F</sub>    | Figures 1, 3       |     | _   | 50  | ns              |

| SCLK High Time                                            | t <sub>HI</sub>   | Figures 1, 3       | 10  |     | —   | ns              |

| SCLK Low Time                                             | t <sub>LO</sub>   | Figures 1, 3       | 10  | _   | —   | ns              |

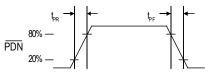

| PDN Rise Time                                             | t <sub>PR</sub>   | Figure 2           |     | —   | 10  | ns              |

| PDN Fall Time                                             | t <sub>PF</sub>   | Figure 2           |     |     | 10  | ns              |

| SDI Setup Time to SCLK <sup>↑</sup>                       | t <sub>su</sub>   | Figure 3           | 15  |     | —   | ns              |

| SDI Hold Time from SCLK↑                                  | t <sub>HOLD</sub> | Figure 3           | 10  | —   | —   | ns              |

| $\overline{SEN} \downarrow$ to $SCLK \uparrow$ Delay Time | t <sub>EN1</sub>  | Figure 3           | 10  | _   | —   | ns              |

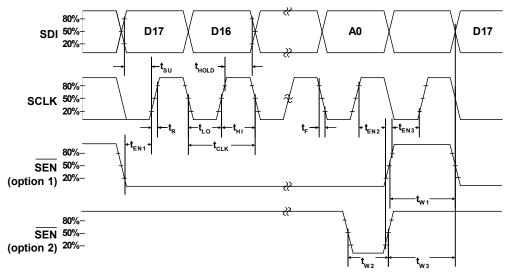

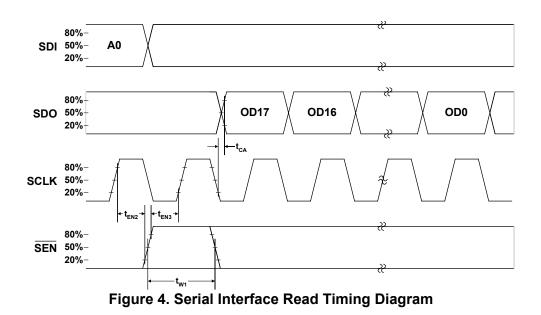

| SCLK↑ to SEN↑ Delay Time                                  | t <sub>EN2</sub>  | Figures 3, 4       | 12  | _   | —   | ns              |

| SEN <sup>↑</sup> to SCLK <sup>↑</sup> Delay Time          | t <sub>EN3</sub>  | Figures 3, 4       | 12  | —   | —   | ns              |

| SEN Pulse Width <sup>1</sup>                              | $t_{W1}, t_{W3}$  | Figures 3, 4       | 10  | —   | —   | ns              |

|                                                           |                   | DGAIN bits only    | 130 |     | —   | μS              |

|                                                           | t <sub>w2</sub>   | Option 2 only      | 10  | —   | —   | ns              |

| SCLK↓ to SDO Time                                         | t <sub>CA</sub>   | Figure 4           |     |     | 27  | ns              |

| Digital Input Pin Capacitance <sup>2</sup>                |                   |                    |     |     | 5   | pF              |

| XIN Input Resistance <sup>3</sup>                         | R <sub>XIN</sub>  |                    | 10  | 15  | 20  | kΩ              |

| XIN Input Capacitance <sup>3</sup>                        | C <sub>XIN</sub>  |                    | 7   | 10  | 14  | pF              |

| XIN Input Sensitivity <sup>3</sup>                        | V <sub>REF</sub>  |                    | 0.5 | _   | _   | V <sub>PP</sub> |

| XIN Input Frequency <sup>3,4</sup>                        | f <sub>REF</sub>  | XSEL = 0, DIV2 = 0 | _   | 13  | _   | MHz             |

|                                                           |                   | XSEL = 1, DIV2 = 1 |     | 26  | _   | MHz             |

Notes:

6

Two programming options are allowed for SEN. Either option may be used. In both cases, the SEN pulse width must be at least 10 ns after writing all registers except after DGAIN is written. After DGAIN is written, SEN must be held high for at least 130 μs. See <u>"AN5</u>0: Aero Transceiver Programming Guide."

**2.** For pins SCLK, SDI,  $\overline{\text{SEN}}$ , XEN, and  $\overline{\text{PDN}}$ .

3. For XIN pin.

4. The XSEL and DIV2 bits control internal divide-by-two circuits and do not effect the XOUT pin.

Figure 1. SCLK Timing Diagram

Figure 3. Serial Interface Write Timing Diagram

## **Table 5. Receiver Characteristics**

(V<sub>DD</sub> = 2.7 to 3.0 V, T<sub>A</sub> = -20 to 85 °C)

| Parameter                                     | Symbol            | Test Condition                                                       | Min  | Тур  | Мах  | Unit |

|-----------------------------------------------|-------------------|----------------------------------------------------------------------|------|------|------|------|

| GSM Input Frequency <sup>1</sup>              | f <sub>IN</sub>   | GSM 850 band                                                         | 869  |      | 894  | MHz  |

|                                               |                   | E-GSM 900 band                                                       | 925  |      | 960  | MHz  |

| DCS or PCS Input Frequency <sup>1</sup>       |                   | DCS 1800 band                                                        | 1805 |      | 1880 | MHz  |

|                                               |                   | PCS 1900 band                                                        | 1930 |      | 1990 | MHz  |

| Noise Figure at 25 °C <sup>2,3</sup>          | NF <sub>25</sub>  | GSM 850 band                                                         |      | 2.9  | 3.8  | dB   |

|                                               |                   | E-GSM 900 band                                                       | _    | 3.0  | 3.9  | dB   |

|                                               |                   | DCS 1800 band                                                        |      | 3.3  | 4.1  | dB   |

|                                               |                   | PCS 1900 band                                                        |      | 3.7  | 4.5  | dB   |

| Noise Figure at 75 °C <sup>2,3</sup>          | NF <sub>75</sub>  | GSM 850 band                                                         | —    | 3.6  | 4.5  | dB   |

|                                               |                   | E-GSM 900 band                                                       | _    | 3.7  | 4.6  | dB   |

|                                               |                   | DCS 1800 band                                                        | _    | 4.2  | 5.0  | dB   |

|                                               |                   | PCS 1900 band                                                        | _    | 4.9  | 5.7  | dB   |

| Noise Figure at 85 °C <sup>2,3</sup>          | NF <sub>85</sub>  | GSM 850 band                                                         |      | 3.7  | 4.6  | dB   |

|                                               |                   | E-GSM 900 band                                                       | _    | 3.8  | 4.7  | dB   |

|                                               |                   | DCS 1800 band                                                        | —    | 4.6  | 5.4  | dB   |

|                                               |                   | PCS 1900 band                                                        | _    | 5.2  | 6.0  | dB   |

| 3 MHz Input Desensitization <sup>2,3,4</sup>  | $DES_3$           | GSM input                                                            | -25  | -21  | —    | dBm  |

|                                               |                   | DCS/PCS inputs                                                       | -28  | -25  | _    | dBm  |

| 20 MHz Input Desensitization <sup>2,3,4</sup> | DES <sub>20</sub> | GSM input                                                            | -21  | –16  | —    | dBm  |

|                                               |                   | DCS/PCS inputs                                                       | –19  | –15  |      | dBm  |

| Input IP2 <sup>2</sup>                        | IP2               | $ f_{1,2} - f_0  \ge 6 \text{ MHz}, \  f_2 - f_1  = 100 \text{ kHz}$ | 29   | 40   | _    | dBm  |

| Input IP3 <sup>2</sup>                        | IP3               | $ f_2 - f_1  \ge 800 \text{ kHz}, \\ f_0 = 2f_1 - f_2$               | –18  | –12  | _    | dBm  |

| Image Rejection <sup>2,4</sup>                | IR                | GSM Input                                                            | 28   | 35   |      | dB   |

|                                               |                   | DCS/PCS Inputs                                                       | 28   | 40   |      | dB   |

| 1 dB Input Compression <sup>2,5</sup>         | CP <sub>MAX</sub> | GSM Input                                                            | -28  | -23  | _    | dBm  |

|                                               |                   | DCS/PCS inputs                                                       | -27  | -22  |      | dBm  |

| 1 dB Input Compression <sup>2,6</sup>         | CP <sub>MIN</sub> | GSM Input                                                            | -23  | -18  |      | dBm  |

|                                               |                   | DCS/PCS inputs                                                       | -23  | -18  | _    | dBm  |

| Minimum Voltage Gain <sup>2,6,7</sup>         | G <sub>MIN</sub>  | GSM input                                                            | 3    | 8.5  | 12.5 | dB   |

|                                               |                   | DCS/PCS inputs                                                       | 10   | 15.5 | 19.5 | dB   |

| Maximum Voltage Gain <sup>2,7</sup>           | G <sub>MAX</sub>  | GSM input                                                            | 100  | 104  | 109  | dB   |

|                                               |                   | DCS/PCS inputs                                                       | 96   | 102  | 107  | dB   |

| LNA Voltage Gain <sup>3,8</sup>               | G <sub>LNA</sub>  | GSM input                                                            |      | 17   |      | dB   |

|                                               |                   | DCS/PCS inputs                                                       |      | 15   | —    | dB   |

| LNA Gain Control Range                        | $\Delta G_{LNA}$  | GSM input                                                            | 13   | 17   | 21   | dB   |

|                                               |                   | DCS/PCS inputs                                                       | 4    | 8    | 12   | dB   |

## Table 5. Receiver Characteristics (Continued)

(V<sub>DD</sub> = 2.7 to 3.0 V, T<sub>A</sub> = –20 to 85 °C)

| Parameter                                                   | Symbol            | Test Condition  | Min  | Тур  | Мах  | Unit             |

|-------------------------------------------------------------|-------------------|-----------------|------|------|------|------------------|

| Analog PGA Control Range                                    | $\Delta G_{APGA}$ |                 | 13   | 16   | 19   | dB               |

| Analog PGA Step Size                                        |                   |                 | 3.2  | 4.0  | 4.8  | dB               |

| Digital PGA Control Range                                   | $\Delta G_{DPGA}$ |                 |      | 63   |      | dB               |

| Digital PGA Step Size                                       |                   |                 |      | 1    |      | dB               |

| Maximum Differential Output Voltage <sup>9</sup>            |                   | DACFS[1:0] = 00 | 0.7  | 1.0  | 1.3  | V <sub>PPD</sub> |

|                                                             |                   | DACFS[1:0] = 01 | 1.5  | 2.0  | 2.5  | V <sub>PPD</sub> |

|                                                             |                   | DACFS[1:0] = 10 | 2.6  | 3.5  | 4.4  | V <sub>PPD</sub> |

| Output Common Mode Voltage <sup>9</sup>                     |                   | DACCM[1:0] = 00 | 0.8  | 1.0  | 1.2  | V                |

|                                                             |                   | DACCM[1:0] = 01 | 1.05 | 1.25 | 1.45 | V                |

|                                                             |                   | DACCM[1:0] = 10 | 1.15 | 1.35 | 1.55 | V                |

| Differential Output Offset Voltage <sup>9,10,11</sup>       |                   |                 |      | —    | 16   | mV               |

| Differential Output Offset Voltage Drift <sup>9,10,11</sup> |                   |                 | —    | _    | 5    | mV               |

| Baseband Gain Error <sup>9,11</sup>                         |                   |                 |      |      | 1    | %                |

| Baseband Phase Error <sup>9,11</sup>                        |                   |                 |      |      | 1    | deg              |

| Output Load Resistance <sup>9</sup>                         | RL                | Single-ended    | 10   |      |      | kΩ               |

| Output Load Capacitance <sup>9</sup>                        | CL                | Single-ended    |      | _    | 10   | pF               |

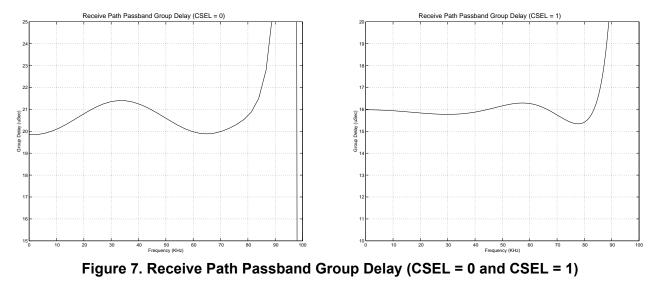

| Group Delay <sup>12</sup>                                   |                   | CSEL = 0        | —    | _    | 22   | μS               |

|                                                             |                   | CSEL = 1        |      | _    | 16   | μS               |

| Differential Group Delay <sup>12</sup>                      |                   | CSEL = 0        |      | _    | 1.5  | μS               |

|                                                             |                   | CSEL = 1        | —    | _    | 1    | μS               |

| Powerup Settling Time <sup>3,13</sup>                       |                   | From powerdown  |      | 200  | 220  | μS               |

Notes:

- 1. GSM input pins RFIGP and RFIGN. DCS input pins RFIDP and RFIDN. PCS input pins RFIPP and RFIPN.

- **2.** Measurement is performed with a 2:1 balun (50  $\Omega$  input, 200  $\Omega$  balanced output) and includes matching network and PCB losses. Measured at max gain (AGAIN[2:0] =100<sub>b</sub>, LNAG[1:0] = 01<sub>b</sub>, LNAC[1:0] = 01<sub>b</sub>) unless otherwise noted. Noise figure measurements are referred to 290 °K. Insertion loss of the balun is removed.

- 3. Specifications guaranteed by characterization using LQW15AN series matching inductors.

- 4. Input signal at balun is -102 dBm. SNR at baseband output is 9 dB.

- 5. AGAIN[2:0]=min=000<sub>b</sub>, LNAG[1:0] = max=01<sub>b</sub>, LNAC[1:0] =max=01<sub>b</sub>.

- **6.** AGAIN[2:0]=min=000<sup>b</sup>, LNAG[1:0] = min=00<sup>b</sup>, LNAC[1:0] = min=00<sup>b</sup>.

- 7. Voltage gain is defined as the differential rms voltage at the RXIP/RXIN pins or RXQP/RXQN pins divided by the rms voltage at the balun input with DACFS[1:0] = 01 and CSEL = 1. Gain is 1.5 dB higher with CSEL = 0. Minimum and maximum values do not include the variation in the DAC full scale voltage (also see Maximum Differential Output Voltage specification).

- 8. Voltage gain is defined as the differential rms voltage at the LNA output divided by the rms voltage at the balun output.

- **9.** Output pins RXIP, RXIN, RXQP, RXQN.

- **10.** Specified as root sum square:  $\sqrt{(RXIP RXIN)^2 + (RXQP RXQN)^2}$ . Drift specification applies to dc offset

calibration and is guaranteed by characterization. See ZERODEL[2:0] in the register description.

- **11.** The baseband signal path is entirely digital. Gain, phase, and offset errors at the baseband outputs are because of the D/A converters. Offsets can be measured and calibrated out. See ZERODEL[2:0] in the register description.

- 12. Group delay is measured from antenna input to baseband outputs. Differential group delay is measured in-band.

- **13.** Includes settling time of the frequency synthesizer. Settling to 5 degrees phase error measured at RXIP, RXIN, RXQP, and RXQN pins.

Downloaded from Elcodis.com electronic components distributor

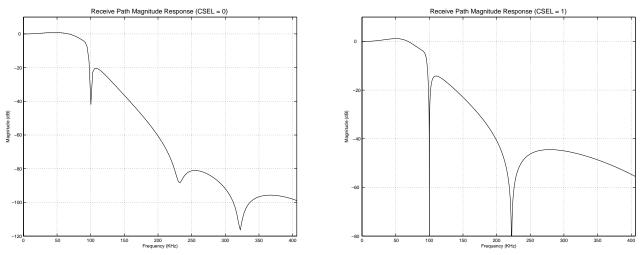

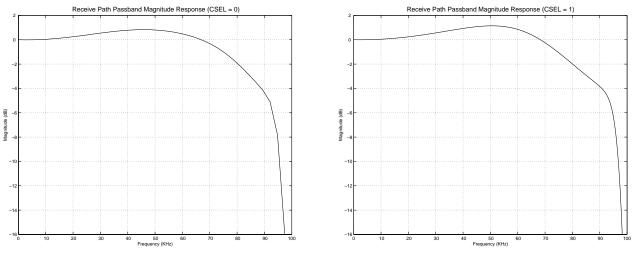

Figure 6. Receive Path Passband Magnitude Response (CSEL = 0 and CSEL = 1)

10

#### **Table 6. Transmitter Characteristics**

(V<sub>DD</sub> = 2.7 to 3.0 V, T<sub>A</sub> = -20 to 85 °C)

| Parameter                                        | Symbol | Test Condition                     | Min  | Тур  | Max  | Unit              |

|--------------------------------------------------|--------|------------------------------------|------|------|------|-------------------|

| RFOG Output Frequency <sup>1</sup>               |        | GSM 850 band                       | 824  | _    | 849  | MHz               |

|                                                  |        | E-GSM 900 band                     | 880  | _    | 915  | MHz               |

| RFOD Output Frequency <sup>2</sup>               |        | DCS 1800 band                      | 1710 |      | 1785 | MHz               |

|                                                  |        | PCS 1900 band                      | 1850 | _    | 1910 | MHz               |

| I/Q Differential Input Swing <sup>3,4</sup>      |        |                                    | 0.88 | _    | 2.2  | V <sub>PPD</sub>  |

| I/Q Input Common-Mode <sup>3</sup>               |        |                                    | 1.1  | _    | 1.4  | V                 |

| I/Q Differential Input Resistance <sup>3,4</sup> |        | BBG[1:0] = 11 <sub>b</sub>         | 26   | 30   | 35   | kΩ                |

|                                                  |        | BBG[1:0] = 00 <sub>b</sub>         | 22   | 25   | 29   | kΩ                |

|                                                  |        | BBG[1:0] = 01 <sub>b</sub>         | 17   | 20   | 23   | kΩ                |

|                                                  |        | Powered down                       |      | Hi-Z |      | kΩ                |

| I/Q Input Capacitance <sup>3,5</sup>             |        |                                    |      |      | 5    | pF                |

| I/Q Input Bias Current <sup>3</sup>              |        |                                    | 13   | 16   | 19   | μA                |

| Sideband Suppression                             |        | 67.7 kHz sinusoid                  |      | -46  | -34  | dBc               |

| Carrier Suppression                              |        | 67.7 kHz sinusoid                  | _    | -48  | -33  | dBc               |

| IM3 Suppression                                  |        | 67.7 kHz sinusoid                  |      | -57  | -50  | dBc               |

| Phase Error <sup>5</sup>                         |        |                                    | _    | 1.9  | 3.0  | o<br>rms          |

|                                                  |        |                                    | _    | 5    | 10   | °<br>PEAK         |

| TXVCO Pushing <sup>1,2</sup>                     |        | Open loop                          | _    | 100  | _    | kHz/V             |

| TXVCO Pulling <sup>1,2</sup>                     |        | VSWR 2:1, all phases,<br>open loop | _    | 200  | _    | kHz <sub>PP</sub> |

| RFOG Output Modulation Spectrum <sup>1,6</sup>   |        | 400 kHz offset                     |      | -65  | -63  | dBc               |

|                                                  |        | 1.8 MHz offset                     |      | -70  | -68  | dBc               |

| RFOD Output Modulation Spectrum <sup>2,6</sup>   |        | 400 kHz offset                     |      | -65  | -63  | dBc               |

|                                                  |        | 1.8 MHz offset                     |      | -70  | -65  | dBc               |

| RFOG Output Phase Noise <sup>1,5,7</sup>         |        | 10 MHz offset                      | _    | -160 | -155 | dBc/Hz            |

|                                                  |        | 20 MHz offset                      |      | -166 | -164 | dBc/Hz            |

| RFOD Output Phase Noise <sup>2,5,7</sup>         |        | 20 MHz offset                      |      | -163 | -157 | dBc/Hz            |

| RFOG Output Power Level <sup>1</sup>             |        | Z <sub>L</sub> = 50 Ω              | 7    | 9    | 11   | dBm               |

| RFOD Output Power Level <sup>2</sup>             |        | Z <sub>L</sub> = 50 Ω              | 6    | 8    | 10   | dBm               |

### Table 6. Transmitter Characteristics (Continued)

(V\_DD = 2.7 to 3.0 V, T\_A = -20 to 85 °C)

| Parameter                                     | Symbol | Test Condition | Min | Тур | Max | Unit |

|-----------------------------------------------|--------|----------------|-----|-----|-----|------|

| RF Output Harmonic Suppression <sup>1,2</sup> |        | 2nd harmonic   | —   | _   | -20 | dBc  |

|                                               |        | 3rd harmonic   | —   | —   | -10 | dBc  |

| Powerup Settling Time <sup>5,8</sup>          |        | From powerdown | —   | _   | 150 | μS   |

Notes:

- **1.** Measured at RFOG pin.

- 2. Measured at RFOD pin.

- **3.** Input pins TXIP, TXIN, TXQP, and TXQN.

- 4. Differential Input Swing is programmable with the BBG[1:0] bits in register 04h. Program these bits to the closest appropriate value. The I/Q Input Resistance scales inversely with the BBG[1:0] setting.

- 5. Specifications guaranteed by characterization.

- 6. Measured with pseudo-random pattern. Carrier power and noise power < 1.8 MHz measured with 30 kHz RBW. Noise power ≥ 1.8 MHz measured with 100 kHz RBW.

- 7. Measured with all 1s pattern.

- 8. Including settling time of the frequency synthesizer. Settling time measured at the RFOD and RFOG pins to 0.1 ppm frequency error.

# Table 7. Frequency Synthesizer Characteristics (V\_{DD} = 2.7 to 3.0 V, T\_A = -20 to 85 $^\circ C$ )

| Parameter                                         | Symbol           | Test Condition                               | Min    | Тур  | Мах    | Unit              |

|---------------------------------------------------|------------------|----------------------------------------------|--------|------|--------|-------------------|

| RF1 VCO Frequency <sup>1</sup>                    | f <sub>RF1</sub> | GSM 850 band                                 | 1737.8 | _    | 1787.8 | MHz               |

|                                                   |                  | E-GSM 900 band                               | 1849.8 |      | 1919.8 | MHz               |

|                                                   |                  | DCS 1800 band                                | 1804.9 |      | 1879.9 | MHz               |

|                                                   |                  | PCS 1900 band                                | 1929.9 |      | 1989.9 | MHz               |

| RF2 VCO Frequency <sup>1</sup>                    | f <sub>RF2</sub> | GSM 850 band                                 | 1272   | _    | 1297   | MHz               |

|                                                   |                  | E-GSM 900                                    | 1279   |      | 1314   | MHz               |

|                                                   |                  | DCS 1800 band                                | 1327   | _    | 1402   | MHz               |

|                                                   |                  | PCS 1900 band                                | 1423   | _    | 1483   | MHz               |

| IF VCO Frequency <sup>1</sup>                     | f <sub>IF</sub>  | GSM 850 band                                 | —      | 896  | —      | MHz               |

|                                                   |                  | E-GSM 900 band<br>880–895 MHz<br>900–915 MHz | _      | 798  | _      | MHz               |

|                                                   |                  | E-GSM 900 band<br>895–900 MHz                |        | 790  | _      | MHz               |

|                                                   |                  | DCS 1800 band                                | _      | 766  | _      | MHz               |

|                                                   |                  | PCS 1900 band                                |        | 854  |        | MHz               |

| RF1 PLL Phase Detector Update<br>Frequency        | $f_{\phi}$       | GSM input,<br>RFUP = 0                       | —      | 200  | _      | kHz               |

|                                                   |                  | DCS/PCS inputs,<br>RFUP = 1                  | _      | 100  | _      | kHz               |

| IF and RF2 PLL Phase Detector<br>Update Frequency | $f_{\phi}$       |                                              | _      | 200  | _      | kHz               |

| RF1 VCO Pushing <sup>2</sup>                      |                  | Open Loop                                    | _      | 500  | _      | kHz/V             |

| RF2 VCO Pushing <sup>2</sup>                      |                  |                                              | _      | 400  | _      | kHz/V             |

| IF VCO Pushing <sup>2</sup>                       |                  |                                              | _      | 300  | —      | kHz/V             |

| RF1 VCO Pulling <sup>2</sup>                      |                  | VSWR = 2:1,                                  | _      | 400  | —      | kHz <sub>PP</sub> |

| RF2 VCO Pulling <sup>2</sup>                      |                  | all phases, open loop                        | _      | 100  | _      | kHz <sub>PP</sub> |

| IF VCO Pulling <sup>2</sup>                       |                  |                                              | _      | 100  | —      | kHz <sub>PP</sub> |

| RF1 PLL Phase Noise <sup>2</sup>                  |                  | 3 MHz offset                                 | _      | -144 | -138   | dBc/Hz            |

| RF2 PLL Phase Noise <sup>2</sup>                  |                  | 400 kHz offset                               | _      | -126 | -121   | dBc/Hz            |

| IF PLL Phase Noise <sup>2</sup>                   |                  | 400 kHz offset                               | _      | -128 | -123   | dBc/Hz            |

| RF1 PLL Spurious <sup>2</sup>                     |                  | 3 MHz offset                                 | _      | -95  | -83    | dBc               |

| RF2 PLL Spurious <sup>2</sup>                     |                  | 400 kHz offset                               | _      | -80  | -75    | dBc               |

| IF PLL Spurious <sup>2</sup>                      |                  | 400 kHz offset                               | _      | -80  | -70    | dBc               |

| Notes:                                            |                  | 1                                            | +      |      | l      |                   |

For the GSM input, the RF1 VCO is divided by two. During transmit, the IF VCO is divided by two.

Specifications are guaranteed by characterization.

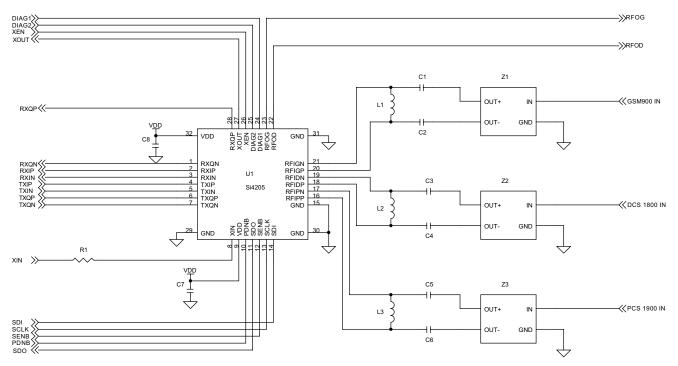

# **Typical Application Schematic**

#### Notes:

- 1. Connect pads on bottom of U1 to GND.

- 2. See "AN92: Aero™ I/Aero™ I+ Transceiver PCB Layout Guidelines" for details on the following:

- LNA matching network (C1–C6, L1–L3). Values should be custom tuned for a specific PCB layout and SAW filter to

optimize performance.

- Differential traces between the SAW filters (Z1–Z3) and transceiver (U1) pins 16–21.

- Detailed SAW filter requirements.

- 3. For the XIN input, no external ac coupling is required.

- 4. For optimum performance, connect pin 31 to ground plane of power amplifier through several vias close to pin.

# **Bill of Materials**

| Component | Value/Description                                      | Supplier(s)                                                                                                                                       |

|-----------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| C1–C2     | 1.2 pF, ±0.1 pF, C0G<br>(GSM 850 and E-GSM 900)        | Murata GRM36C0G series<br>Venkel C0402C0G500 series                                                                                               |

| C3–C4     | 1.2 pF, ±0.1 pF, C0G<br>(DCS 1800)                     | Murata GRM36C0G series<br>Venkel C0402C0G500 series                                                                                               |

| C5–C6     | 1.5 pF, ±0.1 pF, C0G<br>(PCS 1900)                     | Murata GRM36C0G series<br>Venkel C0402C0G500 series                                                                                               |

| C7        | 22 nF, ±20%, Z5U                                       |                                                                                                                                                   |

| C8        | 10 pF, ±20%, C0G                                       |                                                                                                                                                   |

| L1        | 24 nH, ±2%                                             | Murata LQG15HN series (0402 size)<br>Murata LQW15AN series (0402 size)                                                                            |

| L2        | 6.8 nH, ±0.2 nH                                        | Murata LQG15HN series (0402 size)<br>Murata LQW15AN series (0402 size)                                                                            |

| L3        | 5.6 nH, ±0.2 nH                                        | Murata LQG15HN series (0402 size)<br>Murata LQW15AN series (0402 size)                                                                            |

| R1        | 100 Ω, ±5%                                             |                                                                                                                                                   |

| U1        | GSM/GPRS Transceiver                                   | Silicon Laboratories Si4205                                                                                                                       |

| Z1        | GSM 850 RX SAW Filter (150 $\Omega$ balanced output)   | Epcos B39881-B9001-C710 (5-pin, 1.4 x 2.0 mm)<br>Epcos B39881-B9004-E710 (6-pin, 1.6 x 2.0 mm)<br>Murata SAFEK881MFL0T00R00 (6-pin, 1.6 x 2.0 mm) |

|           | E-GSM 900 RX SAW Filter (150 $\Omega$ balanced output) | Epcos B39941-B7820-C710 (5-pin, 1.4 x 2.0 mm)<br>Epcos B39941-B9017-K310 (6-pin, 1.6 x 2.0 mm)<br>Murata SAFEK942MFM0T00R00 (6-pin, 1.6 x 2.0 mm) |

| Z2        | DCS 1800 RX SAW Filter (150 $\Omega$ balanced output)  | Epcos B39182-B7821-C710 (5-pin, 1.4 x 2.0 mm)<br>Epcos B39182-B9013-K310 (6-pin, 1.6 x 2.0 mm)<br>Murata SAFEK1G84FA0T00R00 (6-pin, 1.6 x 2.0 mm) |

| Z3        | PCS 1900 RX SAW Filter (150 $\Omega$ balanced output)  | Epcos B39202-B7825-C710 (5-pin, 1.4 x 2.0 mm)<br>Epcos B39202-B9020-K310 (6-pin, 1.6 x 2.0 mm)<br>Murata SAFEK1G96FA0T00R00 (6-pin, 1.6 x 2.0 mm) |

# **Functional Description**

Figure 8. Aero I Transceiver Block Diagram

The Aero I transceiver is the industry's most integrated RF front end for multi-band GSM/GPRS digital cellular handsets and wireless data modems. The highly integrated solution eliminates the IF SAW filter, external low noise amplifiers (LNAs) for three bands, transmit and RF voltage controlled oscillator (VCO) modules, and more than 70 other discrete components found in conventional designs.

The high level of integration obtained through highperformance packaging and fine line CMOS process technology results in a solution with 50% less area and 80% fewer components than competing solutions. A triple-band GSM transceiver using the Aero I transceiver can be implemented with 15 components in less than 1.2 cm<sup>2</sup> of board area. This level of integration is an enabling force in lowering the cost, simplifying the design and manufacturing, and shrinking the form factor in next-generation GSM/GPRS voice and data terminals.

The receive section uses a digital low-IF architecture that avoids the difficulties associated with direct conversion while delivering lower solution cost and reduced complexity. The baseband interface is

compatible with any supplier's baseband subsystem.

The transmit section is a complete up-conversion path from the baseband subsystem to the power amplifier, and uses an offset phase-locked loop (PLL) with a fully integrated transmit VCO. The frequency synthesizer uses Silicon Laboratories' proven technology, which includes integrated RF and IF VCOs, varactors, and loop filters.

The unique integer-N PLL architecture produces a transient response that is superior in speed to fractional-N architectures without suffering the high phase noise or spurious modulation effects often associated with those designs. This fast transient response makes the Aero I transceiver well suited to GPRS multi-slot applications where channel switching and settling times are critical.

While conventional solutions use BiCMOS or other bipolar process technologies, the Aero I transceiver employs 100% CMOS process. This brings the dramatic cost savings and extensive manufacturing capacity of CMOS to the GSM market.

16

## Receiver

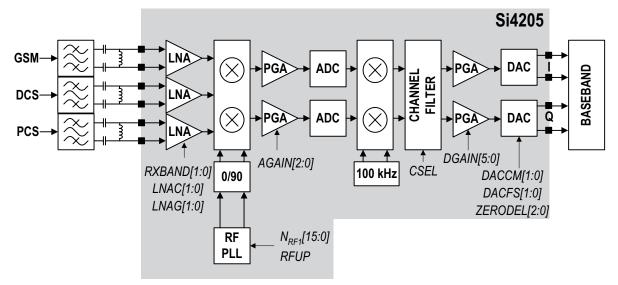

Figure 9. Receiver Block Diagram

The Aero I transceiver uses a low-IF receiver architecture which allows for the on-chip integration of the channel selection filters, eliminating the external RF image reject filters and the IF SAW filter required in conventional superheterodyne architectures. Compared to a direct-conversion architecture, the low-IF architecture has a much greater degree of immunity to dc offsets, which can arise from RF local oscillator (RFLO) self-mixing, 2nd-order distortion of blockers, and device 1/f noise. This relaxes the common-mode balance requirements on the input SAW filters, and simplifies PC board design and manufacturing.

Three differential-input LNAs are integrated. The GSM input supports the GSM 850 (869–894 MHz) or E-GSM 900 (925–960 MHz) bands. The DCS input supports the DCS 1800 (1805–1880 MHz) band. The PCS input supports the PCS 1900 (1930–1990 MHz) band. For quad-band designs, SAW filters for the GSM 850 and E-GSM 900 bands should be connected to a balanced combiner which drives the GSM input for both bands.

The LNA inputs are matched to the 150  $\Omega$  balancedoutput SAW filters through external LC matching networks. The LNA gain is controlled with the LNAG[1:0] and LNAC[1:0] bits in register 05h.

A quadrature image-reject mixer downconverts the RF signal to a 100 kHz intermediate frequency (IF) with the RFLO from the frequency synthesizer. The RFLO frequency is between 1737.8 to 1989.9 MHz, and is internally divided by 2 for GSM 850 and E-GSM 900 modes. The mixer output is amplified with an analog programmable gain amplifier (PGA), which is controlled

with the AGAIN[2:0] bits in register 05h. The quadrature IF signal is digitized with high resolution A/D converters (ADCs).

The ADC output is downconverted to baseband with a digital 100 kHz quadrature LO signal. Digital decimation and IIR filters perform channel selection to remove blocking and reference interference signals. The response of the IIR filter is programmable to a high selectivity setting (CSEL = 0) or a low selectivity setting (CSEL = 1). The low selectivity filter has a flatter group delay response which may be desirable where the final channelization filter is in the baseband chip. After channel selection, the digital output is scaled with a digital PGA, which is controlled with the DGAIN[5:0] bits in register 05h.

The LNAG[1:0], LNAC[1:0], AGAIN[2:0] and DGAIN[5:0] bits must be set to provide a constant amplitude signal to the baseband receive inputs. See "AN51: Aero Transceiver AGC Strategy" for more details.

DACs drive a differential analog signal onto the RXIP, RXIN, RXQP, and RXQN pins to interface to standard analog-input baseband ICs. No special processing is required in the baseband for offset compensation or extended dynamic range. The receive and transmit baseband I/Q pins can be multiplexed together into a 4wire interface. The common mode level at the receive I and Q outputs is programmable with the DACCM[1:0] bits, and the full scale level is programmable with the DACFS[1:0] bits in register 12h.

Downloaded from Elcodis.com electronic components distributor

# Transmitter

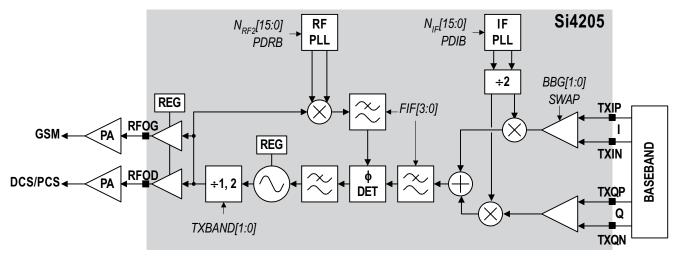

Figure 10. Transmitter Block Diagram

The transmit (TX) section consists of an I/Q baseband upconverter, an offset phase-locked loop (OPLL) and two output buffers that can drive external power amplifiers (PA), one for the GSM 850 (824 to 849 MHz) and E-GSM 900 (880 to 915 MHz) bands and one for the DCS 1800 (1710 to 1785 MHz) and PCS 1900 (1850 to 1910 MHz) bands. The OPLL requires no external duplexer to attenuate transmitter noise or spurious signals in the receive band, saving both cost and power. Additionally, the output of the transmit VCO (TXVCO) is a constant-envelope signal that reduces the problem of spectral spreading caused by non-linearity in the PA.

A quadrature mixer upconverts the differential in-phase (TXIP, TXIN) and quadrature (TXQP, TXQN) signals with the IFLO to generate a SSB IF signal that is filtered and used as the reference input to the OPLL. The IFLO frequency is generated between 766 and 896 MHz and internally divided by 2 to generate the quadrature LO signals for the quadrature modulator, resulting in an IF between 383 and 448 MHz. For the E-GSM 900 band, two different IFLO frequencies are required for spur management. Therefore, the IF PLL must be programmed per channel in the E-GSM 900 band. The IFLO frequencies are defined in Table 7 on page 13.

The OPLL consists of a feedback mixer, a phase detector, a loop filter, and a fully integrated TXVCO. The TXVCO is centered between the DCS 1800 and PCS 1900 bands, and its output is divided by 2 for the GSM 850 and E-GSM 900 bands. The RFLO frequency is generated between 1272 and 1483 MHz. To allow a single VCO to be used for the RFLO, high-side injection is used for the GSM 850 and E-GSM 900 bands, and

low-side injection is used for the DCS 1800 and PCS 1900 bands. The I and Q signals are automatically swapped when switching bands. Therefore, there is no need for the customer to externally swap the I and Q signals. However, for additional layout flexibility, the SWAP bit in register 03h can be used to manually exchange the I and Q signals.

Low-pass filters before the OPLL phase detector reduce the harmonic content of the quadrature modulator and feedback mixer outputs. The cutoff frequency of the filters is programmable with the FIF[3:0] bits in register 04h, and should be set to the recommended settings detailed in the register description.

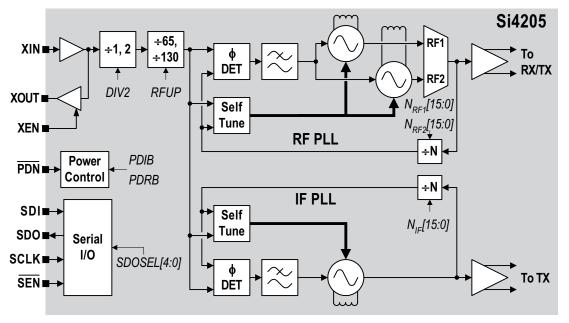

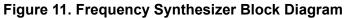

# **Frequency Synthesizer**

The Aero I transceiver integrates two complete PLLs including VCOs, varactors, resonators, loop filters, reference and VCO dividers, and phase detectors. The RF PLL uses two multiplexed VCOs. The RF1 VCO is used for receive mode, and the RF2 VCO is used for transmit mode. The IF PLL is used only during transmit mode. All VCO tuning inductors are also integrated.

The IF and RF output frequencies are set by programming the N-Divider registers,  $N_{RF1}$ ,  $N_{RF2}$  and  $N_{IF}$ . Programming the N-Divider register for either RF1 or RF2 automatically selects the proper VCO. The output frequency of each PLL is as follows:

$$f_{OUT} = N \times f_{\phi}$$

The DIV2 bit in register 31h controls a programmable divider at the XIN pin to allow either a 13 or 26 MHz reference frequency. For receive mode, the RF1 PLL phase detector update rate ( $f_{\varphi}$ ) should be programmed  $f_{\varphi}$  = 100 kHz for DCS 1800 or PCS 1900 bands, and  $f_{\varphi}$  = 200 kHz for GSM 850 and E-GSM 900 bands. For transmit mode, the RF2 and IF PLL phase detector update rates are always  $f_{\varphi}$  =200 kHz.

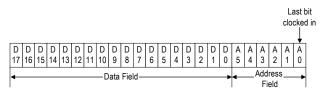

## **Serial Interface**

A three-wire serial interface is provided to allow an external system controller to write the control registers for dividers, receive path gain, powerdown settings, and other controls. The serial control word is 24 bits in length, comprised of an 18-bit data field and a 6-bit address field as shown in Figure 12.

Figure 12. Serial Interface Format

All registers must be written when the PDN pin is asserted (low), except for register 22h. All serial interface pins should be held at a constant level during receive and transmit bursts to minimize spurious emissions. This includes stopping the SCLK clock. A timing diagram for the serial interface is shown in Figure 3 on page 7.

When the serial interface is enabled (i.e., when SEN is low), data and address bits on the SDI pin are clocked into an internal shift register on the rising edge of SCLK. Data in the shift register is then transferred on the rising edge of SEN into the internal data register addressed in the address field. The internal shift register ignores any leading bits before the 24 required bits. The serial interface is disabled when SEN is high.

Optionally, registers can be read as illustrated in Figure 4 on page 7. The serial output data appears on the SDO pin after writing the revision register with the address to be read. Writing to any of the registers causes the function of SDO to revert to its previously programmed function.

# **XOUT Buffer**

The Aero I transceiver contains a reference clock buffer to drive the baseband input. The clock signal from the VC-TCXO is capacitively coupled to the XIN pin. The clock signal is not divided with the XSEL control.

The XOUT buffer is a CMOS driver stage with approximately  $250 \Omega$  of series resistance. This buffer is enabled when the XEN hardware control (pin 26 on the Si4205) is set high, independent of the PDN control pin. To achieve complete powerdown during sleep, the XEN pin must be set low, the XBUF bit in Register 12 must be set to zero, and the XPD1 bit in Register 11 must be set to one. During normal operation, these bits should be set to their default values.

# **Control Registers**

|     |               |      |         |          |                         | . Cak |          | nog  |        | Juin | Bit               |                 |         |                     |                 |      |         |      |         |

|-----|---------------|------|---------|----------|-------------------------|-------|----------|------|--------|------|-------------------|-----------------|---------|---------------------|-----------------|------|---------|------|---------|

| Reg | Name          |      |         | r        | 1                       |       | 1        |      | 1      | E    | bit               |                 | 1       | 1                   | 1               |      | T       | T    |         |

| 1.0 |               | D17  | D16     | D15      | D14                     | D13   | D12      | D11  | D10    | D9   | D8                | D7              | D6      | D5                  | D4              | D3   | D2      | D1   | D0      |

| 01h | Reset         | 0    | 0       | 0        | 0                       | 0     | 0        | 0    | 0      | 0    | 0                 | 0               | 0       | 0                   | 0               | 0    | 0       | 0    | RESET   |

| 02h | Mode          | 0    | 0       | 0        | 0                       | 0     | 0        | 0    | 0      | 0    | 0                 | 0               | 0       | 0                   | 0               | 0    | AUTO    | MOE  | DE[1:0] |

| 03h | Config        | 0    | 0       | 0        | 0                       | DIAG  | 6[1:0]   | SWAP | 0      | 0    | 0                 | TXBAN           | ND[1:0] | RXBA                | RXBAND[1:0] 0 0 |      | 1       | 0    |         |

| 04h | Transmit      | 0    | 0       | 0        | 0                       | 0     | 0        | 0    | 1      | BBG  | [1:0]             |                 | FIF     | 3:0] 0 0            |                 |      | 0       | 0    |         |

| 05h | Receive       | 0    | 0       | 0        | 0                       |       |          | DGAI | N[5:0] |      |                   | 0               | A       | GAIN[2:             | 0]              | LNA  | C[1:0]  | LNA  | .G[1:0] |

| 11h | Config        | 0    | 0       | 0        | 0                       | 0     | )PDS[2:( | )]   | XPD1   | 1    | XSEL              | 0               | 1       | 0                   | 1               | 0    | 0       | 0    | CSEL    |

| 12h | DAC Config    | 0    | 0       | 0        | 0                       | 0     | 0        | 0    | 1      | XBUF | 0                 | ZDBS            | ZE      | RODEL[2:0] DACCM[1: |                 |      |         | DAC  | FS[1:0] |

| 19h | Reserved      | 0    | 0       | 0        | 0                       | 0     | 0        | 0    | 0      | 0    | 0                 | 0               | 0       | 0                   | 0               | 0    | 0       | 0    | 0       |

| 20h | RX Master #1  | RXBA | ND[1:0] |          | N <sub>RF1</sub> [15:0] |       |          |      |        |      |                   |                 |         |                     |                 |      |         |      |         |

| 21h | RX Master #2  | 0    | 0       | )PDS[2:0 | )]                      | LNA   | C[1:0]   | LNA  | G[1:0] | A    | GAIN[2:           | 0]              | 0       | DGAIN[5:0]          |                 |      |         |      |         |

| 22h | RX Master #3  | 0    | 0       | 0        | 0                       | 0     | 0        | 0    | 0      | 0    | 0                 | 0               | 0       |                     |                 | DGA  | IN[5:0] |      |         |

| 23h | TX Master #1  | TXBA | ND[1:0] |          |                         |       |          |      |        |      | N <sub>RF2</sub>  | 2[15:0]         |         |                     |                 |      |         |      |         |

| 24h | TX Master #2  |      | FIF     | [3:0]    |                         |       |          |      |        |      |                   | N <sub>IF</sub> | [13:0]  |                     |                 |      |         |      |         |

| 31h | Config        | 0    | 0       | 0        |                         | SDOS  | EL[3:0]  |      | 0      | 0    | 0                 | 0               | 0       | 0                   | RFUP            | DIV2 | 0       | 0    | 1       |

| 32h | Powerdown     | 0    | 0       | 0        | 0                       | 0     | 0        | 0    | 0      | 0    | 0                 | 0               | 0       | 0                   | 0               | 0    | 0       | PDIB | PDRB    |

| 33h | RF1 N Divider | 0    | 0       |          |                         |       |          |      |        |      | N <sub>RF1</sub>  | [15:0]          |         |                     |                 |      |         |      |         |

| 34h | RF2 N Divider | 0    | 0       |          |                         |       |          |      |        |      | N <sub>RF2</sub>  | 2[15:0]         |         |                     |                 |      |         |      |         |

| 35h | IF N Divider  | 0    | 0       |          |                         |       |          |      |        |      | N <sub>IF</sub> [ | [15:0]          |         |                     |                 |      |         |      |         |

| 3Ah | Reserved      | 0    | 0       | 0        | 0                       | 0     | 0        | 0    | 0      | 0    | 0                 | 0               | 0       | 0                   | 0               | 1    | 0       | 0    | 1       |

| 3Eh | Reserved      | 0    | 0       | 0        | 0                       | 0     | 0        | 0    | 0      | 0    | 0                 | 0               | 0       | 0                   | 0               | 1    | 1       | 1    | 1       |

| 3Fh | Reserved      | 0    | 0       | 0        | 0                       | 0     | 0        | 0    | 0      | 0    | 0                 | 0               | 0       | 0                   | 1               | 0    | 0       | 0    | 0       |

#### Table 8. Register Summary

#### Notes:

1. Any register not listed here is reserved and should not be written. Writing to reserved registers may result in unpredictable behavior.

2. Master registers 20h to 24h simplify programming the Aero I to support initiation of receive (RX) and transmit (TX) operations with only two register writes.

3. See "AN50: Aero Transceiver Programming Guide" for detailed instructions on register programming.

#### Register 01h. Reset

| Bit  | D17 | D16 | D15 | D14   | D13 | D12        | D11                    | D10                | D9                            | D8                  | D7                  | D6     | D5      | D4 | D3 | D2 | D1 | D0                 |

|------|-----|-----|-----|-------|-----|------------|------------------------|--------------------|-------------------------------|---------------------|---------------------|--------|---------|----|----|----|----|--------------------|

| Name | 0   | 0   | 0   | 0     | 0   | 0          | 0                      | 0                  | 0                             | 0                   | 0                   | 0      | 0       | 0  | 0  | 0  | 0  | RESET              |

| Bit  | :   |     | Na  | ame   |     |            |                        |                    |                               |                     |                     | Funct  | tion    |    |    |    |    |                    |

| 17:  | 1   |     | Res | erved |     | Pr         | ogram                  | n to ze            | ro.                           |                     |                     |        |         |    |    |    |    |                    |

| 0    |     |     | RE  | SET   |     | 0 :<br>1 : | = Rese<br>ote: Se<br>w | mal op<br>et all r | egiste<br>ntrol R<br>o 0 twie | ers to c<br>egister | default<br>rs" on p | bage 2 | 1 for m |    |    |    |    | nust be<br>gisters |

#### Register 02h. Mode Control

| Bit  | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2   | D1  | D0     |

|------|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|------|-----|--------|

| Name | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | AUTO | MOD | E[1:0] |

| Bit  | Name      | Function                                                                                                                                                                                                                                                        |

|------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17:3 | Reserved  | Program to zero.                                                                                                                                                                                                                                                |

| 2    | AUTO      | Automatic Mode Select.         0 = Manual. Mode is controlled by MODE[1:0] bits (default).         1 = Automatic. Last register write to N <sub>RF1</sub> implies RX mode; Last register write to N <sub>RF2</sub> implies TX mode. MODE[1:0] bits are ignored. |

| 1:0  | MODE[1:0] | Transmit/Receive/Cal Mode Select.00 = Receive mode (default).01 = Transmit mode.10 = Calibration mode.11 = Reserved.Note: These bits are valid only when AUTO = 0.                                                                                              |

**Note:** Calibration must be performed each time the power supply is applied. To initiate the calibration mode, set MODE[1:0] = 10 and pulse the PDN pin high for at least 150  $\mu$ s.

## Register 03h. Configuration

| Bit  | D17 | D16 | D15  | D14    | D13  | D12                  | D11                     | D10                                             | D9                                              | D8                        | D7                                                     | D6                                                | D5                 | D4      | D3     | D2            | D1             | D0   |

|------|-----|-----|------|--------|------|----------------------|-------------------------|-------------------------------------------------|-------------------------------------------------|---------------------------|--------------------------------------------------------|---------------------------------------------------|--------------------|---------|--------|---------------|----------------|------|

| Name | 0   | 0   | 0    | 0      | DIAG | 6[1:0]               | SWAP                    | 0                                               | 0                                               | 0                         | TXBAN                                                  | ND[1:0]                                           | RXBA               | ND[1:0] | 0      | 0             | 1              | 0    |

| Bit  | :   |     | Na   | ame    |      |                      |                         |                                                 |                                                 |                           | F                                                      | unct                                              | ion                |         |        |               |                |      |

| 17:1 | 4   |     | Res  | erved  |      | Pro                  | ogram                   | to ze                                           | ſO.                                             |                           |                                                        |                                                   |                    |         |        |               |                |      |

| 13:1 | 2   |     | DIA  | G[1:0] |      | 00<br>01<br>10<br>11 | =<br>=<br>=<br>te: Th   | DI<br>LC<br>LC<br>HI<br>HI<br>nese pi<br>ust be | AG1<br>OW<br>OW<br>GH<br>GH<br>ns can<br>progra | be use<br>mmed<br>desirec | DIA<br>LO\<br>HIG<br>LO\<br>HIG<br>ed to co<br>with th | W (de<br>GH<br>W<br>GH<br>on <u>trol</u><br>e PDN | antenn<br>I pin is | zero    | The DI | AG1 <u>/D</u> | <u>IA</u> G2 p | oins |

| 11   |     |     | SV   | WAP    |      | 0 =                  | <b>ansm</b> i<br>= Norn | i <b>t I/Q S</b><br>nal (de                     | Swap.<br>efault)                                |                           |                                                        |                                                   |                    |         |        |               |                |      |

| 10:8 | 3   |     | Res  | erved  |      | Pro                  | ogram                   | to ze                                           | ſ0.                                             |                           |                                                        |                                                   |                    |         |        |               |                |      |

| 7:6  | i   |     | TXBA | ND[1:  | 0]   | 00<br>01<br>10       | = GS<br>= DC<br>= PC    | it Ban<br>M 850<br>S 180<br>S 1900<br>Served    | or E-<br>0.<br>0.                               | ect.<br>GSM S             | 900 (d                                                 | efault                                            | ).                 |         |        |               |                |      |

| 5:4  |     |     | RXBA | ND[1:  | 0]   | 00<br>01<br>10       | = GS<br>= DC<br>= PC    | Band<br>M inpu<br>S inpu<br>S inpu<br>served    | ut (def<br>it.<br>t.                            |                           |                                                        |                                                   |                    |         |        |               |                |      |

| 3:2  | 2   |     | Res  | erved  |      | Pro                  | ogram                   | to ze                                           | ſ0.                                             |                           |                                                        |                                                   |                    |         |        |               |                |      |

| 1    |     |     | Res  | erved  |      | Pro                  | ogram                   | to on                                           | e.                                              |                           |                                                        |                                                   |                    |         |        |               |                |      |

| 0    |     |     | Res  | erved  |      | Pro                  | ogram                   | to ze                                           | ro.                                             |                           |                                                        |                                                   |                    |         |        |               |                |      |

## Register 04h. Transmit Control

| Bit  | D17 | D16 | D15 | D14    | D13                                                                                                                    | D12                                                                                                                                     | D11   | D10     | D9  | D8     | D7 | D6    | D5    | D4       | D3      | D2     | D1 | D0 |

|------|-----|-----|-----|--------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------|---------|-----|--------|----|-------|-------|----------|---------|--------|----|----|

| Name | 0   | 0   | 0   | 0      | 0                                                                                                                      | 0                                                                                                                                       | 0     | 1       | BBG | 6[1:0] |    | FIF   | [3:0] | <u> </u> | 0       | 0      | 0  | 0  |

| Bit  | t   |     | Na  | ame    |                                                                                                                        |                                                                                                                                         |       |         |     |        |    | Funct | ion   |          |         |        |    |    |

| 17:1 | 1   |     | Res | erved  |                                                                                                                        | Pr                                                                                                                                      | ogram | to ze   | ro. |        |    |       |       |          |         |        |    |    |

| 10   |     |     | Res | erved  |                                                                                                                        | Pr                                                                                                                                      | ogram | n to on | e.  |        |    |       |       |          |         |        |    |    |

| 9:8  | 3   |     | BB  | G[1:0] |                                                                                                                        |                                                                                                                                         |       |         |     |        |    |       |       |          | egister | to the |    |    |

| 7:4  |     |     | FIF | [3:0]  |                                                                                                                        | nearest value. <b>TX IF Filter Cutoff Frequency.</b> 0111 = Use for GSM 850, E-GSM 900 and PCS 1900 bands.0110 = Use for DCS 1800 band. |       |         |     |        |    |       |       |          |         |        |    |    |

| 3:0  | )   |     | Res | erved  | Note:         Use the recommended setting for each band. Other settings reserved.           I         Program to zero. |                                                                                                                                         |       |         |     |        |    |       |       |          |         |        |    |    |

Register 05h. Receive Gain

| Bit  | D17 | D16 | D15 | D14     | D13 | D12                                               | D11                                                                                       | D10                                                                         | D9                                   | D8             | D7      | D6     | D5        | D4        | D3      | D2     | D1       | D0     |

|------|-----|-----|-----|---------|-----|---------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------|----------------|---------|--------|-----------|-----------|---------|--------|----------|--------|

| Name | 0   | 0   | 0   | 0       |     |                                                   | DGAI                                                                                      | N[5:0]                                                                      |                                      |                | 0       | A      | AGAIN[2:( | )]        | LNAC    | C[1:0] | LNAC     | G[1:0] |

| Bit  | :   |     | Na  | ame     |     |                                                   |                                                                                           |                                                                             |                                      |                | F       | Funct  | ion       |           |         |        |          |        |

| 17:1 | 4   |     | Res | erved   |     | Pro                                               | ogram                                                                                     | to zer                                                                      | ю.                                   |                |         |        |           |           |         |        |          |        |

| 13:8 | 8   |     | DGA | IN[5:0  | ]   | 001<br>011<br><br>3F                              | h = 0 0<br>h = 1 0<br>h = 63<br><b>te:</b> Se                                             |                                                                             | fault).<br>51: Aer                   |                |         | r AGC  | Strateç   | gy" for ( | details | on set | ting the | e gain |

| 7    |     |     | Res | erved   |     | Pro                                               | ogram                                                                                     | to zer                                                                      | ю.                                   |                |         |        |           |           |         |        |          |        |

| 6:4  |     |     | AGA | IN[2:0  | ]   | 000<br>00<br>01<br>01<br>100<br>100<br>110<br>111 | 0 = 0 (<br>1 = 4 (<br>0 = 8 (<br>1 = 12<br>0 = 16<br>1 = Re<br>0 = Re<br>1 = Re<br>te: Se | dB.<br>dB.                                                                  | fault).<br>d.<br>d.<br>d.<br>51: Aer |                |         | r AGC  | Strateç   | gy" for   | details | on set | ting the | egain  |

| 3:2  | 2   |     | LNA | .C[1:0] |     | 00<br>01<br>10<br>11                              | = Min<br>= Max<br>= Res<br>= Res                                                          | is Cur<br>imum<br>ximum<br>served<br>served<br>ogram                        | currer<br>curre                      | nt (def<br>nt. | fault). | me val | ue as l   | _NAG[     | 1:0].   |        |          |        |

| 1:0  |     |     | LNA | .G[1:0] |     | 00<br>01<br>10<br>11                              | = Min<br>= Max<br>= Res<br>= Res<br>tes:<br>1. Pr<br>2. Se                                | in Cor<br>imum<br>ximum<br>served<br>served<br>ogram<br>se "ANS<br>gisters. | gain (<br>gain.<br>these<br>51: Aer  | bits to        | the sa  |        |           |           |         | on set | ting the | egain  |

## Register 11h. Configuration

| Bit  | D17 | D16              | D15 | D14    | D13 | D12                   | D11                              | D10                         | D9                                | D8                                                              | D7                                                 | D6               | D5                | D4                | D3     | D2 | D1      | D0   |

|------|-----|------------------|-----|--------|-----|-----------------------|----------------------------------|-----------------------------|-----------------------------------|-----------------------------------------------------------------|----------------------------------------------------|------------------|-------------------|-------------------|--------|----|---------|------|

| Name | 0   | 0                | 0   | 0      | [   | )PDS[2:(              | )]                               | XPD1                        | 1                                 | XSEL                                                            | 0                                                  | 1                | 0                 | 1                 | 0      | 0  | 0       | CSEL |

| Bit  |     |                  | Na  | ame    |     |                       |                                  |                             |                                   |                                                                 |                                                    | Funct            | ion               |                   |        |    |         |      |

| 17:1 | 4   |                  | Res | erved  |     | Pro                   | ogram                            | to zei                      | О.                                |                                                                 |                                                    |                  |                   |                   |        |    |         |      |

| 13:1 | 1   |                  | DPD | )S[2:0 | ]   | 11 <sup>.</sup><br>01 | 1= Us<br>1= Us                   | e for D                     | SM 8<br>CS 1                      | <b>Start.</b><br>50 and<br>800 ar<br>mended                     | nd PC                                              | S 190            | 0 ban             | ds (de            | ,      |    | reserve | ed.  |

| 10   |     |                  | XI  | PD1    |     | 0 =<br>1 =            | = Refe<br>= Refe<br>te: Th<br>po | rence<br>rence<br>his bit s | buffe<br>buffe<br>hould<br>wn cur | r autor<br>r disab<br>be set<br>rent (I <sub>F</sub><br>ust als | natica<br>oled.<br>to 0 du<br><sub>2DN</sub> ), th | uring nais bit s | ormal o<br>should | operati<br>be set | on. To |    |         |      |

| 9    |     |                  | Res | erved  |     | Pro                   | ogram                            | to on                       | e.                                |                                                                 |                                                    |                  |                   |                   |        |    |         |      |

| 8    |     | Reserved<br>XSEL |     |        |     |                       | = No d<br>= Divic                | ivider.<br>Ie XIN           | XIN =<br>by 2.                    | icy Se<br>= 13 M<br>XIN =<br>ock sho                            | Hz (d<br>26 M                                      | Hz.              |                   | Hz.               |        |    |         |      |

| 7    |     |                  | Res | erved  |     | Pro                   | ogram                            | to zei                      | о.                                |                                                                 |                                                    | -                |                   |                   |        |    |         |      |

| 6    |     |                  | Res | erved  |     | Pro                   | ogram                            | to on                       | e.                                |                                                                 |                                                    |                  |                   |                   |        |    |         |      |