# **Product Overview**

TRC103 is a single chip, multi-channel, low power UHF transceiver. It is designed for low cost, high volume, two-way short range wireless applications in the 863-870, 902-928 and 950-960 MHz frequency bands. The TRC103 is FCC & ETSI certifiable. All critical RF and base-band functions are integrated in the TRC103, minimizing external component count and simplifying and speeding design-ins. A microcontroller, RF SAW filter, 12.8 MHz crystal and a few passive components are all that is needed to create a complete, robust radio function. The TRC103 incorporates a set of low-power states to reduce overall current consumption and extend battery life. The small size and low power consumption of the TRC103 make it ideal for a wide variety of short range radio applications. The TRC103 complies with Directive 2002/95/EC (RoHS).

# **Key Features**

- Modulation: FSK or OOK with frequency hopping and DTS spread spectrum capability

- Frequency ranges: 863-870, 902-928 and 950-960 MHz

- High sensitivity: -112 dBm in circuit

- High data rate: up to 200 kb/s •

- Low receiver current: 3.3 mA typical

- Low sleep current: 0.1 µA typical

- Up to +11 dBm in-circuit transmit power

- Operating supply voltage: 2.1 to 3.6 V •

- Programmable preamble •

- Programmable packet start pattern

- Integrated RF, PLL, IF and base-band circuitry •

- Integrated data & clock recovery •

- Programmable RF output power

- PLL lock output

- Transmit/receive FIFO size programmable up to 64 bytes

- Continuous, Buffered and Packet data modes

- Packet address recognition

- Packet handling features:

- · Fixed or variable packet length

- Packet filtering

- Packet formatting

- Standard SPI interface

- TTL/CMOS compatible I/O pins

- Programmable clock output frequency

- Low cost 12.8 MHz crystal reference

- Integrated RSSI

- Integrated crystal oscillator

- Host processor interrupt pins

- Programmable data rate

- External wake-up event inputs •

- Integrated packet CRC error detection

- Integrated DC-balanced data scrambling

- Integrated Manchester encoding/decoding

- Interrupt signal mapping function •

- Support for multiple channels •

- Four power-saving modes

- Low external component count

- Small 32-pin QFN plastic package

- Standard 13 inch reel, 3K pieces

# Applications

- Active RFID tags

- Automated meter reading

- Home & industrial automation

- Security systems

- Two-way remote keyless entry

- Automobile immobilizers

- Sports performance monitoring

- Wireless toys •

- Medical equipment

- Low power two-way telemetry systems

- Wireless mesh sensor networks

- Wireless modules

# **TRC103**

# **RF** Transceiver

863-960 MHz

# **Table of Contents**

| 1.0 Pin Configuration                                        | 4  |

|--------------------------------------------------------------|----|

| 1.1 Pin Description                                          | 4  |

| 2.0 Functional Description                                   | 5  |

| 2.1 RF Port                                                  | 7  |

| 2.2 Transmitter                                              | 7  |

| 2.3 Receiver                                                 | 8  |

| 2.4 Crystal Oscillator                                       | 9  |

| 2.5 Frequency Synthesizer                                    | 10 |

| 2.6 PLL Loop Filter                                          | 10 |

| 3.0 Operating Modes                                          | 11 |

| 3.1 Receiving in Continuous Mode                             |    |

| 3.2 Continuous Mode Data and Clock Recovery                  |    |

| 3.3 Continuous Mode Start Pattern Recognition                |    |

| 3.4 RSSI                                                     |    |

| 3.5 Receiving in Buffered Data Mode                          |    |

| 3.6 Transmitting in Continuous or Buffered Data Modes        | 17 |

| 3.7 IRQ0 and IRQ1 Mapping                                    |    |

| 3.8 Buffered Clock Output                                    |    |

| 3.9 Packet Data Modes                                        |    |

| 3.9.1 Fixed Length Packet Mode                               | 19 |

| 3.9.2 Variable Length Packet Mode                            |    |

| 3.9.3 Extended Variable Length Packet Mode                   |    |

| 3.9.4 Packet Payload Processing in Transmit and Receive      |    |

| 3.9.5 Packet Filtering                                       |    |

| 3.9.6 Cyclic Redundancy Check                                |    |

| 3.9.7 Manchester Encoding                                    |    |

| 3.9.8 DC-Balanced Scrambling                                 |    |

| 3.10 SPI Configuration Interface.                            | 25 |

| 3.11 SPI Data FIFO Interface                                 |    |

| 4.0 Configuration Register Memory Map                        | 28 |

| 4.1 Main Configuration Registers (MCFG)                      |    |

| 4.2 Interrupt Configuration Registers (IRQCFG)               |    |

| 4.3 Receiver Configuration Registers (RXCFG)                 |    |

| 4.4 Start Pattern Configuration Registers (SYNCFG)           |    |

| 4.5 Transmitter Configuration Registers (TXCFG)              |    |

| 4.6 Oscillator Configuration Register (OSCFG)                |    |

| 4.7 Packet Handler Configuration Registers (PKTCFG)          |    |

| 4.8 Page Configuration Register (PGCFG)                      |    |

| 5.0 Electrical Characteristics                               | 40 |

| 5.1 DC Electrical Characteristics                            | 40 |

| 5.2 AC Electrical Characteristics                            | 41 |

| 6.0 TRC103 Design In Steps                                   | 43 |

| 6.1 Determining Frequency Specific Hardware Component Values | 43 |

| 6.1.1 SAW Filters and Related Component Values               |    |

| 6.1.2 Voltage Controlled Oscillator Component Values         |    |

| 6.2 Determining Configuration Values for FSK Modulation      | 44 |

| 6.2.1 Bit Rate Related FSK Configuration Values              |    |

| 6.2.2 Determining Transmitter Power Configuration Values     |    |

| 6.3 Determining Configuration Values for OOK Modulation          | 47 |

|------------------------------------------------------------------|----|

| 6.3.1 Bit Rate Related OOK Configuration Values                  | 47 |

| 6.3.2 OOK Demodulator Related Configuration Values               | 49 |

| 6.3.3 OOK Transmitter Related Configuration Values               | 50 |

| 6.4 Frequency Synthesizer Channel Programming for FSK Modulation | 51 |

| 6.5 Frequency Synthesizer Channel Programming for OOK Modulation | 52 |

| 6.6 TRC103 Data Mode Selection and Configuration                 | 53 |

| 6.6.1 Continuous Data Mode                                       | 53 |

| 6.6.2 Buffered Data Mode                                         | 55 |

| 6.6.3 Packet Data Mode                                           | 57 |

| 6.7 Battery Power Management Configuration Values                | 61 |

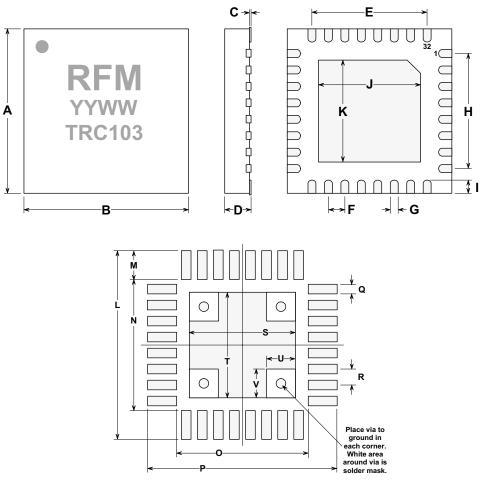

| 7.0 Package Dimensions and Typical PCB Footprint - QFN-32        | 63 |

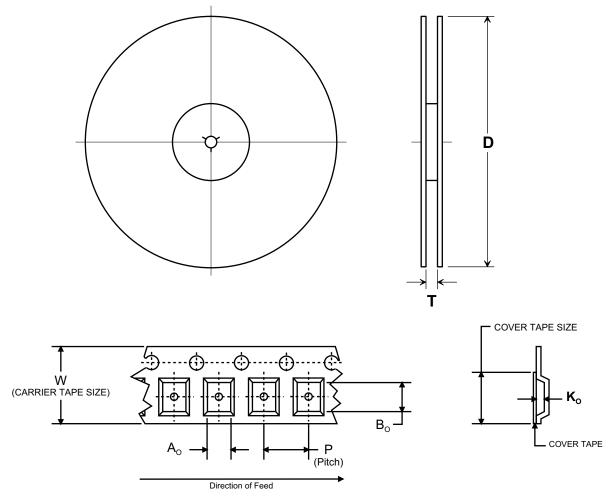

| 8.0 Tape and Reel Dimensions                                     | 64 |

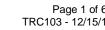

# **1.0 Pin Configuration**

# **1.1 Pin Description**

| PIN | TYPE | NAME       | DESCRIPTION                                       |

|-----|------|------------|---------------------------------------------------|

| 1   | -    | GND        | CONNECT TO GND                                    |

| 2   | -    | GND        | CONNECT TO GND                                    |

| 3   | 0    | VDD_VCO    | REGULATED SUPPLY FOR VCO                          |

| 4   | I/O  | TANK-      | VCO TANK                                          |

| 5   | I/O  | TANK+      | VCO TANK                                          |

| 6   | I/O  | PLL-       | PLL LOOP FILTER OUTPUT                            |

| 7   | I/O  | PLL+       | PLL LOOP FILTER INPUT                             |

| 8   | -    | GND        | CONNECT TO GND                                    |

| 9   | -    | GND        | CONNECT TO GND                                    |

| 10  | I    | XTAL-      | CRYSTAL CONNECTION (OSCILLATOR OUTPUT)            |

| 11  | I    | XTAL+      | CRYSTAL CONNECTION (OSCILLATOR INPUT)             |

| 12  | -    | GND        | CONNECT TO GND                                    |

| 13  | -    | NC         | NO CONNECT - FLOAT IN NORMAL OPERATION            |

| 14  | I    | nSS_CONFIG | SLAVE SELECT FOR SPI CONFIGURATION DATA           |

| 15  | I    | nSS_DATA   | SLAVE SELECT FOR SPI TX/RX DATA                   |

| 16  | 0    | SDO        | SERIAL DATA OUT                                   |

| 17  | I    | SDI        | SERIAL DATA IN                                    |

| 18  | I    | SCK        | SERIAL SPI CLOCK IN                               |

| 19  | 0    | CLKOUT     | BUFFERED CLOCK OUTPUT                             |

| 20  | I/O  | DATA       | TRANSMIT/RECEIVE DATA                             |

| 21  | 0    | IRQ0       | INTERRUPT OUTPUT                                  |

| 22  | 0    | IRQ1/DCLK  | INTERRUPT OUTPUT/RECOVERED DATA CLOCK (CONT MODE) |

| 23  | 0    | PLL_LOCK   | PLL LOCKED INDICATOR                              |

| 24  | -    | GND        | CONNECT TO GND                                    |

| 25  | -    | GND        | CONNECT TO GND                                    |

| 26  | I    | VDD        | MAIN 3.3 V SUPPLY VOLTAGE                         |

| 27  | 0    | VDD_ANALOG | REGULATED SUPPLY FOR ANALOG CIRCUITRY             |

| 28  | 0    | VDD_DIG    | REGULATED SUPPLY FOR DIGITAL CIRCUITRY            |

| 29  | 0    | VDD_PA     | REGULATED SUPPLY FOR RF POWER AMP                 |

| 30  | -    | GND        | CONNECT TO GND                                    |

| 31  | I/O  | RF-        | RF I/O                                            |

| 32  | I/O  | RF+        | RF I/O                                            |

| PAD | -    | GROUND     | GROUND PAD ON PKG BOTTOM                          |

Table 1

www.RFM.com E-mail: info@rfm.com ©2009-2010 by RF Monolithics, Inc.

Technical support +1.800.704.6079

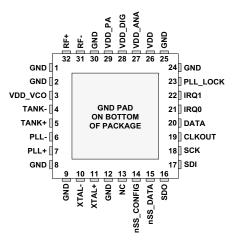

# 2.0 Functional Description

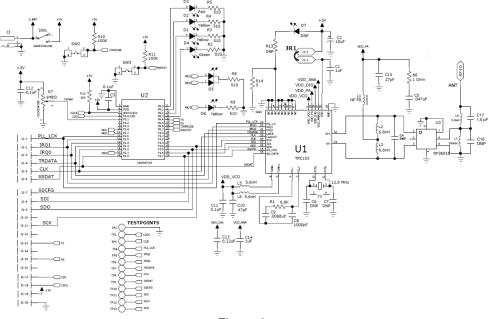

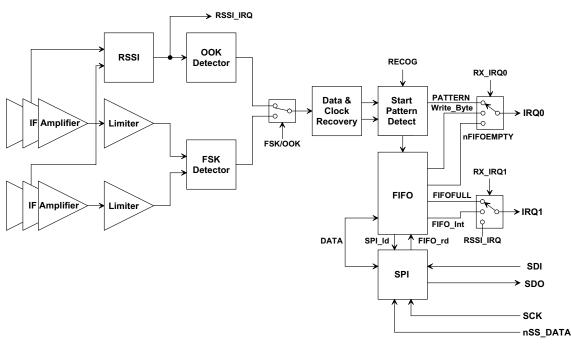

The TRC103 is a single-chip transceiver that can operate in the 863-870 and 902-928 MHz license-free bands, and in the 950-960 MHz RFID band. The TRC103 supports two modulation schemes - FSK and OOK. The TRC103's highly integrated architecture requires a minimum of external components, while maintaining design flexibility. All major RF communication parameters are programmable and most can be dynamically set. The TRC103 is optimized for very low power consumption (3.3 mA typical in receiver mode). It complies with European ETSI, FCC Part 15 and Canadian RSS-210 regulatory standards. Advanced digital features including the TX/RX FIFO and the packet handling data mode significantly reduce the load on the host microcontroller.

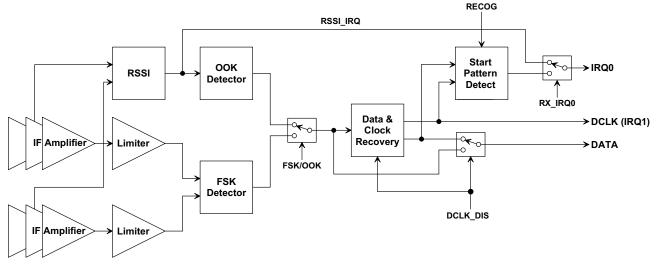

**TRC103 Block Diagram**

The receiver is based on a superheterodyne architecture. It is composed of the following major blocks:

- An LNA that provides low noise RF gain followed by an RF band-pass filter.

- A first mixer which down-converts the RF signal to an intermediate frequency equal to 1/9 th of the carrier frequency (about 100 MHz for 915 MHz signals).

- A variable gain first IF preamplifier followed by two second mixers which down convert the first IF signal to I and Q signals at a low frequency (zero-IF for FSK, low-IF for OOK).

- A two-stage IF filter followed by an amplifier chain for both the I and Q channels. Limiters at the end of each chain drive the I and Q inputs to the FSK demodulator function. An RSSI signal is also derived from the I and Q IF amplifiers to drive the OOK detector. The second filter stage in each channel can be configured as either a third-order Butterworth low-pass filter for FSK operation or an image reject polyphase band-pass filter for OOK operation.

- An FSK arctangent type demodulator driven from the I and Q limiter outputs, and an OOK demodulator driven by the RSSI signal. Either detector can drive a data and clock recovery function that provides matched filter enhancement of the demodulated data.

The transmitter chain is based on the same double-conversion architecture and uses the same intermediate frequencies as the receiver chain. The main blocks include:

- A digital waveform generator that provides the I and Q base-band signals. This block includes digital-toanalog converters and anti-aliasing low-pass filters.

- A compound image-rejection mixer to up convert the base-band signal to the first IF at 1/9th of the carrier frequency, and a second image-rejection mixer to up-convert the IF signal to the RF frequency

- Transmitter driver and power amplifier stages to drive the antenna port

The frequency synthesizer is based on an integer-N PLL having an typical frequency step size of 12.5 kHz. Two programmable frequency dividers in the feedback loop of the PLL and one programmable divider on the reference oscillator allow the LO frequency to be adjusted. The reference frequency is generated by a crystal oscillator running at 12.8 MHz.

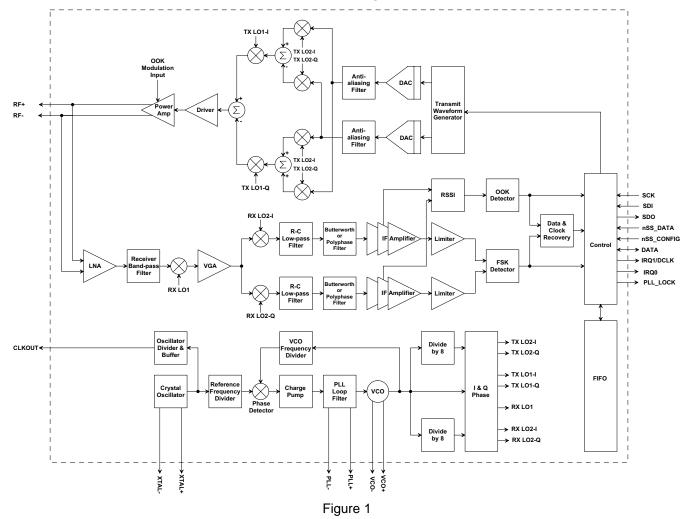

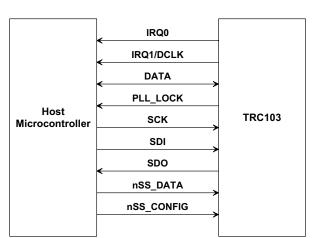

The TRC103 is controlled by a digital block that includes registers to store the configuration settings of the radio. These registers are accessed by a host microcontroller through an SPI style serial interface. The microcontroller's serial connections to the TRC103's SDI, SDO and SCK pins are shown in Figure 2 (component values shown are for 950-960 MHz operation; see Tables 53 and 54 for other frequency bands). On-chip regulators provide stable supply voltages to sensitive blocks and allow the TRC103 to be used with supply voltages from 2.1 to 3.6 V. Most blocks are supplied with a voltage below 1.6 V.

www.RFM.com E-mail: info@rfm.com ©2009-2010 by RF Monolithics, Inc. Technical support +1.800.704.6079

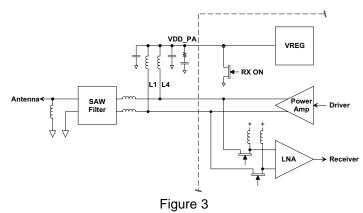

# 2.1 RF Port

The receiver and the transmitter share the same RF pins. Figure 3 shows the implementation of the common front-end. In transmit mode, the PA and the PA regulator are on; the voltage on VDD\_PA pin is the nominal voltage of the regulator, about 1.8 V. The external inductances L1 and L4 are used for the PA. In receive mode, both PA and PA regulator are off, and VDD\_PA is tied to ground. The external inductances L1 and L4 are used for biasing and matching the LNA, which is implemented as a common gate amplifier.

#### Internal RF Port Detail

#### 2.2 Transmitter

The TRC103 is set to transmit mode when **MCFG00\_Chip\_Mode[7..5]** bits are set to 100. In continuous mode the transmitted data is sent directly to the modulator. The host microcontroller is provided with a bit rate clock by the TRC103 to clock the data; using this clock to send the data synchronously is mandatory in FSK configuration and optional in OOK configuration. In buffered mode the data is first written into the 64-byte FIFO via the SPI interface; data from the FIFO is then sent to the modulator.

At the front end of the transmitter, I and Q signals are generated by the base-band circuit which contains a digital waveform generator, two D/A converters and two anti-aliasing low-pass filters. The I and Q signals are two quadrature sinusoids whose frequency is the selected frequency deviation. In FSK mode, the phase shift between I and Q is switched between +90° and -90° according to the input data. The modulation is then performed at this stage, since the information contained in the phase shift will be converted into a frequency shift when the I and Q signals are combined in the first mixers. In OOK mode, the phase shift is kept constant whatever the data. The combination of the I and Q signals in the first mixers creates a fixed frequency signal at a low intermediate frequency which is equal to the selected frequency deviation. After D/A conversion, both I and Q signals are filtered by anti-aliasing filters whose bandwidth is programmed with the register **TXCFG1A\_TXInterpfilt[7..4]**. Behind the filters, a set of four mixers combines the I and Q signals and converts them into two I and Q signals at the second intermediate frequency which is equal to 1/8 of the LO frequency, which in turn is equal to 8/9 of the RF frequency. These two new I and Q signals are then combined and up-converted to the desired RF frequency by two quadrature mixers fed by the LO signals. The signal is then amplified by a driver and power amplifier stage.

| MCFG0C_PA_ramp[43] | T <sub>PA</sub> (μs) | Rise/fall (µs) |

|--------------------|----------------------|----------------|

| 00                 | 3                    | 2.5/2          |

| 01                 | 8.5                  | 5/3            |

| 10                 | 15                   | 10/6           |

| 11                 | 23                   | 20/10          |

| Table | 2 |

|-------|---|

|-------|---|

www.RFM.com E-mail: info@rfm.com ©2009-2010 by RF Monolithics, Inc. Technical support +1.800.704.6079

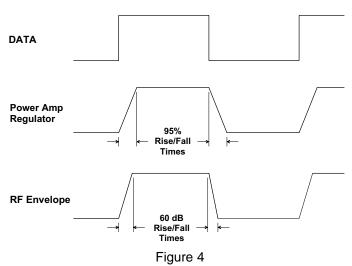

OOK modulation is performed by switching on and off the power amplifier and its regulator. The rise and fall times of the OOK signal can be configured in register **MCFG0C\_PA\_ramp[4..3]**, which controls the charge and discharge time of the regulator. Figure 4 shows the time constants set by **MCFG0C\_PA\_ramp[4..3]**. Table 2 gives typical values of the rise and fall times as defined in Figure 4 when the capacitance connected to the output of the regulator is 0.047  $\mu$ F.

OOK Modulation Waveforms

# 2.3 Receiver

The TRC103 is set to receive mode when **MCFG00\_Chip\_Mode[7..5]** is set to 011. The receiver is based on a double-conversion architecture. The front-end is composed of an LNA and a mixer whose gains are constant. The mixer down-converts the RF signal to an intermediate frequency which is equal to 1/8 of the LO frequency, which in turn is equal to 8/9 of the RF frequency. Behind this first mixer there is a variable gain IF amplifier that can be programmed from maximum gain to 13.5 dB less in 4.5 dB steps with the **MCFG01\_IF\_Gain[1..0]** register.

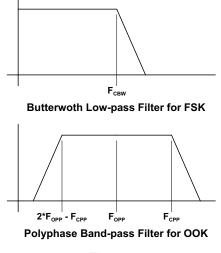

After the variable gain IF amplifier, the signal is down-converted into two I and Q base-band signals by two guadrature mixers which are fed by reference signals at 1/8 the LO frequency. These I and Q signals are then filtered and amplified before demodulation. The first filter is a second-order passive R-C filter whose bandwidth can be programmed to 16 values with the register **RXCFG10\_LP\_filt[7..4**]. The second filter can be configured as either a third-order Butterworth active filter which acts as a low-pass filter for the zero-IF FSK configuration, or as a polyphase band-pass filter for the low-IF OOK configuration. To select Butterworth low-pass filter operation, bit RXCFG12\_PolyFilt\_En[7] is set to 0. The bandwidth of the Butterworth filter can be programmed to 16 values with the register RXCFG10\_BW\_Filt[3..0]. The low-IF configuration must be used for OOK modulation. This configuration is enabled when the bit **RXCFG12** PolyFilt En[7] is set to 1. The center frequency of the polyphase filter can be programmed to 16 values with the register **RXCFG11\_PolyFilt[7..4]**. The bandwidth of the filter can be programmed with the register RXCFG10 BW Filt[3..0]. In OOK mode, the value of the low-IF is equal to the deviation frequency defined in register MCFG02 Freq dev. In addition to channel filtering, the function of the polyphase filter is to reject the image. Figure 5 below shows the two configurations of the second IF filter. In the Butterworth configuration, F<sub>CBW</sub> is the 3 dB cutoff frequency. In the polyphase band-pass configuration F<sub>OPP</sub> is the center frequency given by RXCFG11\_PolyFilt[7..4], and F<sub>CPP</sub> is the upper 3 dB bandwidth of the filter whose offset, referenced to F<sub>OPP</sub>, is given by **RXCFG10\_BW\_Filt[3..0]**.

#### **TRC103 Second IF Filter Details**

Figure 5

After filtering, the I and Q signals are each amplified by a chain of 11 amplifiers having 6 dB of gain each. The outputs of these amplifiers and their intermediate 3 dB nodes are used to evaluate the received signal strength (RSSI). Limiter are located behind the 11 amplifiers of the I and Q chains and the signals at the output of these limiters are used by the FSK demodulator. The RSSI output is used by the OOK demodulator. The global bandwidth of the whole base-band chain is given by the bandwidths of the passive filter, the Butterworth filter, the amplifier chain and the limiter. The maximum achievable global bandwidth when the bandwidths of the first three blocks are programmed at their upper limit is about 350 kHz.

# 2.4 Crystal Oscillator

Crystal specifications for the TRC103 reference oscillator are given in Table 3. RFM recommends the XTL1020P crystal, which is specifically designed for use with the TRC103. Note that crystal frequency error will directly translate to carrier frequency, bit rate and frequency deviation error.

| Specification                                         | Min  | Typical                   | Max  | Units  |

|-------------------------------------------------------|------|---------------------------|------|--------|

| Nominal frequency                                     | -    | 12.80000<br>(fundamental) | -    | MHz    |

| Load capacitance for Fs                               | 13.5 | 15                        | 16.5 | pF     |

| Motional resistance                                   | -    | -                         | 50   | Ω      |

| Motional capacitance                                  | 5    | -                         | 20   | fF     |

| Shunt capacitance                                     | 1    | -                         | 7    | pF     |

| Calibration tolerance at 25 °C                        | -    |                           | ±10  | ppm    |

| Stability over temperature range<br>(-40 °C to 85 °C) | 1    | -                         | ±15  | ppm    |

| Aging in first 5 years                                | -    | -                         | ±2   | ppm/yr |

# 2.5 Frequency Synthesizer

The Frequency Synthesizer generates the local oscillator (LO) signal for the receiver and transmitter sections. The core of the synthesizer is implemented with an integer-N PLL architecture.

The frequency is set by three divider parameters R, P and S. R is the frequency divider ratio in the reference frequency path. P and S set the frequency divider ratio in the feedback loop of the PLL. The frequency synthesizer includes a crystal oscillator which provides the frequency reference for the PLL. The equations giving the relationships between the reference crystal frequency, the local oscillator frequency and RF carrier frequency are given below:

$F_{LO} = F_{XTAL}^*(75^*(P + 1) + S)/(R + 1)$ , with P and S in the range 0 to 255, S less than (P + 1), R in the range 64 to 169, and  $F_{LO}$  and  $F_{XTAL}$  in MHz.

$F_{RF} = 1.125^*F_{LO}$ , where  $F_{RF}$  and  $F_{LO}$  are in MHz

$F_{LO}$  is the first local oscillator (VCO) frequency,  $F_{XTAL}$  is the reference crystal frequency and  $F_{RF}$  is the RF channel frequency.

$F_{LO}$  is the frequency used for the first down-conversion of the receiver and the second up-conversion of the transmitter. The intermediate frequency used for the second down-conversion of the receiver and the first up-conversion of the transmitter is equal to 1/8 of  $F_{LO}$ . As an example, with a crystal frequency of 12.8 MHz and an RF frequency of 869 MHz,  $F_{LO}$  is 772.4 MHz and the first IF of the receiver is 96.6 MHz.

There are two sets of divider ratio registers: SynthR1[7..0], SynthP1[7..0], SynthS1[7..0], and SynthR2[7..0], SynthP2[7..0], SynthS2[7..0]. The MCFG00\_RF\_Frequency[0] bit is used to select which set of registers to use as the current frequency setting. For frequency hopping applications, this reduces the programming and synthesizer settling time when changing frequencies. While the data is being transmitted, the next frequency is programmed and ready. When the current transaction is complete, the MCFG00\_RF\_Frequency[0] bit is complemented and the frequency shifts to the next freq according to the contents of the divider ratio registers. This process is repeated for each frequency hop.

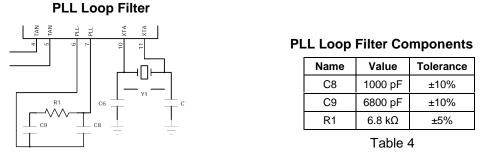

# 2.6 PLL Loop Filter

The loop filter for the frequency synthesizer is shown in Figure 6.

Figure 6

Typical recommended component values for the frequency synthesizer loop filter are provided in Table 4 above. The loop filter settings are not dependent on the frequency band, so they can be universally used on all designs. PLL lock status can be provided on Pin 23 by setting the **IRQCFG0E\_PLL\_LOCK\_EN[0]** bit to a 1 (default). When the PLL is locked Pin 23 (PLL\_LOCK) is high, and when the PLL is unlocked Pin 23 is low. The lock status of the PLL can also be checked by reading the **IRQCFG0E\_PLL\_LOCK\_ST[1]** bit. Note that this bit latches high each time the PLL locks and must be reset by writing a 1 to it.

# 3.0 Operating Modes

The TRC103 has 5 possible chip-level modes. The chip-level mode is set by **MCFG00\_Chip\_Mode[7..5]**, which is a 3-bit pattern in the configuration register. Table 5 summarizes the chip-level modes:

| MCFG00_Chip_Mode[75] | Chip-level Mode                               | Enabled Functions                              |

|----------------------|-----------------------------------------------|------------------------------------------------|

| 0 0 0                | Sleep                                         | None                                           |

| 001                  | Standby                                       | Crystal oscillator                             |

| 010                  | Synthesizer Crystal and frequency synthesizer |                                                |

| 011                  | Receive Crystal, frequency synthesizer and r  |                                                |

| 100                  | Transmit                                      | Crystal, frequency synthesizer and transmitter |

#### Table 5

Table 6 gives the state of the digital pins for the different chip-level modes and settings:

| PIN Function | Sleep<br>Mode | Standby<br>Mode | Synthesizer<br>Mode | Receive<br>Mode | Transmit<br>Mode |

|--------------|---------------|-----------------|---------------------|-----------------|------------------|

| nSS_CONFIG*  | -             | -               | Ι                   | -               | -                |

| nSS_DATA*    | -             | -               | Ι                   | I               |                  |

| IRQ0         | TRI           | 0               | 0                   | 0               | 0                |

| IRQ1         | TRI           | 0               | 0                   | 0               | 0                |

| DATA         | TRI           | TRI             | TRI                 | 0               | -                |

| CLKOUT       | TRI           | 0               | 0                   | 0               | 0                |

| SDO**        | TRI/O         | TRI/O           | TRI/O               | TRI/O           | TRI/O            |

| SDI          | I             | I               | I                   | I               | I                |

| SCK          | I             | I               | I                   | I               | I                |

I = Input, O = Output, TRI = High impedance

\*nSS\_CONFIG has priority OVER nSS\_DATA

\*\*SDO is an output if nSS\_CONFIG = 0 and/or nSS\_DATA = 0

#### Table 6

The TRC103 transmitter and receiver sections support three data handling modes of operation:

- Continuous mode: each bit transmitted or received is accessed directly at the DATA input/output pin.

- Buffered mode: a 64-byte FIFO is used to store each data byte transmitted or received. This data is written to and read from the FIFO through the SPI bus.

- Packet handling mode: in addition to using the FIFO, this data mode builds the complete packet in transmit mode and extracts the useful data from the packet in receive mode. The packet includes a preamble, a start pattern (sync pattern), an optional node address and length byte and the data. Packet data mode can also be configured to perform additional operations like CRC error detection and DC-balanced Manchester encoding or data scrambling.

The Buffered and Packet data modes allow the host microcontroller overhead to be significantly reduced. The DATA pin is bidirectional and is used in both transmit and receive modes. In receive mode, DATA represents the demodulated received data. In transmit mode, input data is applied to this pin.

The working length of the FIFO can set to 16, 32, 48 or 64 bytes through the **MCFG05\_FIFO\_depth[7..6]** register. In the discussions below describing the FIFO behavior, the explanations are given with an assumption of 64 bytes, but the principle is the same for the four possible FIFO sizes.

The status of the FIFO can be monitored via interrupts which are described in Section 3.7. In addition to the straightforward nFIFOEMPY and FIFOFULL interrupts, additional configurable interrupts Fifo\_Int\_Tx and Fifo\_Int\_Rx are also available.

A low-to-high transition occurs on Fifo\_Int\_Rx when the number of bytes in the FIFO is greater than or equal to the threshold set by **MCFG05\_FIFO\_thresh[5..0]** (number of bytes  $\geq$  FIFO\_thresh).

A low-to-high transition occurs on Fifo\_Int\_Tx when the number of bytes in the FIFO is less than or equal to the threshold set by **MCFG05\_FIFO\_thresh[5..0]** (number of bytes  $\leq$  FIFO\_thresh).

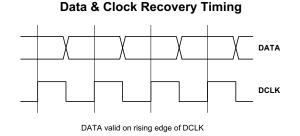

# 3.1 Receiving in Continuous Data Mode

The receiver operates in continuous mode when the **MCFG01\_Mode[5]** bit is set low. In this mode, the receiver has two output signals indicating recovered clock, DCLK and recovered NRZ bit DATA. DCLK is connected to output pin IRQ1 and DATA is connected to pin DATA configured in output mode. The data and clock recovery controls the recovered clock signal, DCLK. Data and clock recovery is enabled by **RXCFG12\_DCLK\_Dis[6]** to 0 (default value). The clock recovered from the incoming data stream appears at DCLK. When data and clock recovery is disabled, the DCLK output is held low and the raw demodulator output appears at DATA. The function of data and clock recovery is to remove glitches from the data stream and to provide a synchronous clock at DCLK. The output DATA is valid at the rising edge of DCLK as shown in Figure 8.

#### **TRC103 Continuous Mode Demodulation**

Figure 7

As shown in Figure 7, the demodulator section includes the FSK demodulator, the OOK demodulator, data and clock recovery and the start pattern detection blocks.

If FSK is selected, the demodulation is performed by analyzing the phase between the I and Q limited signals at the output of the base-band channels.

If OOK is selected, the demodulation is performed by comparing the RSSI output value stored in **RXCFG14\_ RSSI[7..0]** register to the threshold which can be either a fixed value or a time-variant value depending on the past history of the RSSI output. Table 7 gives the three main possible procedures, which can be selected via the register **MCFG01\_RX\_OOK[4..3]**:

| OOK Mode          | MCFG01_RX_OOK[43]                                                    | Description                                                  |  |

|-------------------|----------------------------------------------------------------------|--------------------------------------------------------------|--|

| Eine d Thus shald | 00                                                                   | RSSI output is compared with a fixed threshold stored in     |  |

| Fixed Threshold   | 00                                                                   | MCFG04_OOK_thresh                                            |  |

| Deale             | 04                                                                   | RSSI output is compared with a threshold which is at a fixed |  |

| Peak              | 01                                                                   | offset below the maximum RSSI.                               |  |

| Average           | Average 10 RSSI output is compared with the average of the last RSSI |                                                              |  |

#### Table 7

If the end-user application requires direct access to the output of the demodulator, then the **RXCFG12\_ DCLK\_Dis[6]** bit is set to 1 disabling the clock recovery. In this case the demodulator output is directly connected to the DATA pin and the IRQ1 pin (DCLK) is set to low.

For proper operation of the TRC103 demodulator in FSK mode, the modulation index  $\beta$  of the input signal should meet the following condition:

$$\beta = \frac{2^* \mathsf{F}_{\mathsf{DEV}}}{\mathsf{BR}} \ge 2$$

where F<sub>DEV</sub> is the frequency deviation in hertz (Hz) and BR is the data rate in bits per second (b/s).

#### 3.2 Continuous Mode Data and Clock Recovery

The raw output signal from the demodulator may contain jitter and glitches. Data and clock recovery converts the data output of the demodulator into a glitch-free bit-stream DATA and generates a synchronized clock DCLK to be used for sampling the DATA output as shown in Figure 8. DCLK is available on pin IRQ1 when the TRC103 operates in continuous mode.

Figure 8

To ensure correct operation of the data and clock recovery circuit, the following conditions have to be satisfied:

- A 1-0-1-0... preamble of at least 24 bits is required for synchronization

- The transmitted bit stream must have at least one transition from 0 to 1 or from 1 to 0 every 8 bits during transmission

- The bit rate accuracy must be better than 2 %.

Data and clock recovery is enabled by default. It is controlled by **RXCFG12\_DCLK\_Dis[6]**. If data and clock recovery is disabled, the output of the demodulator is directed to DATA and the DCLK output (IRQ1 Pin in continuous mode) is set to 0.

The received bit rate is defined by the value of the **MCFG03\_Bit\_Rate[6..0]** configuration register, and is calculated as follows:

$BR = F_{XTAL}/(64^{*}(D + 1))$ , with D in the range of 0 to 127

with BR the bit rate in kb/s,  $F_{XTAL}$  the crystal frequency in kHz, and D the value in **MCFG03\_Bit\_Rate[6..0]**. For example, using a 12.8 MHz crystal (12,800 kHz), the bit rate is 25 kb/s when D = 7.

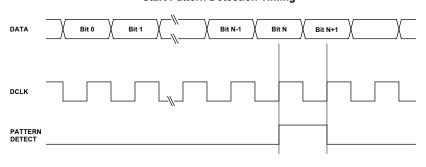

# 3.3 Continuous Mode Start Pattern Recognition

Start pattern detection (recognition) is activated by setting the **RXCFG12\_Recog[5]** bit to 1. The demodulated signal is compared with a pattern stored in the **SYNCFG** registers. The Start Pattern Detect (PATTERN) signal, mapped to output pin IRQ0, is driven by the output of this comparator and is synchronized by DCLK. It is set to 1 when a start pattern match is detected, otherwise it is set to 0. The Start Pattern Detect output is updated at the rising edge of DCLK. The number of bytes used for comparison is defined in the **RXCFG12\_Pat\_sz[4..3]** register and the number of tolerated bit errors for the pattern detection is defined in the **RXCFG12\_Ptol[2..1]** register. Figure 9 illustrates the pattern detection process.

Start Pattern Detection Timing

Figure 9

Note that start pattern detection is enabled only if data and clock recovery is enabled.

# 3.4 RSSI

The received signal strength is measured in the amplifier chains behind the second mixers. Each amplifier chain is composed of 11 amplifiers each having a gain of 6 dB and an intermediate output at 3 dB. By monitoring the two outputs of each stage, an estimation of the signal strength with a resolution of 3 dB and a dynamic range of 63 dB is obtained without IF gain compensation. This estimation is performed 16 times over a period of the I and Q signals and the 16 samples are averaged to obtain a final RSSI value with a 0.5 dB step. The period of the I and Q signal is the inverse of the deviation frequency, which is the low-IF frequency in OOK mode. The RSSI effective dynamic range can be increased to 70 dB by adjusting **MCFG01\_IF\_Gain[1..0]** for less gain on high signal levels.

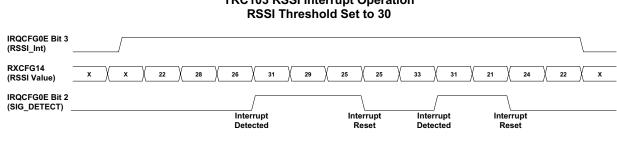

The RSSI block can be used in interrupt mode by setting the bit IRQCFG0E\_RSSI\_Int[3] to 1. When RXCFG14 \_ **RSSI**[7..0] is equal or greater than a predefined value stored in **IRQCFG0F RSSI** thid [7..0], the bit **IRQCFG0E** SIG\_DETECT[2] goes high and an interrupt signal RSSI\_IRQ is generated on pin IRQ0 if IRQCFG0D\_RX\_ **IRQ0[7..6]** is set to 01 (see Table 8). The interrupt is cleared by writing a 1 to bit **IRQCFG0E** SIG DETECT[2]. If the bit RSSI IRQ remains high, the process starts again. Figure 10 shows the timing diagram of RSSI in interrupt mode.

# 3.5 Receiving in Buffered Data Mode

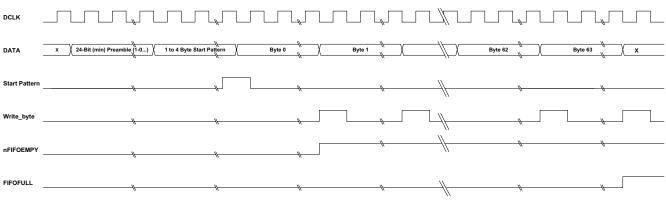

The receiver works in buffered mode when the MCFG01 Mode[5] bit is set to 1. In this mode, the output of the data and clock recovery, i.e., the demodulated and resynchronized signal and the clock signal DCLK are not sent directly to the output pins DATA and IRQ1 (DCLK). These signals are used to store the demodulated data in blocks of 8 bits in a 64-byte FIFO. Figure 11 shows the receiver chain in this mode. The FSK and OOK demodulators, data and clock recovery circuit and start pattern detect block work as described for Continuous data mode, but they are used with two additional blocks, the FIFO and SPI.

#### **TRC103 Bufferd & Packet Mode Demodulation**

When the TRC103 is in receive mode and **MCFG01\_Mode [5]** bit is set to 1, all of the blocks described above are enabled. In a normal communication frame, the data stream is comprised of preamble bytes, a start pattern and the data. Upon receipt of a matching start pattern the receiver recognizes the start of data, strips off the preamble and start pattern, and stores the data in the FIFO for retrieval by the host microcontroller. This automated data extraction reduces the loading on the host microcontroller.

The **IRQCFG0E\_Start\_Fill[7]** bit determines how the FIFO is filled. If **IRQCFG0E\_Start\_Fill[7]** is set to 0, data only fills the FIFO when a pattern match is detected. Received data bits are shifted into the pattern recognition block which continuously compares the received data with the contents of the **SYNCFG** registers. If a match occurs, the pattern matching block output is set for one bit period and the **IRQCFG0E\_Start\_Det[6]** bit is also set. This internal signal can be mapped to the IRQ0 output using interrupt signal mapping. Once a pattern match has occurred, the pattern recognition block will remain inactive until **IRQCFG0E\_Start\_Det[6]** bit is reset.

If **IRQCFG0E\_Start\_Fill**[7] is set to 1, FIFO filling is initiated by asserting **IRQCFG0E\_Start\_Det**[6]. Once 64 bytes have been written to the FIFO the **IRQCFG0D\_FIFOFULL**[2] signal is set. Data should then be read out. If no action is taken, the FIFO will overflow and subsequent data will be lost. If this occurs the **IRQCFG0D\_ FIFO\_OVR**[0] bit is set to 1. The **IRQCFG0D\_FIFOFULL**[2] signal can be mapped to pin IRQ1 as an interrupt for a microcontroller if **IRQCFG0D\_RX\_IRQ1[5..4]** is set to 01. To recover from an overflow, a 1 must be written to **IRQCFG0D\_FIFO\_OVR**[0]. This clears the contents of the FIFO, resets all FIFO status flags and re-initiates pattern matching. Pattern matching can also be re-initiated during a FIFO filling sequence by writing a 1 to **IRQCFG0E\_Start\_Det**[6].

The details of the FIFO filling process are shown in Figure 12. As the first byte is written into the FIFO, signal **IRQCFG0D\_nFIFOEMPY[1]** is set indicating at least one byte is present. The host microcontroller can then read the contents of the FIFO through the SPI interface. When all data is read from the FIFO, **IRQCFG0D\_ nFIFOEMPY[1]** is reset. When the last bit of the 64<sup>th</sup> byte has been written into the FIFO, signal **IRQCFG0D\_ FIFOFULL[2]** is set. Data must be read before the next byte is received or it will be overwritten.

The **IRQCFG0D\_nFIFOEMPY[1]** signal can be used as an interrupt signal for the host microcontroller by mapping to pin IRQ0 if **IRQCFG0D\_RX\_IRQ0[7..6]** is set to 10. Alternatively, the WRITE\_byte signal may also be used as an interrupt if **IRQCFG0D\_RX\_IRQ0[7..6]** is set to 01.

Demodulation in Buffered data mode occurs in the same way as in Continuous data mode. Received data is directly read from the FIFO and the DATA and DCLK pins are not used. Data and clock recovery in Buffered data mode is automatically enabled. DCLK is not externally available.

The pattern recognition block is automatically enabled in buffered mode. The Start Pattern Detect (PATTERN) signal can be mapped to pin IRQ0. In Buffered data mode RSSI operates the same way as in Continuous data mode. However, RSSI\_IRQ may be mapped to IRQ1 instead of to IRQ0 in continuous mode.

TRC103 RX FIFO Fill

Figure 12

# 3.6 Transmitting in Continuous or Buffered Data Modes

The transmitter operates in Continuous data mode when the **MCFG01\_Mode [5]** bit is set to 0. Bit clock DCLK is available on pin IRQ1. Bits are clocked into the transmitter on the rising edge of this clock. Data must be stable 2  $\mu$ s before the rising edge of DCLK and must be held for 2  $\mu$ s following the rising edge of this clock (T<sub>SUDATA</sub>). To meet this requirement, data can be changed on the falling edge of DCLK. In FSK mode DCLK must be used but is optional in OOK mode.

The transmitter operates in Buffered data mode when the MCFG01\_Mode [5] bit is set to 1. Data to be transmitted is written to the 64-byte FIFO through the SPI interface. FIFO data is loaded byte-by-byte into a shift register which then transfers the data bit-by-bit to the modulator. FIFO operation in transmit mode is similar to receive mode. Transmission can start immediately after the first byte of data is written into the FIFO or when the FIFO is full, as determined by the IRQCFG0E\_Start\_Full[4] bit setting. If the transmit FIFO is full, the interrupt signal **IRQCFG0D** FIFOFULL[2] is asserted on pin IRQ1. If data is written into the FIFO while it is full, the flag IRQCFG0D\_FIFO\_OVR[0] will be set to 1 and the previous FIFO contents will be overwritten. The IRQCFG0D\_ FIFO\_OVR[0] flag is cleared by writing a 1 to it. At the same time the contents of the FIFO are cleared. Once the last data byte in the FIFO is loaded into the shift register driving the transmitter modulator, the flag **IRQCFG0D**\_ nFIFOEMPY[1] is set to 0 on pin IRQ0. If new data is not written to the FIFO and the last bit has been transferred to the modulator, the IRQCFG0E\_TX\_ STOP[5] bit goes high as the modulator starts to send the last bit. The transmitter must remain on one bit period after TX STOP to transmit the last bit. If the transmitter is switched off (switched to another mode), the transmission stops immediately even if there is still data in the shift register. In transmit mode the two interrupt signals are IRQ0 and IRQ1. IRQ1 is mapped to IRQCFG0D FIFOFULL[2] signal indicating that the transmission FIFO is full when **IRQCFG0D TX IRQ1[3]** is set to 0, or to **IRQCFG0E TX** STOP[5] when IRQCFG0D\_TX\_IRQ1[3] is set to 1. IRQ0 is mapped to the IRQCFG0D\_nFIFOEMPY[1] signal. This signal indicates the transmitter FIFO is empty and must be refilled with data to continue transmission.

# 3.7 IRQ0 and IRQ1 Mapping

Two TRC103 outputs are dedicated to host microcontroller interrupts or signaling. The interrupts are IRQ0 and IRQ1 and each have selectable sources. Tables 8, 9, 10 and 11 below summarize the interrupt mapping options. These interrupts are especially useful in Continuous or Buffered data mode operation.

| IRQCFG0D_RX_IRQ0 | Data Mode  | IRQ0    | IRQ0 Interrupt Source                            |

|------------------|------------|---------|--------------------------------------------------|

| 00               | Continuous | Output  | Start Pattern Detect                             |

| 01               | Continuous | Output  | RSSI_IRQ                                         |

| 10               | Continuous | Output  | Start Pattern Detect                             |

| 11               | Continuous | Output  | Start Pattern Detect                             |

| 00               | Buffered   | Output  | None (set to 0)                                  |

| 01               | Buffered   | Output  | Write_byte                                       |

| 10               | Buffered   | Output  | nFIFOEMPY                                        |

| 11               | Buffered   | Output  | Start Pattern Detect                             |

| 00               | Packet     | Output  | Data_Rdy                                         |

| 01               | Packet     | Output  | Write_byte                                       |

| 10               | Packet     | Output  | nFIFOEMPY                                        |

| 11               | Packet     | Quitout | Node Address Match if<br>ADDRS_cmp is enabled    |

|                  | i doket    | Output  | Start Pattern Detect if<br>ADDRS_cmp is disabled |

#### Table 8

| IRQCFG0D_RX_IRQ1 | Data Mode  | IRQ1   | IRQ1 Interrupt Source |

|------------------|------------|--------|-----------------------|

| 00               | Continuous | Output | DCLK                  |

| 01               | Continuous | Output | DCLK                  |

| 10               | Continuous | Output | DCLK                  |

| 11               | Continuous | Output | DCLK                  |

| 00               | Buffered   | Output | None (set to 0)       |

| 01               | Buffered   | Output | FIFOFULL              |

| 10               | Buffered   | Output | RSSI_IRQ              |

| 11               | Buffered   | Output | FIFO_Int_Rx           |

| 00               | Packet     | Output | CRC_OK                |

| 01               | Packet     | Output | FIFOFULL              |

| 10               | Packet     | Output | RSSI_IRQ              |

| 11               | Packet     | Output | FIFO_Int_Rx           |

#### Table 9

## Tables 10 and 11 describe the interrupts available in transmit mode:

| IRQCFG0D_TX_IRQ0 | Data Mode  | IRQ0   | IRQ0 Interrupt Source |

|------------------|------------|--------|-----------------------|

| 0                | Continuous | Output | None (set to 0)       |

| 1                | Continuous | Output | None (set to 0)       |

| 0                | Buffered   | Output | FIFO_thresh           |

| 1                | Buffered   | Output | nFIFOEMPY             |

| 0                | Packet     | Output | FIFO_thresh           |

| 1                | Packet     | Output | nFIFOEMPY             |

#### Table 10

| IRQCFG0D_TX_IRQ1 | Data Mode  | IRQ1   | IRQ0 Interrupt Source |

|------------------|------------|--------|-----------------------|

| 0                | Continuous | Output | DCLK                  |

| 1                | Continuous | Output | DCLK                  |

| 0                | Buffered   | Output | FIFOFULL              |

| 1                | Buffered   | Output | TX_Stop               |

| 0                | Packet     | Output | FIFOFULL              |

| 1                | Packet     | Output | TX_Stop               |

#### Table 11

www.RFM.com E-mail: info@rfm.com ©2009-2010 by RF Monolithics, Inc. Technical support +1.800.704.6079

# 3.8 Buffered Clock Output

The buffered clock output is a signal derived from  $F_{XTAL}$ . It can be used as a reference clock for the host microcontroller and is output on the CLKOUT pin. The **OSCFG1B\_Clkout\_En[7]** bit controls the CLKOUT pin. When this bit is set to 1, CLKOUT is enabled, otherwise it is disabled. The output frequency of CLKOUT is defined by the value of the **OSCFG1B\_Clk\_freq[6..2]** parameter which gives the frequency divider ratio applied to  $F_{XTAL}$ . Refer to Table 40 for programming details. Note: CLKOUT is disabled when the TRC103 is in sleep mode. If sleep mode is used, the host microcontroller must have provisions to run from its own clock source.

# 3.9 Packet Data Modes

The TRC103 provides optional on-chip RX and TX packet handling features. These features ease the development of packet oriented wireless communication protocols and free the MCU resources for other tasks. The options include enabling protocols based on fixed and variable packet lengths, data scrambling, CRC checksum calculations, and received packet filtering. All the programmable parameters of the packet handler are accessible through the PKTCFG configuration registers of the device. The packet handling mode is enabled when the register bit **MCFG01\_Packet\_HdI\_En[2]** is set to 1.

The packet handler supports three types of packet formats: fixed length packets, variable length packets, and extended variable length packets. The **PKTCFG1E\_Pkt\_mode[7]** bit selects either the fixed or the variable length packet formats.

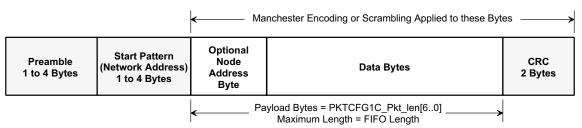

#### 3.9.1 Fixed Length Packet Mode

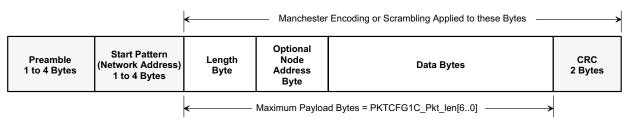

The fixed length packet mode is selected by setting the **PKTCFG1E\_Pkt\_mode[7]** bit to 0. In this mode the length of the packet is set by the **PKTCFG1C\_Pkt\_len[6..0]** register up to the size of the FIFO which has been selected. The length stored in this register is the length of the payload which includes the message data bytes and optional address byte. The fixed length packet format shown in Figure 13 is made up of the following fields:

- 1. Preamble

- 2. Start pattern (network address)

- 3. Node address byte (optional)

- 4. Data bytes

- 5. Two-byte CRC checksum (optional)

# Fixed Length Packet Format

The Preamble, Start Pattern and CRC bytes are added to the packet by the TRC103 during transmit and removed from the packet during receive.

Figure 13

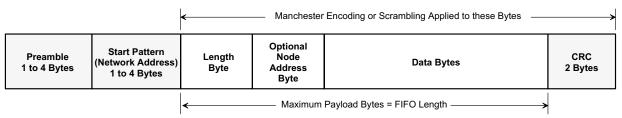

#### 3.9.2 Variable Length Packet Mode

The variable length packet mode is selected by setting bit **PKTCFG1E\_Pkt\_mode[7]** to 1. The packet format shown in Figure 14 is programmable and is made up of the following fields:

- 1. Preamble

- 2. Start pattern (network address)

- 3. Length byte

- 4. Node address byte (optional)

- 5. Data bytes

- 6. Two-byte CRC checksum (optional)

#### Variable Length Packet Format

The Preamble, Start Pattern and CRC bytes are added to the packet by the TRC103 during transmit and removed from the packet during receive.

Figure 14

In variable length packet mode, the length of the rest of the payload is given by the first byte written to the FIFO. The length byte itself is not included in this count. The **PKTCFG1C\_Pkt\_len[6..0]** parameter is used to set the maximum received payload length allowed. Any received packet having a value in the length byte greater than this maximum is discarded. The variable length packet format accommodates payloads, including the length byte, up to the length of the FIFO.

#### 3.9.3 Extended Variable Length Packet Mode

The extended variable length packet mode is selected by setting bit **PKTCFG1E\_Pkt\_mode[7]** to 1 and setting **PKTCFG1C\_Pkt\_len[6..0]** to a value between 65 and 127. The packet format shown in Figure 15 is programmable and is made up of the following fields:

- 1. Preamble

- 2. Start pattern (network address)

- 3. Length byte

- 4. Node address byte (optional)

- 5. Data bytes

- 6. Two-byte CRC checksum (optional)

#### Extended Variable Length Packet Format, 65 to 127 Bytes

The Preamble, Start Pattern and CRC bytes are added to the packet by the TRC103 during transmit and removed from the packet during receive.

Figure 15

In extended variable length packet mode, the length of the rest of the payload is given by the first byte written to the FIFO. The length byte itself is not included in this count. There are a number of ways to use the extended variable length packet capability. The most common way is outlined below:

1. Set **PKTCFG1C\_Pkt\_len[6..0]** to a value between 65 (0x41) and 127 (0x7F). This sets the maximum allowed payload in extended packet mode. Any received packet having a value in the length byte greater than this maximum is discarded.

2. Set PKTCFG1E\_Pkt\_mode[7] to 1 for variable length packet mode operation. Set the PKTCFG1E\_Preamb\_len[6..5] bits to 10 or 11 for a minimum of 3 to 4 preamble bytes. Set the PKTCFG1E\_CRC\_En[3] bit to 1 to enable CRC processing. Set the PKTCFG1E\_Pkt\_ADDRS\_cmp[2..1] bits as required. Clear the PKTCFG1E\_ CRC\_stat[0] bit by writing a 1 to it.

3. Set MCFG05\_FIFO\_depth[7..6] bits to 11 for a 64-byte FIFO length.

4. Set the **MCFG05\_FIFO\_thresh[5..0]** to approximately 31(0x1F). This sets the threshold to 32, near the mid point of the FIFO. Provided the host microcontroller is relatively fast (usual case), this setting can be used for monitoring the FIFO in both transmit and receive. If the host microcontroller is relatively slow, set the threshold to a value lower than 31 for receive, and higher than 31 for transmit.

5. Set the **IRQCFG0D\_RX\_IRQ1[5..4]** bits to 11. This maps FIFO\_Int\_Rx interrupt to IRQ1, which trips when the number of received bytes in the FIFO is equal to or greater than the value in MCFG05\_FIFO\_thresh. IRQ1 will then signal received bytes must be retrieved. If received bytes are not retrieved before the FIFO completely fills, data will be lost.

6. Set the **IRQCFG0E\_Start\_Full[4]** bit to 0. This causes a transmission to start when the number of transmit bytes in the FIFO is equal to or greater than the value in MCFG05\_FIFO\_thresh. Also, the FIFO\_Int\_Tx interrupt is mapped to IRQ0 in transmit mode, and is set when the number of bytes in the FIFO is equal to or less than the value in MCFG05\_FIFO\_thresh. IRQ0 will then signal more bytes can be added to the FIFO. If more message bytes are not added in time, the transmission will cease prematurely and data will be lost. Likewise, if more bytes are sent to the FIFO than it has room for, data will be lost.

7. When receiving an extended variable length packet, monitor IRQ1. When IRQ1 trips, clock out some of the received bytes from the FIFO (leave at least one byte in the FIFO). Repeat the partial packet retrieval each time IRQ1 triggers. The first byte received is the number of message bytes, and can be used to tell when the last message byte has been retrieved. When it is determined that the remaining message bytes will not overflow the FIFO, the **IRQCFG0D\_RX\_IRQ1[5..4]** bits can be set to 00, which maps CRC\_OK to IRQ1. After the CRC is checked, the final bytes can be read from the FIFO and the **IRQCFG0D\_RX\_IRQ1[5..4**] bits can be reset to 11 to track FIFO\_Int\_Rx when the next packet is received. Note that CRC mapping to IRQ1 is not required if the CRC state is read from the **PKTCFG1E\_CRC\_stat[0]** bit prior to reading the final FIFO bytes.

8. When transmitting an extended variable length packet, begin filling the FIFO until IRQ0 trips, indicating the FIFO is half full. Add up to 32 bytes to the FIFO (64 - (MCFG05\_FIFO\_thresh +1)) when IRQ0 resets. Repeat the partial packet loading each time IRQ0 resets until all bytes to be transmitted have been clocked in. The **IRQCFG0D\_TX\_IRQ1[3]** bit can then be set to 1, which allows the TX\_STOP event to be mapped to IRQ1. TX\_STOP signals the last bit to be transmitted has been transferred the modulator. Allow one bit period for this bit to be transmitted before switching out of transmit mode.

#### 3.9.4 Packet Payload Processing in Transmit and Receive

The TRC103 packet handler constructs transmit packets using the payload bytes in the FIFO. In receive, it processes the packets and extracts the payload bytes to the FIFO. Packet processing in transmit and receive are detailed below.

For transmit, the packet handler adds the following fields and processing to the payload in the FIFO:

- 1. One to four programmable preamble bytes

- 2. One to four start pattern bytes, programmable and usually set to at least 2 bytes

- 3. Optional CRC checksum calculated over the FIFO payload and appending to the end of the packet

- 4. Optional Manchester encoding or DC-balanced scrambling

The payload in the FIFO may contain one or both of the following optional fields:

- 1. A length byte if the variable packet length mode is selected

- 2. A node address byte

The way transmission is initiated depends on the configuration set by the user and the value of the **IRQCFG0E\_Start\_Full[4]** bit.

If the FIFO is filled while transmit mode is enabled, and if **IRQCFG0E\_Start\_Full[4]** is set to 1, the modulator waits until the first byte is written into the FIFO, then it starts sending the programmed preamble bytes followed by the start pattern and the user payload. If **IRQCFG0E\_Start\_Full[4]** is set to 0 in the same conditions, the modulator waits until the number of bytes written in the FIFO is equal to the number defined in the register **MCFG05\_ FIFO\_thresh[5..0]**. Note that the transmitter automatically sends preamble bytes in addition the number programmed while in transmit mode and waiting for the FIFO to receive the required number of bytes to start data transmission. Data to be transmitted can also be written into the FIFO during standby mode. In this case, the data is automatically transmitted when the transmit mode is enabled and the transmitter reaches its steady state.

If CRC is enabled, the CRC checksum is calculated over the payload bytes. This 16-bit checksum is sent after the bytes in the FIFO. If CRC is enabled, the TX\_STOP bit is set when the last CRC bit is transferred to the TX modulator. If CRC is not enabled, the TX\_STOP bit is set when the last bit from the FIFO is transferred to the TX modulator. Note that the transmitter must remain on one bit period after the TX\_STOP bit is set while the last bit is being transmitted. If the transmitter remains on following the transmission of the last bit after TX\_STOP is set, the transmitter will send preamble bytes. If Manchester encoding or scrambling is enabled, all data except the preamble and start pattern is encoded or scrambled before transmission. Note that the length byte in the FIFO determines the length of the packet to be sent and the **PKTCFG1C\_Pkt\_len[6..0]** parameter is not used in transmit.

In receive the packet handler retrieves the payload by performing the following steps:

- 1. Data and clock recovery synchronization to the preamble

- 2. Start pattern detection

- 3. Optional address byte check

- 4. Error detection through CRC

When receive mode is enabled, the demodulator detects the preamble followed by the start pattern. If fixed length packet format is enabled, then the number of bytes received as the payload is given by the **PKTCFG1C\_Pkt\_ len[6..0]** parameter.

In variable length and extended variable length packet modes, the first byte received after the start pattern is interpreted as the length of the balance of the payload. An internal length counter is initialized to this length. The **PKTCFG1C\_Pkt\_len[6..0]** register must be set to a value which is equal to or greater than the maximum

expected length byte value of the received packet. If the length byte value of a received packet is greater than the value in the **PKTCFG1C\_Pkt\_len[6..0]** register, the packet is discarded. Otherwise the packet payload begins loading into the FIFO.

If address match is enabled, the second byte received in a variable length mode or the first byte in the fixed length mode is interpreted as the node address. If this address matches the byte in **PKTCFG1D\_Node\_Addrs[7..0]**, reception of the packet continues, otherwise it is stopped. A CRC check is performed if **PKTCFG1E\_CRC\_En[3]** is set to 1. If the CRC check is successful, a 1 is loaded in the **PKTCFG1E\_CRC\_stat[0]** bit, and CRC\_OK and Dat\_Rdy interrupts are simultaneously generated on IRQ1 and IRQ0 respectively. This signals that the pay-load or balance of the payload can be read from the FIFO. In receive mode, address match, Dat\_Rdy, and CRC\_OK interrupts and the CRC\_stat bit are reset when the last byte in the FIFO is read. Note the FIFO can be read in standby mode by setting **PGCFG1F\_RnW\_FIFO[6]** bit to 1. In standby, reading the last FIFO byte does not clear CRC\_OK and the CRC\_stat bit. They are reset once the TRC103 is put in receive mode again and a start pattern is detected.

If the CRC check fails, the FIFO is cleared and no interrupts are generated. This action can be overridden by setting **PGCFG1F\_CRCcIr\_auto[7**] to 1, which forces a Data\_Rdy interrupt and preserves the payload in the FIFO even if the CRC fails.

#### 3.9.5 Packet Filtering

Received packets can be filtered based on two criteria: length filtering and address filtering. In variable length or extended variable length packet formats, **PKTCFG1C\_Pkt\_len[6..0]** stores the maximum payload length permitted. If a received packet length byte is greater than this value, then the packet is discarded. Node address filtering is enabled by setting parameter **PKTCFG1E\_Addrs\_cmp[2..1]** to any value other than 00, i.e., 01, 10 or 11. These settings enable the following three options:

**PKTCFG1E\_Addrs\_cmp[2..1]** = 01: This configuration activates the node address filtering function on the packet handler and the received address byte is compared with the address in the **PKTCFG1D\_Node\_ Addrs[7..0]** register. If both address bytes are the same, the received packet is for the current destination and is stored in FIFO. Otherwise it is discarded. An interrupt can also be generated on IRQ0 if the address comparison is successful.

**PKTCFG1E\_Addrs\_cmp[2..1]** = 10: In this configuration the received address is compared to both the **PKTCFG1D\_Node\_Addrs[7..0]** register and constant 0x00. If the received node address byte matches either value, the packet is accepted. An interrupt can also be generated on IRQ0 if the address comparison is successful. The 0x00 address is useful for sending broadcast packets.

**PKTCFG1E\_Addrs\_cmp[2..1]** = 11: In this configuration the packet is accepted if the received node address matches the **PKTCFG1D\_Node\_Addrs[7..0]** register, 0x00 or 0xFF. An interrupt can also be generated on IRQ0 if the address comparison is successful. The 0x00 and 0xFF addresses are useful for sending two types of broadcast packets.

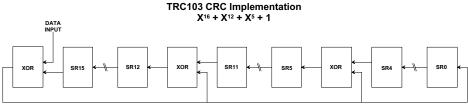

#### 3.9.6 Cyclic Redundancy Check

The CRC check is enabled by setting the **PKTCFG1E\_CRC\_En[3]** bit to 1. A 16-bit CRC checksum is calculated on the payload part of the packet and is appended to the end of the transmitted message. The CRC checksum is calculated on the received payload and compared to the transmitted CRC. The result of the comparison is stored in the **PKTCFG1E\_CRC\_stat[0]** bit and a CRC\_OK interrupt can also be generated on IRQ1. The CRC is based on the CCITT polynomial as shown in Figure 16. The CRC also detects errors due to leading and trailing zeros.

All 16 shift registers preset to 1 before each CRC calculation

Figure 16

#### 3.9.7 Manchester Encoding

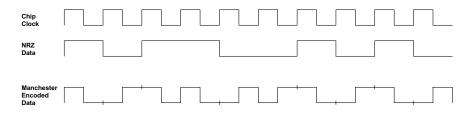

Manchester encoding is enabled by setting the **PKTCFG1C\_Man\_En[7]** bit to 1, and can only be used in Packet data mode. Figure 17 illustrates Manchester encoding. NRZ data is converted to Manchester by encoding 1 bits as 10 chip sequences, and 0 bits as 01 chip sequences. Manchester encoding guarantees DC-balance and frequent data transitions in the encoded data. Note the maximum Manchester chip rate corresponds to the maximum bit rate given in the specifications in Table 48.

#### TRC103 Manchester Data Encoding

In transmit, Manchester encoding is applied only to the payload and CRC parts of the packet. The receiver decodes the payload and CRC before performing other packet processing tasks.

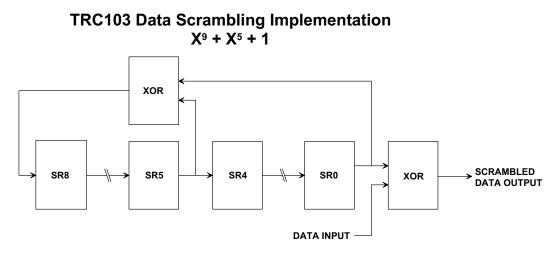

#### 3.9.8 DC-Balanced Scrambling

A payload may contain long sequences of 1 or 0 bits. These sequences would introduce DC biases in the transmitted signal, causing a non-uniform power distribution spectrum. These sequences would also degrade the performance of the demodulation and data and clock recovery functions in the receiver. System performance can be enhanced if the payload bits are randomized to reduce DC biases and increase the number of bit transitions.

As discussed above, DC-balanced data can be obtained by using Manchester encoding, which ensures that there are no more than two consecutive 1's or 0's in the transmitted data. However, this reduces the effective bit-rate of the system because it doubles the amount of data to be transmitted.

Another technique called scrambling (whitening) is widely used for randomizing data before radio transmission. The data is scrambled using a random sequence on the transmit side and then descrambled on the receive side using the same sequence.

The TRC103 packet handler provides a mechanism for scrambling the packet payload. A 9-bit LFSR is used to generate a random sequence. The payload and the 16-bit CRC checksum are XOR'd with this random sequence as shown in Figure 18. The data is descrambled on the receiver side by XORing with the same random sequence. The scrambling/descrambling process is enabled by setting the **PKTCFG1E\_Scrmb\_En[4]** bit to 1.

All 9 shift registers preset to 1 before each scrambling (DC balancing) calculation

# 3.10 SPI Configuration Interface

The TRC103 contains two SPI-compatible interfaces, one to read and write the configuration registers, the other to read and write FIFO data. Both interfaces are configured in slave mode and share the same pins: SDO (SPI Slave Data Out), SDI (SPI Slave Data In), and SCK (Serial Clock). Two pins are provided to select the SPI connection. The nSS\_CONFIG pin allows access to the configuration registers and the nSS\_DATA pin allows access to the FIFO. Figure 19 shows a typical connection between a host microcontroller and the SPI interface.

#### **TRC103 - Microcontroller Signal Connections**

A byte transmission can be seen as a rotate operation between the value stored in an 8-bit shift register in the master device (host microcontroller) and the value stored in an 8-bit shift register in the transceiver. The SCK line is used to synchronize both SPI bit transfers. Data is transferred full-duplex from master to slave through the SDI line and from slave to master through the SDO line. The most significant bit is always sent first. In both directions the rising SCK edge is used to sample a bit, and the falling SCK edge shifts the bits through the shift register.

The active low nSS\_CONFIG or nSS\_DATA signals are asserted by the master device and should remain low during a byte transmission. The transmission is synchronized by these nSS\_CONFIG or nSS\_DATA signals. While the nSS\_CONFIG or nSS\_DATA is set to 1, the counters controlling transmission are reset. Reception starts with the first clock cycle after the falling edge of nSS\_CONFIG or nSS\_DATA. If either signal goes high during a byte transmission the counters are reset and the byte must be retransmitted.

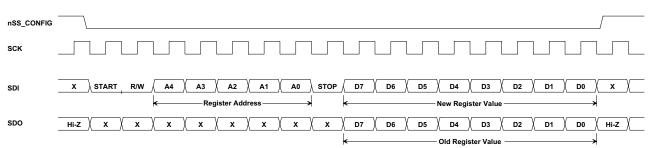

The configuration interface is selected if nSS\_CONFIG is low even if the TRC103 is in buffered mode and nSS\_DATA is low (nSS\_CONFIG has priority). To configure the transceiver two bytes are required. The first byte contains a 0 start bit, R/W information (1 = read, 0 = write), 5 bits for the address of the register and a 0 stop bit. The second byte contains the data to be sent in write mode or the new address to read from in read mode.

#### Single Byte Configuration Register Write

#### Figure 20

Figure 20 shows the timing diagram for a single byte write sequence to the TRC103 through the SPI configuration interface. Note that nSS\_CONFIG must remain low during the transmission of the two bytes (address and data). If it goes high after the first byte, then the next byte will be considered as an address byte. When writing more than one register successively, nSS\_CONFIG does not need to have a high-to-low transition between two write sequences. The bytes are alternatively considered as an address byte followed by a data byte.

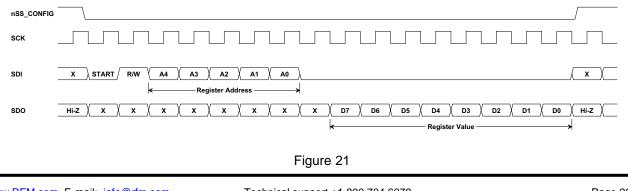

The read sequence through the SPI configuration interface is similar to the write sequence. The host microcontroller sends the address during the first SPI communication and then reads the data during a second SPI communication. Note that 0 bits can be input to the SDI during the second SPI communication for a single byte read. Figure 21 shows the timing diagram for a single byte read sequence from the TRC103 through the SPI.

#### Single Byte Configuration Register Read

www.RFM.com E-mail: info@rfm.com ©2009-2010 by RF Monolithics, Inc. Technical support +1.800.704.6079

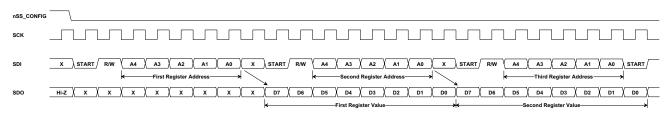

Multi-byte Configuration Register Read

Multiple configuration register reads are also possible by sending a series of register addresses into the SPI port, as shown in Figure 22.

# 3.11 SPI Data FIFO Interface

When the transceiver is used in Buffered or Packet data mode, data is written to and read from the FIFO through the SPI interface. Two interrupts, IRQ0 and IRQ1, are used to manage the transfer procedure.

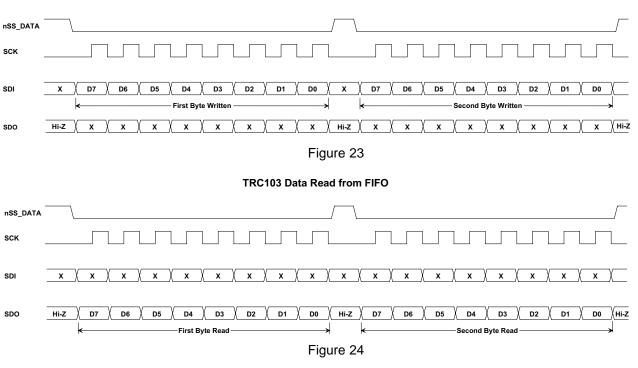

When the transceiver is operating in Buffered or Packet data mode, the FIFO interface is selected when nSS\_DATA is set to 0 and nSS\_CONFIG is set to 1. SPI operations with the FIFO are similar to operations with the configuration registers with two important exceptions. First, no addresses are used with the FIFO, only data bytes are exchanged. Second, nSS\_DATA *must be toggled high and back low* between data bytes when writing to the FIFO or reading from the FIFO. Toggling nSS\_DATA indexes the access pointer to each byte in the FIFO in lieu of using explicit addressing. Figure 23 shows the timing diagram for a multiple-byte write sequence to the TRC103 during transmit, and Figure 24 shows the timing for a multi-byte read sequence.

TRC103 Data Write to FIFO

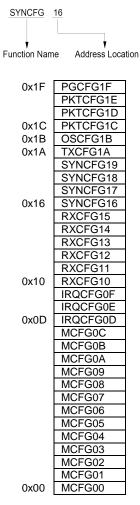

# 4.0 Configuration Register Memory Map

Register names are based on the function name and address location for easy reference:

Table 12

# 4.1 Main Configuration Registers (MCFG)

Power up default setting are shown in **bold**:

| Name         | Bits  | R/W | Description                                                                                 |

|--------------|-------|-----|---------------------------------------------------------------------------------------------|

|              |       |     | Transceiver chip mode:                                                                      |

|              |       |     | $000 \rightarrow \text{Sleep}$                                                              |

|              |       |     | $001 \rightarrow $ Stand-by                                                                 |

| Chip_Mode    | 7,6,5 | r/w | $010 \rightarrow Frequency synthesizer$                                                     |

|              |       |     | $011 \rightarrow \text{Receive}$                                                            |

|              |       |     | $100 \rightarrow \text{Transmit}$                                                           |

|              |       |     | 101, 100, 111 $\rightarrow$ not used                                                        |

|              |       |     | Frequency band:                                                                             |

|              |       |     | $00 \rightarrow 902-915 \text{ MHz}$                                                        |

| Band         | 4,3   | r/w | $01 \rightarrow 915$ -928 MHz                                                               |

|              |       |     | $10 \rightarrow 950\text{-}960~\text{MHz}$ (863-870 MHz with alternate VCO tank)            |

|              |       |     | $11 \rightarrow not used$                                                                   |

|              |       |     | PLL tune offset voltage (VCO trim):                                                         |

|              |       |     | $00 \rightarrow 0 \text{ mV}$                                                               |

| Trim_Band    | 2,1   | r/w | $01 \rightarrow 60 \text{ mV}$                                                              |

|              |       |     | $10 \rightarrow 120 \text{ mV}$                                                             |

|              |       |     | $11 \rightarrow 180 \text{ mV}$                                                             |

|              |       |     | Selection between two RF frequencies as defined by SynthRx, SynthPx, and SynthSx registers: |

| RF_Frequency | 0     | r/w | $0 \rightarrow \text{frequency 1}$                                                          |

|              |       |     | $1 \rightarrow \text{frequency } 2$                                                         |

#### 0x00 - MCFG00 [default 0x28]

Table 13

#### 0x01 - MCFG01 [default 0x88]

| Name          | Bits | R/W | Description                                                         |

|---------------|------|-----|---------------------------------------------------------------------|

|               |      |     | TX/RX modulation:                                                   |

|               |      |     | $00 \rightarrow \text{Reset}$                                       |

| FSK_OOK       | 7,6  | r/w | 01→ OOK                                                             |

|               |      |     | $10 \rightarrow FSK$                                                |

|               |      |     | $11 \rightarrow \text{not used}$                                    |

|               |      |     | Enable data mode:                                                   |

| Mode          | 5    | r/w | $0 \rightarrow Continuous$                                          |

|               |      |     | $1 \rightarrow Buffered$                                            |

|               |      |     | RX OOK threshold mode:                                              |

|               |      |     | $00 \rightarrow$ Fixed Threshold                                    |

| RX_OOK        | 4,3  | r/w | $01 \rightarrow \text{Peak Mode}$                                   |

|               |      |     | $10 \rightarrow AVG Mode$                                           |

|               |      |     | $11 \rightarrow \text{not used}$                                    |

|               |      |     | Enable Packet mode:                                                 |

| Packet_Hdl_En | 2    | r/w | $0 \rightarrow \mathbf{Disabled}$ ; mode selected by Mode bit above |

|               |      |     | $1 \rightarrow Enabled$                                             |

|               |      |     | Gain (AGC) on IF chain in IF amplifier:                             |

|               |      |     | $00 \rightarrow maximum IF gain$                                    |

| IF_Gain       | 1,0  | r/w | $01 \rightarrow -4.5 \text{ dB}$ below maximum                      |

|               |      |     | $10 \rightarrow -9 \text{ dB}$ below maximum                        |

|               |      |     | $11 \rightarrow -13.5 \text{ dB}$ below maximum                     |

#### Table 14

#### 0x02 - MCFG02 [default 0x03]

| Name     | Bits | R/W | Description                                                                                                                                                                                                                                  |

|----------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Freq_Dev | 70   | r/w | Frequency deviation:<br>$F_{DEV} = F_{XTAL}/(32 \cdot (R+1))$ where R is the Freq_Dev register value, $F_{DEV}$ and $F_{XTAL}$ are in kHz,<br>$0 \le R \le 255$<br>Freq_Dev default = 3, $F_{DEV} = \pm 100$ kHz for $F_{XTAL} = 12,800$ kHz |

#### Table 15

#### 0x03 - MCFG03 [default 0x07]

| Name     | Bits | R/W | Description                                                                                                                                                                                                             |

|----------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -        | 7    |     | Not used                                                                                                                                                                                                                |

| Bit_Rate | 60   | r/w | BR = $F_{xTAL}/(64^{*}(D + 1))$ , where D is the Bit_Rate value and bit rate BR and $F_{xTAL}$ are in kHz<br>0 ≤ D ≤ 127 for FSK, 5 ≤ D ≤ 127 for OOK<br>Bit_Rate default = 7, BR = 25 kb/s for $F_{xTAL}$ = 12,800 kHz |

Table 16

#### 0x04 - MCFG04 [default 0x0C]