# **ST-NXP Wireless**

#### **IMPORTANT NOTICE**

Dear customer,

As from August 2<sup>nd</sup> 2008, the wireless operations of NXP have moved to a new company, ST-NXP Wireless.

As a result, the following changes are applicable to the attached document.

- Company name NXP B.V. is replaced with ST-NXP Wireless.

- **Copyright** the copyright notice at the bottom of each page "© NXP B.V. 200x. All rights reserved", shall now read: "© ST-NXP Wireless 200x All rights reserved".

- Web site <u>http://www.nxp.com</u> is replaced with <u>http://www.stnwireless.com</u>

- **Contact information** the list of sales offices previously obtained by sending an email to <u>salesaddresses@nxp.com</u>, is now found at <u>http://www.stnwireless.com</u> under Contacts.

If you have any questions related to the document, please contact our nearest sales office. Thank you for your cooperation and understanding.

ST-NXP Wireless

**Product data sheet**

#### 1. General description

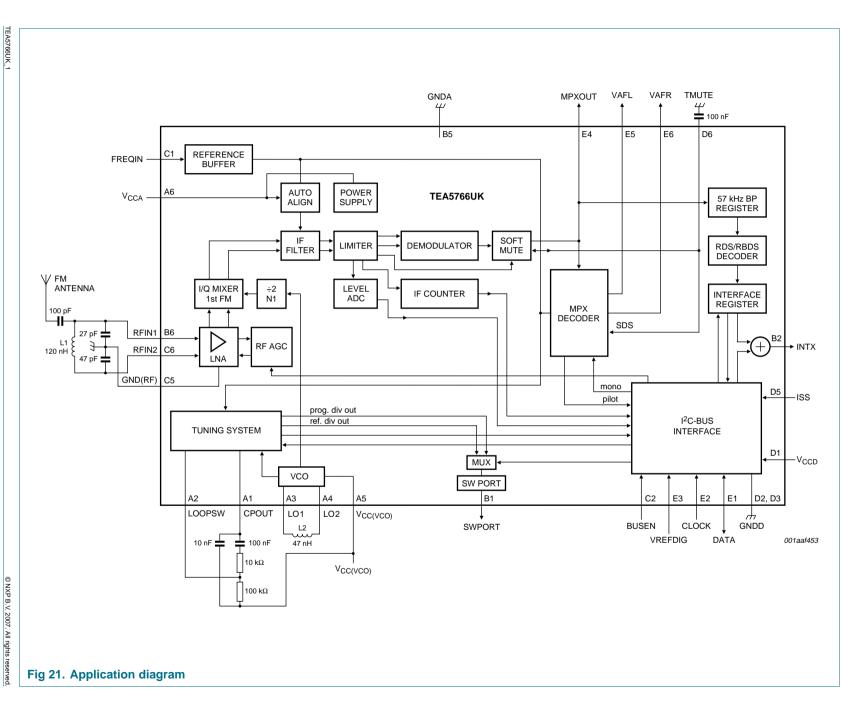

The TEA5766UK is a single chip electronically tuned FM stereo radio with Radio Data System (RDS) and Radio Broadcast Data System (RBDS) demodulator and RDS/RBDS decoder, for portable application with fully integrated Intermediate Frequency (IF) selectivity and FM demodulation.

The radio is completely adjustment free and only requires a minimum of small and low cost external components.

The radio can tune to the European, US and Japanese FM bands. It has a low power consumption at a low supply voltage.

The TEA5766UK application software is compatible to the TEA5764 software to enable easy design-in for customers.

#### 2. Features

- High sensitivity due to integrated low noise Radio Frequency (RF) input amplifier

- FM mixer for conversion of the US/Europe (87.5 MHz to 108 MHz) and Japanese FM band (76 MHz to 90 MHz) to IF

- Preset tuning to receive Japanese TV audio up to 108 MHz

- Autonomous search tuning, 100 kHz grid

- RF automatic gain control circuit

- LC tuner oscillator operating with integrated varicaps and one low-cost chip inductor

- Fully integrated FM IF selectivity

- Fully integrated FM demodulator

- 32768 Hz external reference frequency

- Phase Locked Loop (PLL) synthesizer tuning system

- IF counter, 7-bit output via control interface

- Level detector, 4-bit level information output via the control interface

- Soft mute, signal depending mute function, can be switched on or off via the control interface

- Mono/stereo blend, signal depending gradual change from mono to stereo, can be switched on or off via the control interface

- Standby mode

- Software programmable port

- Fully integrated RDS/RBDS demodulator in accordance with EN 62106

- RDS/RBDS decoder with memory for two RDS data blocks provides block synchronization and error correction; block data and status information are available via the I<sup>2</sup>C-bus

Interrupt flagInterrupt line

#### 3. Quick reference data

#### Table 1. Quick reference data

Under all conditions a reference clock of 32.768 kHz is present.

| Symbol                                  | Parameter              | Conditions                                                | Min          | Тур  | Max                                                                                    | Unit |

|-----------------------------------------|------------------------|-----------------------------------------------------------|--------------|------|----------------------------------------------------------------------------------------|------|

| General ele                             | ectrical parameters    |                                                           |              |      |                                                                                        |      |

| V <sub>CCA</sub>                        | analog supply voltage  |                                                           | 2.6          | 2.7  | 3.6                                                                                    | V    |

| V <sub>CC(VCO)</sub>                    | VCO supply voltage     |                                                           | 2.6          | 2.7  | 3.6                                                                                    | V    |

| I <sub>CCA</sub>                        | analog supply current  | operating                                                 | <u>[1]</u> _ | 13.5 | 17                                                                                     | mA   |

|                                         |                        | Standby mode                                              | <u>[1]</u> _ | -    | 5         μA           3.6         V           450         μA           1.5         mA |      |

| V <sub>CCD</sub>                        | digital supply voltage |                                                           | 2.6          | 2.7  | 3.6                                                                                    | V    |

| I <sub>CCD</sub> digital supply current | digital supply current | operating; RDS off                                        | -            | 350  | 450                                                                                    | μA   |

|                                         |                        | operating; RDS on                                         | -            | 0.75 | 1.5                                                                                    | mA   |

|                                         |                        | Standby mode                                              | -            | 5    | 10                                                                                     | μΑ   |

|                                         |                        | Sleep mode; only in I <sup>2</sup> C-bus;<br>BUSEN = HIGH | -            | 16   | 25                                                                                     | μA   |

| V <sub>VREFDIG</sub>                    | voltage on pin VREFDIG | $V_{VREFDIG} \leq V_{CCD}$                                | 1.65         | 1.8  | V <sub>CCD</sub>                                                                       | V    |

|                                         | current on pin VREFDIG |                                                           | 0            | 0.5  | 1                                                                                      | μA   |

|                                         |                        | Standby mode                                              | 0            | 0.5  | 1                                                                                      | μA   |

| General op                              | erating conditions     |                                                           |              |      |                                                                                        |      |

| f <sub>i(FM)</sub>                      | FM input frequency     |                                                           | 76           | -    | 108                                                                                    | MHz  |

| T <sub>amb</sub>                        | ambient temperature    | device meets all specifications                           | -20          | -    | +85                                                                                    | °C   |

| anio                                    |                        | TEA5766UK functional, specification not guaranteed        | -30          | -    | +85                                                                                    | °C   |

[1] Includes both analog supply current on pin  $V_{CCA}$  and VCO supply current on pin  $V_{CC(VCO)}$ .

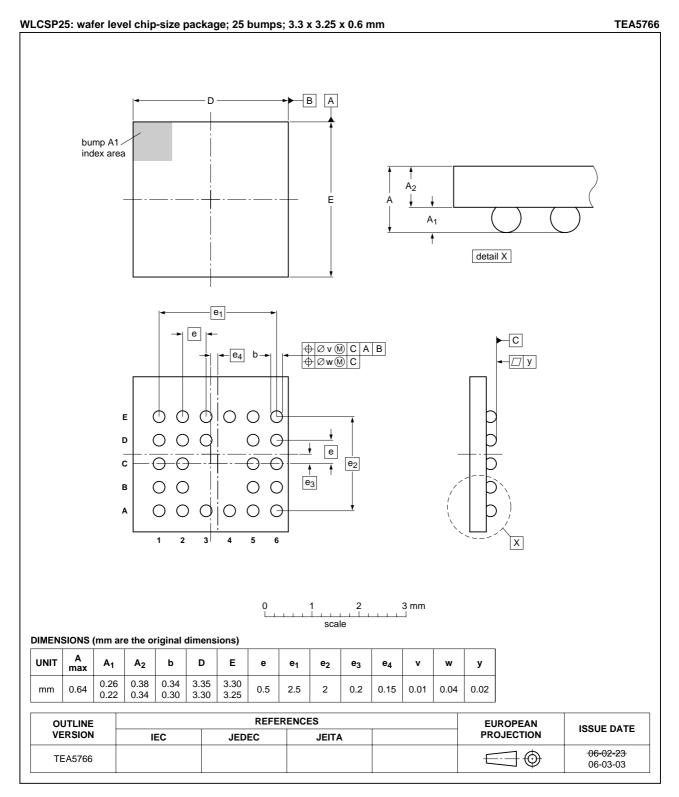

#### 4. Ordering information

#### Table 2.Ordering information

| Type number | Package |                                                                          |         |

|-------------|---------|--------------------------------------------------------------------------|---------|

|             | Name    | Description                                                              | Version |

| TEA5766UK   | WLCSP25 | wafer level chip-size package; 25 bumps; $3.3 \times 3.25 \times 0.6$ mm | TEA5766 |

NXP Semiconductors

Stereo FM radio + RDS

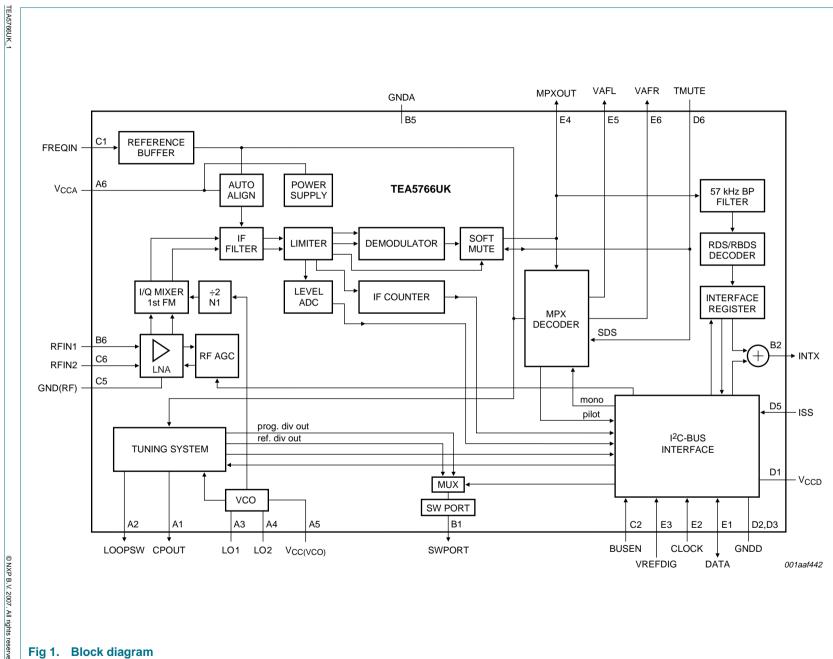

# 5. Block diagram

Product data sheet

Rev. 01 — 22 March 2007

3 of 59

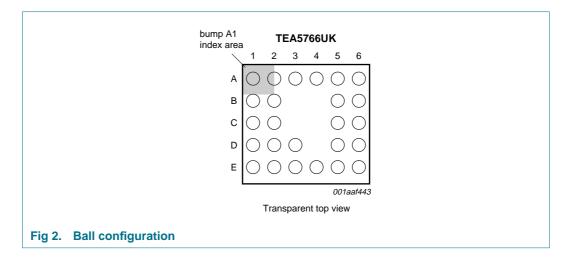

#### 6. Pinning information

#### 6.1 Pinning

#### 6.2 Pin description

#### Table 3.Pin description

| Table 5.             | Findescription |                                                                |

|----------------------|----------------|----------------------------------------------------------------|

| Symbol               | Pin            | Description                                                    |

| CPOUT                | A1             | charge pump output of synthesizer PLL                          |

| LOOPSW               | A2             | switch output of synthesizer PLL loop filter                   |

| LO1                  | A3             | local oscillator coil connection                               |

| LO2                  | A4             | local oscillator coil connection                               |

| V <sub>CC(VCO)</sub> | A5             | Voltage Controlled Oscillator (VCO) supply voltage             |

| V <sub>CCA</sub>     | A6             | analog supply voltage                                          |

| SWPORT               | B1             | software programmable port output                              |

| INTX                 | B2             | interrupt output                                               |

| GNDA                 | B5             | analog ground                                                  |

| RFIN1                | B6             | RF input 1                                                     |

| FREQIN               | C1             | input for 32.768 kHz reference frequency                       |

| BUSEN                | C2             | <ul> <li>I<sup>2</sup>C-bus enable input</li> </ul>            |

|                      |                | <ul> <li>SPI-bus chip select input</li> </ul>                  |

| GND(RF)              | C5             | RF ground                                                      |

| RFIN2                | C6             | RF input 2                                                     |

| V <sub>CCD</sub>     | D1             | digital supply voltage                                         |

| GNDD                 | D2             | digital ground                                                 |

| GNDD                 | D3             | digital ground                                                 |

| ISS                  | D5             | I <sup>2</sup> C-bus or SPI-bus selection input <sup>[1]</sup> |

| TMUTE                | D6             | time constant capacitor connection for soft mute               |

| DATA                 | E1             | input/output and control interface data line                   |

| CLOCK                | E2             | control interface clock line input                             |

| VREFDIG              | E3             | digital reference voltage for control interface                |

Stereo FM radio + RDS

| SymbolPinDescriptionMPXOUTE4multiplex signal (MPX) outputVAFLE5left audio outputVAFRE6right audio output | Table 3. | Pin description | continued                     |

|----------------------------------------------------------------------------------------------------------|----------|-----------------|-------------------------------|

| VAFL E5 left audio output                                                                                | Symbol   | Pin             | Description                   |

|                                                                                                          | MPXOUT   | E4              | multiplex signal (MPX) output |

| VAFR E6 right audio output                                                                               | VAFL     | E5              | left audio output             |

|                                                                                                          | VAFR     | E6              | right audio output            |

[1] The ISS pin the bus type can be selected, see <u>Section 10.1</u>.

#### 7. Functional description

#### 7.1 Low noise RF amplifier

The Low Noise Amplifier (LNA) input impedance together with the LC RF input circuit defines an FM band filter. The gain of the LNA is controlled by the RF Automatic Gain Control (AGC) circuit to prevent overdrive of the subsequent circuits.

#### 7.2 FM mixer

The FM quadrature mixer converts the received RF (76 MHz to 108 MHz) to the IF of 225 kHz. Downconversion is achieved by multiplication of the RF with the Local Oscillator (LO) frequency. Image frequency suppression is achieved by using quadrature signal processing.

#### 7.3 VCO

The LC tuned VCO provides the local oscillator signal for the downconversion of the RF signal to IF. The VCO is tuned to the double frequency required for the downconversion. The LO is divided by two to provide the quadrature oscillator signals for the downconversion process. The VCO frequency range is from 150 MHz to 217 MHz. Integrated varactors are used for the VCO tuning. The only external component used for the VCO is a coil.

#### 7.4 Reference frequency

An external 32.768 kHz reference frequency is used as system clock. The reference clock specifications are given in <u>Section 13.2</u>.

The reference frequency is used for:

- Synthesizer PLL reference frequency

- Timing for the IF counter

- Adjustment of the 38 kHz VCO for the stereo decoder

- Auto alignment of the selectivity as well as the demodulator filters

- Auto alignment of the 57 kHz RDS filter

#### 7.5 Tuning system

The PLL synthesizer tuning system is suitable to operate with a 32.768 kHz reference frequency. A 14-bit word is used to tune the radio, see <u>Table 15</u>. Calculation of this 14-bit word shall be done as follows:

Formula for high-side injection:

$$N_{DEC} = \frac{4 \times (f_{RF} + f_{IF})}{f_{ref}} \tag{1}$$

Formula for low-side injection:

$$N_{DEC} = \frac{4 \times (f_{RF} - f_{IF})}{f_{ref}}$$

(2)

where:

N<sub>DEC</sub> = decimal value of PLL word

$f_{RF}$  = wanted tuning frequency (Hz)

f<sub>IF</sub> = intermediate frequency of 225 kHz

f<sub>ref</sub> = reference frequency of 32.768 kHz

Example for receiving a channel at 100.1 MHz:

$$N_{DEC} = \frac{4 \times (100.1 \times 10^6 + 225 \times 10^3)}{32768} = 12246.704$$

(3)

Value 12246.704, is rounded down to the lowest integer value, being 12246, the PLL word becomes 2FD6h.

The result found using Equation 1 or Equation 2 must always be rounded to the lowest integer value (truncation). Via the control interface this value can be written to register FRQSET and the TEA5766UK will then start an autonomous search beginning at this frequency or go to a preset channel at this frequency. When the application is built according to the application diagram of Figure 21 and with the preferred components, the tuning system will settle to the new frequency within 40 ms.

The PLL is triggered by writing one of the four bytes of the FRQSET and TNCTRL and registers.

The Lock Detect (LD) bit in register TUNCHK will be set after PLL lock detection (see Table 18).

#### 7.6 Band limits

The TEA5766UK can be switched to the Japanese FM band or the US/Europe FM band. Bit BLIM in register TNCTRL (see <u>Table 16</u>) set to logic 0 enables the US/European band (87.5 MHz to 108 MHz) and BLIM set to logic 1 enables the Japanese band (76 MHz to 90 MHz).

#### 7.7 **RF AGC**

The RF AGC (or wideband AGC) prevents overloading and limits the amount of intermodulation products created by strong adjacent channels. Default the RF AGC is on and it can be turned off via the control interface.

The TEA5766UK also has an in-band AGC to prevent overloading by the wanted channel itself. The in-band AGC is always on.

#### 7.8 IF filter

Fully integrated IF filter with a center frequency of 225 kHz.

#### 7.9 FM demodulator

Fully integrated FM quadrature demodulator.

#### 7.10 IF counter

#### 7.10.1 IF counter correct channel checking

The received RF signal is converted down to a 225 kHz Intermediate Frequency (IF). The IF is measured by means of a frequency counter. A correct IF frequency measurement result indicates that the radio is tuned to a valid channel and not to an image or a channel with high interference. The 7-bit IF counter output can be read via the control interface. The IF counter is continuously active and can be read at any time via the bus. It also activates a flag when the IF count result is outside the IF count valid result window; see also Section 8.2.4.

#### 7.10.2 IF counter count time

Before a tuning cycle is initiated the IF count period can be set to 2 ms or to 15.6 ms with bit IFCTC in register TNCTRL (see <u>Table 16</u>). When the IF count period is set to 2 ms, initiating the tuning algorithm with a preset (SM = 0) will always give an RDS update as shown in <u>Section 7.21</u>. In case the IF count time is set to 15.6 ms the tuning flowchart of <u>Section 7.20</u> is used. Once tuned, the IF count period is always 15.6 ms.

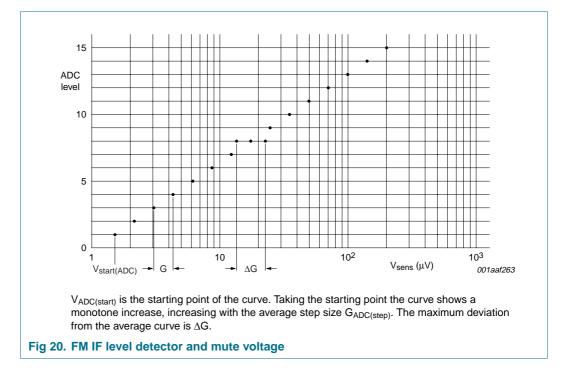

#### 7.11 Level voltage generator and level analog-to-digital converter

The level voltage reflects the received field strength at the antenna. The analog level voltage is digitized to 4 bits by the level Analog-to-Digital Converter (ADC). This level ADC is continuously active and the output can be read at any time via the control interface. The level ADC information is used during search as well as preset tuning to compare the received signal strength with a search stop level (see Section 8.2.5). A flag will be set to indicate that the level voltage is reduced below a programmable threshold value (see Section 8.2.5). The threshold value is relative to the search stop level. The hysteresis between the search stop level and the threshold level can be selected by bit LHSW (see Table 19, Table 20 and Section 8.2.5).

When the ADC level is set to its minimum value 3, the search algorithm will only stop at channels having an RF level higher than or equal to ADC level 3. After completing the search algorithm and being tuned to a station, due to the hysteresis the effective limit will be set to 0. This means that the continuous ADC level check will never set the LEVFLAG.

#### 7.12 Mute

#### 7.12.1 Soft mute

The low-pass filtered level voltage drives the softened attenuator. At low RF input levels, the audio output is faded and hence also the noise. The softened function can be turned on/off via the control interface, bit SMUTE in register TNCTRL (see Table 16).

#### 7.12.2 Hard mute

With the MU bit of the TNCTRL register byte 2 (see <u>Table 16</u>), the audio outputs VAFL and VAFR can be hard-muted; this means they are put in high-impedance state. The same can be done by setting the bits Left Hard Mute (LHM) or Right Hard Mute (RHM) in register TESTREG (see <u>Table 19</u>), which mute only one output at a time (or both when both set). When one output is muted the stereo decoder switches to mono. When he TEA5766UK is in Standby mode the audio outputs are in high-impedance state (see <u>Table 4</u>).

#### 7.12.3 Audio Frequency Mute (AFM)

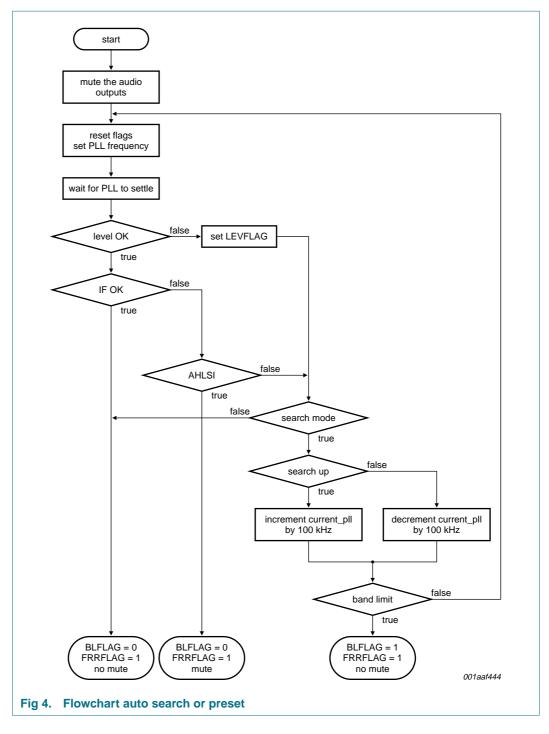

With the AFM bit of the TNCTRL register byte 1, the audio signal can be muted. The audio pins maintain their functional impedance and DC-biasing level while the audio signal is muted. The audio frequency mute is automatically activated during preset as well as search tuning modes as shown in the flowchart of Figure 4. The audio frequency mute can be disabled in software test mode when bit TM = 1 and bit AFMDIS = 1.

#### 7.12.4 Specification of mute modes

#### Table 4. Specification of mute modes

|         | opechication o       | cation of mate modes |                    |                   |                    |  |  |

|---------|----------------------|----------------------|--------------------|-------------------|--------------------|--|--|

| Туре    | Description          | VAFL                 |                    | VAFR              | VAFR               |  |  |

|         |                      | Impedance Mode       |                    | Impedance         | Mode               |  |  |

| AFM     | audio frequency mute | 350 Ω                | muted              | 350 Ω             | muted              |  |  |

| RHM     | right hard mute      | 350 Ω                | mono audio         | > 500 kΩ          | muted              |  |  |

| LHM     | left hard mute       | > 500 kΩ             | muted              | 350 Ω             | mono audio         |  |  |

| MU      | hard mute            | > 500 kΩ             | muted              | > 500 kΩ          | muted              |  |  |

| Standby | standby              | > 1 MΩ               | -                  | > 1 MΩ            | -                  |  |  |

| SMUTE   | soft mute            | RF sensitive au      | udio level; has no | influence on mute | e pin or impedance |  |  |

|         |                      |                      |                    |                   |                    |  |  |

#### 7.13 MPX decoder

The stereo decoder PLL is adjustment free. The stereo decoder can be switched to mono via the control interface.

#### 7.14 Signal depending mono/stereo blend (stereo noise cancellation)

With decreasing RF input level the MPX decoder blends from stereo to mono to limit the output noise. The continuous mono-to-stereo blend can also be programmed via the control interface to an RF level depending switched mono to stereo transition. Stereo noise cancellation can be switched on or off via the control interface using bit SNC in register TNCTRL (see <u>Table 16</u>). When stereo noise cancellation is switched off, the radio switches from mono to stereo instead of blending. The RF input voltage where blending starts can be switched with bit SNCLEV in register TESTREG (see <u>Table 19</u>).

#### 7.15 Software programmable port

One software programmable port SWPORT (CMOS output) is available and can be controlled via the control interface. With bit SWPM = 1 the software port (pin SWPORT) functions as the output for the FRRFLAG and with bit SWPM = 0 the software port output follows bit SWP. Bits SWP and SWPM are in register TNCTRL (see Table 16). In software

test mode the software port outputs signals according to <u>Table 21</u>. Software test mode is selected by setting bit TM of register TESTREG (see <u>Table 19</u>). The software port is not disabled by the PUPD bits (see <u>Section 7.16</u>).

#### 7.16 Standby mode

With the PUPD[1:0] (power-up/power-down) bits the radio can be put in Standby mode. Standby mode is defined as where the TEA5766UK has all supply voltages available but the circuits are powered down via software (PUPD) or after power-on reset. The RDS part can be turned off separately, using one of the PUPD bits. After a power-on reset or when the TEA5766UK is in Standby mode, the TEA5766UK is still accessible via the control interface, but takes only a limited amount of power from the supply. The software programmable port maintains active to allow peripheral devices to be controlled. The audio outputs are hard-muted.

In I<sup>2</sup>C-bus mode when pin BUSEN = HIGH and the circuits are powered down via software (PUPD) the TEA5766UK is in Sleep mode. In this Sleep mode the TEA5766UK is accessible via the bus, but the radio part is not active. The  $I_{VREFDIG}$  current is higher than in Standby mode.

When the supply voltages  $V_{CCA}$  and  $V_{CCD}$  are made 0 V and pin VREFDIG = HIGH, all I/Os, the audio outputs and the reference clock input are in high-impedance state. The power supplies can be switched on in any order.

#### 7.17 Power-on reset

After start-up of V<sub>CCA</sub> and V<sub>CCD</sub>, a power-on reset circuit will generate a reset pulse and the registers will be set to their default values as shown in <u>Table 12</u>. The power-on reset is effectively generated by V<sub>CCD</sub>. Power-on reset: the audio output pins are in high-impedance state (hard mute) and all other bits are set default according to the tables in <u>Section 11</u>. To initialize the TEA5766UK all bytes have to be transferred.

#### 7.18 RDS/RBDS demodulator

Fully integrated RDS/RBDS demodulator, uses the reference frequency (32678 Hz) of the PLL synthesizer tuning system. The RDS demodulator recovers and regenerates the continuously transmitted RDS or RBDS data stream of the multiplex signal (MPXRDS) and provides the signals clock (RDCL), data (RDDA) for further processing by the integrated RDS decoder.

TEA5766UK 1

#### 7.19 RDS/RBDS decoder

The RDS decoder provides block synchronization, error correction and flywheel function for reliable extraction of RDS or RBDS block data. Different modes of operation can be selected to fit different application requirements. Availability of new data is signalled by bit DAVFLG and output pin INTX, which generates an interrupt. Up to two blocks of data and status information are available via the I<sup>2</sup>C-bus in a single transmission.

The behavior of the DAVFLG is described in Section 9.

#### 7.20 Auto search and preset mode

In search mode TEA5766UK can search channels automatically.

When the INTX signal is used as an interrupt to the host processor to indicate a search stop, the INTMSK register must be reset and only bit FRRMSK must be set. In this way the host processor will only be interrupted when the search/preset algorithm is ready. Search mode is initiated setting the SM bit to logic 1 in the FRQSET register. When bit SUD is logic 0 then it searches down and when SUD is logic 1 it searches up. The tuner starts searching at the frequency where it is or at a new start frequency programmed to the tuner. With the Search Stop Level (SSL[1:0]) bits the minimum field strength of channels to be found can be set. The tuner will stop on a channel with a field strength equal to or higher than this reference level and then will check the IF frequency. When both are valid the search mode stops. If the level check or the IF count fails, it continues the search. When no channels are found the TEA5766UK stops searching when it has reached the band-limit and bit BLFLAG goes to logic 1. A search always stops with bit FRRFLAG being set and a hardware interrupt. Figure 4 shows this procedure.

After this interrupt the TEA5766UK will keep its status and will not update the INTREG, FRQCHK and TUNCHK tuner registers for a period of 15.6 ms. The state of the TEA5766UK can be checked by reading tuning registers: INTREG, FRQCHK and TUNCHK. Table 5 shows the possible states after an auto search or a preset.

A preset is done by setting bit SM to logic 0 and writing a frequency to byte FRQSETMSB. The tuner jumps to the selected frequency and sets bit FRRFLAG when it is ready. After this interrupt the TEA5766UK will keep not update the tuner registers for a period of 15.6 ms. The state of the TEA5766UK can be checked by reading registers: INTFLAG, FRQCHK and TNCTRL. Table 5 shows the possible states after an auto search or preset.

| Bit    |        |         | Comment                                                                                        |

|--------|--------|---------|------------------------------------------------------------------------------------------------|

| IFFLAG | BLFLAG | FRRFLAG |                                                                                                |

| 0      | 0      | 0       | this cannot occur if INTX has gone LOW and only IFMSK, FRRMSK and BLMSK were set               |

| 0      | 0      | 1       | channel found during search/preset FRRMSK set                                                  |

| 0      | 1      | 0       | not a valid state                                                                              |

| 0      | 1      | 1       | a valid channel found and the band limit has been reached during a search; BLMSK or FRRMSK set |

| 1      | 0      | 0       | not a valid state                                                                              |

#### Table 5.Tuner truth table

| Table 5. | Tuner truth | table <sup>[1]</sup> col | ntinued                                                                                                                                                                                                     |

|----------|-------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit      |             |                          | Comment                                                                                                                                                                                                     |

| IFFLAG   | BLFLAG      | FRRFLAG                  |                                                                                                                                                                                                             |

| 1        | 0           | 1                        | a preset or search has been done, but the wanted channel<br>has a valid RSSI level but fails the IF count; when AHLSI<br>was set HLSI must be toggled and a new PLL value must be<br>programmed; FRRMSK set |

| 1        | 1           | 0                        | not a valid state                                                                                                                                                                                           |

| 1        | 1           | 1                        | band limit is reached during search; no valid channel found;<br>BLMSK or FRRMSK set                                                                                                                         |

[1] This table is valid until 31.25 ms after the tuning cycle has completed. It shows the outcome of the flag register when a read is done after INTX has gone LOW with the condition that no other mask bits are set than shown in the table.

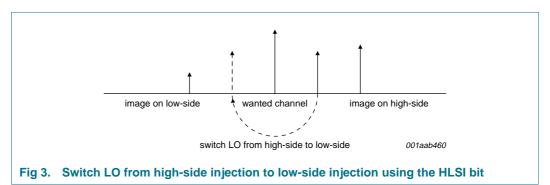

#### 7.20.1 Auto high-side and low-side injection stop switch

The channel quality can sometimes be improved in case of image frequency interference. This can be achieved if the Local Oscillator (LO) injection is positioned at the opposite side of the wanted channel (see Figure 3). Indication for image frequency interference can be derived from the IF frequency counter. To enable this feature the AHLSI bit must be set to logic 1.

The search/preset algorithm will stop and generate an interrupt event after the detection of a valid RSSI level in combination with a frequency outside the IF frequency window. The host processor can detect this state by reading the interrupt register. Swap of the LO injection is achieved by inversion of bit HLSI in combination with a new tuning word for the changed oscillator frequency (see Section 7.5).

#### 7.20.2 Muting during search or preset

During preset and search the tuner is always muted, which is done by the algorithm itself. When the AHLSI bit is set and the tuner has stopped during a preset or a search because of a wrong IF count, the tuner keeps muted and generates an interrupt event. In this way the host processor can switch the high or low setting quietly and waits for the new result.

All these mute actions are done by blocking the audio signal and the audio output will keep its DC level and stay in low-impedance state i.e. 50  $\Omega$  (see <u>Table 4</u>). A hard mute with the MU bit will cause a plop.

## **TEA5766UK**

Stereo FM radio + RDS

#### 7.21 RDS update or alternative frequency jump

A channel which transmits RDS data can have alternative channels which carry the same information. These alternative channel frequencies are in the RDS data, so the host processor can read the alternative frequencies and store them in a memory. More details on this subject can be found in section 3.5 of *RDS: The Radio Data System, Dietmar Kopitz and Bev Marks*.

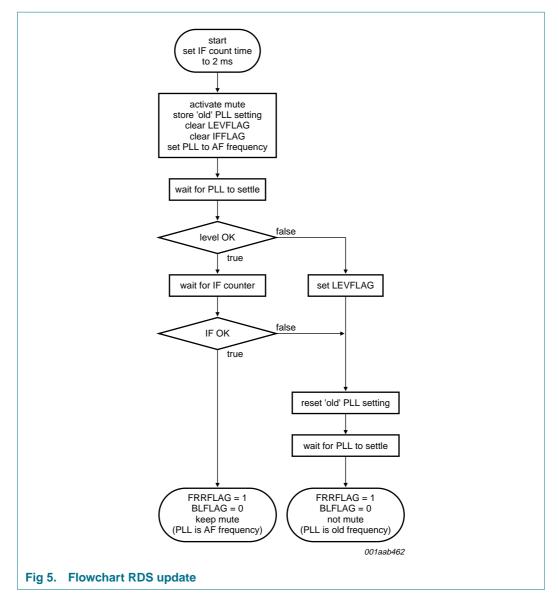

The tuner can do an RDS update. This is a preset, but with a 2 ms IF count time. The tuner will jump to the alternative frequency and check the level and the IF count using a 2 ms count time. When RSSI level check is above the specified level and the IF count result is within the limits then the tuner will stay at the alternative frequency and stay muted. The host processor can now decide what to do. If the alternative frequency is not valid it will jump back to the frequency it came from. The algorithm will finish with the FRRFLAG being set and generate an interrupt. After this interrupt the TEA5766UK will not measure the IF count for a period of 15.6 ms. 15.6 ms after completing an RDS jump a measurement of the IF count will start and hence the IF count result and the IFFLAG will be updated 31.25 ms after completing the algorithm. The level measurement will start 15.6 ms after the tuning algorithm, so bit LEVFLAG and the RSSI information will be updated 15.6 ms after the algorithm. The state of the TEA5766UK can be checked by reading registers: INTFLAG, FRQCHK, IFCHK and LEVCHK. Table 6 shows the possible states after an RDS update and Figure 5 shows the flowchart.

#### 7.21.1 Muting during RDS update

An RDS update (AF jump) is always muted. There are two states after the algorithm has stopped:

- 1. The tuner jumps to an alternative frequency which is not valid (according to the specified SSL limit and fixed IF counter limits) and jumps back, then it will get not muted automatically.

- 2. The tuner jumps to a valid alternative frequency and stays there. Now it remains in mute. The host processor can switch to not muted or it keeps the tuner muted and can check for the presence of RDS data. The recommended method to get not muted is to do a preset to the current frequency (at a preset an IF count time of 15.6 ms is used, which gives a more accurate IF count result than the result obtained by the AF jump, where 2 ms is used).

| Bit    |        |         | Comment                                                                                                     |

|--------|--------|---------|-------------------------------------------------------------------------------------------------------------|

| IFFLAG | BLFLAG | FRRFLAG |                                                                                                             |

| 0      | 0      | 0       | this cannot occur if INTX has gone LOW and only IFMSK, FRRMSK and BLMSK were set                            |

| 0      | 0      | 1       | alternative frequency jump successful; radio is tuned to the alternative frequency and keeps muted          |

| 0      | 1      | 0       | not a valid state                                                                                           |

| 0      | 1      | 1       | not a valid state                                                                                           |

| 1      | 0      | 0       | not a valid state                                                                                           |

| 1      | 0      | 1       | AF jump has been done, but the wanted channel fails the IF count, the PLL will be set back to the old value |

| 1      | 1      | 0       | not a valid state                                                                                           |

| 1      | 1      | 1       | this cannot occur if INTX has gone LOW and only IFMSK, FRRMSK and BLMSK were set                            |

#### Table 6. RDS update truth table<sup>[1]</sup>

[1] This table is valid until 31.25 ms after an RDS update has completed. It shows the outcome of the flag register when a read is done after INTX has gone LOW with the condition that no other mask bits are set than shown in the table.

# **TEA5766UK**

#### Stereo FM radio + RDS

#### 8. Interrupt handling

#### 8.1 Interrupt register

The first two bytes of the  $l^2$ C-bus register contain the interrupt masks and the interrupt flags. A flag is set when it is logic 1.

|          |            |               | , 10 543                 | register byte | on bit ai | location      |                         |

|----------|------------|---------------|--------------------------|---------------|-----------|---------------|-------------------------|

| 7        | 6          | 5             | 4                        | 3             | 2         | 1             | 0                       |

| DAVFLG   | TESTBIT    | LSYNCFL       | IFFLAG                   | LEVFLAG       | -         | FRRFLAG       | BLFLAG                  |

| Table 8. | INTMSK (IN | ITREQ byte 2) | - I <sup>2</sup> C-bus r | egister byte  | 1R/byte 0 | W bit allocat | ion                     |

| 7        | 6          | 5             | 4                        | 3             | 2         | 1             | 0                       |

| DAVMSK   | -          | LSYNCMSK      | IFMSK                    | LEVMSK        | -         | FRRMSK        | BLMSK                   |

|          |            |               |                          |               |           | © NXP B.V. 20 | 07. All rights reserved |

| Table 7. | INTFLAG (INTREQ byte 1) - I <sup>2</sup> C-bus register byte 0R bit allocation |  |

|----------|--------------------------------------------------------------------------------|--|

|----------|--------------------------------------------------------------------------------|--|

The interrupt flag register contains the flags set according to the behavior outlined in <u>Section 8.2</u>. When these flags are set they can also cause the INTX to go active (hardware interrupt line) depending on the status of the corresponding mask bit in <u>Table 8</u>. A logic 1 in the mask register enables the hardware interrupt for that flag.

Hence it is conceivable that, with all the mask bits cleared, the software could operate in a polling mode by a continuous read operation of the interrupt flag register to look for bits being set.

Interrupt mask bits are always cleared after reading the first two bytes of the interrupt register. This is to control multiple hardware interrupts (see Figure 6). Bit LSYNCMSK has a different function and is not cleared after reading the interrupt register bytes (see Section 8.2.3).

#### 8.1.1 Interrupt clearing

The interrupt flag and mask bits are always cleared after:

- They have been read via the control interface

- A power-on reset

#### 8.1.2 Timing

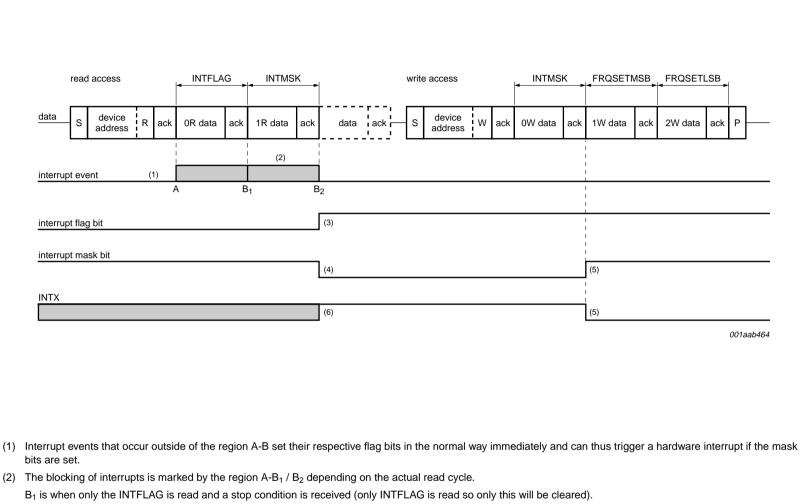

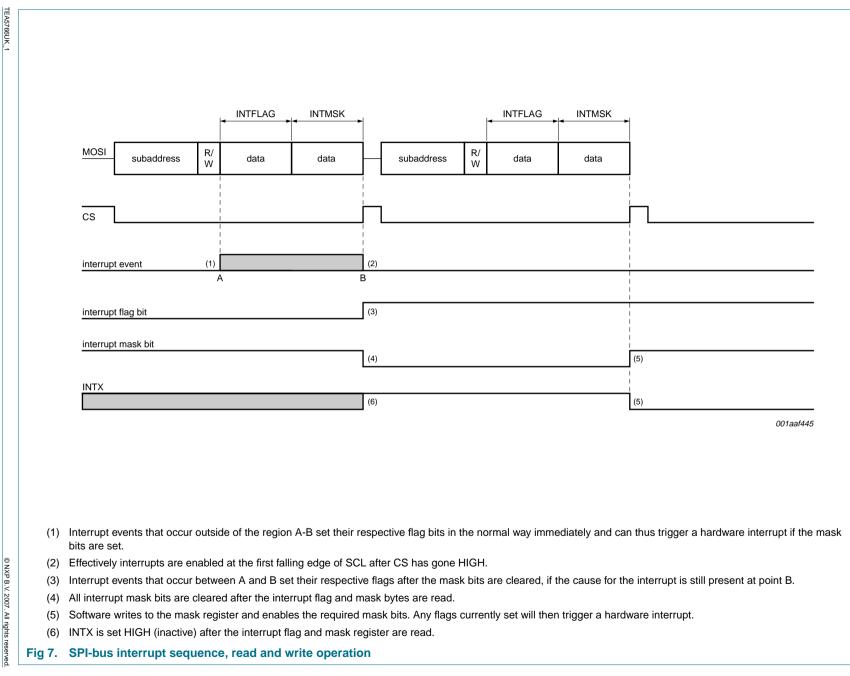

The timing sequence for the general operation interrupts is shown in Figure 6 and shows a read access of the interrupt bytes INTFLAG and INTMSK and a subsequent (though not necessarily immediate) write to the mask register. It also indicates two key timing points A and B.

If an interrupt event occurs while the register is being accessed (after point A) it must be held until after the mask register is cleared at the end of the read operation (point B).

Point A is situated after the R/W bit has been decoded and point B is where the acknowledge has been received from the master (host processor, etc.) after the first two bytes have been sent.

The LOW time for the INTX line  $(t_p)$  has a maximum value specified in <u>Section 13.4</u>. However it can be shorter if the read of the INTREG registers occurs within the  $t_p$ .

#### 8.1.3 Reset

A reset can be performed (at any time) by a simple read of the interrupt bytes (byte 0R and byte 1R), which automatically clears the interrupt flags and masks.

TEA5766UK 1

© NXP B.V. 2007. All rights

B<sub>2</sub> is when both registers are read and hence cleared and this is terminated by either an acknowledge or stop bit.

- (3) Interrupt events that occur between A and B set their respective flags after the mask bits are cleared. Which means that in this diagram an interrupt event occurred in period A-B, so after A-B the flag goes to logic 1.

- (4) All interrupt mask bits are cleared after the interrupt flag and mask bytes are read.

- (5) Software writes to the mask byte and enables the required mask bits. Any flags currently set will then trigger a hardware interrupt.

- (6) INTX is set HIGH (inactive) after the interrupt mask bytes are read.

#### Fig 6. I<sup>2</sup>C-bus interrupt sequence, read and write operation

Stereo FM radio + RDS

EA5766UK

Stereo FM radio + RDS

Product data sheet

#### 8.2 Interrupt flags and behavior

#### 8.2.1 Multiple interrupt events

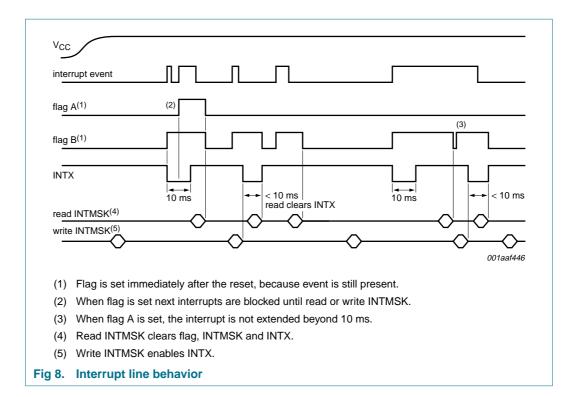

If the interrupt mask register bit is set then the setting of an interrupt flag for that bit causes a hardware interrupt (INTX goes LOW). If the event occurs again before the flag is cleared, then this does not trigger any further hardware interrupts until that specific flag is cleared. However two different events can occur in sequence and generate a sequence of hardware interrupts. Only when read, followed by a write of the INTMSK byte has been done, a second interrupt can be generated, as the first interrupt blocks the input of the INTX one-shot generator.

If subsequent interrupts occur within the INTX LOW period then these interrupts do not cause the INTX period to extend beyond its specified maximum period. See also <u>Section 8.3</u>, Figure 8.

#### 8.2.2 Data available: DAVFLG

When a new block of data is received, the DAVFLG is set according to the diagrams shown in <u>Section 9</u> where the different DAV modes are described. Once synchronized, this continues for all subsequent received blocks (dependent on DAV mode) and in the following situations:

- During synchronization search in any DAV mode, if two valid blocks in the correct sequence are received with BBC < BBL (synchronized)

- During synchronization search in DAV-B mode if a valid A(C')-block has been detected; this mode can be used for fast search tuning (detection and comparison of the Program Identification (PI) code contained in the A(C')-block)

- If the pre-processor is synchronized and in mode DAV-A or DAV-B a new block has been processed

- If the pre-processor is synchronized and in DAV-C mode two new blocks have been processed

- If the decoder is synchronized and for any DAV mode, with LSYNCMSK = 0, loss of synchronization is detected (flywheel loss of synchronization, resulting in a restart of synchronization search)

The DAVFLG is reset by a read of BL[7:0] of RDSR2 (byte 15R) or BP[7:0] of RDSR3 (byte 17R). An interrupt is given each time when a new block of data is decoded and when the DAVMSK is set; for details see <u>Section 9</u>.

#### 8.2.3 RDS synchronization: LSYNCFL

The SYNC bit, (see <u>Table 22</u>) shows the status of the RDS decoder. If it is set the decoder is synchronized.

The action of the TEA5766UK depends on the status of the LSYNCMSK bit in <u>Table 8</u>. If this is set then the loss of synchronization causes the LSYNCFL to go logic 1 and a hardware interrupt is generated. The RDS part of the TEA5766UK is set to idle and waits for the host processor to initiate a new synchronization search by setting the NWSY bit as described in <u>Table 26</u>.

TEA5766UK 1

If the LSYNCMSK bit is logic 0 and synchronization is lost the TEA5766UK automatically starts a new synchronization search. It will not generate a hardware interrupt. The host processor can wait until the RDS decoder is synchronized again; this will be indicated by the DAVFLG and the SYNC status bit (this requires the DAVMSK being set).

The LSYNCFL is reset by a read of the INTMSK byte 1R.

The LSYNCMSK is not reset by a read of the INTMSK byte; it must be set or reset by the host processor. Resetting it automatically would change the status of the TEA5766UK and cause an automatic synchronization search as described above.

How the synchronization is defined is explained in *EN 62106 Specification of the radio data system (RDS) for VHF/FM sound broadcasting range from 87.5 to 108 MHz, 1998* and in brief in <u>Section 9</u>.

#### 8.2.4 IF frequency: IFFLAG

During automatic frequency search, preset or AF update, the FM part of the TEA5766UK performs a check on the received IF frequency as a measure of the level of interference in the channel received. If an incorrect IF frequency is received then this indicates the presence of strong interferers or tuning to an image and the IFFLAG bit in the INTFLAG register is set. Also a preset to a channel with no signal will result in a wrong IF count value and hence setting of the IFFLAG.

When a search, preset or AF update is finished the FRRFLAG will be set to indicate this and generates an interrupt. The host processor can now read the outcome of the registers which will contain the IF count value and the IFFLAG status of the channel it is tuned to. In case of an AF update the IF count value of the alternative frequency will be in the registers, also when it jumps back because it will then not start a new IF count. Note: 15.6 ms after the tuning algorithm has been completed the IF counter will start a new count. So 31.25 ms after a failed AF update the IF count result will be equal again to that of the channel from where the jump was initiated.

15.6 ms after the FRRFLAG has been set the IF counter will start to run continuously on the tuned frequency and if the conditions for correct frequency are not met then this sets the IFFLAG bit in the interrupt register. When the IFMSK is set this will also cause an interrupt.

The IFFLAG bit is cleared by a read of byte 1R, or by starting the tuning algorithm.

#### 8.2.5 RSSI threshold: LEVFLAG

The level voltage reflects the field strength received by the antenna. The level voltage is analog to digital converted with 4 bits and output via the bus. This 4-bit level value can be compared to a threshold level set by the SSL bits in <u>Table 16</u> or the LHSW bit in <u>Table 19</u>. The level ADC (which converts the analog value to digital) can be triggered to convert in two ways.

During a tuning step, a search, a preset or an AF update the LEVFLAG is triggered by these algorithms and compares the level with the threshold set by the SSL bits. The LEVFLAG bit is set if the RSSI level drops below the threshold level set by the SSL bits in Table 16 The hardware interrupt is only generated if the corresponding mask bit is set.

After a search, a preset or an AF update the threshold for comparison is switched to the hysteresis level. The hysteresis level is set by the combination of SSL bits and the LHSW bit, which results in a hysteresis as shown in <u>Table 20</u>. Then the level ADC starts to run automatically and compares the level each 500  $\mu$ s with the hysteresis level. The LEVFLAG bit is set if the RSSI level drops below the threshold level set by the SSL bits in combination with the LHSW bit. The hardware interrupt is only generated if the corresponding mask bit is set. With the LHSW bit a small or a large hysteresis can be selected, which results in the levels of the left RSSI hysteresis threshold column for LHSW = 0 and in the right RSSI hysteresis threshold column (see Table 19).

**Remark:** when a search or preset is done with the ADC level set to 3 then when the algorithm has finished, the threshold level is set to 0. Hence the LEVFLAG will never be set.

The LEVFLAG bit is cleared by a read of the INTMSK byte 1R, or by starting the tuning algorithm.

#### 8.2.6 Frequency ready: FRRFLAG

The frequency ready flag bit is set when the automatic tuning has finished a search, a preset or an RDS AF update. The function of this bit is described in <u>Table 5</u> and <u>Table 6</u>. The FRRFLAG is cleared by a read of byte 1R.

#### 8.2.7 Band limit: BLFLAG

The band limit bit BLFLAG is set when the automatic tuning has detected the end of the tuning band or when the PLL cannot lock on a certain frequency. The description of this bit is in Table 5 and Table 6. This bit is cleared by a read of byte 1R.

#### 8.3 Interrupt line: pin INTX

The interrupt line driver is a MOS transistor with a nominal sink current of 900  $\mu$ A, it is pulled HIGH by an 18 k $\Omega$  resistor connected to pin VREFDIG. The interrupt line can be connected to another similar device with an interrupt output and an 18 k $\Omega$  pull-up resistor, providing a wired-OR function. This allows any of the drivers to pull the line LOW by sinking the current as specified in <u>Section 13.4</u>. So when a flag is set and not masked it generates an interrupt.

Product data sheet

TEA5766UK 1

Stereo FM radio + RDS

#### 9. RDS data processing

The RDS demodulator and decoder perform the following operations:

- Demodulation of the RDS/RBDS data stream from the MPX signal

- Symbol decoding

- Obtain block and group synchronization

- Error detection and correction

- · Store last and previous data block received with associated ID and error status

- Set the DAVFLG when new data is received

- · Set the SYNC status bit according to the current synchronization state

- · Set the LSYNCFL flag when synchronization is lost

The RDS decoder can be set in different modes, each meant to look for specific information. The modes DAV-A, DAV-B and DAV-C are described in the next paragraphs.

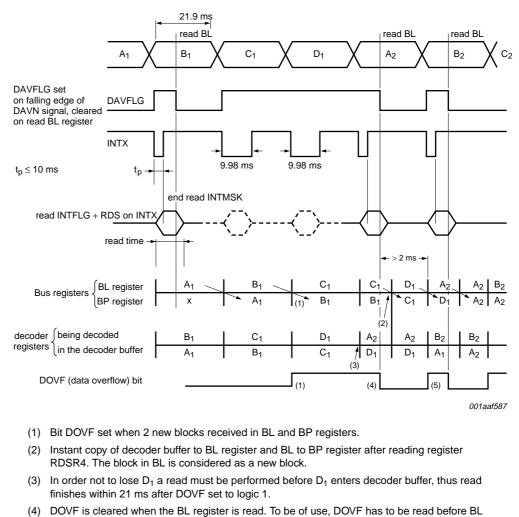

#### 9.1 DAV-A processing mode

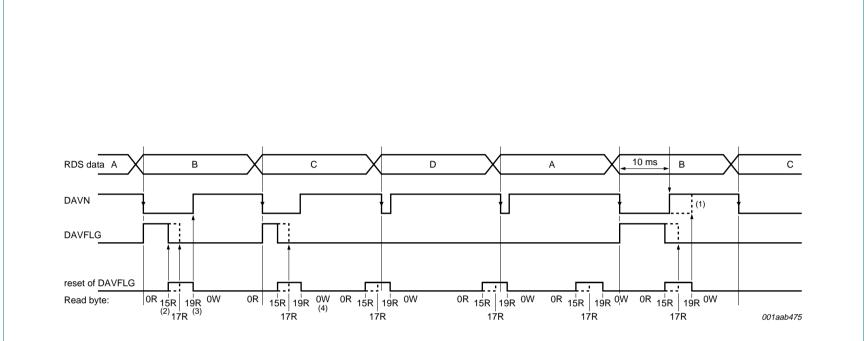

The DAV-A processing mode is the standard processing mode. In this mode each time when a data block has been decoded it is transferred to the bus registers. It generates interrupts on the INTX line after every new block of RDS data that has been processed and also the DAVFLG is set. This is shown in Figure 9. The DAVFLG is reset by a read of the bus registers.

If a data block is decoded and a new data block arrives, INTX will go LOW again, the DAVFLG will be set, the last block will be shifted to the previous block and the last decoded block will be put in the last block. This means that all RDS data is still available in the BL and BP registers.

When the bus registers are not read the DAVFLG will not be reset. If a data block is decoded and a new data block arrives, INTX will go LOW and the last block will be shifted to the previous block and the last decoded block will be put in the last block. This means that all RDS data is still available in the BL and BP registers, but must be read. This is indicated by the DOVF bit which is set.

If again the bus registers are not read, data will be lost except when this read is done within 20 ms after the INTX line has gone LOW, so 2 ms before the arrival of a new block. If this read is done at least 2 ms before the arrival of a new block, then BL and BP are read and the data in the decoder buffer is then instantaneously shifted to the BL register. All data is now read and the DOVF bit will be reset.

The diagram assumes that block synchronization has been achieved and that no other interrupt flags are being set.

# **TEA5766UK**

Stereo FM radio + RDS

- (4) DOVF is cleared when the BL register is read. To be of use, DOVF has to be read before BL and BP registers.

- (5) To prevent DOVF being set again, an extra read of BL must be performed before A2 has been decoded.

#### Fig 9. DAV-A timing diagram

TEA5766UK\_1 Product data sheet

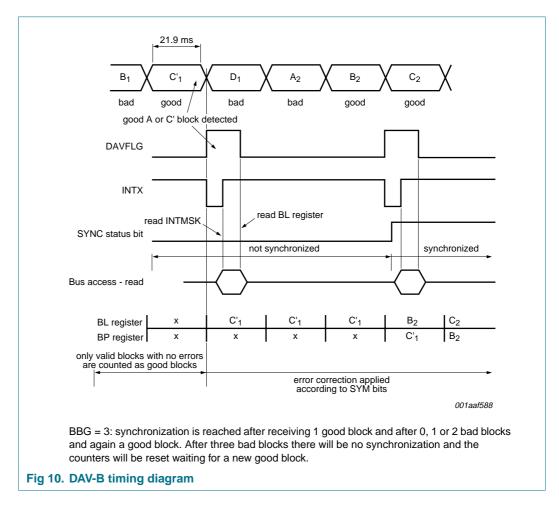

#### 9.2 DAV-B processing mode and fast PI search mode

This mode is used when, for example, the receiver has been re-tuned to a new station and a fast search of the PI code (always contained in the A/C'-block) is required. The diagram shown in <u>Figure 10</u>, assumes that the RDS decoder is unsynchronized initially and is performing a synchronization search.

During synchronization search the decoder does not set the DAVFLG until a valid A/C'-block is detected. If a valid B-block is immediately detected, the decoder is synchronized and the SYNC bit is set to logic 1. In fact, if any 2 good blocks in a valid order are found the RDS decoder will synchronize and give an interrupt.

If for some reason a valid B block was not received the next valid A/C'-block is decoded and the DAVFLG set. The BP and BL registers would record the A-block history.

After synchronization each decoded block will set the DAVFLG (assuming it was reset by a read action) and generate an interrupt.

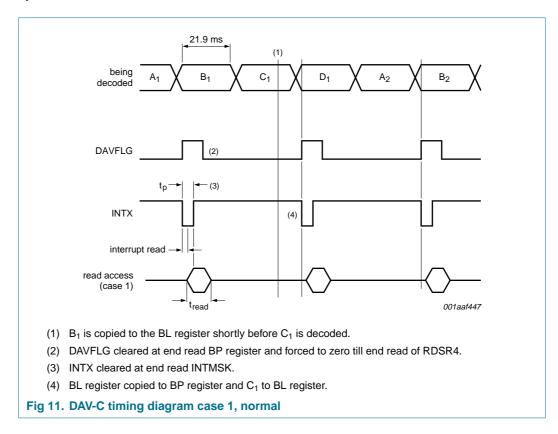

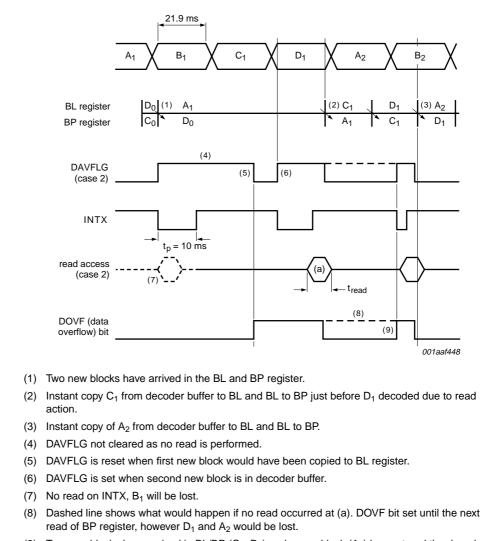

#### 9.3 DAV-C reduced processing mode

The DAV-C processing mode is very similar to DAV-A mode with the main exception that a data flag is only set after two new blocks are received. Hence the update rate is reduced by half.

# **TEA5766UK**

Stereo FM radio + RDS

(9) Two new blocks have arrived in BL/BP (C<sub>1</sub>, D<sub>1</sub>) and a new block (A<sub>2</sub>) has entered the decoder buffer. Hence DOVF is set again. To prevent this, an extra read must be performed after reading (a).

#### Fig 12. DAV-C timing diagram case 2, late read of BL and BP register

#### 9.4 Synchronization

#### 9.4.1 Conditions for synchronization

When the RDS decoder is turned on it must be synchronized to extract valid data from the MPX signal. To do so the decoder automatically initiates a search for synchronization. The conditions to meet synchronization and the status of this synchronization can be set and checked with the following bits:

- BBL[5:0] Bad Blocks Lose these bits can be set via the bus and have a value between 0 and 63.

- GBL[5:0] Good Blocks Lose these bits can be set via the bus and have a value between 0 and 63.

- BBG[4:0] Bad Blocks Gain these bits can be set via the bus and have a value between 0 and 32.

- GBC[5:0] Good Block Count these bits can be read via the bus and have a value between 0 and 63.

- BBC[5:0] Bad Block Count bits can be read via the bus and have a value between 0 and 63.

When the decoder is not synchronized it will initiate a synchronization search. This involves calculation of the syndrome (see *EN 62106 Specification of the radio data system (RDS) for VHF/FM sound broadcasting range from 87.5 to 108 MHz, 1998* for details) for each block of 26 received bits on a bit-by-bit basis. When a correct syndrome (and hence block ID) is received the decoder clocks the next 26 bits into the internal registers and performs a second syndrome check. Synchronization is found when a certain number of blocks have been decoded and two goods blocks have been found; this number of blocks is defined by the BBG bits. If the first block needed for synchronization has been found and the expected second block (after 26 bits) is an invalid block, then the decoder module internal bad\_blocks\_counter is incremented and the next expected block is calculated. Exception: if RBDS mode is selected and the first block is E, then the next expected block is always block A, until synchronization is found or the maximum bad\_blocks\_counter value is reached. If the decoder module internal bad\_blocks\_counter value of the BBG[4:0], then immediately a new synchronization search (bit-by-bit) is started to find a new first block.

The synchronization is monitored by use of two flywheel counters; GBC and BBC. These are 6-bit counters that can be preset by the GBL and BBL bits to values between 0 and 63. Each time a block is decoded and recognized as a bad block the BBC value is incremented by 1. When the BBC value is equal to the BBL value, synchronization is lost. The SYNC bit will become logic 0 and the LSYNCFL is set to signal the loss of synchronization. The TEA5766UK will now automatically initiate a new synchronization search.

Each time when a good block is decoded the GBC value is incremented. When the GBC value is equal to the GBL value both counters (BBC and GBC), are set to 0 and a new count starts. The GBC counter is only incremented when the decoder is synchronized.

#### 9.4.2 Modified Mobile Broadcast Service (MMBS) mode

There are three synchronization modes, RDS, RBDS and MMBS.

- RDS mode: the decoder can read A, B, C and D blocks and synchronize on A, B, C and D blocks.

- RBDS mode: the decoder can read A, B, C, D and E blocks and synchronize on A, B, C and D blocks.

- MMBS mode: the decoder can read A, B, C, D and E blocks and synchronize on A, B, C, D and E blocks.

MMBS mode can be selected using bit MMBS in register TESTREG (see Table 19).

#### 9.4.3 Data overflow

During synchronization after RDS data is read from the registers, new available blocks are shifted to the registers as described in Section 9.1 to Section 9.3. When the registers are not read in time, the decoder cannot shift any new available block to the registers and hence a data overflow will occur; this is indicated by the DOVF bit which is set to logic 1. The DOVF bit is reset by a read of the registers or if NWSY = 1 which results in the start of a new synchronization search.

#### 9.5 RDS flag behavior during read action

Each time when an RDS data block is decoded the DAVN signal will go LOW to signal the presence of a new data block. Also the DAVN signal triggers the interrupt output INTX. In principle the microprocessor must now start reading and must have read all RDS data, so byte 12R to byte 19R before the arrival of a new RDS data block. In the application there can be a too large delay between the arrival of a new block and reading this block. This can have various causes such as a microprocessor which has to start up from Sleep mode or when polling is used instead of interrupt based read actions. Figure 13 describes the behavior of the DAVFLG and the DAVN signal when polling, which effectively means that reading can occur at any moment.

**Remark:** DAVN sets the INTX one-shot generator when DAVMSK = 1. Unlike INTX, DAVN is not cleared by a read of the mask register.

TEA5766UK 1

Blocking DAVFLG: at end of reading byte 15R or byte 17R (DAV-A, B/C) DAVFLG is forced to zero. Only after reading byte 19R DAVFLG is released again.

If synchronous reading is performed using TEA5766UK generated interrupts, this problem does not occur.

To prevent undefined situations, byte 12R to byte 19R should always be read in one action immediately after each other.

Signal DAVN ≠ INTX.

Fig 13. RDS flag behavior

- (1) Normally reading byte 19R would reset signal DAVN, but now it is reset after 10 ms, the maximal LOW time of signal DAVN.

- (2) Read of byte 15R in DAV-A and DAV-B mode clears DAVFLG. In DAV-C mode two consecutive RDS data blocks are read and hence DAVFLG is reset after reading byte 17R instead of byte 15R (dotted line).

- (3) Read of byte 19R clears signal DAVN.

- (4) Write byte 0W (interrupt register).

Stereo FM radio + RDS

NXP

Semiconductors

#### 9.6 Error detection and reporting

The TEA5766UK must report information on the number of errors corrected in the last and previously decoded blocks. This is reported in the ELB[1:0] and EPB[1:0] fields as shown in Table 22.

During synchronization search the error correction is disabled for detection of the first block and is enabled for processing of the second block according to the mode set by the SYM[1:0] bits as described in Table 26.

#### 9.7 RDS data - reading from registers

To read RDS data the microprocessor must read byte 12R to byte 19R. All 8 bytes must be read to reset the status bytes byte 12R and byte 13R, i.e. effectively the status bits can be updated by the decoder after reading the last bit of byte 19R. The DOVL bit is cleared after reading the last bit of byte 19R and the status of the SYNC bit does not depend on reading the register; the SYNC bit tells if the decoder is synchronized or not. When starting a read action from byte 12R, the decoder blocks update from the RDS bytes until byte 19R has been read. RDS byte 12R to byte 19R must be read in one read action.

#### **10. Control interface**

#### 10.1 Selection between I<sup>2</sup>C-bus and SPI-bus

The TEA5766UK supports the  $I^2$ C-bus and the 3-wire SPI-bus. With pin ISS the bus types can be selected according to Table 9.

| Table 9. | Bus type selection |                      |

|----------|--------------------|----------------------|

| Pin ISS  |                    | Bus                  |

| LOW      |                    | l <sup>2</sup> C-bus |

| HIGH     |                    | SPI 3-wire           |

#### 10.2 I<sup>2</sup>C-bus

The full I<sup>2</sup>C-bus specification can be found in *The I<sup>2</sup>C-bus specification, version 2.1, January 2000.*

| S <sup>(1)</sup> | S <sup>(1)</sup> CHIP ADDRESS (READ) |       | CHIP ADDRESS (READ) |              | A <sup>(2)</sup>   | DATA BYT         | E 1 | А |

|------------------|--------------------------------------|-------|---------------------|--------------|--------------------|------------------|-----|---|

|                  |                                      |       |                     |              |                    | 001aaf456        |     |   |

| a. Write         | mode                                 |       |                     |              |                    |                  |     |   |

| 0(1)             |                                      | A (2) | 1                   |              |                    | D(4)             |     |   |

| S <sup>(1)</sup> | CHIP ADDRESS (WRITE)                 | A(2)  |                     | DATA BYTE(S) | NAK <sup>(3)</sup> | P <sup>(4)</sup> |     |   |

|                  |                                      |       |                     |              |                    | 001aaf457        |     |   |

| b. Read          | I mode                               |       |                     |              |                    |                  |     |   |

| (1) S = S        | TART condition.                      |       |                     |              |                    |                  |     |   |

| (2) A = a        | cknowledge (SDA LOW).                |       |                     |              |                    |                  |     |   |

| (3) NAK :        | = non acknowledge (SDA HIGH)         |       |                     |              |                    |                  |     |   |

| (4) $P = S^{2}$  | TOP condition.                       |       |                     |              |                    |                  |     |   |

| ()               |                                      |       |                     |              |                    |                  |     |   |

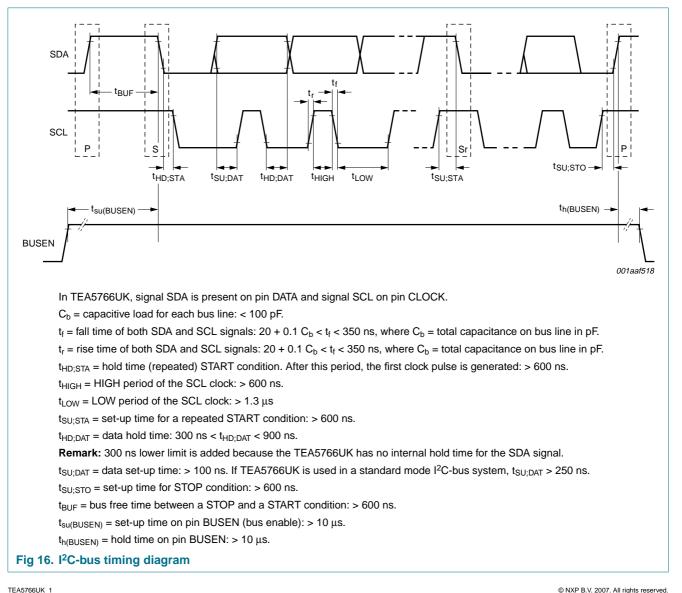

The I<sup>2</sup>C-bus specification is based on version 2.1, January 2000, expanded by the following definitions:

- The chip has two I<sup>2</sup>C-bus addresses:

- FM radio: 001 0000[R/W] starts at byte 0R or byte 0W

- RDS part: 001 0001[R/W] starts at byte 12R or byte 7W

- Structure of the I<sup>2</sup>C-bus:

- Slave transceiver, subaddresses not used.

- Maximum LOW-level input:  $V_{IL} = 0.3 \times V_{VREFDIG}$

- Minimum HIGH-level input:  $V_{IH} = 0.7 \times V_{VREFDIG}$

#### **10.2.1** Data transfer to the TEA5766UK

- The data transfer has to be in the order shown in <u>Figure 14</u>. The bit 0 (LSB) = 0 of the address indicates a WRITE operation to the TEA5766UK, indicated by the R/W bit of the I<sup>2</sup>C-bus address.

- Bit 7 of each byte is considered the MSB and has to be transferred as the first bit of the byte.

- The data becomes valid bitwise at the appropriate falling edge of the clock. A stop condition after any byte can shorten transmission times. When writing to the transceiver by using the stop condition before completion of the whole transfer:

- The remaining bytes will contain the old information.

- If the transfer of a byte is not completed, the new bits will be used, but a new tuning cycle will not be started.

To speed up RDS traffic it is possible to read all the RDS data and then only write back byte INTMSK to set the appropriate mask(s) again.

Figure 15 shows the sequence of  $I^2C$ -bus data bytes for read and write operations for both FM and FM + RDS access. For simplicity the address, start, stop and acknowledge bits are not shown. The FM and RDS part have different  $I^2C$ -bus addresses as stated.

When the TEA5766UK is addressed with the FM radio address, also in one read action byte 12R to byte 27R can be read. A read does not have to stop at byte 11R.

When writing also all bytes, byte 0W to byte 10W can be written with one write action.

So effectively using the RDS part address only skips some bytes, which reduces bus access.

| BYTE 0R                          | BYTE 1R                        | BYTE 2R    | BYTE 3R  | BYTE 4R  | BYTE 5R  | BYTE 6R  | BYTE 7R   | BYTE 8R  | BYTE 9R  | BYTE 10R | BYTE 11R  |

|----------------------------------|--------------------------------|------------|----------|----------|----------|----------|-----------|----------|----------|----------|-----------|

|                                  |                                |            |          |          | •        |          |           |          |          |          | 001aaf458 |

| a. FM                            | read mode                      | e data tra | nsfer    |          |          |          |           |          |          |          |           |

|                                  |                                |            |          |          |          |          |           |          |          |          |           |

| BYTE 12R                         | BYTE 13R                       | BYTE 14R   | BYTE 15R | BYTE 16R | BYTE 17R | BYTE 18R | BYTE 19R  | BYTE 20R | BYTE 21R | BYTE 22R | BYTE 23R  |

| BYTE 24R                         | BYTE 25R                       | BYTE 26R   | BYTE 27R |          |          |          |           |          |          |          | 001aaf459 |

|                                  |                                |            |          | -        |          |          |           |          |          |          |           |

| b. RDS read mode data transfer   |                                |            |          |          |          |          |           |          |          |          |           |

|                                  |                                |            |          |          |          |          |           |          |          |          |           |

|                                  |                                | BYT        | E OW BYT | E 1W BYT | E 2W BYT | E 3W BYT | E 4W BYT  | E 5W BYT | ∃ 6W     |          |           |

| 001aaf460                        |                                |            |          |          |          |          |           |          |          |          |           |

| c. FM                            | c. FM write mode data transfer |            |          |          |          |          |           |          |          |          |           |

|                                  |                                |            |          |          |          |          |           |          |          |          |           |

| BYTE 7W BYTE 8W BYTE 9W BYTE 10W |                                |            |          |          |          |          |           |          |          |          |           |

|                                  |                                |            |          |          |          |          |           |          |          |          |           |

|                                  |                                |            |          |          |          |          | 001aaf461 |          |          |          |           |

| d. RDS write mode data transfer  |                                |            |          |          |          |          |           |          |          |          |           |

| d. RDS                           | S write mo                     | de data tr | ansfer   |          |          |          |           |          |          |          |           |

With the standby bit, the TEA5766UK can be switched in a low current Standby mode. Then the bus is still active. Is the bus interface deactivated, by making pin BUSEN LOW and without programmed Standby mode, the TEA5766UK keeps its normal operation, but is isolated from the bus lines.

It is possible to operate the TEA5766UK with pin BUSEN hard wired to pin VREFDIG and have the bus interface always active.

Power-on reset: the mute is set, all other bits are set default according to the tables in Section 11.2. To initialize the TEA5766UK all bytes have to be transferred.

#### **10.2.2** I<sup>2</sup>C-bus output driving characteristics

The I<sup>2</sup>C-bus output driving characteristics deviate from table 4 and table 5 in <u>Ref. 1</u> as shown in <u>Table 10</u>.

#### NXP Semiconductors

### **TEA5766UK**

Stereo FM radio + RDS

| Table TU.        | Characteristics of the data output stage for fast mode and standard mode |                                                                                    |     |     |     |      |  |  |

|------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|

| Symbol           | Parameter                                                                | Conditions                                                                         | Min | Тур | Max | Unit |  |  |

| V <sub>OL1</sub> | LOW-level output voltage                                                 | open collector; I <sub>sink</sub> = 2 mA; V <sub>VREFDIG</sub> > 2 V               |     |     |     |      |  |  |

|                  |                                                                          | standard mode                                                                      | 0   | -   | 0.5 | V    |  |  |

|                  |                                                                          | fast mode                                                                          | 0   | -   | 0.5 | V    |  |  |

| V <sub>OL3</sub> | LOW-level output voltage                                                 | fast mode; open collector; I <sub>sink</sub> = 2 mA;<br>V <sub>VREFDIG</sub> < 2 V | 0   | -   | 0.5 | V    |  |  |

| t <sub>of</sub>  | output fall time                                                         | from $V_{IH(min)}$ to $V_{IL(max)}$ ; $C_b = 5 \text{ pF}$ to 100 pF [1]           |     |     |     |      |  |  |

|                  |                                                                          | standard mode                                                                      | 250 | -   | 350 | ns   |  |  |

|                  |                                                                          | fast mode                                                                          | 250 | -   | 350 | ns   |  |  |

#### Table 40 Characteristics of the data output stage for fast mode and standard mode

[1] The maximum fall time for the SDA and SCL bus lines quoted in table 5 of Ref. 1, 300 ns, is shorter than the specified maximum for the output stages, 350 ns, therefore no series protection resistors may be connected between the SDA and SCL pins and the SDA and SCL bus lines as shown in figure 36 of Ref. 1.

#### 10.2.3 I<sup>2</sup>C-bus timing diagram

#### 10.3 SPI-bus

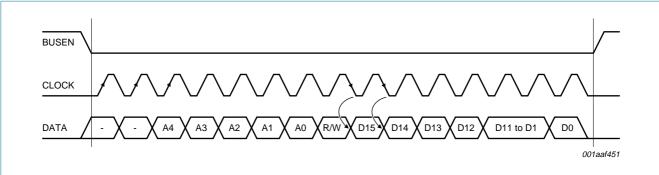

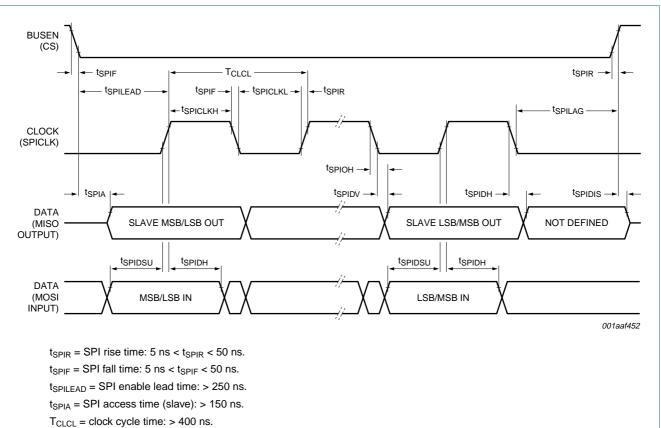

SPI stands for serial peripheral interface. TEA5766UK uses the SPI-bus in 3-wire mode, the data-in and data-out are combined to one bidirectional data line.

For this application the SPI-bus works as a slave receiver or a slave transmitter. During an SPI transfer, the input serial clock line SPICLK is driven by the master microcontroller up to a frequency of 2.5 MHz and synchronizes shifting and sampling the information on the serial data line. The slave select line CS allows individual selection of a slave SPI device. The lines of the SPI-bus interface are associated to pins as shown in Table 11.

#### Table 11. SPI-bus control signals and pinning

| SPI signal | TEA5766UK pin | Description                           |

|------------|---------------|---------------------------------------|

| CS         | BUSEN         | chip select (active LOW)              |

| SPICLK     | CLOCK         | clock input line                      |

| MOSI/MISO  | DATA          | serial data input and output of slave |

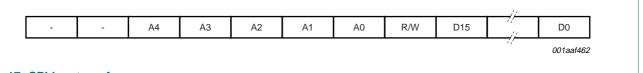

The TEA5766UK functions as a slave receiver and slave transmitter with a maximum clock frequency of 2.5 MHz. Data transfer is possible when signal CS (pin BUSEN) is LOW. When pin BUSEN is HIGH, the clock input line is disabled internally and the serial output of the TEA5766UK is in 3-state. The data transfer consists of packages of 8 bits data. First the address byte is shifted in, followed by 2 data bytes, which gives a total of 24 bits.

#### Fig 17. SPI-bus transfer

The address byte consists of 2 null bits, 5 address bits and 1 bit (R/W) for the direction of the data transfer. The 2 null bits are added to the address byte because of the SPI 8-bit data transfer protocol. Bits A[4:0] are the register address. All register addresses between 0 and 15 are allowed. Register addresses between 16 and 31 are not recognized and the SPI-bus interface leaves the data line in 3-state.

The R/W bit determines the direction of the data transfer. If R/W = 1, the slave device is set to read mode and if R/W = 0, the slave device is set to write mode.

Bits D[15:0] are the data bits. This data size corresponds to that of the register bank implemented in the TEA5766UK. The data transfer is such that the MSB is shifted first and the LSB last.

When pin BUSEN becomes LOW, an SPI start condition is detected and data is sampled in the slave device on the rising edge of the pin CLOCK signal. After the R/W bit is shifted in, the R/W selection becomes active at the next falling edge. If R/W = 1 data will be put at the data output and shifted out on the falling edge of the CLOCK.

When pin BUSEN becomes HIGH, the slave device (TEA5766UK) will be set to Idle mode, in which the data output line is set to 3-state. A negative edge on pin BUSEN restarts the data transfer. In <u>Figure 18</u> and <u>Figure 19</u> the SPI transfer is shown.

Stereo FM radio + RDS

#### Fig 18. SPI transfer, 3 wire-mode

$t_{SPICLKH} = SPICLK HIGH time: > 190 ns.$

$t_{SPICLKL} = SPICLK LOW time: > 190 ns.$

- $t_{SPILAG} = SPI \text{ enable lag time: } 250 \text{ ns.}$

- $t_{SPIOH} = SPI$  output data hold time: > 0 s.

- $t_{SPIDIS}$  = SPI disable time (slave): 0 ns <  $t_{SPIDIS}$  < 167 ns.

- t<sub>SPIDSU</sub> = SPI data set-up time (master or slave): > 5 ns.

- t<sub>SPIDH</sub> = SPI data hold time (master or slave): > 5 ns.

- $t_{SPIDV}$  = SPI enable to output data valid time: < 240 ns.

- Fig 19. SPI-bus timing diagram

## **11. Registers**

#### 11.1 Register map

The reference for the register map is the Motorola SPI addressing. The actual register is in fact one long register, so the I<sup>2</sup>C-bus bytes are mapped onto the SPI registers.

| Table 12. | Register | overview |

|-----------|----------|----------|

|-----------|----------|----------|

| Register name SPI address |    | I <sup>2</sup> C-bus byt | e number | R/W access | Reset                  | Reference |

|---------------------------|----|--------------------------|----------|------------|------------------------|-----------|

|                           |    | Read                     | Write    |            |                        |           |

| INTREG                    | 02 | 0R - 1R                  | 0W[1]    | R/W        | 0000h                  | Table 14  |

| FRQSET                    | 03 | 2R - 3R                  | 1W - 2W  | R/W        | 8000h                  | Table 15  |

| TNCTRL                    | 04 | 4R - 5R                  | 3W - 4W  | R/W        | 08D2h                  | Table 16  |

| FRQCHK                    | 05 | 6R - 7R                  |          | R          | -                      | Table 17  |

| TUNCHK                    | 06 | 8R - 9R                  |          | R          | -                      | Table 18  |

| TESTREG                   | 07 | 10R - 11R                | 5W - 6W  | R/W        | 0000h                  | Table 19  |

| RDSR1                     | 08 | 12R - 13R                |          | R          | -                      | Table 22  |

| RDSR2                     | 09 | 14R - 15R                |          | R          | -                      | Table 23  |

| RDSR3                     | 10 | 16R - 17R                |          | R          | -                      | Table 24  |

| RDSR4                     | 11 | 18R - 19R                |          | R          | -                      | Table 25  |

| RDSW1                     | 12 | 20R - 21R                | 7W - 8W  | R/W        | 0010h                  | Table 26  |

| RDSW2                     | 13 | 22R - 23R                | 9W - 10W | R/W        | 0000h                  | Table 27  |

| MANID                     | 00 | 24R - 25R                |          | R          | 102Bh <mark>[2]</mark> | Table 28  |