# **MIC2808**

RF PA Power Management IC 2MHz, 600mA DC/DC w/DAC Input and Bypass Switch, Dual Low Noise 200mA/30mA LDO Regulators

# **General Description**

The MIC2808 integrates a high performance 600mA DC/DC step down regulator intended for powering a power amplifier (PA) in a mobile phone with dual low noise low dropout (LDO) regulators for the rest of the RF section. Optimized for low noise performance, the MIC2808 improves efficiency in the handset without compromising quality.

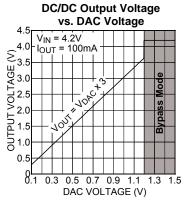

The MIC2808 has a 2MHz, constant frequency pulse width modulated (PWM) DC/DC regulator designed for low noise operation and high efficiency. The output voltage (V<sub>OUT</sub>) is variable from 0.3V to the input voltage (V<sub>IN</sub>), adjustable from 0.3V to 3.6V through a DAC input when V<sub>IN</sub> > V<sub>OUT</sub>. The regulator will work in a 100% duty cycle mode to offer maximum power and efficiency in the application. In addition to 100% duty cycle, the DC/DC regulator has a bypass mode of operation where the input voltage node (PVIN pin) is shorted to the output voltage node (OUT pin) through a 95m $\Omega$  switch.

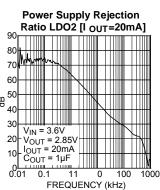

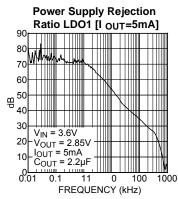

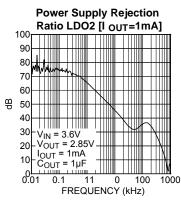

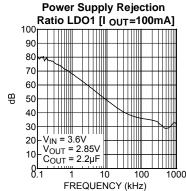

The integrated dual low noise low dropout regulators are optimized for high PSRR capability and fast turn-on times. The constant frequency DC/DC regulator along with dual low noise LDO regulators enables a very quiet and efficient solution for mobile applications.

The MIC2808 is a  $\mu$ Cap design, operating with small ceramic output capacitors and inductors for stability, reducing required board space and component cost and it is available in the tiny 2.0mm x 2.5mm TMLF<sup>®</sup> package.

Data sheets and support documentation can be found on Micrel's web site at: www.micrel.com.

#### **Features**

- 2.7V to 5.5V input voltage range

- · Stable with ceramic output capacitors

- Tiny 16-pin 2.0mm x 2.5mm TMLF® Package

- Thermal shutdown protection

- · Current limit protection

## RF PA Power Supply DC/DC Regulator

- Adjustable output power supply DAC controlled

- $V_{OUT} = V_{DAC} \times 3$

- · Bypass mode operation

- Internal  $95m\Omega$  switch between PVIN and OUT pins

- $V_{DAC} > 1.2V$

- Up to 600mA output current in PWM mode

- 100% duty cycle operation for maximum efficiency

- Tiny 4.7µH, 1µF output inductor and capacitor

- Low-noise 2MHz PWM operation

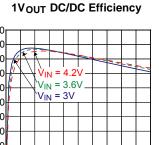

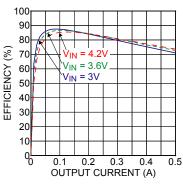

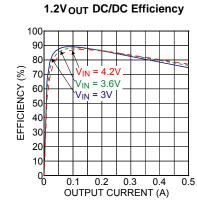

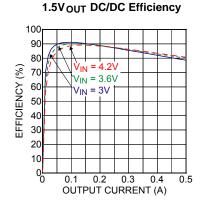

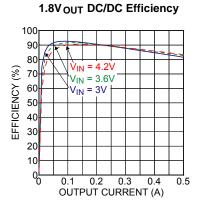

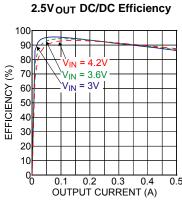

- >90% efficiency

## **Dual Low Noise Low Dropout Regulators**

- High accuracy ±2% over temperature

- High PSRR greater than 70dB

- Very low output noise 32µVrms

- LDO1 200mA output current capability

- LDO2 30mA output current capability

# **Applications**

- CDMA2000 mobile phones

- UMTS/WCDMA mobile phones

- WiMAX/Wibro modules

- · WiFi modules

- Power amplifier modules (PAMs) with linear PAs

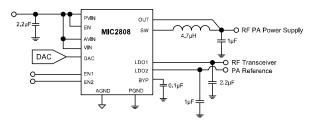

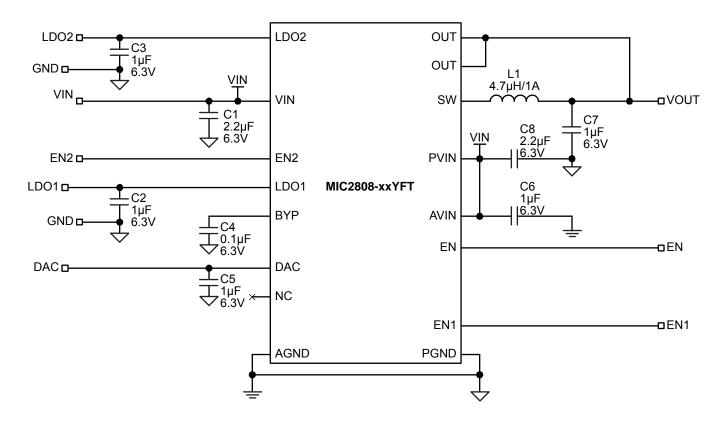

# **Typical Application**

CDMA2000/WCDMA RF Power Supply Circuit

MLF and MicroLeadFrame are registered trademarks of Amkor Technology, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

July 2009 M9999-071709-A

# **Ordering Information**

| Part Number   | Marking<br>Code | LDO1/LDO2<br>Voltage <sup>(3)</sup> | Junction<br>Temp. Range | Package <sup>(1)</sup>         | Lead Finish <sup>(2)</sup> |

|---------------|-----------------|-------------------------------------|-------------------------|--------------------------------|----------------------------|

| MIC2808-NNYFT | NNYJ            | 2.85V/2.85V                         | –40°C to +125°C         | 16-Pin 2.0mm x 2.5mm Thin MLF® | Pb-Free                    |

#### Note:

- 1. Thin MLF<sup>®</sup> = Pin 1 identifier.

- 2. Thin MLF® is a GREEN RoHS compliant package. Lead finish is NiPdAu. Mold compound is halogen free.

- 3. Contact Micrel for other output voltages.

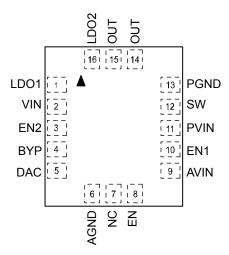

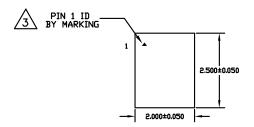

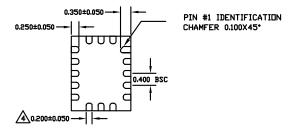

# **Pin Configuration**

16-Pin 2.0mm x 2.5mm Thin MLF® (FT) (Top View)

# **Pin Description**

| Pin<br>Number | Pin Name | Pin Function                                                                                                                                                                                                                                                                              |

|---------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | LDO1     | Output of the LDO1.                                                                                                                                                                                                                                                                       |

| 2             | VIN      | LDO1 and LDO2 Supply Voltage. Must be connected to PIN 9 (AVIN).                                                                                                                                                                                                                          |

| 3             | EN2      | Enables the LDO2 regulator. Do not leave floating.                                                                                                                                                                                                                                        |

| 4             | BYP      | Filter capacitor for LDO1 and LDO2 internal voltage reference. Connect a 0.1µF capacitor-to-ground.                                                                                                                                                                                       |

| 5             | DAC      | DAC Control Input (Analog Voltage Input). Provides control of output voltage of DC/DC regulator. The output voltage is 3x's the DAC voltage (Ex. $0.5V_{DAC} = 1.5V_{OUT}$ ) when $V_{IN} > V_{OUT}$ . Bypass mode is enabled when the DAC voltage exceeds 1.2V or $V_{IN} \le V_{OUT}$ . |

| 6             | AGND     | Signal ground.                                                                                                                                                                                                                                                                            |

| 7             | NC       | No Connect.                                                                                                                                                                                                                                                                               |

| 8             | EN       | Enables the DC/DC Regulator. Do not leave floating.                                                                                                                                                                                                                                       |

| 9             | AVIN     | Supply voltage for DC/DC regulator control circuitry and reference voltage circuit. Must be connected to PIN 2 (VIN).                                                                                                                                                                     |

| 10            | EN1      | Enables LDO1 Regulator. Do not leave floating.                                                                                                                                                                                                                                            |

| 11            | PVIN     | Supply Voltage: Requires bypass capacitor to ground.                                                                                                                                                                                                                                      |

| 12            | SW       | Switch: Internal power MOSFET output switches of DC/DC regulator.                                                                                                                                                                                                                         |

| 13            | PGND     | Power ground.                                                                                                                                                                                                                                                                             |

| 14, 15        | OUT      | Drain of internal bypass switch, also serves as feedback for the internal regulator.                                                                                                                                                                                                      |

| 16            | LDO2     | Output of the LDO2.                                                                                                                                                                                                                                                                       |

# Absolute Maximum Ratings<sup>(1)</sup>

| Supply Voltage (PV <sub>IN</sub> , AV <sub>IN</sub> , V <sub>IN</sub> )                                          | 0V to 6V              |

|------------------------------------------------------------------------------------------------------------------|-----------------------|

| Output Switch Voltage (V <sub>SW</sub> )                                                                         | 6V                    |

| DAC Input Voltage (V <sub>DAC</sub> )                                                                            |                       |

| Logic Input Voltage (V <sub>EN</sub> , V <sub>EN1</sub> , V <sub>EN2</sub> )                                     | 0V to V <sub>IN</sub> |

| Logic Input Voltage (V <sub>EN</sub> , V <sub>EN1</sub> , V <sub>EN2</sub> )<br>Power Dissipation <sup>(3)</sup> | Internally Limited    |

| Storage Temperature (T <sub>s</sub> )                                                                            | 65°C to +150°C        |

| Storage Temperature (T <sub>s</sub> )<br>ESD Rating <sup>(4)</sup>                                               | ±2kV                  |

# Operating Ratings<sup>(2)</sup>

| Supply Voltage (PV <sub>IN</sub> , AV <sub>IN</sub> , V <sub>IN</sub> ) | 2.7V to 5.5V            |

|-------------------------------------------------------------------------|-------------------------|

| Output Voltage (V <sub>OUT</sub> )                                      | 0V to V <sub>IN</sub>   |

| Enable Voltage (V <sub>EN</sub> , V <sub>EN1</sub> , V <sub>EN2</sub> ) | 0V to V <sub>IN</sub>   |

| DAC Input Voltage (V <sub>DAC</sub> )                                   | 0.1V to V <sub>IN</sub> |

| Junction Temperature (T <sub>J</sub> )                                  | 40°C to +125°C          |

| Thermal Resistance                                                      |                         |

| 2.0mmx2.5mm TMLF-16 (θ <sub>JA</sub> )                                  | 96°C/W                  |

|                                                                         |                         |

# Electrical Characteristics<sup>(5)</sup>

## **DC/DC** Regulator

$V_{IN}$  =  $PV_{IN}$  =  $AV_{IN}$  =  $V_{EN}$  = 3.6V;  $V_{DAC}$  = 0.6V;  $V_{EN1}$  =  $V_{EN2}$  = 0V; L = 4.7 $\mu$ H;  $C_{OUT}$  = 1 $\mu$ F;  $T_A$  = 25°C, **bold** values indicate  $-40^{\circ}C \le T_J \le +125^{\circ}C$ , unless noted.

## LDO1/LDO2

$V_{IN} = V_{EN1} = V_{EN2} = 3.6V; \ C_{OUTLDO1} = 2.2 \mu F; \ V_{EN} = 0V; \ C_{OUTLDO2} = 1 \mu F; \ I_{OUT} = 100 \mu A; \ T_A = 25^{\circ}C, \ \textbf{bold} \ values \ indicate -40^{\circ}C \leq T_J \leq +125^{\circ}C, \ unless \ noted.$

| Parameter                           | Condition                                                                      | Min   | Тур  | Max   | Units |

|-------------------------------------|--------------------------------------------------------------------------------|-------|------|-------|-------|

| Supply Voltage Range                |                                                                                | 2.7   |      | 5.5   | V     |

| Total Quiescent Current             | $V_{EN} = V_{EN1} = V_{EN2} = 3.6V$<br>$V_{DAC} = 0.6V$ (DC/DC: not switching) |       | 480  |       | μA    |

| Enable Pin Threshold                | Logic Low                                                                      |       |      | 0.4   | V     |

|                                     | Logic High                                                                     | 1.3   |      |       | V     |

| Enable Pin Hysteresis               |                                                                                |       | 70   |       | mV    |

| Enable Pin Input Current            |                                                                                |       | 0.01 | 1     | μA    |

| Under-Voltage<br>Lockout Threshold  | (turn-on)                                                                      |       | 2.6  | 2.7   | V     |

| UVLO Hysteresis                     |                                                                                |       | 85   |       | mV    |

| Shutdown Temperature                |                                                                                |       | 160  |       | °C    |

| Shutdown Temperature Hysteresis     |                                                                                |       | 20   |       | °C    |

| Total Shutdown Current              | $V_{EN} = V_{EN1} = V_{EN2} = 0V$                                              |       | 1    | 5     | μA    |

| DC/DC Regulator [V <sub>EN1</sub> = | $V_{EN2} = 0V$                                                                 |       |      |       |       |

| Maximum Duty Cycle                  |                                                                                | 100   |      |       | %     |

| Bypass Quiescent<br>Current         | V <sub>DAC</sub> = 1.3V                                                        |       | 490  | 650   | μA    |

| Quiescent Current                   | V <sub>DAC</sub> = 0.6V (regulator on, not switching)                          |       | 360  | 450   | μA    |

| Output Voltage                      | $V_{DAC} = 0.6V$ , $I_{LOAD} = 0mA$                                            | 1.746 | 1.8  | 1.854 | V     |

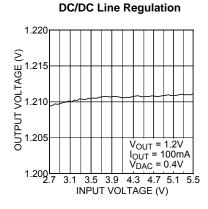

| Output Voltage<br>Line Regulation   | 3.0V≤ V <sub>IN</sub> ≤ 4.5, I <sub>LOAD</sub> = 10mA                          |       | 0.05 | 0.5   | %/V   |

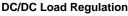

| Output Voltage<br>Load Regulation   | 0mA < I <sub>OUT</sub> < 400mA                                                 |       | 0.2  |       | %     |

| Switch On-Resistance                | I <sub>SW</sub> = -100mA, High-Side Switch                                     |       | 0.55 | 0.7   | Ω     |

|                                     | I <sub>SW</sub> = 100mA, Low-Side Switch                                       |       | 0.59 | 8.0   | Ω     |

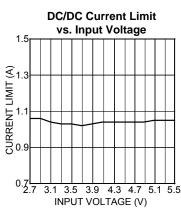

| Current Limit<br>(Peak SW Current)  |                                                                                | 0.65  | 0.85 | 1.6   | А     |

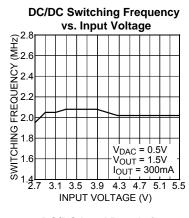

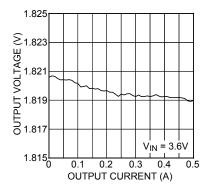

| Frequency                           |                                                                                | 1.8   | 2    | 2.2   | MHz   |

| Parameter                           | Condition                                                                    | Min       | Тур  | Max   | Units         |

|-------------------------------------|------------------------------------------------------------------------------|-----------|------|-------|---------------|

| Turn-On Time                        | I <sub>OUT</sub> = 100μA                                                     |           | 25   | 50    | μs            |

| DAC Input Current                   |                                                                              |           | 0.15 | 2     | μA            |

| Output Voltage/<br>DAC Voltage      | (internally set)                                                             |           | 3    |       | V/V           |

| Bypass Switch<br>Threshold          | DAC Voltage required to enable bypass mode                                   | 1.176     | 1.2  | 1.224 | V             |

| Bypass Switch<br>Hysteresis         |                                                                              |           | 35   |       | mV            |

| Bypass Transition Time              | Delay from V <sub>DAC</sub> = 1.3V to V <sub>OUT</sub> = 0.90V <sub>IN</sub> |           | 10   | 40    | μs            |

| Bypass Switch<br>On-Resistance      | $V_{IN} = 3.0V$ , $I_{BYPASS} = 100mA$                                       |           | 95   | 150   | mΩ            |

| Bypass Switch Leakage               |                                                                              |           |      | 5     | μA            |

| Bypass Over-Current<br>Limit        |                                                                              | 1         | 1.4  | 2.5   | А             |

| Current Limit Retry Time            |                                                                              |           | 32   |       | μs            |

| Current Limit Retry<br>Duty Cycle   |                                                                              |           | 12.5 |       | %             |

| LDO1/LDO2 [V <sub>EN</sub> = 0V]    |                                                                              |           |      |       |               |

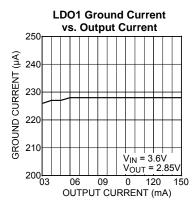

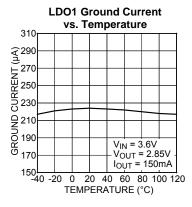

| Total Ground Current <sup>(8)</sup> | V <sub>EN1</sub> = V <sub>EN2</sub> = 3.6V                                   |           | 220  |       | μA            |

| Turn-on Time                        | LDO1 or LDO2; $C_{BYP} = 0.1 \mu F$                                          |           | 30   | 100   | μs            |

| LDO1 [V <sub>EN</sub> = 0V]         |                                                                              |           |      |       |               |

| Output Voltage Accuracy             | Variation from nominal V <sub>OUT</sub>                                      | <b>–1</b> |      | +1    | %             |

|                                     | -40°C to +125°C                                                              | -2        |      | +2    | %             |

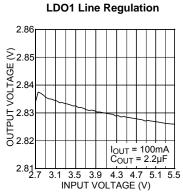

| Line Regulation                     | $V_{IN} = V_{OUT} + 1V \text{ to } 5.5V$                                     |           | 0.02 | 0.3   | %/V           |

| Load Regulation <sup>(6)</sup>      | I <sub>OUT</sub> = 100μA to 200mA                                            |           | 0.2  | 0.5   | %             |

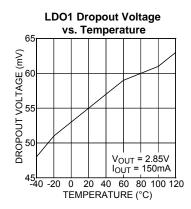

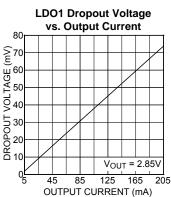

| Dropout Voltage <sup>(7)</sup>      | $I_{OUT} = 50 \text{mA}; V_{OUT} > 2.8 \text{V}$                             |           | 20   |       | mV            |

|                                     | $I_{OUT} = 150 \text{mA}; V_{OUT} > 2.8 \text{V}$                            |           | 55   |       | mV            |

|                                     | I <sub>OUT</sub> = 200mA; V <sub>OUT</sub> > 2.8V                            |           | 70   | 100   | mV            |

| Ground Pin Current <sup>(8)</sup>   | I <sub>OUT</sub> = 0mA; EN2 = GND                                            |           | 190  | 300   | μΑ            |

| Ripple Rejection                    | $f = up to 1kHz; C_{BYP} = 0.1\mu F$                                         |           | 70   |       | dB            |

|                                     | $f = 1kHz - 20kHz$ ; $C_{BYP} = 0.1\mu F$                                    |           | 45   |       | dB            |

| Current Limit                       | V <sub>OUT</sub> = 0V                                                        | 225       | 300  | 700   | mA            |

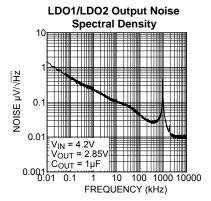

| Output Voltage Noise                | C <sub>BYP</sub> =0.1μF, 10Hz to 100kHz                                      |           | 32   |       | $\mu V_{RMS}$ |

| LDO2 [V <sub>EN</sub> = 0V]         |                                                                              | T         | ı    | 1     | 1             |

| Output Voltage Accuracy             | Variation from nominal V <sub>OUT</sub>                                      | _1        |      | +1    | %             |

|                                     | _40°C to +125°C                                                              | -2        |      | +2    | %             |

| Line Regulation                     | $V_{IN} = V_{OUT} + 1V \text{ to } 5.5V$                                     |           | 0.02 | 0.3   | %/V           |

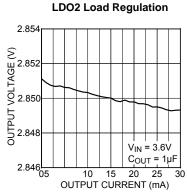

| Load Regulation <sup>(6)</sup>      | I <sub>OUT</sub> = 100μA to 30mA                                             |           | 0.2  | 0.5   | %             |

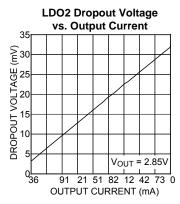

| Dropout Voltage <sup>(7)</sup>      | $I_{OUT} = 10$ mA; $V_{OUT} > 2.8$ V                                         |           | 10   |       | mV            |

| (8)                                 | I <sub>OUT</sub> = 30mA; V <sub>OUT</sub> > 2.8V                             |           | 30   | 60    | mV            |

| Ground Pin Current <sup>(8)</sup>   | I <sub>OUT</sub> = 0mA; EN1 = GND                                            |           | 190  | 300   | μA            |

| Ripple Rejection                    | $f = up \text{ to } 1kHz; C_{BYP} = 0.1 \mu F$                               |           | 65   |       | dB            |

|                                     | $f = 1kHz - 20kHz; C_{BYP} = 0.1\mu F$                                       |           | 40   |       | dB            |

| Current Limit                       | V <sub>OUT</sub> = 0V                                                        | 40        | 60   | 150   | mA            |

| Output Voltage Noise                | $C_{BYP} = 0.1 \mu F$ , 10Hz to 100kHz                                       |           | 32   |       | $\mu V_{RMS}$ |

#### Notes:

- 1. Exceeding the absolute maximum rating may damage the device.

- 2. The device is not guaranteed to function outside its operating rating.

- 3. The maximum allowable power dissipation of any T<sub>A</sub> (ambient temperature) is P<sub>D(max)</sub> = (T<sub>J(max)</sub> T<sub>A</sub>) / θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will result in excessive die temperature, and the regulator will go into thermal shutdown.

- 4. Devices are ESD sensitive. Handling precautions recommended.

- 5. Specification for packaged product only.

- 6. Regulation is measured at constant junction temperature using low duty cycle pulse testing, changes in output voltage due to heating effects are covered by the thermal regulation specification.

- 7. Dropout voltage is defined as the input-to-output differential at which the output voltage drops 2% below its nominal value measured at 1V differential.

- 8. Ground pin current is the regulator quiescent current.

MIC2808 Micrel, Inc.

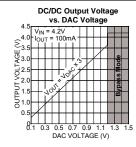

# **Typical Characteristics (DC/DC)**

# **Typical Characteristics (LDO1/LDO2)**

#### 2.860 2.855 0 2.855 0 2.845 0 2.845 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.840 2.

INPUT VOLTAGE (V)

# **Typical Characteristics (LDO1/LDO2 cont.)**

MIC2808 Micrel, Inc.

# **Functional Characteristics**

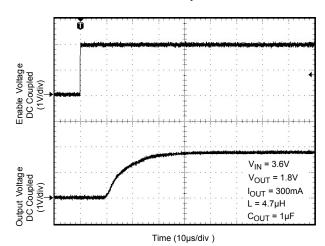

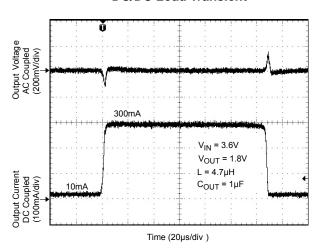

$V_{IN} = 3.6V$

V<sub>OUT</sub> = 1.8V

# **DC/DC PWM Waveforms**

# Switch Voltage DC Coupled (2V/div) Output Voltage AC Coupled (10mV/div) Inductor Current DC Coupled (100m/A/div)

$I_{OUT} = 100mA$

L = 4.7µH

$C_{OUT} = 1\mu F$

Time (400ns/div)

## **DC/DC Start-Up Waveforms**

## **DC/DC Load Transient**

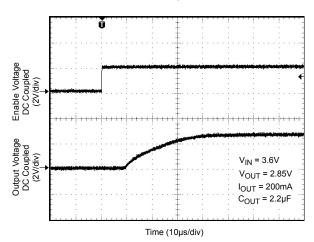

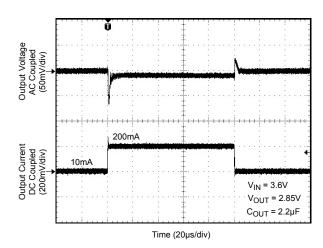

# **Functional Characteristics (continued)**

# **LDO1 Start-Up Waveforms**

## **LDO1 Load Transient**

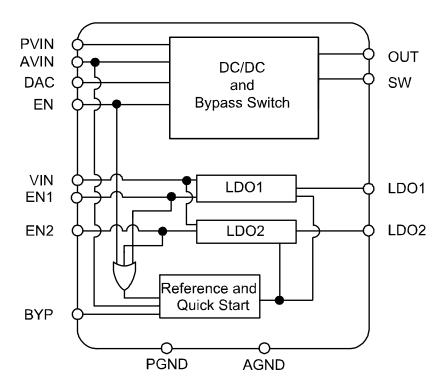

# **Functional Diagram**

MIC2808 Block Diagram

# **Device Functional Description**

The MIC2808 is a power management IC with a single integrated step-down regulator and two low dropout regulators. LDO1 is a 200mA low dropout regulator and LDO2 is a 30mA low dropout regulator. The 500mA pulse-width-modulated (PWM) step-down regulator utilizes a dynamically adjustable output voltage for powering RF power amplifiers. By dynamically adjusting the output power as necessary, battery life can be dramatically improved in battery powered RF power amplifier applications. Also where high power is required, the step-down PWM regulator has a bypass mode where an internal  $95m\Omega$  switch connects the OUT and PVIN pins together.

## **Pin Functional Description**

#### **PVIN**

PVIN (Power VIN) provides power to the MOSFETs for the step-down switching regulator section of the MIC2808, along with the current limit sensing circuitry. Due to the high switching speeds, a minimum 1µF capacitor is recommended close to PVIN and the power ground (PGND) pin for bypassing\*.

#### **AVIN**

AVIN (Analog VIN) provides power to the internal reference and control section of the step-down regulator. AVIN, VIN, and PVIN must all be tied together. Careful layout should be considered to ensure high frequency switching noise caused by PVIN is reduced before reaching AVIN\*.

#### DAC

The DAC pin is the control pin that sets the output voltage of the step-down regulator. The Output voltage is 3X the voltage set on the DAC pin ( $V_{OUT} = V_{DAC} \times 3$ ). When 1.2V or greater is applied to the DAC pin, the MIC2808's step-down regulator enters bypass mode. In bypass mode, the input supply is connected to the output through a 95m $\Omega$  P-Channel MOSFET.

#### EN/EN1/EN2

The EN pin provides a logic level control of the step-down regulator output. In the off state, supply current of the device is greatly reduced (typically  $\leq 1\mu A$ ). Also, in the off state, the output drive and bypass switch are placed in a "tri-stated" condition, where both the high side P-channel MOSFET and the low-side N-channel are in an off or non-conducting state. EN1 provides logic control for LDO1, and EN2 provides logic control for LDO2. Placing a logic high voltage on any one of the respective enable pins (EN, EN1 or EN2) will turn-on (powering up the bias and control circuitry) that respective regulator (DC/DC, LDO1 or LDO2). Do not drive the enable pins above the supply voltage (AVIN and VIN).

#### VIN

VIN provides power to the LDO1 and the LDO2 control sections of the MIC2808. A minimum 1 $\mu$ F capacitor, 2.2 $\mu$ F recommended, should be placed as close as possible between the VIN and AGND pins. VIN must have the same voltage as AVIN\*.

#### OUT

The OUT pin connects the internal bypass drain and the feedback signal to the output. The bypass applies the input voltage through a low resistance (95m $\Omega$  typical) P-Channel MOSFET switch. The feedback signal provides the control path to set the output at three times the DAC voltage.

#### SW

The SW pin connects directly to the inductor and provides the switching current necessary to operate in PWM mode. Due to the high speed switching on this pin, the switch node should be routed away from sensitive nodes.

#### **PGND**

PGND (Power GND) is the ground path for the MOSFETs in the step-down regulator section. The current loop for the power ground should be as small as possible and separate from the analog ground (AGND) loop\*.

#### **AGND**

AGND (Analog GND) is the ground path for the biasing and control circuitry. The current loop for the signal ground should be separate from the Power ground (PGND) loop\*.

#### LD<sub>0</sub>1

Regulated output voltage of the LDO1. Power is provided by VIN. Recommended output capacitance is  $2.2\mu F$ .

#### LDO2

Regulated output voltage of the LDO2. Power is provided by VIN. Recommended output capacitance is 1µF.

#### **BYP**

Filter capacitor for the voltage reference for the LDO1 and the LDO2. A 100nF capacitor is recommended from the BYP pin to ground.

\* Refer to PCB layout section of this data sheet for optimal layout principles.

# **Component Selection**

## **Output Capacitor**

LDO1 output requires a 2.2 $\mu$ F ceramic capacitor, while the LDO2 and DC/DC regulator outputs require a 1 $\mu$ F ceramic capacitor. All output capacitor values can be increased to improve transient response, but performance has been optimized for a 2.2 $\mu$ F ceramic capacitor for LDO1 and 1 $\mu$ F ceramic capacitors for both the DC/DC regulator and LDO2. X7R/X5R dielectric-type ceramic capacitors are recommended because of their temperature performance. X5R/X7R-type capacitors change capacitance by 15% over their operating temperature range and are the most stable type of ceramic capacitors. Z5U and Y5V dielectric capacitors change value by as much as 50% to 60% respectively over their operating temperature ranges.

# **Input Capacitor**

For optimal bypassing a minimum 1µF ceramic, 2.2µF recommended, should be placed as close as possible to the VIN pin. X5R or X7R dielectrics are recommended for the input capacitor. Y5V dielectrics lose most of their capacitance over temperature and are therefore, not recommended. For high frequency filtering a minimum 1µF is recommended close to the VIN and PGND pins. Smaller case size capacitors are recommended due to their lower ESR and ESL. Please refer to the PCB layout section for an example of an appropriate circuit layout.

#### **Inductor Selection**

The MIC2808 is designed for use with a 4.7µH inductor. Proper selection should ensure that the inductor can handle the maximum average and peak currents required by the load. Maximum current ratings of the inductor are generally given in two methods; permissible DC current and saturation current. Permissible DC current can be rated either for a 40°C temperature rise or a 10% to 20% loss in inductance. Ensure that the inductor selected can handle the maximum operating current. When saturation current is specified, make sure that there is enough margin, so that the peak current will not saturate the inductor. Peak inductor current can be calculated as follows:

$$I_{PK} = I_{OUT} + \frac{V_{OUT} \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}{2 \times f \times L}$$

I<sub>PK</sub>: Peak Inductor Current I<sub>OUT</sub>: Output/Load Current

$V_{\text{IN}}$ : Input Voltage  $V_{\text{OUT}}$ : Output Voltage

f: Switching Frequency of PWM Regulator

L: Inductor Value

# **Typical Application Circuit**

# **Bill of Materials**

| Item                | Part Number      | Manufacturer                | Description                                                                      | Qty. |

|---------------------|------------------|-----------------------------|----------------------------------------------------------------------------------|------|

| C1, C8              | C1608X5R0J225K   | TDK <sup>(1)</sup>          | 2.2µF Ceramic Capacitor, 6.3V, X5R, Size 0603                                    | 2    |

| C2,<br>C3,<br>C5-C7 | C1608X5R0J105K   | TDK <sup>(1)</sup>          | 1μF Ceramic Capacitor, 6.3V, X5R, Size 0603                                      | 5    |

| C4                  | C1608X5R0J104K   | TDK <sup>(1)</sup>          | 0.1µF Ceramic Capacitor, 6.3V, X5R, Size 0603                                    | 1    |

|                     | VLS3012T-4R7M1R0 | TDK <sup>(1)</sup>          | 4.7μH, 1.2A, 130mΩ, L3.0mm x W3.0mm x H1.2mm                                     |      |

|                     | CDH3D13-4R7NC    | Sumida <sup>(3)</sup>       | 4.7μH, 1.15A, 175mΩ, L3.0mm x W3.0mm x H1.4mm                                    |      |

| L1                  | ME3220-472MLB    | Coilcraft <sup>(4)</sup>    | 4.7μH, 1.4A, 190mΩ, L3.2mm x W2.5mm x H2.0mm                                     | 1    |

|                     | LQH32CN4R7M53    | Murata <sup>(5)</sup>       | 4.7μH, 650mA, 150mΩ, L3.2mm x W2.5mm x H1.55mm                                   |      |

|                     | MIPF2520D4R7     | FDK <sup>(6)</sup>          | 4.7μH, 1.1A, 110mΩ, L2.5mm x W2.0mm x H1.0mm                                     |      |

| U1                  | MIC2808-xxYFT    | Micrel, Inc. <sup>(7)</sup> | 2MHz 600mA Buck with DAC Input, Bypass Switch and Dual Low Noise 200mA/30mA LDOs | 1    |

#### Notes:

- 1. TDK: www.tdk.com

- 2. Vishay: www.vishay.com

- ${\it 3. \; Sumida: www.sumida.com}\\$

- 4. Coilcraft: www.coilcraft.com

- 5. Murata: www.murata.com

- 6. FDK: www.fdk.co.jp

- 7. Micrel, Inc.: www.micrel.com

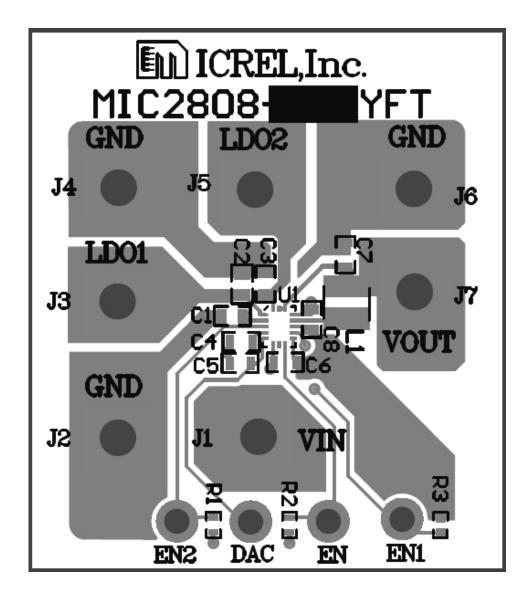

**Top Layer**

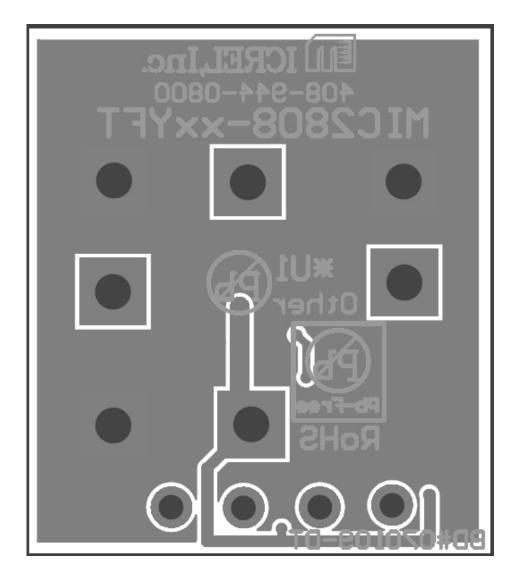

**Bottom Layer**

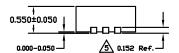

# **Package Information**

TOP VIEW

#### BOTTOM VIEW

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS, ANGLES ARE IN DEGREES.

N IS THE TOTAL NUMBER OF TERMINALS.

- 2. MAX PACKAGE WARPAGE IS 0.05mm, MAX ALLOWABLE BURRS IS 0.076 mm IN ALL DIRECTIONS.

- 3 PIN #1 ID ON TOP WILL BE LASER/INK MARKED.

- DIMENSION APPLIES TO PLATED TERMINAL AND IS MEASURED

- BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

\$\delta\process{APPLIED FOR EXPOSED PAD AND TERMINALS.}

SIDE VIEW

16-Pin 2.0mm x 2.5mm FC-TMLF® (FT)

## MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2009 Micrel, Incorporated.

July 2009 18 M9999-071709-A