## 433 MHz / 868 MHz / 915 MHz

# Low-Power, Integrated UHF Transceiver

## **GENERAL DESCRIPTION**

The XE1203F is a single chip transceiver operating in the 433, 868 and 915 MHz license-free ISM (Industry Scientific and Medical) frequency bands. Its highly integrated architecture allows for minimum external components while maintaining design flexibility. All major RF communication parameters are programmable and most of them can be dynamically set. The XE1203F offers the excellent advantage of high data rate communication at rates of up to 152.3 kbit/s, without the need to modify the number or parameters of the external components. The XE1203F is optimized for low power consumption while offering high RF output power and exceptional receiver sensitivity. The device is suitable for applications which have to satisfy either the European (ETSI-300-220) or the North American (FCC part 15) regulatory standards. TrueRF™ technology enables a low -cost external component count (elimination of the SAW filter) whilst still satisfying ETSI and FCC regulations.

## **APPLICATIONS**

- Automated Meter Reading (AMR)

- Home Automation and Access Control

- High-Quality Speech, Music and Data over RF

- · Applications requiring Konnex-compatibility

## **KEY PRODUCT FEATURES**

- RF output power: up to +15 dBm

- High reception sensitivity: down to –114 dBm (typical)

- Low power consumption: R<sub>x</sub> = 14 mA; T<sub>x</sub> = 62 mA @15 dBm (typical)

- Supply voltage down to 2.4V

- Data rate from 1.2 to 152.3 kbit/s, NRZ coding

- Konnex-compatible operation mode

- 11-bit Barker encoder/decoder

- On-chip frequency synthesizer with minimum frequency resolution of 500 Hz Continuous phase 2-level FSK modulation Received data pattern recognition

- Bit-Synchronizer for incoming data/clock synchronization and recovery

- RSSI (Received Signal Strength Indicator)

- FEI (Frequency Error Indicator)

- RoHS green package

## **ORDERING INFORMATION**

| Part number     | Temperature<br>range | Package |

|-----------------|----------------------|---------|

| XE1203FI063TRLF | -40 °C to +85 °C     | MLPQ48  |

## **Table of Contents**

| 1     | Functional Block Diagram                                    | . 3 |

|-------|-------------------------------------------------------------|-----|

| 2     | Pin description                                             | . 4 |

| 3     | Electrical Characteristics                                  | . 5 |

| 3.1   | Absolute Maximum Operating Ranges                           | . 5 |

| 3.2   | Specifications                                              |     |

| 3.2.1 | Operating Range                                             |     |

| 3.2.2 | Electrical Specifications                                   |     |

| 4     | GENERAL DESCRIPTION                                         | . 7 |

| 4.1   | The Receiver Section                                        |     |

| 4.1.1 | LNA & Receiver modes                                        |     |

| 4.1.2 | Demodulation chain                                          |     |

| 4.1.3 | Demodulator                                                 |     |

| 4.1.4 | Bit synchronizer                                            |     |

| 4.1.5 | The DATA and DATAIN pins                                    |     |

| 4.1.6 | Pattern recognition block                                   |     |

| 4.1.7 | RSSI                                                        |     |

| 4.1.8 | Frequency Error Indicator – FEI                             | 12  |

| 4.2   | The Transmitter Section.                                    |     |

| 4.2.1 | Transmitter                                                 |     |

| 4.2.2 | Barker encoder/decoder                                      |     |

| 4.3   | The Frequency Synthesizer                                   |     |

| 4.3.1 | Clock Output for external processor                         | 17  |

| 5     | SERIAL Interface definition AND Principles of operation     | 18  |

| 5.1   | Serial Control Interface                                    |     |

| 5.2   | Configuration and Status registers                          | 20  |

| 5.2.1 | The ConfigSwitch Register                                   |     |

| 5.2.2 | RTParam Configuration Register                              |     |

| 5.2.3 | FSParam Configuration Register                              |     |

| 5.2.4 | SWParam Configuration Register - switching parameters       | 24  |

| 5.2.5 | DataOut Status Register                                     | 25  |

| 5.2.6 | ADParam Configuration Register                              | 25  |

| 5.2.7 | Pattern register                                            |     |

| 5.2.8 | Test Registers and additional settings                      | 28  |

| 5.3   | Operating Modes                                             | 28  |

| 5.3.1 | Standard power up sequence for the receiver and transmitter | 28  |

| 5.4   | Selection of the reference frequency                        | 29  |

| 5.5   | Clock Output Interface                                      |     |

| 5.6   | Default settings at power-up                                |     |

| 6     | Application Information                                     | 31  |

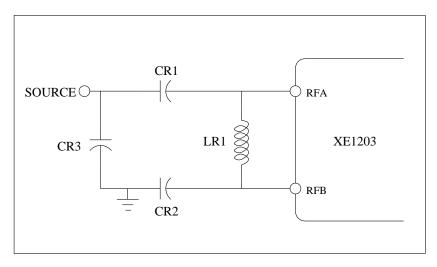

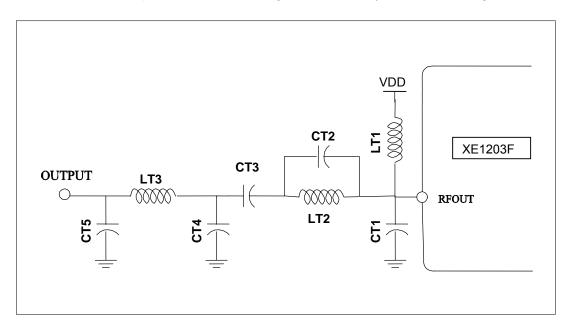

| 6.1   | RECEIVER Matching network                                   | 31  |

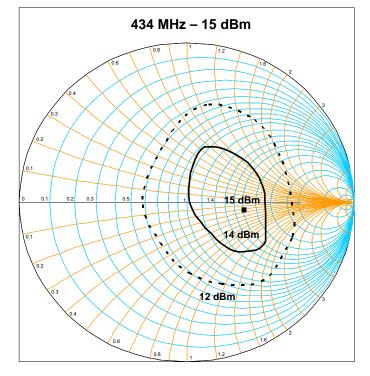

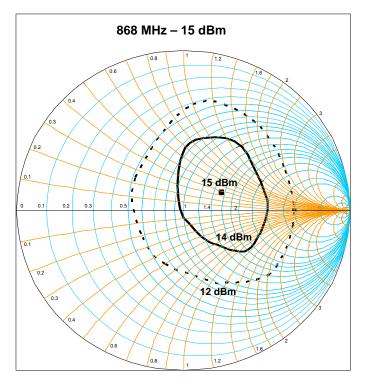

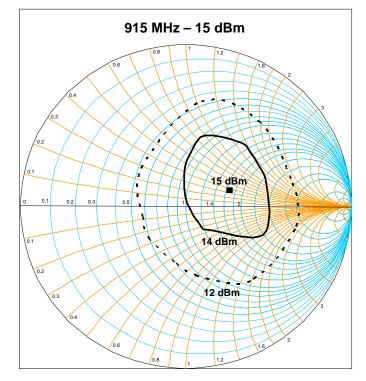

| 6.2   | Transmitter matching network                                | 31  |

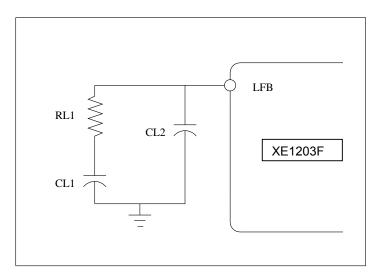

| 6.3   | VCO tank                                                    | 34  |

| 6.4   | Loop filter of the frequency synthesizer                    | 34  |

| 6.5   | frequency synthesizer Reference crystal                     |     |

| 7     | Revision History                                            | 36  |

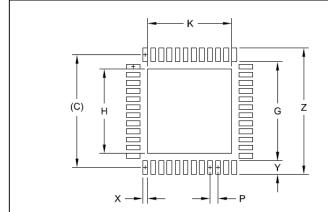

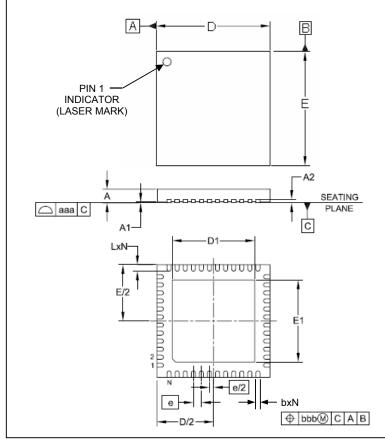

| 8     | Packaging information                                       | 37  |

SEMTECH

XE1203F

## **ADVANCED COMMUNICATION & SENSING PRODUCTS**

The XE1203F is a single-chip UHF transceiver integrated circuit intended for use as a low cost FSK transceiver to establish a frequency-agile, half-duplex, bi-directional RF link, with NRZ (non-return to zero) data coding. Barker encoder/decoder hardware can be activated to modulate/demodulate the transmitted signal to reduce the effects of fixed-frequency in-band interference. The device is available in a MLPQ48 package and is designed to provide a fully functional multi-channel FSK transceiver. It is intended for applications in the 868 MHz European band and the North American 902-928 MHz ISM band. The single chip transceiver operates down to 2.4V and provides a low power solution for battery-operated and power sensitive applications. The XE1203F is capable of operating data rates up to 152.3 kbit/s, making it ideally suited for applications where high data rates are required.

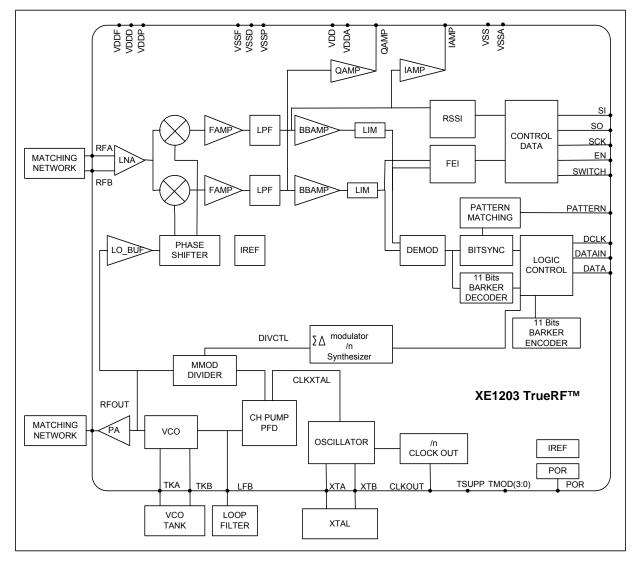

## 1 FUNCTIONAL BLOCK DIAGRAM

Figure 1: XE1203F Block Diagram

## 2 PIN DESCRIPTION

| PIN | NAME     | I/O    | Description                                                |  |

|-----|----------|--------|------------------------------------------------------------|--|

| 1   | N.C.     |        | Not connected                                              |  |

| 2   | N.C.     |        | Not connected                                              |  |

| 3   | N.C.     |        | Not connected                                              |  |

| 4   | VSSF     |        | Ground for the RF analog blocks                            |  |

| 5   | RFA      | IN     | RF input                                                   |  |

| 6   | RFB      | IN     | RF input                                                   |  |

| 7   | VSSP     |        | Ground for the RF power amplifier                          |  |

| 8   | VSSP     |        | Ground for the RF power amplifier                          |  |

| 9   | RFOUT    | OUT    | RF output                                                  |  |

| 10  | VDDP     |        | Power supply for the RF power amplifier                    |  |

| 11  | Test pin | IN     | Connected to ground                                        |  |

| 12  | VDDF     |        | Power supply for the RF analog blocks                      |  |

| 13  | VSSF     |        | Ground for the RF analog blocks                            |  |

| 14  | ТКА      | IN/OUT | VCO tank                                                   |  |

| 15  | ТКВ      | IN/OUT | VCO tank                                                   |  |

| 16  | VSSF     |        | Ground for the RF analog blocks                            |  |

| 17  | LFB      | IN/OUT | Loop filter of the PLL                                     |  |

| 18  | VDDD     |        | Power supply for the RF digital blocks                     |  |

| 19  | VSSD     |        | Ground for the RF digital blocks                           |  |

| 20  | Test pin | IN     | Connected to ground                                        |  |

| 21  | Test pin | IN     | Connected to ground                                        |  |

| 22  | N.C.     |        | Not connected                                              |  |

| 23  | Test pin | IN     | Connected to ground                                        |  |

| 24  | Test pin | IN     | Connected to ground                                        |  |

| 25  | VSSA     |        | Ground for the analog blocks                               |  |

| 26  | XTA      | IN/OUT | Crystal and input of external clock                        |  |

| 27  | VSSA     |        | Ground for the analog blocks                               |  |

| 28  | XTB      | IN/OUT | Crystal                                                    |  |

| 29  | VDDA     |        | Power supply for the analog blocks                         |  |

| 30  | QAMP     |        | Buffered Q output                                          |  |

| 31  | IAMP     |        | Buffered I output                                          |  |

| 32  | Test pin | IN     | Connected to ground                                        |  |

| 33  | Test pin | IN     | Connected to ground                                        |  |

| 34  | Test pin | IN     | Connected to ground                                        |  |

| 35  | EN       | IN     | 3-wire interface communication enable signal               |  |

| 36  | VDD      |        | Power supply for the digital blocks                        |  |

| 37  | SWITCH   | IN/OUT | Receiver or Transmitter mode selection                     |  |

| 38  | SO       | OUT    | Data output of the 3-wires interface                       |  |

| 39  | SI       | IN     | Data input of the 3-wires interface                        |  |

| 40  | SCK      | IN     |                                                            |  |

|     | -        |        | Input clock of the 3-wires interface                       |  |

| 41  | CLKOUT   | Out    | Output clock at quartz frequency divided by 4, 8, 16 or 32 |  |

| 42  | VSS      |        | Ground for the digital blocks                              |  |

| 43  | DCLK     | OUT    | Transmitter or Receiver clock                              |  |

| 44  | DATA     | IN/OUT | Transmitter input data or Receiver output data             |  |

| 45  | DATAIN   | IN     | Transmitter input data                                     |  |

| 46  | PATTERN  | Out    | Output of the pattern recognition block                    |  |

| 47  | N.C.     |        | Not connected                                              |  |

| 48  | N.C.     | 1      | Not connected                                              |  |

## **3 ELECTRICAL CHARACTERISTICS**

## 3.1 ABSOLUTE MAXIMUM OPERATING RANGES

Stresses above the values listed below in Table 1 may cause permanent device failure. Exposure to absolute maximum ratings for extended periods may affect device reliability.

| Symbol | Description          | Min. | Max. | Unit |

|--------|----------------------|------|------|------|

| VDDmax | Supply voltage       | -0.4 | 3.9  | V    |

| ML     | Receiver input level |      | -5   | dBm  |

| Tmax   | Storage temperature  | -55  | 125  | °C   |

Table 1: Absolute Maximum Ratings

The device is ESD sensitive and should be handled with precaution.

## 3.2 SPECIFICATIONS

## 3.2.1 Operating Range

| Symbol | Description                       | Min. | Max. | Unit |

|--------|-----------------------------------|------|------|------|

| VDD    | Supply voltage                    | 2.4  | 3.6  | V    |

| Т      | Temperature                       | -40  | 85   | °C   |

| CLop   | Load capacitance on digital ports | -    | 25   | pF   |

Table 2: Operating Range

## 3.2.2 Electrical Specifications

Table 3 below gives the electrical specifications of the transceiver under the following conditions: Supply Voltage VDD = 3.3V, temperature = 25 °C, 2-level FSK without pre-filtering, carrier frequency fc = 915 MHz, frequency deviation  $\Delta f$  = 55 kHz, bit rate BR = 4.8 kbit/s, Base band filter bandwidth BBW = 200 kHz, bit error rate BER = 0.1% (measured at the output of the bit synchronizer), LNA input and RF PA output matched to 50 $\Omega$ , environment as defined in Section 6, unless otherwise specified.

| Symbol | Description                        | Conditions                            | Min | Тур  | Max  | Unit |

|--------|------------------------------------|---------------------------------------|-----|------|------|------|

| IDDSL  | Supply current in sleep mode       |                                       | -   | 0.2  | 1    | uA   |

| IDDST  | Supply current in standby mode     | Quartz oscillator (39 MHz)<br>enabled | -   | 0.85 | 1.10 | mA   |

| IDDR   | Supply current in receiver mode    |                                       | -   | 14   | 17   | mA   |

| IDDT   | Supply current in transmitter mode | RFOP = 5 dBm                          | -   | 33   | 40   | mA   |

|        | (with optimum load-matching)       | RFOP = 15 dBm                         | -   | 62   | 75   | mA   |

| RFS    | RF sensitivity                     | BR = 4.8 kbit/s Mode A (*1)           | -   | -114 | -111 | dBm  |

|        |                                    | BR = 4.8 kbit/s Mode B (*1)           | -   | -101 | -98  | dBm  |

|        |                                    | BR = 32.7 kbit/s Mode A (*1)          | -   | -109 | -106 | dBm  |

|        |                                    | BR = 32.7 kbit/s Mode B (*1)          | -   | -96  | -93  | dBm  |

|        |                                    | ∆f = 200 kHz,<br>BBW = 600 kHz        |     |      |      |      |

|        |                                    | BR = 152.3 kbit/s Mode A (*1)         | -   | -101 | -98  | dBm  |

|        |                                    | BR = 152.3 kbit/s Mode B (*1)         | -   | -89  | -86  | dBm  |

| RFSB   | RF sensitivity with Barker         | BR = 1154 bit/s Mode A (*1)           | -   | -113 | -110 | dBm  |

|        | Coding/decoding enabled            | BR = 1154 bit/s Mode B(*1)            | -   | -100 | -97  | dBm  |

| FDA    | Frequency deviation                | Programmable                          | 1   | -    | 255  | kHz  |

| CCR    | Co-channel rejection               |                                       | -13 | -10  | -    | dBc  |

#### **ADVANCED COMMUNICATION & SENSING PRODUCTS** Conditions Symbol Description Min Тур Max Unit IIP3 Input intercept point $f_1 = f_{LO} + 1 MHz$ f<sub>2</sub> = f<sub>LO</sub> + 1.945 MHz -36 -33 dBm \_ Mode A (\*1) Mode B (\*1) -21 -18 dBm BBW Base band filter bandwidth DSB Programmable (\*2) 200 kHz 600 kHz --ACR Adjacent channel rejection $funw = f_{LO} + 650 \text{ kHz}$ 45 48 dBc Pw= - 108dBm, mode A (\*1) BR Bit rate Programmable 1.2 152.3 kbit/s RFOP RF output power Programmable RFOP1 -3 0 dBm \_ RFOP2 +2 +5 dBm \_ RFOP3 +7 +10 dBm RFOP4 +12 +15 dBm \_ FR 435 MHz Synthesizer frequency range Programmable 433 \_ 868 870 MHz Each range with its own \_ 902 MHz external components 928 TS\_TR Transmitter wake-up time 150 250 From oscillator enabled us TS RE Receiver Baseband wake-up time From oscillator enabled 0.5 0.8 ms -TS\_RSSI RSSI wake-up time From receiver enabled 1 ms -\_ TS\_RSSIM 0.5 **RSSI** measurement time ms TS OS Crystal oscillator wake-up time Fundamental 0.3 0.5 ms \_ 3<sup>rd</sup> overtone 2.5 ms TS\_FEI FEI wake-up time \_ \_ 2/BR ms TS\_SYNC\_AQ Time for synchronization of the Input power of -106 dBm 5 ms Barker decoder Data rate = 1154 bits/s Chip rate = 12.7 kcps From Rx enabled Fundamental or 3rd overtone **XTAL** Crystal oscillator frequency 39 MHz \_ \_ FSTEP Frequency synthesizer step Exact step is XTAL / 77 824 500 Hz \_ \_ VTHR RSSI equivalent input thresholds Mode A (\*1) Low range:VTHR1 -100 dBm VTHR2 -95 dBm VTHR3 -90 dBm High range:VTHR1 -85 dBm VTHR2 -80 dBm \_ VTHR3 -75 dBm --SPR Spurious emissions in Rx mode (\*4) -65 dBm SCK MHz Serial Clock frequency 1 % VIH Digital input level high (\*3) % VDD 75 \_ \_ VIL Digital input level low (\*3) % VDD 25 % \_ VOH Digital output level high % VDD 75 \_ \_ % VOL Digital output level low % VDD 25 % \_ -

#### Table 3: Electrical Specifications

Notes:

Mode A: High sensitivity mode; Mode B: High Linearity mode. As defined in Paragraph 4.1.1.

An intermediate bandwidth of 300 kHz can also be selected by using additional settings described in section 5.2.8.

Throughout this document, digital signal levels are named "high" or "1", and "low" or "0".

SPR strongly depends on the design of the application board and the choice of the external components.

© Semtech 2008

(\*1) (\*2) (\*3) (\*4)

Values down to -70 dBm can be achieved with careful design.

EMTECH

## 4 GENERAL DESCRIPTION

The XE1203F is a direct conversion (Zero-IF) half-duplex data transceiver. The circuit operates in three different ISM frequency bands (433 MHz, 868 MHz and 915 MHz) and uses 2-level FSK modulation/demodulation to provide a complete transmission link. It is capable of operating at data rates between 1.2 and 152.3 kbit/s, making it ideally suited for applications where high data rates are required. It also supports the Konnex standard where the bit rate is 32.7 kbit/s. The device includes dedicated Barker encoder/decoder hardware that may be activated to modulate/demodulate the transmitted signal to reduce in-band interferences.

The XE1203F is a highly programmable device – channel, bit rate, frequency deviation, output power, base band filter bandwidth, sensitivity vs. linearity, RSSI feature, and many other parameters – which makes it extremely flexible, to meet a large number of end user requirements.

The main functional blocks of the XE1203F are the receiver, the transmitter, the frequency synthesizer and some service blocks. The device also includes a series of configuration and status registers. In a typical application, the XE1203F is programmed by a microcontroller via the 3-wire serial bus SI, SO, SCK to write to and read from these registers.

The Receiver converts the incoming 2-level FSK modulated signal into a synchronized bit stream.

The Transmitter performs the modulation of the carrier by an input bit stream and the transmission of the modulated signal.

**The Frequency Synthesizer** generates the local oscillator (LO) signal for the receiver section as well as the continuous phase FSK modulated signal for the transmitter section.

The Service Blocks provide the internal voltage and current sources and provide all the necessary functions for the circuit to work properly.

**The Configuration Registers** are a set of variable-length registers that are used to store various settings to operate the XE1203F transceiver circuit. They are listed below in Table 4. Refer to Section 5.2 for the detailed descriptions of these registers. These registers are accessed in write or read mode through the 3-wire serial bus, as described in Section 5.1.

| Name         | Description                                                                            |  |

|--------------|----------------------------------------------------------------------------------------|--|

| ConfigSwitch | 1-bit data to switch between 2 sets of user-predefined SWParam Configuration Registers |  |

| RTParam      | Receiver and transmitter parameters                                                    |  |

| FSParam      | LO, Bitrate, Deviation and other frequency parameters                                  |  |

| SWParam      | 2 sets of user-predefined configuration registers                                      |  |

| DataOut      | Status register which can be read through the 3-wire serial interface                  |  |

| ADParam      | Additional parameters                                                                  |  |

| Pattern      | Reference pattern for the "pattern recognition" feature                                |  |

Table 4: Configuration Registers

<u>Naming convention</u>: throughout this document, each individual bit in a particular Configuration Register includes the name of this register followed by a bit identifier. For example, RTParam\_Band are the "Band" bits within the RTParam register.

The Digital Interface provides internal control signals for the whole circuit according to the configuration register settings.

## 4.1 THE RECEIVER SECTION

The receiver converts the incoming 2-level FSK modulated signal into a synchronized bit stream. The receiver is composed of a low-noise amplifier, two down-conversion mixers, two base band filters, two base band amplifiers, two limiters, a demodulator and a bit synchronizer. The bit synchronizer translates the output of the demodulator into a glitch-free bit stream available on the pin DATA. It also generates a synchronized clock, DCLK, which can be

used to sample the DATA signal without additional external signal processing. In addition, the receiver includes a digital Received Signal Strength Indicator (RSSI), a Frequency Error Indicator (FEI) that provides information about the local oscillator frequency error, and a pattern recognition function to detect preprogrammed sequences in the received serial data stream. Finally, a user-selectable Barker coding/decoding feature can be activated to spread the outgoing data with an 11-bit Barker code upon transmission and decode the incoming data upon reception by correlating the spread data with the 11-bit Barker code.

#### 4.1.1 LNA & Receiver modes

The LNA of the receiver has two programmable operation modes: the high sensitivity mode, Mode A, for reception of weak signals; and the high linearity mode, Modxe B, for strong signals. The operation mode is defined by the contents of the SWParam\_Rmode1 and SWParam\_Rmode2 Configuration Register bits.

- Mode A: High sensitivity mode, approximately 13dB better than in Mode B (see 3.2.2, RFS parameter)

- Mode B: High Linearity mode, IIP3 approximately 15dB higher than in Mode A (see 3.2.2, IIP3 parameter)

#### 4.1.2 Demodulation chain

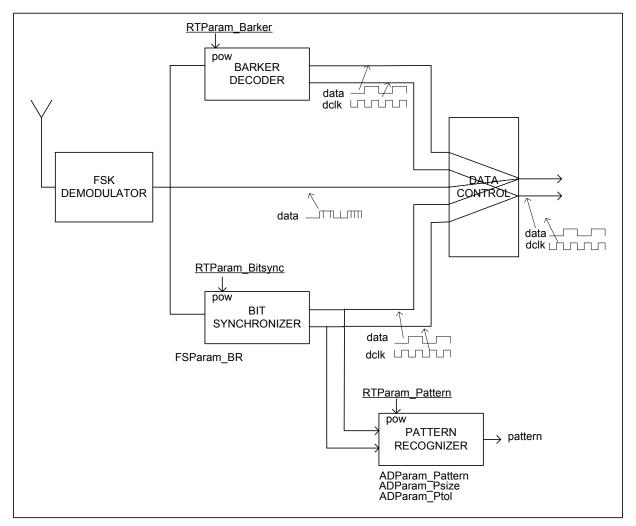

The demodulation chain consists of an FSK demodulator, bit synchronizer, Barker decoder and a Pattern Recognition block. Figure 2 below illustrates the interaction between each section of the demodulation chain.

Figure 2: Demodulation architecture

## 4.1.3 Demodulator

The demodulator provides a demodulated data stream from the received FSK modulated base band limited signals, I\_lim and Q\_lim. If the end-user application requires direct access to the output of the demodulator, then the RTParam\_Bitsync and RTParam\_Barker Configuration Register bits are set low (disabled). In this case the www.semtech.com

8

demodulator output is directly connected to the DATA pin and the DCLK pin is set to low. Otherwise, the demodulator output is processed by the bit synchronizer.

For correct operation of the demodulator the modulation index  $\beta$  of the input signal should meet the following condition:

$$\beta = \frac{2 \cdot \Delta f}{BR} \ge 2,$$

where  $\Delta f$  is the frequency deviation and BR the bit rate.

### 4.1.4 Bit synchronizer

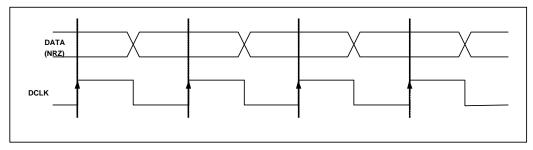

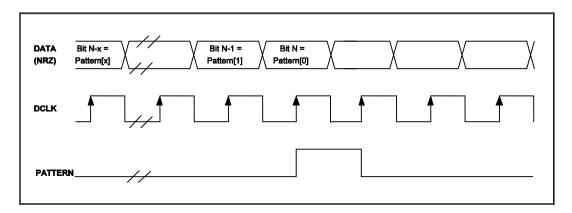

The raw output signal from the demodulator usually contains jitter and glitches. The bit synchronizer transforms the data output of the demodulator into a glitch-free bit stream available on the DATA pin and generates a synchronized clock DCLK to be used for sampling the DATA output (see Figure 3, below).

Figure 3: Bit synchronizer timing diagram.

For proper operation, in addition to the requirement for the modulation index defined in 4.1.3 above, the Bit Synchronizer must first receive three bytes of alternating logic value preamble, i.e. "0101" sequences. After this startup phase, the rising edge of DCLK signal is centered on the demodulated bit. Subsequent data transitions will preserve this centering.

This has two implications:

- If the Bit Rates of Transmitter and Receiver are known to be the same, the XE1203F will be able to receive an infinite unbalanced sequence (all "0s" or all "1s") with no restriction.

- If there is a difference in Bit Rate between Tx and Rx, the amount of adjacent bits at the same level that the BitSync can withstand can be estimated as:

Number of Bits =  $0.5 \cdot \frac{BR}{\Delta BR}$

This implies approximately 6 consecutive unbalanced bytes when the Bit Rate precision is 1%, which is easily achievable (crystal tolerance is in the range of 50 to 100 ppm). It is recommended that the bit rate accuracy be better than  $\pm 5\%$  (3% for Konnex mode operation).

The bit synchronizer is enabled when RTParam\_Bsync Configuration Register bit is high. If this bit set low, the bit synchronizer is disabled. In this case the output of the demodulator is directed to the DATA pin and the DCLK output is set to "0".

The received bit rate is defined by the value of the FSParam\_BR Configuration Register, and is calculated as follows:

Bit rate =  $\frac{152.34e3}{int(FSParam_BR(6:0))+1}$

where int(x) is the integer value of the unsigned binary representation of (x).

Note: for Konnex standard operations, the bit rate is fixed at 32.7 kbit/s. ADParam\_enable\_konnex should be set to a '1'.

#### 4.1.5 The DATA and DATAIN pins

The pin DATA is by default used by both the transmitter and the receiver sections. By default it is set as a bidirectional I/O pin. When in receive mode, demodulated data appears at DATA as an output signal. In transmit mode, the transmitted bit stream is applied to this pin as an input.

Some applications may require separate input and output pins for the transmitted and received data. In this case the user has to set the ADParam\_disable\_data\_bidir Configuration Register bit to '1'. As a result the DATA pin is set as an output only for the received data, while the transmit data is controlled via the DATAIN input pin.

#### 4.1.6 Pattern recognition block

When in receiver mode, this feature is activated by setting RTParam\_Pattern Configuration Register bit high. The demodulated data signal is compared with a pattern stored in the PATParam\_Pattern Configuration Register. The PATTERN output pin is driven by the output of this comparator and is synchronized by DCLK. It is set to high when a matching condition is detected, otherwise set to low. The PATTERN output is updated at the rising edge of DCLK. The number of bits used for comparison is defined in the ADParam\_Psize Configuration Register and the number of tolerated errors for the pattern recognition is defined in the ADParam\_Ptol register. Figure 4, below, illustrates the pattern matching process.

Figure 4: Pattern Matching Operation.

## 4.1.7 RSSI

When enabled, this function provides a Received Signal Strength Indication based on the signal at the output of the base-band filter. To enable the RSSI function, the RTParam\_RSSI Configuration Register bit should be set to "1". When enabled, the status of the RSSI in the DataOut\_RSSI register is a 2-bit word which can be read via the serial control interface. The content of the register is defined in Table 5, below, where  $V_{RFFIL}$  is the differential amplitude equivalent to the RF input signal with the receiver operated in A-mode. The thresholds,  $V_{TH}$  are the equivalent of the signal at the output of the base-band filter stage, divided by the signal gain.

| DataOut_RSSI | Description                    |

|--------------|--------------------------------|

| 0 0          | $V_{\text{RFFIL}} \leq VTHR1$  |

| 0 1          | $VTHR1 < V_{RFFIL} \leq VTHR2$ |

| 10           | $VTHR2 < V_{RFFIL} \leq VTHR3$ |

| 11           | VTHR3 < V <sub>RFFIL</sub>     |

#### Table 5 RSSI status description

Two possible ranges, each having a set of three  $V_{TH}$  threshold values, VTHR1, VTHR2, and VTHR3 (see 3.2.2 for actual values), are selected with the RTParam\_RSSIR Configuration Register bit. They provide an overall RSSI range of typically 25 dB.

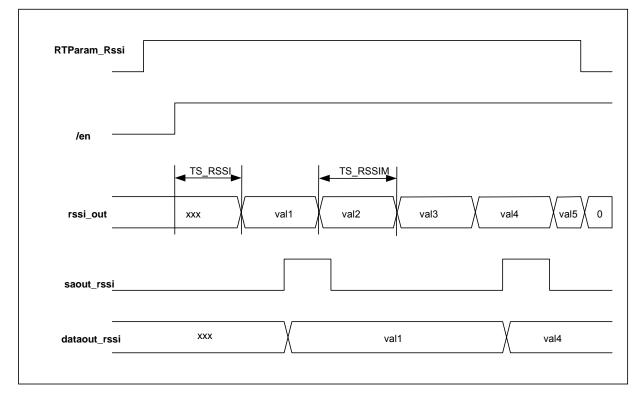

The timing diagram of an RSSI measurement is illustrated in the Figure 5 below. When the RSSI function has been activated, the signal strength is periodically measured and the result is stored in the register DataOut\_RSSI each time this DataOut\_RSSI register is read via the 3-wire serial interface. Note that TS\_RS is the wake-up time required after the function has been enabled to ensure that a valid reading of RSSI is obtained.

ADVANCED COMMUNICATION & SENSING PRODUCTS

Figure 5: RSSI measurement timing diagram

<u>Note on the Dataout RSSI update</u>: during a read sequence of the Dataout\_RSSI Status Register, the Saout\_rssi signal is generated internally as illustrated in the Figure 6 below. It can be seen the value of the Dataout\_RSSI Status Register is updated upon transmission of the bit A0 on the SI line. The maximum frequency of SCK during the read operation of the RSSI value is 100 kHz.

| SI (A(4)XA(3)XA(2)XA(1)XA | 0)                                                   |

|---------------------------|------------------------------------------------------|

| EN                        |                                                      |

| SO HZ                     | <u>Д(7)(0(6))(5)) D(4))(0(3))</u> D(2))(1)) D(0)/ нz |

| СК                        |                                                      |

| saout_rssi                |                                                      |

Figure 6: Generation of saout\_rssi

# SEMTECH

## ADVANCED COMMUNICATION & SENSING PRODUCTS

## 4.1.8 Frequency Error Indicator – FEI

When enabled this function provides an indication of the frequency error of the local oscillator compared with the received carrier frequency. For guaranteed operation of the FEI function the following two conditions should be met:

1) The modulation index,  $\beta$ , should meet the following condition:

$$\beta = \frac{2 \cdot \Delta f}{BR} \ge 2,$$

where:  $\Delta f$  = frequency deviation of the modulated input signal, BR = input data bit-rate.

2) The bandwidth of the baseband filter (BBW) must be greater than the sum of the frequency offset and the received peak signal bandwidth, as defined below:

$BBW > f_{OFFSET} + BW_{SIGNAL}$

where BBW is the baseband filter bandwidth defined by the RTParam\_BW register.  $f_{OFFSET}$  is the difference between the carrier frequency and the LO frequency, and BW<sub>SIGNAL</sub> is equal to  $\left(\frac{BR}{2} + \Delta f\right)$ .

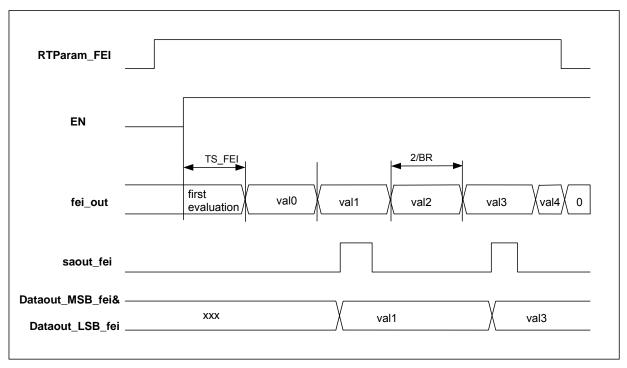

<u>Note on the timing for FEI measurement</u>: The timing diagram of the FEI measurement process is illustrated in Figure 7 below. As long as the FEI function remains enabled, the frequency error is continuously measured every 2/BR seconds, starting TS\_FEI (see Paragraph 3.2.2) after the FEI function is enabled. The measurement results are loaded into the status registers Dataout\_MSB\_fei and Dataout\_LSB\_fei each time the Dataout\_LSB\_fei register is read through the 3-wire serial interface. In the diagram below, Saout\_fei is generated internally during a read sequence from the "Dataout\_LSB\_fei " status register.

Figure 7: Timing diagram of the FEI measurement process

The maximum frequency of SCK during the FEI read operation is 100 kHz. When using the Konnex standard, the bit ADParam\_enable\_konnex Configuration Register must be set to '1'.

The frequency error can then be calculated by using the following formula:

Frequency error = (BR/8)\*int(Dataout FEI(11:0)),

where Dataout\_FEI(11:0) = Dataout\_MSB\_fei(3:0) + Dataout\_LSB\_fei(7:0), and int(x) is the integer value of the signed binary representation of x.

#### 4.2 THE TRANSMITTER SECTION

The Transmitter performs the modulation of the carrier by an input bit stream and the transmission of the modulated signal. Carrier modulation is achieved directly through the frequency synthesizer via a Sigma-Delta modulator. The frequency deviation and the bit-rate of the modulated carrier are programmable. An on-chip power amplifier then amplifies the RF signal. The output power can be programmed with 4 possible settings:

| RTParam_Tpow | Output power |

|--------------|--------------|

| 0 0          | RFOP1        |

| 0 1          | RFOP2        |

| 10           | RFOP3        |

| 11           | RFOP4        |

Table 6: Output power settings

### 4.2.1 Transmitter

The transmit data should be applied to DATA or DATAIN pins depending on the setting of the ADParam\_disable\_data\_bidir configuration bit. If the parameter is set to "1", then the DATAIN pin is used, otherwise the bidirectional pin DATA is used.

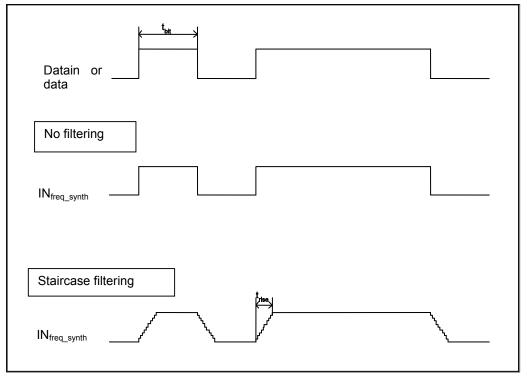

The modulating signal on DATA or DATAIN can be pre-processed before modulating the local oscillator to produce the outgoing FSK RF signal. This is the pre-filtering feature. The pre-filtering is selected by setting the RTParam\_Filter configuration bit to "1". When RTParam\_Filter is set to "1", the input baseband data is pre-filtered before being applied to the frequency synthesizer. This means that the rising and falling edge of each bit is linearly smoothed with a staircase transition. When RTParam\_Filter is set to "0", the input baseband data is applied directly to the frequency synthesizer without any pre-filtering function.

The two possible modulation methods are shown in Figure 8, where "datain" is the input bit stream from DATA or DATAIN pins.

Figure 8: Modulation with and without pre-filtering

The main characteristic of this pre-filtering function is the ratio between the rise/fall time to the bit duration,  $t_{rise}/t_{bit}$ . The value of this ratio can be programmed between two pre-defined values in the RTParam\_Stair configuration bit, as shown in the Table 7.

| RTParam_Stair | t <sub>rise</sub> /t <sub>bit</sub> |

|---------------|-------------------------------------|

| 0             | 10%                                 |

| 1             | 20%                                 |

Table 7: t<sub>rise</sub>/t<sub>bit</sub> ratio

When the pre-filtering function is enabled (RTParam\_Filter set to "1"), only the following bit rates and frequency deviations can be used:

| FSParam_Dev | Frequency deviation |

|-------------|---------------------|

| 00101000    | 40 kHz              |

| 00110111    | 55 kHz              |

| 01010000    | 80 kHz              |

| 10100000    | 160 kHz             |

| 11001000    | 200 kHz             |

| FSParam_Br | Bit rate (bit/s) |

|------------|------------------|

| 111110     | 1200             |

| 0111111    | 2400             |

| 0011111    | 4800             |

| 0001111    | 9600             |

| 0000111    | 19200            |

| 0000011    | 38400            |

| 0000001    | 76800            |

| others (*) | 153000           |

Table 8: Possible bit rates and frequency deviations when pre-filtering is enabled

(\*) For any programmed value of FSParam\_Br which is not in the Table 8 above, the data-rate is fixed to 153 kbit/s and the pre-filtering is applied as defined by the user.

If ADParam\_enable\_konex is set high, then the pre-filtering option is available for a bit rate of 32.7 kbit/s and one of the frequency deviations defined above.

#### 4.2.2 Barker encoder/decoder

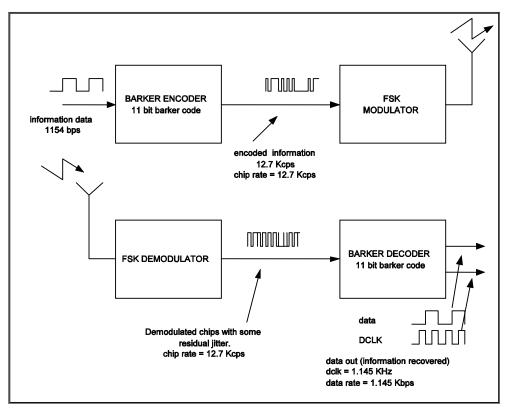

The Barker encoder/decoder hardware can be activated to modulate/demodulate the transmitted signal to reduce in-band interferences The Barker decoder provides an alternative to the bit synchronizer only for a **fixed data rate of 1154bits/s**. The Barker block is selected when the RTParam\_Barker configuration bit is set to "1". In transmission, the information data at a bit rate of 1154bits/s is spread using an 11-bit Barker code. The result is an encoded bit stream at 12.7 kilochips per second (kcps), which is applied to the frequency synthesizer. On the receiver part, the signal is demodulated using the FSK demodulator (at 12.7 kcps) and then fed into the Barker decoder to recover the un-encoded data at 1154 bit/s, together with a synchronized clock to sample it. Figure 8 on the next page, illustrates the coding/decoding process.

Figure 9: Barker Encoding and Decoding Channels.

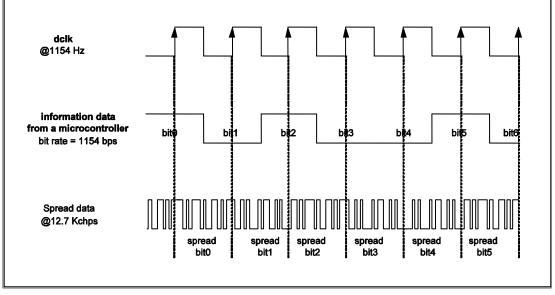

In receiver mode, the XE1203F provides a clock output, DCLK, to a microcontroller. The data can be sampled at the rising edge of the clock. When using the Barker decoding process, DCLK is used to detect the sync acquisition. If there is no valid data, DCLK remains high. The first falling edge of the clock means that the sync acquisition phase has been reached and that the output data is now available. This is illustrated below in Figure 10.

Figure 10: Data exchange during reception mode with Barker the feature enabled

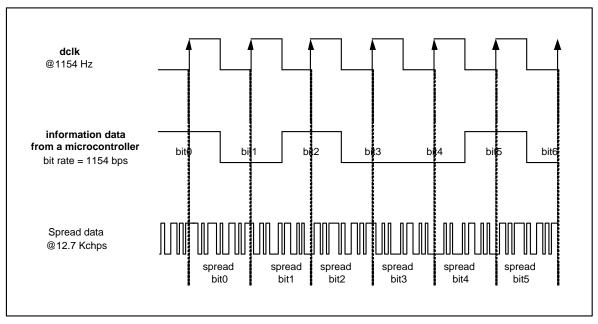

When using the Barker encoding in transmitter mode, the RTParam\_Barker parameter is set to "1" and the baseband data at 1154 bit/s is applied through either the DATA or DATAIN depending to the status of ADParam\_disable\_data\_bidir. The data is spread into an encoded chip stream at 12.7 kcps by the Barker encoder. This chip stream is directly applied to the frequency synthesizer without any pre-filtering.

When using the Barker coder/decoder feature in transmission mode, the DCLK pin is used to synchronize the data coming from a microcontroller or another source. This DCLK clock is generated by the XE1203F. At the falling edge of the each clock a new data bit (on DATA or DATAIN) should be supplied by the microcontroller or another source. This data is sampled by the XE1203F at the next rising edge of DCLK. It is then spread by using an 11-bit length Barker code. The Figure 11 shows the data exchange during the transmission mode when the Barker feature is enabled.

Figure 11: Data exchange during transmission mode with the Barker feature enabled

#### 4.3 THE FREQUENCY SYNTHESIZER

The Frequency Synthesizer generates the local oscillator (LO) signal for the receiver section as well as the continuous phase FSK (CPFSK) modulated signal for the transmitter section. The core of the synthesizer is implemented with a Sigma-Delta PLL architecture. The frequency is programmable with a minimum step-size of 500 Hz in the 433, 868 and 915 MHz frequency bands. This block includes a crystal oscillator which provides the frequency reference for the PLL. This reference frequency can also be used as a reference clock for the external microcontroller on the CLKOUT pin.

#### 4.3.1 Clock Output for external processor

A reference clock can be generated by XE1203F for use by an external microcontroller. The RTParam\_Clkout configuration bit determines the status of the CLKOUT pin. When set high CLKOUT is enabled, otherwise it's disabled. The output frequency at CLKOUT is defined by the value of the ADParam\_Clkfreq parameter. The output frequency at CLKOUT is the reference oscillator frequency divided by 4, 8, 16 or 32. With the reference oscillator frequency at 39 MHz this provides a reference clock at 9.75 MHz, 4.87 MHz, 2.44 MHz or 1.22 MHz, respectively. This clock signal is disabled in Sleep Mode.

## 5 SERIAL INTERFACE DEFINITION AND PRINCIPLES OF OPERATION

## 5.1 SERIAL CONTROL INTERFACE

A 3-wire bi-directional bus (SCK, SI, SO) is used to communicate with the XE1203F. SCK and SI are input signals supplied externally, for example by the microcontroller. The XE1203F configures the SO signal as an output pin during read operation, and it is tri-stated in other modes. The falling edge of the SCK signal is used to sample the SI pin to write data into the internal shift register of the XE1203F. The rising edge of the SCK signal is used to output data to SO pin by XE1203F, so the microcontroller should sample data at the falling edge of SCK.

The signal EN must be low during the whole write and read sequences. In write mode the content of the particular configuration register (see 5.2) is updated on the next rising edge of the EN signal. Before this rising edge, the new data is stored in temporary registers which do not affect the transceiver settings.

The timing diagram of a write sequence is illustrated in Figure 12 below. The sequence is initiated when a Start condition is detected, defined by the SI signal being set to "0" during one period of SCK. The next bit is a read/write (R/W) bit which should be "0" to indicate a write operation. The next 5 bits contain the address of the configuration/status registers A[4:0] to be accessed, MSB first (see 5.2). Then, the next 8 bits contain the data to be written into the register. The sequence ends with 2 stop bits set to "1". The data on SI should change on the rising edges of SCK, and is sampled on the falling edge of SCK. After the 2 stop bits, the data transfer is terminated. The SI line should be at "1" for at least one extra SCK clock cycle before a new write or read sequence can start. This mode of operation allows data to be written into multiple registers keeping the EN line low.

The maximum frequency of SCK is 1 MHz, except as defined above when reading the RSSI or FEI outputs, where the maximum frequency of SCK is limited to 100 kHz. The minimum clock pulse width is 0.5 us. Over the operating supply and temperature range, set-up and hold time for SI on the falling edge of SCK are 200 ns.

The register at address 0 is one bit long. When writing this register, the sequence described above is valid except that only one data bit is required instead of 8. However, if a single write procedure is used for all registers 8 data bits must be sent when writing at address 0, but only the MSB will be stored at address 0. The remaining 7 data bits must all be "1".

| si                | D(3) X D(2) X D(1) X D(0) Y |

|-------------------|-----------------------------|

| /en               |                             |

| so High impedance |                             |

Figure 12: Write sequence into configuration register

Figure 13 illustrates a write sequence at address zero.

© Semtech 2008

ADVANCED COMMUNICATION & SENSING PRODUCTS

| sck |                               |

|-----|-------------------------------|

| si  | A(4) A(3) A(2) A(1) A(0) D(7) |

| /en | 1                             |

|     |                               |

Figure 13: Write sequence into configuration register at address zero

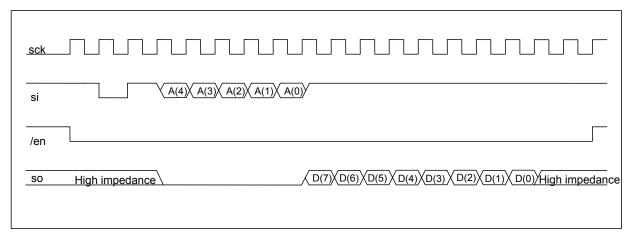

The time diagram of a read sequence is illustrated in Figure 14 below. The sequence is initiated when a Start condition is detected, defined by the SI signal being set to "0" during a period of SCK. The next bit is a read/write (R/W) bit which should be "1" to indicate a read operation. The next 5 bits are the address of the control register A[4:0] to be accessed, MSB first. The data from the register is then output on the SO pin. The data become valid at the rising edges of SCK and should be sampled at the falling edge of SCK. After this, the data transfer is terminated. The SI line must stay high for at least one extra SCK clock cycle to start a new write or read sequence. The maximum current drive on SO is 2 mA at a supply voltage of 2.7V and the maximum load is CLop, as defined in Paragraph 3.2.2.

When the serial interface is not used for read or write operations, both SCK and SI should be set to "1". Except when in read mode, SO is set to a high impedance mode.

#### Figure 14: Read sequence of configuration register

When reading the register at address zero, the timing diagram is illustrated in Figure 15.

| sck |                |           |                |      |                |

|-----|----------------|-----------|----------------|------|----------------|

| si  |                | A(4) A(3) | A(2) A(1) A(0) | у    |                |

| /en |                |           |                |      |                |

| SO  | High impedance |           |                | D(7) | High impedance |

Figure 15: Read sequence of configuration register at address 0

## 5.2 CONFIGURATION AND STATUS REGISTERS

The XE1203F has several operating modes and configuration parameters which can be programmed by the user or the application. In addition, status information may be read from the circuit. Some of the operating modes, the status information and the configuration parameters are stored in a series of internal Configuration and Status Registers that can be accessed by the microcontroller through the 3-wire serial interface.

| Name         | Description                                                                                  | Size<br>(bits) | Address<br>(binary format) |  |

|--------------|----------------------------------------------------------------------------------------------|----------------|----------------------------|--|

| ConfigSwitch | 1-bit data to switch between 2 sets of<br>user-predefined SWParam<br>Configuration Registers | 1 x 1          | 00000                      |  |

| RTParam      | Receiver and transmitter parameters                                                          | 2 x 8          | 00001 - 00010              |  |

| FSParam      | LO, Bitrate, Deviation and other frequency parameters                                        | 3 x 8          | 00011 - 00101              |  |

| SWParam      | 2 sets of user-predefined configuration registers                                            | 6 x 8          | 00110 - 01011              |  |

| DataOut      | Status register which can be read through the 3-wire serial interface                        | 2 x 8          | 01100 - 01101              |  |

| ADParam      | Additional parameters                                                                        | 5 x 8          | 01110 - 10010              |  |

| Pattern      | Reference pattern for the "pattern recognition" feature                                      | 4 x 8          | 10011 - 10110              |  |

There are seven variable Configuration and Status Registers, as listed below in Table 9.

Table 9: Configuration and Status Registers List

All the bits that are referred to as "reserved" in this section should be set to "0" during write operations.

#### 5.2.1 The ConfigSwitch Register

When operating the XE1203F, it might by useful to quickly switch between two pre-defined operating modes, to save time and traffic on the 3-wire serial interface bus. This may occur when the XE1203F is required to switch quickly between receive and transmit mode, when it has to operate on two different carrier frequencies, or when it has to switch between the high linearity mode B and the high sensitivity mode A. For that purpose, the five parameters stored in the SWParam Configuration Register are duplicated: the configuration set#1 and the configuration set #2.

EMTECH

Depending on the ConfigSwitch 1-bit Register or the input level at the SWITCH pin, the XE1203F transceiver will use either the SWParam configuration set#1 or the set #2. If the RTParam\_Switch\_ext configuration parameter is low, then the SWParam configuration set is selected by the ConfigSwitch parameter – set#1 if ConfigSwitch is "0", set#2 if ConfigSwitch is "1". If the RTParam\_Switch\_ext configuration parameter is high, then the SWParam configuration set is selected by the ConfigUration parameter is high, then the SWParam configuration set is selected by the SWITCH pin – set#1 if SWITCH is low, set#2 if SWITCH is high.

Table 10 below summarizes the chip configuration programming:

| ConfigSwitch<br>Register | SWITCH pin                                                               | RTParam_switch_ext configuration parameter | SWParam configuration set selected                                                              |

|--------------------------|--------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------|

| 0                        | SWITCH is an output:                                                     | 0                                          | Set #1:                                                                                         |

|                          | '1' in transmitter mode<br>'0' in the other modes                        |                                            | SWParam_mode_1<br>SWParam_Power_1<br>SWParam_Rmode_1<br>SWParam_t_delsig_in_1<br>SWParam_freq_1 |

| 1                        | SWITCH is an output:                                                     | 0                                          | Set #2:                                                                                         |

|                          | <ul><li>'1' in transmitter mode</li><li>'0' in the other modes</li></ul> |                                            | SWParam_mode_2<br>SWParam_Power_2<br>SWParam_Rmode_2<br>SWParam_t_delsig_in_2<br>SWParam_freq_2 |

| Х                        | 0                                                                        | 1                                          | Set #1:                                                                                         |

|                          |                                                                          |                                            | SWParam_mode_1<br>SWParam_Power_1<br>SWParam_Rmode_1<br>SWParam_t_delsig_in_1<br>SWParam_freq_1 |

| Х                        | 1                                                                        | 1                                          | Set #2:                                                                                         |

|                          |                                                                          |                                            | SWParam_mode_2<br>SWParam_Power_2<br>SWParam_Rmode_2<br>SWParam_t_delsig_in_2<br>SWParam_freq_2 |

Table 10: ConfigSwitch, SWITCH pin and SWParam Configuration Register

By default the configuration set#1 is used and register RTParam\_switch\_ext is set to '0'.

Note that a new value of the ConfigSwitch register or at the SWITCH pin should be modified when the EN signal is low. The actual switch to the newly selected set of SWParam register will be applied to the transceiver on the next rising edge of the EN signal.

## 5.2.2 RTParam Configuration Register

Receiver and transmitter parameters

| Name            | Bits | Address | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTParam_Bitsync | 7    | 00001   | Bit synchronizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 |      |         | 0 -> disabled<br>1 -> enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RTParam_Barker  | 6    | 00001   | BARKER coder/decoder:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |      |         | 0 -> disabled<br>1 -> enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RTParam_Rssi    | 5    | 00001   | RSSI function:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 |      |         | 0 -> disabled<br>1 -> enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RTParam_Rssir   | 4    | 00001   | RSSI range:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 |      |         | 0 -> low range (see 3.2.2)<br>1 -> high range (see 3.2.2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RTParam_Fei     | 3    | 00001   | FEI function:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |      |         | 0 -> disabled<br>1-> enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RTParam_BW      | 2    | 00001   | Baseband filter bandwidth (BBW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 |      |         | 0 -> 200 kHz (DSB)<br>1 -> 600 kHz (DSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RTParam_Osc     | 1    | 00001   | Reference frequency source:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 |      |         | 0 -> internal crystal oscillator<br>1 -> external source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RTParam_Clkout  | 0    | 00001   | CLKOUT - Reference frequency divided by 4,8,16,or 32:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |      |         | 0 -> disabled<br>1 -> enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RTParam_Stair   | 7    | 00010   | Transmitter pre-filter rise/fall time:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 |      |         | 0 -> 10% of bit duration<br>1 -> 20% of bit duration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RTParam_Filter  | 6    | 00010   | Pre-filtering of the bit stream in transmitter mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                 |      |         | 0 -> no filtering<br>1 -> filtering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                 |      |         | The filtering function is available only for the following bit rates<br>and frequency deviations:<br>FSPanam_Br = "1111110" -> BR = 1200 bit/s<br>FSPanam_Br = "0111111" -> BR = 2400 bit/s<br>FSPanam_Br = "0011111" -> BR = 4800 bit/s<br>FSPanam_Br = "0001111" -> BR = 9600 bit/s<br>FSPanam_Br = "0000111" -> BR = 19200 bit/s<br>FSPanam_Br = "0000011" -> BR = 19200 bit/s<br>FSPanam_Br = "000001" -> BR = 76800 bit/s<br>FSPanam_Br = "000001" -> BR = 76800 bit/s<br>FSPanam_Dev = "00101000" -> $\Delta f$ = 40 kHz<br>FSParam_Dev = "00110111" -> $\Delta f$ = 55 kHz<br>FSParam_Dev = "01010000" -> $\Delta f$ = 80 kHz<br>FSParam_Dev = "10100000" -> $\Delta f$ = 160 kHz<br>FSParam_Dev = "11001000" -> $\Delta f$ = 200 kHz |

| RTParam_Modul   | 5    | 00010   | Transmitter modulation:<br>0 -> enabled<br>1 -> disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Name               | Bits | Address | Description                                                                                                                                                                 |

|--------------------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTParam_IQAMP      | 4    | 00010   | I&Q amplifiers:                                                                                                                                                             |

|                    |      |         | 0 -> disabled<br>1 -> enabled                                                                                                                                               |

| RTParam_Switch_ext | 3    | 00010   | SWParam configuration set selection:                                                                                                                                        |

|                    |      |         | <ul> <li>0 -&gt; configuration set defined by ConfigSwitch. SWITCH is an output</li> <li>1 -&gt; configuration set defined by the pin SWITCH. SWITCH is an input</li> </ul> |

| RTParam_Pattern    | 2    | 00010   | Pattern recognition function:                                                                                                                                               |

|                    |      |         | 0 -> disabled<br>1 -> enabled                                                                                                                                               |

| RTParam_Band       | 1-0  | 00010   | Frequency band:                                                                                                                                                             |

|                    |      |         | 01 -> 433 – 435 MHz<br>10 -> 868 – 870 MHz<br>11 -> 902 – 928 MHz                                                                                                           |

Table 11: RTParam Configuration Register

## 5.2.3 FSParam Configuration Register

LO, Bitrate, Deviation and other frequency parameters

| Name               | Bits | Address | Description                                                                                                                 |

|--------------------|------|---------|-----------------------------------------------------------------------------------------------------------------------------|

| FSParam_Dev        | 7-0  | 00011   | Frequency deviation $\Delta f$ :                                                                                            |

|                    |      |         | $\Delta f = int(FSParan_Dev) * 1 kHz,$<br>where int(x) = integer value of the binary representation of x.                   |

|                    |      |         | Example:<br>00000001 -> Δf = 1 kHz<br>11111111 -> Δf = 255 kHz                                                              |

| FSParam_Change_Osr | 7    | 00100   | OSR Mode (Oversampling Rate mode):                                                                                          |

|                    |      |         | 0 -> default Bit rate defined by FSParam_Br<br>1 -> variable OSR                                                            |

| FSParam_Br         | 6-0  | 00100   | Bit rate (when "FSParam_Change_Osr" = "0"):                                                                                 |

|                    |      |         | Br = $152340/(int(FSParam_Br)+1)$ ,<br>where int(x) = integer value of the binary representation of x.                      |

|                    |      |         | Example:<br>0000000 -> Br = 152.34 kbit/s<br>1111111 -> Br = 1.19 kbit/s<br>0000100 -> Br = 32.7 kbit/s used in Konnex mode |

| FSParam_OSR        | 7-0  | 00101   | Define BR in terms of FSParam_BR and FS_Param_OSR:                                                                          |

|                    |      |         | FSParam_OSR = "00011101" and FSParam_Change_Osr =<br>'1' for Konnex standard                                                |

Table 12: FSParam Configuration Register

**XE1203F**

SEMTECH

ADVANCED COMMUNICATION & SENSING PRODUCTS

## 5.2.4 SWParam Configuration Register - switching parameters

The table below shows 2 sets of user-predefined configuration registers. Please refer to Section 5.2 for more details.

| Name            | Bits | Address | Description                                                                                                                                                           |

|-----------------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWParam_mode_1  | 7-6  | 00110   | Chip mode configuration set#1:                                                                                                                                        |

|                 |      |         | 00 -> Sleep mode<br>01 -> Stand by mode<br>10 -> Receiver mode<br>11 -> Transmitter mode                                                                              |

| SWParam_Power_1 | 5-4  | 00110   | Transmitter output power configuration set#1:                                                                                                                         |

|                 |      |         | 00 -> 0 dBm<br>01 -> 5 dBm<br>10 -> 10 dBm<br>11 -> 15 dBm                                                                                                            |

| SWParam_Rmode_1 | 3    | 00110   | Receiver Mode configuration set#1:                                                                                                                                    |

|                 |      |         | 0 -> Mode A (high sensitivity)<br>1 -> Mode B (high linearity)                                                                                                        |

| RESERVED        | 2-0  | 00110   | RESERVED                                                                                                                                                              |

| SWParam_Freq_1  | 7-0  | 00111   | LO frequency in 2's complement representation configuration set#1:                                                                                                    |

|                 | 7-0  | 01000   | 000 -> Flo = middle of the range<br>0XX-> Flo = higher than the middle of the range<br>1XX-> Flo = lower than the middle of the range<br>see Table 14 below           |

| SWParam_node_2  | 7-6  | 01001   | Chip mode configuration set#2:                                                                                                                                        |

|                 |      |         | 00 -> Sleep mode<br>01 -> Stand by mode<br>10 -> RX mode<br>11 -> TX mode                                                                                             |

| SWParam_Power_2 | 5-4  | 01001   | Transmitter output power configuration set#2:                                                                                                                         |

|                 |      |         | 00 -> 0 dBm<br>01 -> 5 dBm<br>10 -> 10 dBm<br>11 -> 15 dBm                                                                                                            |

| SWParam_Rmode_2 | 3    | 010001  | Receiver Mode configuration set#2:                                                                                                                                    |

|                 |      |         | 0 -> Mode A (high sensitivity)<br>1 -> Mode B (high linearity)                                                                                                        |

| RESERVED        | 2-0  | 01001   | RESERVED                                                                                                                                                              |