# 50 MHz to 1000 MHz Quadrature Demodulator

# AD8348

#### **FEATURES**

Integrated I/Q demodulator with IF VGA amplifier **Operating IF frequency 50 MHz to 1000 MHz** (3 dB IF BW of 500 MHz driven from  $R_s = 200 \Omega$ ) **Demodulation bandwidth 75 MHz** Linear-in-decibel AGC range 44 dB **Third-order intercept** IIP3 +28 dBm @ minimum gain (F<sub>IF</sub> = 380 MHz) IIP3 -8 dBm @ maximum gain (F<sub>IF</sub> = 380 MHz) **Quadrature demodulation accuracy** Phase accuracy 0.5° Amplitude balance 0.25 dB Noise figure 11 dB @ maximum gain (F<sub>IF</sub> = 380 MHz) LO input -10 dBm Single supply 2.7 V to 5.5 V Power-down mode Compact, 28-lead TSSOP package

#### APPLICATIONS

QAM/QPSK demodulator W-CDMA/CDMA/GSM/NADC Wireless local loop LMDS

#### **GENERAL DESCRIPTION**

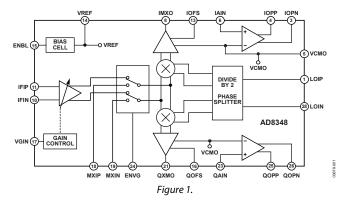

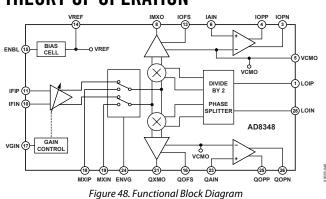

The AD8348 is a broadband quadrature demodulator with an integrated intermediate frequency (IF), variable gain amplifier (VGA), and integrated baseband amplifiers. It is suitable for use in communications receivers, performing quadrature demodulation from IF directly to baseband frequencies. The baseband amplifiers are designed to interface directly with dual-channel ADCs, such as the AD9201, AD9283, and AD9218, for digitizing and post-processing.

The IF input signal is fed into two Gilbert cell mixers through an X-AMP\* VGA. The IF VGA provides 44 dB of gain control. A precision gain control circuit sets a linear-in-decibel gain characteristic for the VGA and provides temperature compensation. The LO quadrature phase splitter employs a divide-by-2 frequency divider to achieve high quadrature accuracy and amplitude balance over the entire operating frequency range.

Optionally, the IF VGA can be disabled and bypassed. In this mode, the IF signal is applied directly to the quadrature mixer inputs via the MXIP and MXIN pins.

#### Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

#### FUNCTIONAL BLOCK DIAGRAM

Separate I- and Q-channel baseband amplifiers follow the baseband outputs of the mixers. The voltage applied to the VCMO pin sets the dc common-mode voltage level at the baseband outputs. Typically, VCMO is connected to the internal VREF voltage, but it can also be connected to an external voltage. This flexibility allows the user to maximize the input dynamic range to the ADC. Connecting a bypass capacitor at each offset compensation input (IOFS and QOFS) nulls dc offsets produced in the mixer. Offset compensation can be overridden by applying an external voltage at the offset compensation inputs.

The mixers' outputs are brought off-chip for optional filtering before final amplification. Inserting a channel selection filter before each baseband amplifier increases the baseband amplifiers' signal handling range by reducing the amplitude of high level, out-of-channel interferers before the baseband signal is fed into the I/Q baseband amplifiers. The single-ended mixer output is amplified and converted to a differential signal for driving ADCs.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2006 Analog Devices, Inc. All rights reserved.

## **TABLE OF CONTENTS**

| Features 1                                   |

|----------------------------------------------|

| Applications                                 |

| Functional Block Diagram 1                   |

| General Description                          |

| Revision History                             |

| Specifications                               |

| Absolute Maximum Ratings                     |

| ESD Caution                                  |

| Pin Configuration and Function Descriptions7 |

| Equivalent Circuits                          |

| Typical Performance Characteristics11        |

| VGA and Demodulator11                        |

| Demodulator Using MXIP and MXIN14            |

| Final Baseband Amplifiers                    |

| VGA/Demodulator and Baseband Amplifier16     |

| Theory of Operation                          |

| VGA                                          |

| Downconversion Mixers                        |

| Phase Splitter                               |

| I/Q Baseband Amplifiers                      |

|   | Enable                                    | 18 |

|---|-------------------------------------------|----|

|   | Baseband Offset Cancellation              | 18 |

| A | pplications                               | 20 |

|   | Basic Connections                         | 20 |

|   | Power Supply                              | 20 |

|   | Device Enable                             | 20 |

|   | VGA Enable                                | 20 |

|   | Gain Control                              | 20 |

|   | LO Inputs                                 | 20 |

|   | IF Inputs                                 | 20 |

|   | MX Inputs                                 | 20 |

|   | Baseband Outputs                          | 21 |

|   | Output DC Bias Level                      | 21 |

|   | Interfacing to Detector for AGC Operation | 21 |

|   | Baseband Filters                          | 22 |

|   | LO Generation                             | 23 |

|   | Evaluation Board                          | 23 |

| С | Outline Dimensions                        | 28 |

|   | Ordering Guide                            | 28 |

#### **REVISION HISTORY**

#### 4/06—Rev. 0 to Rev. A

| Updated Format                      | Universal |

|-------------------------------------|-----------|

| Changes to Specifications           |           |

| Changes to IF Inputs Section        |           |

| Changes to Evaluation Board Section |           |

| Changes to Table 6                  |           |

| Changes to Ordering Guide           |           |

|                                     |           |

#### 8/03—Revision 0: Initial Version

### **SPECIFICATIONS**

$V_S = 5 V$ ,  $T_A = 25^{\circ}$ C,  $F_{LO} = 380 MHz$ ,  $F_{IF} = 381 MHz$ ,  $P_{LO} = -10 dBm$ ,  $R_S (LO) = 50 \Omega$ ,  $R_S (IFIP and MXIP/MXIN) = 200 \Omega$ , unless otherwise noted.

Table 1.

| Parameter                             | Conditions                                                                 | Min  | Тур              | Max           | Unit          |

|---------------------------------------|----------------------------------------------------------------------------|------|------------------|---------------|---------------|

| OPERATING CONDITIONS                  |                                                                            |      |                  |               |               |

| LO Frequency Range                    | External input = $2 \times LO$ frequency                                   | 100  |                  | 2000          | MHz           |

| IF Frequency Range                    |                                                                            | 50   |                  | 1000          | MHz           |

| Baseband Bandwidth                    |                                                                            |      | 75               |               | MHz           |

| LO Input Level                        | 50 Ω source                                                                | -12  | -10              | 0             | dBm           |

| V <sub>SUPPLY</sub> (V <sub>S</sub> ) |                                                                            | 2.7  |                  | 5.5           | V             |

| Temperature Range                     |                                                                            | -40  |                  | +85           | °C            |

| IF FRONT END WITH VGA                 | IFIP to IMXO (QMXO),                                                       |      |                  |               |               |

|                                       | ENVG = 5 V, IMXO/QMXO load = 1.5 k $\Omega$                                |      |                  |               |               |

| Input Impedance                       | Measured differentially across MXIP/MXIN                                   |      | 200  1.1         |               | Ω  pF         |

| Gain Control Range                    |                                                                            |      | 44               |               | dB            |

| Maximum Conversion Voltage Gain       | VGIN = 0.2 V (maximum voltage gain)                                        |      | 25.5             |               | dB            |

| Minimum Conversion Voltage Gain       | VGIN = 1.2 V (minimum voltage gain)                                        |      | -18.5            |               | dB            |

| 3 dB Bandwidth                        |                                                                            |      | 500              |               | MHz           |

| Gain Control Linearity                | VGIN = 0.4 V (+21 dB) to 1.1 V (-14 dB)                                    |      | ±0.5             |               | dB            |

| IF Gain Flatness                      | $F_{\rm IF} = 380 \text{ MHz} \pm 5\% \text{ (VGIN} = 1.2 \text{ V)}$      |      | 0.1              |               | dB p-p        |

|                                       | $F_{IF} = 900 \text{ MHz} \pm 5\% \text{ (VGIN} = 1.2 \text{ V)}$          |      | 1.3              |               | dB p-p        |

| Input 1 dB Compression Point (P1dB)   | VGIN = 0.2 V (maximum gain)                                                |      | -22              |               | dBm           |

| input i ub compression romt (r iub)   | VGIN = 0.2 V (maximum gain)<br>VGIN = 1.2 V (maximum gain)                 |      | +13              |               | dBm           |

| Second-Order Input Intercept (IIP2)   | IF1 = 385 MHz, IF2 = 386 MHz                                               |      | 715              |               | ubiii         |

| Second-Order input intercept (IF2)    | +3 dBm each tone from 200 $\Omega$ source,                                 |      | 65               |               | dBm           |

|                                       |                                                                            |      | 05               |               | UDITI         |

|                                       | VGIN = 1.2 V (minimum gain)<br>-42 dBm each tone from 200 $\Omega$ source, |      | 18               |               | dBm           |

|                                       |                                                                            |      | 10               |               | авт           |

| Third Order Inc. + Intersect (IID2)   | VGIN = 0.2 V (maximum gain)                                                |      |                  |               |               |

| Third-Order Input Intercept (IIP3)    | IF1 = 381 MHz, IF2 = 381.02 MHz                                            |      | 20               |               | 10            |

|                                       | Each tone 10 dB below P1dB from 200 $\Omega$ source,                       |      | 28               |               | dBm           |

|                                       | VGIN = 1.2 V (minimum gain)                                                |      |                  |               |               |

|                                       | Each tone 10 dB below P1dB from                                            |      | -8               |               | dBm           |

|                                       | $200 \Omega$ source,                                                       |      | -0               |               | ubiii         |

|                                       | VGIN = 0.2 V (maximum gain)                                                |      |                  |               |               |

| LO Leakage                            | Measured at IFIP, IFIN                                                     |      | -80              |               | dBm           |

| LO Leakage                            | Measured at IMXO/QMXO (LO = 50 MHz)                                        |      | 60               |               | dBm           |

| Demodulation Bandwidth                | Small signal 3 dB bandwidth                                                |      | 00<br>75         |               | MHz           |

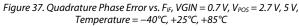

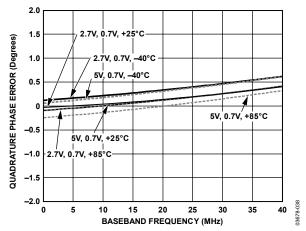

| Quadrature Phase Error <sup>1</sup>   | LO = 380  MHz (LOIP/LOIN 760  MHz)                                         | -0.7 | ±0.1             | +0.7          | Degree        |

| Quadrature Phase Life                 |                                                                            | -0.7 |                  | τ <b>0</b> .7 |               |

|                                       | vs. temperature<br>vs. baseband frequency (dc to 30 MHz)                   |      | -0.0032<br>+0.01 |               | °/°C<br>°/MHz |

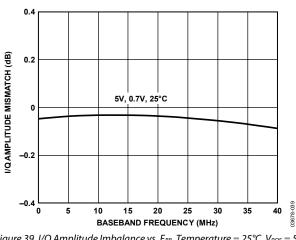

| 1/O Amplitudo Impoloncol              | vs. baseband nequency (dc to so minz)                                      | -0.3 | +0.01<br>±0.05   | 102           | dB            |

| I/Q Amplitude Imbalance <sup>1</sup>  |                                                                            | -0.5 |                  | +0.3          |               |

|                                       | vs. temperature                                                            |      | 0                |               | dB/°C         |

| Noico Eiguro (Double Sidebord)        | vs. baseband frequency (dc to 30 MHz)                                      |      | ±0.0125          |               | dB            |

| Noise Figure (Double Sideband)        | Maximum gain, from 200 Ω source,<br>$F_{\rm IF} = 380  \rm MHz$            |      | 10.75            |               | dB            |

| Mixer Output Impedance                |                                                                            |      | 40               |               | Ω             |

|                                       | Shunt from IMYO ONAYO to VCMO                                              |      | U                | 10            |               |

| Capacitive Load                       | Shunt from IMXO, QMXO to VCMO                                              | 0    | 1 Г              | 10            | pF            |

| Resistive Load                        | Shunt from IMXO, QMXO to VCMO                                              | 200  | 1.5              |               | kΩ            |

| Mixer Peak Output Current             |                                                                            |      | 2.5              |               | mA            |

| Parameter                                                      | Conditions                                                                                        | Min       | Тур      | Max  | Unit    |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------|----------|------|---------|

| IF FRONT END WITHOUT VGA                                       | From MXIP, MXIN to IMXO (QMXO),                                                                   |           |          |      |         |

|                                                                | ENVG = 0 V, IMXO/QMXO load = $1.5 \text{ k}\Omega$                                                |           |          |      |         |

| Input Impedance                                                | Measured differentially across MXIP/MXIN                                                          |           | 200  1.5 |      | Ω∥pF    |

| Conversion voltage Gain                                        |                                                                                                   |           | 10.5     |      | dB      |

| 3 dB Output Bandwidth                                          |                                                                                                   |           | 75       |      | MHz     |

| IF Gain Flatness                                               | $F_{IF} = 380 \text{ MHZ} \pm 5\%$                                                                |           | 0.1      |      | dB p-p  |

|                                                                | $F_{IF} = 900 \text{ MHZ} \pm 5\%$                                                                |           | 0.15     |      | dB p-p  |

| Input 1 dB Compression Point (P1dB)                            |                                                                                                   |           | -4       |      | dBm     |

| Third-Order Input Intercept (IIP3)                             | IF1 = 381 MHz, IF2 = 381.02 MHz                                                                   |           | 14       |      | dBm     |

|                                                                | Each tone 10 dB below P1dB from 200 $\Omega$ source                                               |           |          |      |         |

| LO Leakage                                                     | Measured at MXIP/MXIN                                                                             |           | -70      |      | dBm     |

|                                                                | Measured at IMXO, QMXO                                                                            |           | -60      |      | dBm     |

| Demodulation Bandwidth                                         | Small signal 3 dB bandwidth                                                                       |           | 75       |      | MHz     |

| Quadrature Phase Error                                         | LO = 380 MHz (LOIP/LOIN 760 MHz, single-ended)                                                    | -2        | ±0.5     | +2   | Degrees |

| I/Q Amplitude Imbalance                                        |                                                                                                   |           | 0.25     |      | dB      |

| Noise Figure (Double Sideband)                                 | From 200 $\Omega$ source, F <sub>IF</sub> = 380 MHz                                               |           | 21       |      | dB      |

| I/Q BASEBAND AMPLIFIER                                         | From IAIN to IOPP/IOPN and QAIN to QOPP/<br>QOPN, $R_{LOAD} = 2 k\Omega$ , single-ended to ground |           |          |      |         |

| Gain                                                           |                                                                                                   |           | 20       |      | dB      |

| Bandwidth                                                      | 10 pF differential load                                                                           |           | 125      |      | MHz     |

| Output DC Offset (Differential)                                | LO leakage offset corrected using 500 pF capacitor on IOFS, QOFS (VIOPP – VIOPN)                  | -50       | ±12      | +50  | mV      |

| Output Common-Mode Offset                                      | $(V_{IOPP} + V_{IOPN})/2 - VCMO$                                                                  | -75       | ±35      | +75  | mV      |

| Group Delay Flatness                                           | 0 MHz to 50 MHz                                                                                   |           | 3        |      | ns p-p  |

| Input-Referred Noise Voltage                                   | Frequency = 1 MHz                                                                                 |           | 8        |      | nV/√Hz  |

| Output Swing Limit (Upper)                                     |                                                                                                   | $V_s - 1$ |          |      | V       |

| Output Swing Limit (Lower)                                     |                                                                                                   |           |          | 0.5  | V       |

| Peak Output Current                                            |                                                                                                   |           | 1        |      | mA      |

| Input Impedance                                                |                                                                                                   |           | 50  1    |      | kΩ∥pF   |

| Input Bias Current                                             |                                                                                                   |           | 2        |      | μA      |

| RESPONSE FROM IF AND MX INPUTS TO<br>BASEBAND AMPLIFIER OUTPUT | IMXO and QMXO connected directly to<br>IAIN and QAIN, respectively                                |           |          |      |         |

| Gain                                                           | From MXIP/MXIN                                                                                    |           | 30.5     |      | dB      |

|                                                                | From IFIP/IFIN, VGIN = 0.2 V                                                                      |           | 45.5     |      | dB      |

|                                                                | From IFIP/IFIN, VGIN = 1.2 V                                                                      |           | 1.5      |      | dB      |

| CONTROL INPUT/OUTPUTS                                          |                                                                                                   |           |          |      |         |

| VCMO Input Range                                               | $V_s = 5 V$                                                                                       | 0.5       | 1        | 4    | v       |

|                                                                | Vs = 2.7 V                                                                                        | 0.5       | 1        | 1.7  | V       |

| VREF Output Voltage                                            |                                                                                                   | 0.95      | 1        | 1.05 | v       |

| Gain Control Voltage Range                                     | VGIN                                                                                              | 0.2       |          | 1.2  | V       |

| Gain Slope                                                     |                                                                                                   | -55       | -50      | -45  | dB/V    |

| Gain Intercept                                                 | Linear extrapolation back to theoretical gain at VGIN = 0 V                                       | 55        | 61       | 67   | dB      |

| Gain Control Input Bias Current                                |                                                                                                   |           | 1        |      | μA      |

| LO INPUTS                                                      |                                                                                                   |           |          |      | ·       |

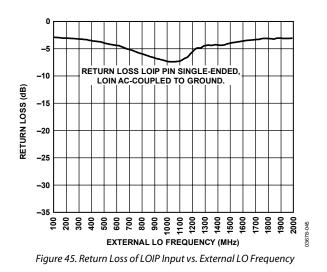

| LOIP Input Return Loss                                         | LOIN ac-coupled to ground<br>(760 MHz applied to LOIP)                                            |           | -6       |      | dB      |

| Parameter           | Conditions                                                             | Min    | Тур  | Max | Unit |

|---------------------|------------------------------------------------------------------------|--------|------|-----|------|

| POWER-UP CONTROL    |                                                                        |        |      |     |      |

| ENBL Threshold Low  | Low = standby                                                          | 0      | Vs/2 | 1   | V    |

| ENBL Threshold High | High = enable                                                          | Vs - 1 | Vs/2 | Vs  | V    |

| Input Bias Current  |                                                                        |        | 2    |     | μA   |

| Power-Up Time       | Time for final baseband amplifiers to be within 90% of final amplitude |        | 45   |     | μs   |

| Power-Down Time     | Time for supply current to be <10% of enabled value                    |        | 700  |     | ns   |

| POWER SUPPLIES      | VPOS1, VPOS2, VPOS3                                                    |        |      |     |      |

| Voltage             |                                                                        | 2.7    |      | 5.5 | V    |

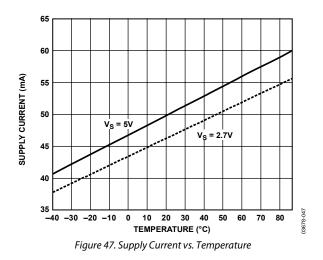

| Current (Enabled)   | $V_S = 5 V, V_{ENBL} = 5 V$                                            | 38     | 48   | 58  | mA   |

| Current (Standby)   | $V_{S} = 5 V, V_{ENBL} = 5 V$ $V_{S} = 5 V, V_{ENBL} = 0 V$            |        | 75   |     | μΑ   |

$^{1}$  These parameters are guaranteed but not tested in production. Limits are  $\pm 6\,\Sigma$  from the mean.

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| 1 abic 2.                                  |                    |

|--------------------------------------------|--------------------|

| Parameter                                  | Rating             |

| Supply Voltage on VPOS1, VPOS2, VPOS3 Pins | 5.5 V              |

| LO Input Power                             | 10 dBm (re: 50 Ω)  |

| IF Input Power                             | 18 dBm (re: 200 Ω) |

| Internal Power Dissipation                 | 450 mW             |

| θ <sub>JA</sub>                            | 68°C/W             |

| Maximum Junction Temperature               | 150°C              |

| Operating Temperature Range                | –40°C to +85°C     |

| Storage Temperature Range                  | –65°C to +125°C    |

| Lead Temperature (Soldering, 60 sec)       | 300°C              |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

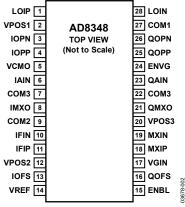

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. 28-Lead TSSOP Pin Configuration

#### Table 3. Pin Function Descriptions—28-Lead TSSOP

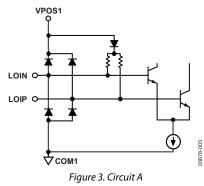

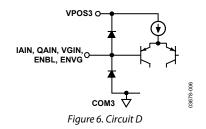

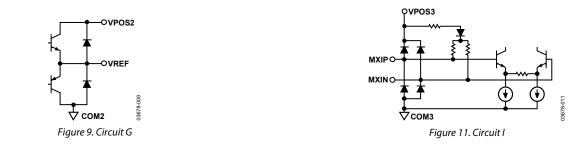

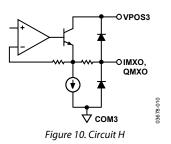

| Pin No.      | Mnemonic                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Equivalent<br>Circuit |

|--------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

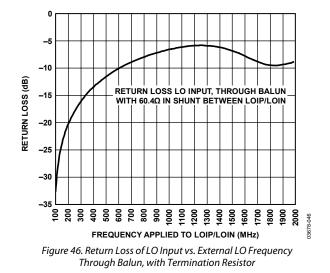

| 1, 28        | LOIP, LOIN                | LO Inputs. For optimum performance, these inputs should be ac-coupled and driven differentially. Differential drive from single-ended sources can be achieved via a balun. To obtain a broadband 50 $\Omega$ input impedance, connect a 60.4 $\Omega$ shunt resistor between LOIP and LOIN. Typical input drive level is equal to $-10$ dBm.                                                                                                                                                                                                                                          | A                     |

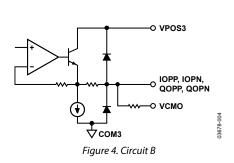

| 2, 12, 20    | VPOS1, VPOS2,<br>VPOS3    | Positive Supply for LO, IF, and Biasing and Baseband Sections, Respectively. These pins should be decoupled with 0.1 $\mu$ F and 100 pF capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                   |                       |

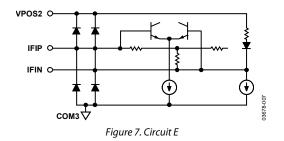

| 3, 4, 25, 26 | IOPN, IOPP,<br>QOPP, QOPN | I- and Q-Channel Differential Baseband Outputs. Typical output swing is equal to 2 V p-p differential. The dc common-mode voltage level on these pins is set by the voltage on VCMO.                                                                                                                                                                                                                                                                                                                                                                                                  | В                     |

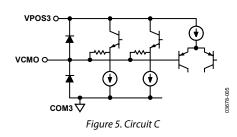

| 5            | VCMO                      | Baseband DC Common-Mode Voltage. The voltage applied to this pin sets the dc common-mode levels for all the baseband outputs and inputs (IMXO, QMXO, IOPP, IOPN, QOPP, QOPN, IAIN, and QAIN). This pin can be connected either to VREF or to a reference voltage from another device (typically an ADC).                                                                                                                                                                                                                                                                              | с                     |

| 6, 23        | IAIN, QAIN                | I- and Q-Channel Baseband Amplifier Inputs. The single-ended signals on these pins are referenced to VCMO and must have a dc bias equal to the dc voltage on the VCMO pin. If IMXO (QMXO) is dc-coupled to IAIN (QAIN), biasing will be provided by IMXO (QMXO). If an ac-coupled filter is placed between IMXO and IAIN, these pins can be biased from the source driving VCMO through a 1 k $\alpha$ resistor. The gain from IAIN/QAIN to the differential outputs (IOPP/IOPN and QOPP/QOPN) is 20 dB.                                                                              | D                     |

| 7, 22        | COM3                      | Ground for Biasing and Baseband Sections.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                       |

| 8, 21        | ΙΜΧΟ, QΜΧΟ                | I- and Q-Channel Mixer Baseband Outputs. These are low impedance (40 $\Omega$ ) outputs whose bias levels are set by the voltage applied to the VCMO pin. These pins are typically connected to IAIN and QAIN, respectively, either directly or through a filter. Each output can drive a maximum current of 2.5 mA.                                                                                                                                                                                                                                                                  | н                     |

| 9            | COM2                      | IF Section Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                       |

| 10, 11       | IFIN, IFIP                | IF Inputs. IFIN should be ac-coupled to ground. The single-ended IF input signal should be ac-coupled into IFIP. The nominal differential input impedance of these pins is 200 $\Omega$ . For a broadband 50 $\Omega$ input impedance, a minimum-loss L pad should be used; R <sub>SERIES</sub> = 174 $\Omega$ , R <sub>SHUNT</sub> = 57.6 $\Omega$ . This provides a 200 $\Omega$ source impedance to the IF input. However, the AD8348 does not necessarily require a 200 $\Omega$ source impedance, and a single shunt 66.7 $\Omega$ resistor can be placed between IFIP and IFIN. | E                     |

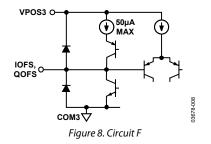

| 13, 16       | IOFS, QOFS                | I- and Q-Channel Offset Nulling Inputs. DC offsets on the I-channel mixer output (IMXO) can be nulled by connecting a 0.1 $\mu$ F capacitor from IOFS to ground. Driving IOFS with a fixed voltage (typically a DAC calibrated such that the offset at IOPP/IOPN is nulled) can extend the operating frequency range to include dc. The QOFS pin can likewise be used to null offsets on the Q-channel mixer output (QMXO).                                                                                                                                                           | F                     |

| 14           | VREF                      | Reference Voltage Output. This output voltage (1 V) is the main bias level for the device and can be used to externally bias the inputs and outputs of the baseband amplifiers. The typical maximum drive current for this output is 2 mA.                                                                                                                                                                                                                                                                                                                                            | G                     |

| Pin No. | Mnemonic   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Equivalent<br>Circuit |

|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 15      | ENBL       | Chip Enable Input. Active high. Threshold is equal to V <sub>s</sub> /2.                                                                                                                                                                                                                                                                                                                                                                                                                                      | D                     |

| 17      | VGIN       | Gain Control Input. The voltage on this pin controls the gain on the IF VGA. The gain control voltage range is from 0.2 V to 1.2 V and corresponds to a conversion gain range from +25.5 dB to -18.5 dB. This is the gain to the output of the mixers (that is, IMXO and QMXO). There is an additional 20 dB of fixed gain in the final baseband amplifiers (IAIN to IOPP/IOPN and QAIN to QOPP/QOPN). Note that the gain control function has a negative sense (that is, increasing voltage decreases gain). | D                     |

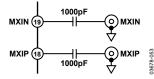

| 18, 19  | MXIP, MXIN | Auxiliary Mixer Inputs. If ENVG is low, the IFIP and IFIN inputs are disabled and MXIP and MXIN are enabled, allowing the VGA to be bypassed. The auxiliary mixer inputs are fully differential inputs that should be ac-coupled to the signal source.                                                                                                                                                                                                                                                        | I                     |

| 24      | ENVG       | Active High VGA Enable. When ENVG is high, IFIP and IFIN inputs are enabled and MXIP and MXIN inputs are disabled. When ENVG is low, MXIP and MXIN inputs are enabled and IFIP and IFIN inputs are disabled.                                                                                                                                                                                                                                                                                                  | D                     |

| 27      | COM1       | LO Section Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |

### **EQUIVALENT CIRCUITS**

## TYPICAL PERFORMANCE CHARACTERISTICS

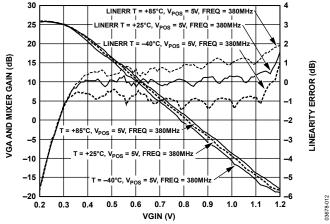

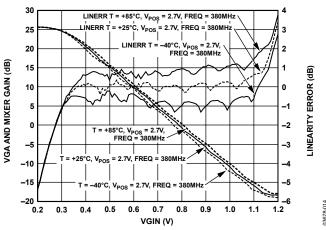

Figure 12. Mixer Gain and Linearity Error vs. VGIN,  $V_{POS} = 5 V$ ,  $F_{IF} = 380 \text{ MHz}$ ,  $F_{BB} = 1 \text{ MHz}$ , Temperature  $= -40^{\circ}\text{C}$ ,  $+25^{\circ}\text{C}$ ,  $+85^{\circ}\text{C}$

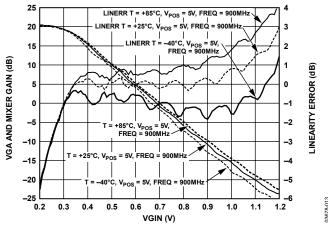

Figure 13. Mixer Gain and Linearity Error vs. VGIN,  $V_{POS} = 5 V$ ,  $F_{IF} = 900 MHz$ ,  $F_{BB} = 1 MHz$ , Temperature =  $-40^{\circ}$ C,  $+25^{\circ}$ C,  $+85^{\circ}$ C

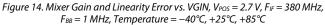

Figure 15. Mixer Gain and Linearity Error vs. VGIN,  $V_{POS} = 2.7 V$ ,  $F_{IF} = 900 MHz$ ,  $F_{BB} = 1 MHz$ , Temperature  $= -40^{\circ}C$ ,  $+25^{\circ}C$ ,  $+85^{\circ}C$

Rev. A | Page 11 of 28

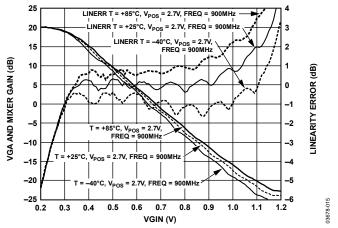

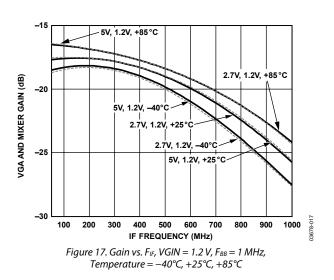

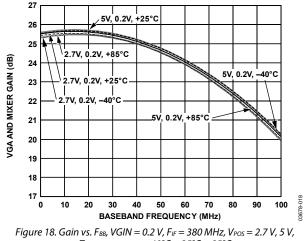

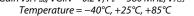

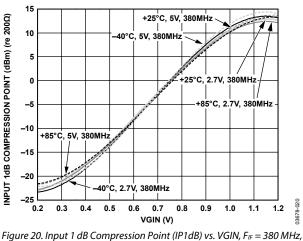

Temperature =  $-40^{\circ}$ C,  $+25^{\circ}$ C,  $+85^{\circ}$ C

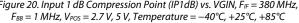

Figure 21. Input 1 dB Compression Point (IP1dB) vs. VGIN, F<sub>I</sub> = 900 MHz, F<sub>BB</sub> = 1 MHz, V<sub>POS</sub> = 2.7 V, 5 V, Temperature = −40°C, +25°C, +85°C

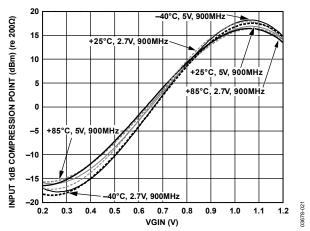

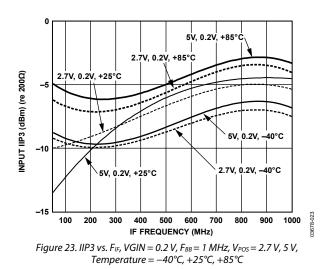

Figure 22. IIP3 vs.  $F_{IF}$ , VGIN = 1.2 V,  $F_{BB} = 1 MHz$ ,  $V_{POS} = 2.7 V$ , 5 V, Temperature =  $-40^{\circ}C$ ,  $+25^{\circ}C$ ,  $+85^{\circ}C$ , Tone Spacing = 20 kHz

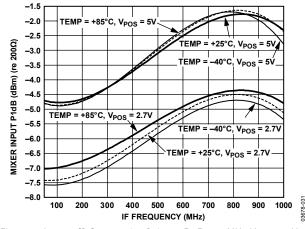

Rev. A | Page 13 of 28

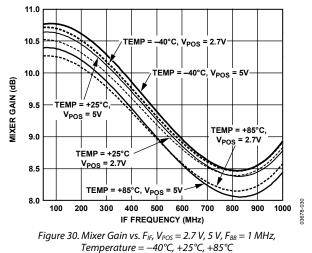

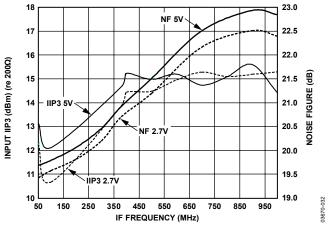

#### **DEMODULATOR USING MXIP AND MXIN**

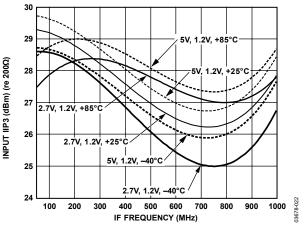

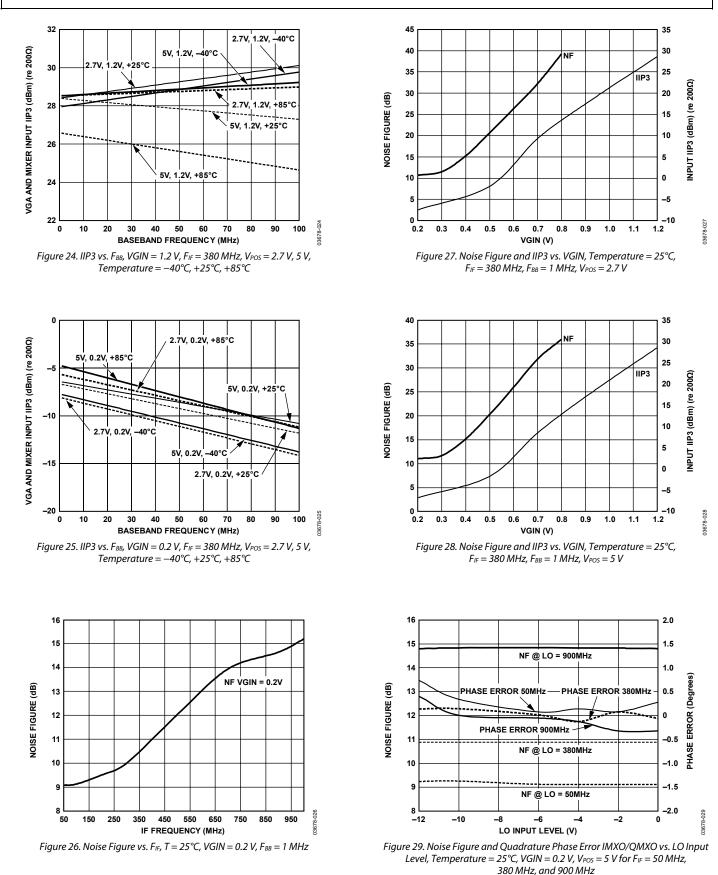

Figure 32. IIP3 and Noise Figure vs.  $F_{IF}$ ,  $V_{POS} = 2.7 V$ , 5 V, Temperature = 25°C

Figure 31. Input 1 dB Compression Point vs.  $F_{IF}$ ,  $F_{BB} = 1$  MHz,  $V_{POS} = 2.7$  V, 5 V, Temperature =  $-40^{\circ}$ C, +25 °C, +85 °C

03678-035

03678-036

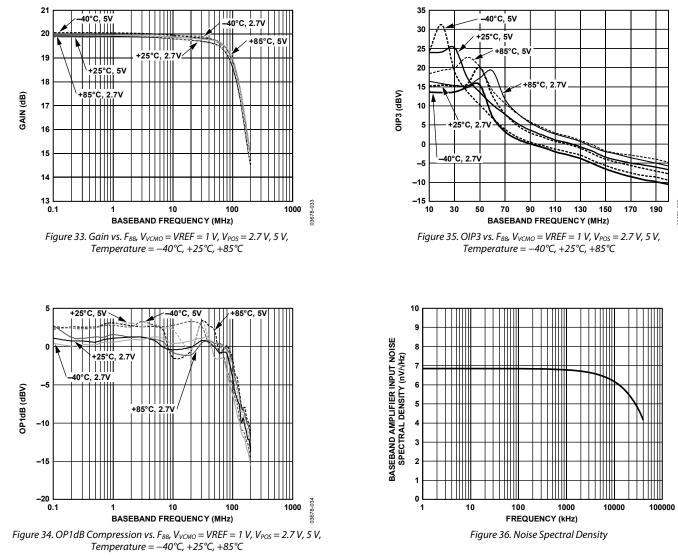

#### **FINAL BASEBAND AMPLIFIERS**

#### VGA/DEMODULATOR AND BASEBAND AMPLIFIER

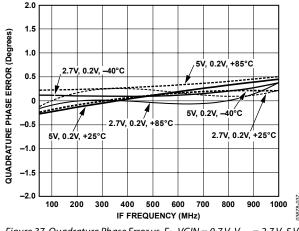

Figure 38. Quadrature Phase Error vs. F<sub>BB</sub>, VGIN = 0.7 V, V<sub>POS</sub> = 2.7 V, 5 V, *Temperature* =  $-40^{\circ}$ *C*,  $+25^{\circ}$ *C*,  $+85^{\circ}$ *C*,  $F_{IF} = 380$  MHz

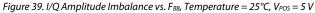

Figure 40. I/Q Amplitude Imbalance vs. F<sub>IF</sub>, Temperature = 25°C, V<sub>POS</sub> = 5 V

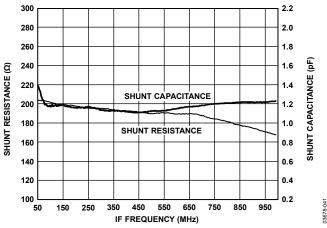

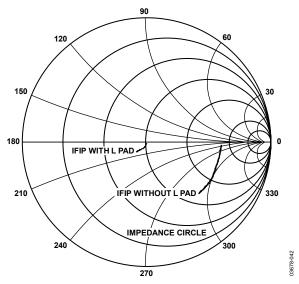

Figure 42. S11 of IF Input vs.  $F_{IF}$ ,  $F_{IF} = 50$  MHz to 1 GHz, VGIN = 0.7 V,  $V_{POS} = 5 V$  (with L Pad, with No Pad, Normalized to 50  $\Omega$ )

Rev. A | Page 16 of 28

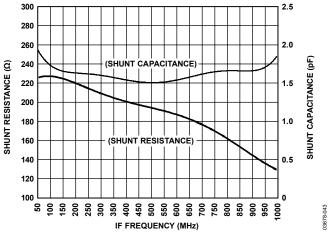

Figure 43. Input Impedance of Mixer Input vs. FIF, VGIN = 0.7 V, VPOS = 5 V

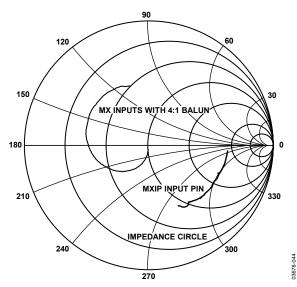

Figure 44. S11 of Mixer Input vs.  $F_{IF}$ ,  $F_{IF} = 50$  MHz to 1 GHz, VGIN = 0.7 V,  $V_{POS} = 5$  V (With and Without Balun)

### **THEORY OF OPERATION**

#### VGA

The VGA is implemented using the patented X-AMP architecture. The single-ended IF signal is attenuated in eight discrete 6 dB steps by a passive R-2R ladder. Each discrete attenuated version of the IF signal is applied to the input of a transconductance stage. The current outputs of all transconductance stages are summed together and drive a resistive load at the output of the VGA. Gain control is achieved by smoothly turning on and off the relevant transconductance stages with a temperaturecompensated interpolation circuit. This scheme allows the gain to continuously vary over a 44 dB range with linear-in-decibel gain control. This configuration also keeps the relative dynamic range constant (for example, IIP3 - NF in dB) over the gain setting; however, the absolute intermodulation intercepts and noise figure vary directly with gain. The analog voltage VGIN sets the gain. VGIN = 0.2 V is the maximum gain setting, and VGIN = 1.2 V is the minimum voltage gain setting.

#### **DOWNCONVERSION MIXERS**

The output of the VGA drives two (I and Q) double-balanced Gilbert cell downconversion mixers. Alternatively, driving the ENVG pin low can disable the VGA, and the mixers can be externally driven directly via the MXIP and MXIN ports. At the input of the mixer, a degenerated differential pair performs linear voltage-to-current conversions. The differential output current feeds into the mixer core where it is downconverted by the mixing action of the Gilbert cell. The phase splitter provides quadrature LO signals that drive the LO ports of the in-phase and quadrature mixers.

Buffers at the output of each mixer drive the IMXO and QMXO pins. These linear, low output impedance buffers drive 40  $\Omega$ , temperature-stable, passive resistors in series with each output pin (IMXO and QMXO). This 40  $\Omega$  should be considered when calculating the reverse termination if an external filter is inserted between IMXO (QMXO) and IAIN (QAIN). The VCMO pin sets the dc output level of the buffer. This can be set externally or connected to the on-chip 1.0 V reference, VREF.

#### PHASE SPLITTER

Quadrature generation is achieved using a divide-by-2 frequency divider. Unlike a polyphase filter that achieves quadrature over a limited frequency range, the divide-by-2 approach maintains quadrature over a broad frequency range and does not attenuate the LO. The user, however, must provide an external signal XLO that is twice the frequency of the desired LO frequency. XLO drives the clock inputs of two flip-flops that divide down the frequency by a factor of 2. The outputs of the two flip-flops are one-half period of XLO out of phase. Equivalently, the outputs are onequarter period (90°) of the desired LO frequency out of phase. Because the transitions on XLO define the phase difference at the outputs, deviation from 50% duty cycle translates directly to quadrature phase errors.

If the user generates XLO from a  $1 \times$  frequency ( $f_{REF}$ ) and a frequency-doubling circuit (XLO =  $2 \times f_{REF}$ ), fundamentally there is a 180° phase uncertainty between  $f_{REF}$  and the AD8348 internal quadrature LO. The phase relationship between I and Q LO, however, is always 90°.

#### **I/Q BASEBAND AMPLIFIERS**

Two (I and Q) fixed gain (20 dB), single-ended-to-differential amplifiers are provided to amplify the demodulated signal after off-chip filtering. The amplifiers use voltage feedback to linearize the gain over the demodulation bandwidth. These amplifiers can be used to maximize the dynamic range at the input of an ADC following the AD8348.

The input to the baseband amplifiers, IAIN (QAIN), feeds into the base of a bipolar transistor with an input impedance of roughly 50 k $\Omega$ . The baseband amplifiers sense the single-ended difference between IAIN (QAIN) and VCMO. IAIN (QAIN) can be dc biased by terminating it with a shunt resistor to VCMO, such as when an external filter is inserted between IMXO (QMXO) and IAIN (QAIN). Alternatively, any dc connection to IMXO (QXMO) can provide appropriate bias via the offset-nulling loop.

#### ENABLE

A master biasing cell that can be disabled using the ENBL pin controls the biasing for the chip. If the ENBL pin is held low, the entire chip powers down to a low power sleep mode, typically consuming 75  $\mu$ A at 5 V.

#### **BASEBAND OFFSET CANCELLATION**

A low output current integrator senses the output voltage offset at IOPP and IOPN (QOPP and QOPN) and injects a nulling current into the signal path. The integration time constant of the offset-nulling loop is set by Capacitor COFS from IOFS (QOFS) to VCMO. This forms a high-pass response for the baseband signal path with a lower 3 dB frequency of

$$f_{PASS} = \frac{1}{2\pi \times 2650 \ \Omega \ \times COFS}$$

Alternatively, the user can externally adjust the dc offset by driving IOFS (QOFS) with a digital-to-analog converter or other voltage source. In this case, the baseband circuit operates all the way down to dc ( $f_{PASS} = 0$  Hz). The integrator output current is only 50  $\mu$ A and can be easily overridden with an external voltage source. The nominal voltage level applied to IOFS (QOFS) to produce a 0 V differential offset at the baseband outputs is 900 mV.

The IOFS (QOFS) pin must be connected to either a bypass capacitor (>0.1  $\mu$ F) or an external voltage source to prevent the feedback loop from oscillating.

The feedback loop will be broken at dc if an ac-coupled baseband filter is placed between the mixer outputs and the baseband amplifier inputs. If an ac-coupled filter is implemented, the user must handle the offset compensation via some external means.

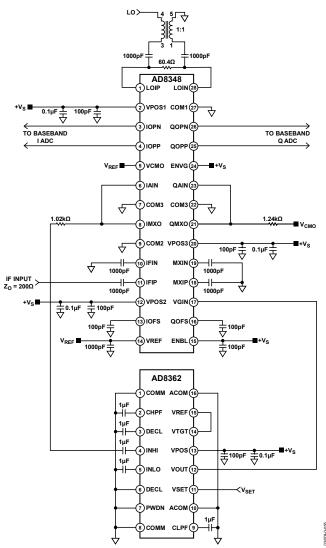

### APPLICATIONS BASIC CONNECTIONS

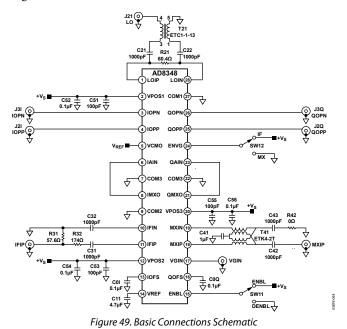

Figure 49 shows the basic connections schematic for the AD8348.

#### **POWER SUPPLY**

The voltage supply for the AD8348, between 2.7 V and 5 V, should be provided to the +VPOSx pins, and ground should be connected to the COMx pins. Each supply pin should be decoupled separately using two capacitors whose recommended values are 100 pF and 0.1  $\mu$ F (values close to these can also be used).

#### **DEVICE ENABLE**

To enable the device, the ENBL pin should be driven to Vs. Grounding the ENBL pin disables the device.

#### **VGA ENABLE**

Driving the voltage on the ENVG pin to  $V_S$  enables the VGA. In this mode, the MX inputs are disabled and the IF inputs are used. Grounding the ENVG pin disables the VGA and the IF inputs. When the VGA is disabled, the MX inputs should be used.

#### **GAIN CONTROL**

When the VGA is enabled, the voltage applied to the VGIN pin sets the gain. The gain control voltage range is between 0.2 V and 1.2 V. This corresponds to a gain range between +25.5 dB and -18.5 dB.

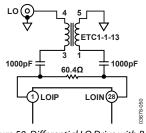

#### LO INPUTS

For optimum performance, the local oscillator port should be driven differentially through a balun. The recommended balun is M/A-COM ETC1-1-13. The LO inputs to the device should be ac-coupled, unless an ac-coupled transformer is being used. For a broadband match to a 50  $\Omega$  source, a 60.4  $\Omega$  resistor should be placed between the LOIP and LION pins.

Figure 50. Differential LO Drive with Balun

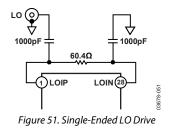

Alternatively, the LO port can be driven from a single-ended source without a balun (Figure 51). The LO signal is ac-coupled directly into the LOIP pin via an ac-coupling capacitor, and the LOIN pin is ac-coupled to ground. Driving the LO port from a single-ended source results in an increase in both quadrature phase error and LO leakage.

The recommended LO drive level is between -12 dBm and 0 dBm. The LO frequency at the input to the device should be twice that of the desired LO frequency at the mixer core. The applied LO frequency range is between 100 MHz and 2 GHz.

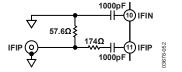

#### **IF INPUTS**

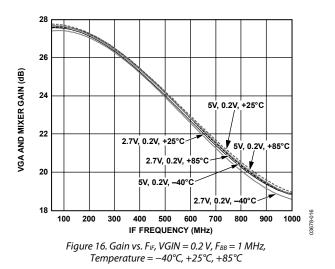

The IF inputs have an input impedance of  $200 \Omega$ . A broadband  $50 \Omega$  match can be presented to the driving source through the use of a minimum-loss L pad. This minimum-loss pad introduces an 11.46 dB loss in the input path and must be taken into account when calculating metrics such as gain and noise figure. Figure 42 shows the S11 of the IF input with and without the L pad.

Figure 52. Minimum-Loss L Pad for 50  $\Omega$  IF Input

#### **MX INPUTS**

The mixer inputs, MXIP and MXIN, have a nominal impedance of 200  $\Omega$  and should be driven differentially. When driven from a differential source, the input should be ac-coupled to the source via capacitors, as shown in Figure 53.

Figure 53. Driving the MX Inputs from a Differential Source

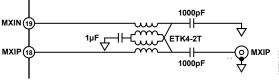

If the MX inputs are to be driven from a single-ended 50  $\Omega$  source, a 4:1 balun can be used to transform the 200  $\Omega$  impedance of the inputs to 50  $\Omega$  while performing the required single-endedto-differential conversion. The recommended transformer is the M/A-COM ETK4-2T.

Figure 54. Driving the MX Inputs from a Single-Ended 50  $\Omega$  Source

#### **BASEBAND OUTPUTS**

The baseband amplifier outputs, IOPP, IOPN, QOPP, and QOPN, should be presented with loads of at least 2 k $\Omega$  (single-ended to ground). They are not designed to drive 50  $\Omega$  loads directly. The typical swing for these outputs is 2 V p-p differential (1 V p-p single-ended), but larger swings are possible as long as care is taken to ensure that the signals remain within the lower limit of 0.5 V and the upper limit of V<sub>s</sub> – 1 V of the output swing. To achieve a larger swing, it is necessary to adjust the common-mode bias of the baseband output signals. Increasing the swing can have the benefit of improving the signal-to-noise ratio of the baseband amplifier output.

When connecting the baseband outputs to other devices, care should be taken to ensure that the outputs are not capacitively loaded by approximately 20 pF or more. Such loads could potentially overload the output or induce oscillations. The effect of capacitive loading on the baseband amplifier outputs can be mitigated by inserting series resistors of approximately 200  $\Omega$ .

#### **OUTPUT DC BIAS LEVEL**

The dc bias of the mixer outputs and the baseband amplifier inputs and outputs is determined by the voltage that is driven onto the VCMO pin. The range of this voltage is typically between 500 mV and 4 V when operating with a 5 V supply.

To achieve maximum voltage swing from the baseband amplifiers, VCMO should be driven at 2.25 V; this allows a swing of up to 7 V p-p differential (3.5 V p-p single-ended).

#### INTERFACING TO DETECTOR FOR AGC OPERATION

The AD8348 can be interfaced with a detector such as the AD8362 rms-to-dc converter to provide an automatic signalleveling function for the baseband outputs.

Figure 55. AD8362 Configuration for AGC Operation

Assuming the I and Q channels have the same rms power, the mixer output (or the output of the baseband filter) of one channel can be used as the input of the AD8362. The AD8362 should be operated in a region where its linearity error is small. Also, a voltage divider should be implemented with an external resistor in series with the 200  $\Omega$  input impedance of the AD8362 input. This attenuates the AD8348 mixer output so that the AD8362 input is not overdriven. The size of the resistor between the mixer output and the AD8362 input should be chosen so that the peak signal level at the input of the AD8362 is about 10 dB less than the approximately 10 dBm maximum of the AD8362 dynamic range.

The other side of the AD8348 baseband output should be loaded with a resistance equal to the series resistance of the attenuating resistor in series with the AD8362's 200  $\Omega$  input impedance. This resistor should be tied to the source driving VCMO so that there is no dc drawn from the mixer output.

The level of the mixer output (or the output of the baseband filter) can then be set by varying the setpoint voltage fed to Pin 11 (VSET) of the AD8362.

Care should be taken to ensure that blockers—unwanted signals in the band of interest that are demodulated along with the desired signal—do not dominate the rms power of the AD8362 input. This can cause an undesired reduction in the level of the mixer output. To overcome this, baseband filtering can be implemented to filter out undesired signals before the signal is presented to the AD8362.

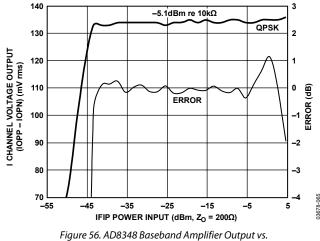

Figure 56 shows the effectiveness of the AGC loop in maintaining a baseband amplifier output amplitude with less than 0.5 dB of amplitude error over an IF input range of 40 dB while demodulating a QPSK-modulated signal at 380 MHz. The AD8362 is insensitive to crest factor variations and therefore provides similar performance regardless of the modulation of the incoming signal.

IF Input Power with AD8362 AGC Loop

#### **BASEBAND FILTERS**

Baseband low-pass or band-pass filtering can be conveniently performed between the mixer outputs (IMXO and QMXO) and the input to the baseband amplifiers. Consideration should be given to the output impedance of the mixers (40  $\Omega$ ).

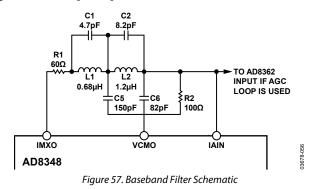

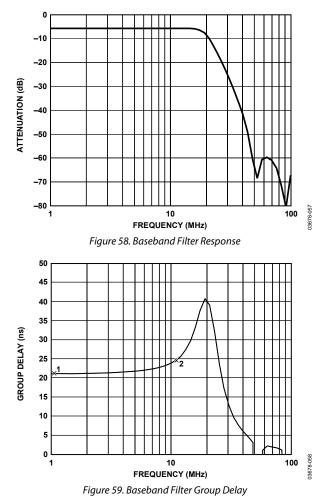

Figure 57 shows the schematic for a 100  $\Omega$ , fourth-order elliptic low-pass filter with a 3 dB cutoff frequency of 20 MHz. Source and load impedances of approximately 100  $\Omega$  ensure that the filter sees a matched source and load. This also ensures that the mixer output is driving an overall load of 200  $\Omega$ . Note that the shunt termination resistor is tied to the source driving VCMO and not to ground. This ensures that the input to the baseband amplifier is biased to the proper reference level. VCMO is not

The frequency response and group delay of this filter are shown in Figure 58 and Figure 59.

an output pin and must be biased by a low impedance source.

#### LO GENERATION

Analog Devices has a line of PLLs that can be used for generating the LO signal. Table 4 lists the PLLs and their maximum frequency and phase noise performance.

| ADI Model  | Frequency F⊪<br>(MHz) | @ 1 kHz ΦN<br>dBc/Hz,<br>200 kHz PFD |

|------------|-----------------------|--------------------------------------|

| ADF4001BRU | 165                   | -99                                  |

| ADF4001BCP | 165                   | -99                                  |

| ADF4110BRU | 550                   | -91                                  |

| ADF4110BCP | 550                   | -91                                  |

| ADF4111BRU | 1200                  | -78                                  |

| ADF4111BCP | 1200                  | -78                                  |

| ADF4112BRU | 3000                  | -86                                  |

| ADF4112BCP | 3000                  | -86                                  |

| ADF4116BRU | 550                   | -89                                  |

| ADF4117BRU | 1200                  | -87                                  |

| ADF4118BRU | 3000                  | -90                                  |

ADI also offers the ADF4360 fully integrated synthesizer and VCO on a single chip that offers differential outputs for driving the local oscillator input of the AD8348. This means that the user can eliminate the use of a balun for single-ended-to-differential conversions. The ADF4360 comes as a family of chips with six operating frequency ranges. One can be chosen depending on the local oscillator frequency required. Table 5 shows the options available.

Table 5. ADF4360 Family Operating Frequencies

| ADI Model | Output Frequency Range (MHz)        |  |  |  |

|-----------|-------------------------------------|--|--|--|

| ADF4360-1 | 2150 to 2450                        |  |  |  |

| ADF4360-2 | 1800 to 2150                        |  |  |  |

| ADF4360-3 | 1550 to 1950                        |  |  |  |

| ADF4360-4 | 1400 to 1800                        |  |  |  |

| ADF4360-5 | 1150 to 1400                        |  |  |  |

| ADF4360-6 | 1000 to 1250                        |  |  |  |

| ADF4360-7 | Lower frequencies set by external L |  |  |  |

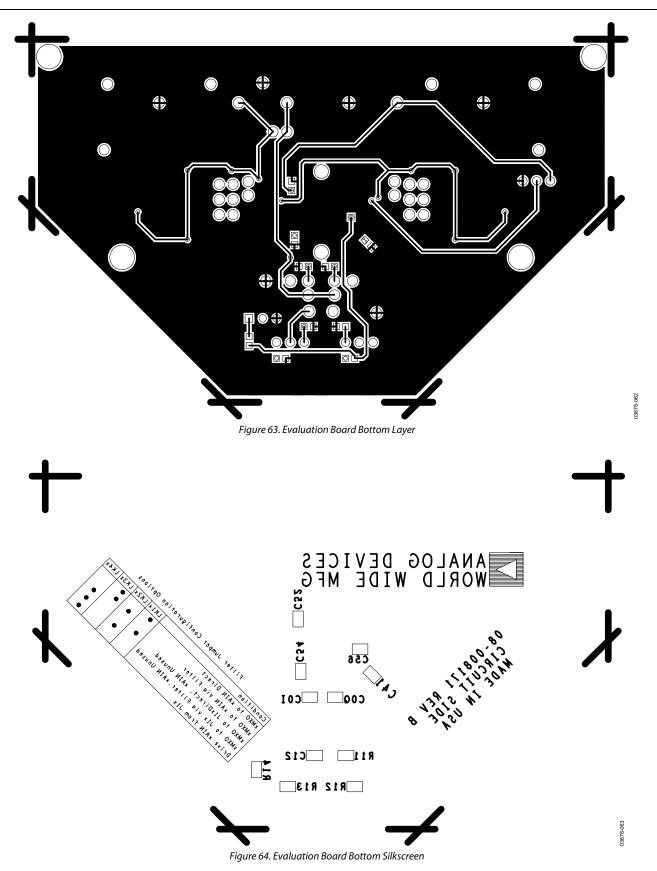

#### **EVALUATION BOARD**

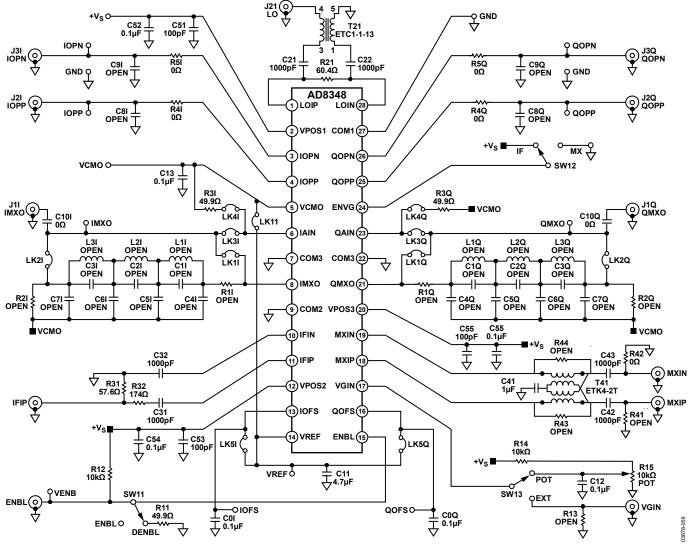

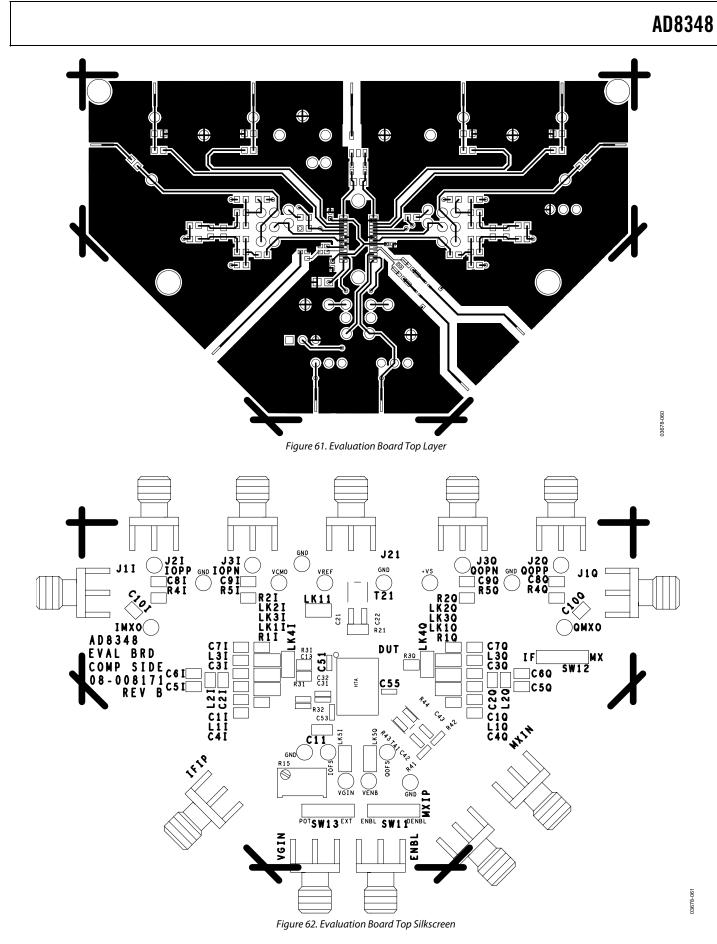

Figure 60 shows the schematic for the AD8348 evaluation board. Note that uninstalled components are indicated with the OPEN designation. The board is powered by a single supply in the range of 2.7 V to 5.5 V. Table 6 details the various configuration options of the evaluation board. Table 7 shows the various jumper configurations for operating the evaluation board with different signal paths.

Power to operate the board can be fed to a single  $V_S$  test point located near the LO input port at the top of the evaluation board. A GND test point is conveniently provided next to the  $V_S$  test point for the return path. The device is enabled by moving Switch SW11 (at the bottom left of the evaluation board) to the ENBL position. The device is disabled by moving SW11 to the DENBL position. If desired, the device can be enabled and disabled from an external source that can be fed into the ENBL SMA connector or the VENB test point, in which case SW11 should be placed in the DENBL position.

The IF and MX inputs are selected via SW12. The switch should be moved in the direction of the desired input.

#### **Gain Control**

For convenience, a potentiometer, R15, is provided to allow for changes in gain without the need for an additional dc voltage source. To use the potentiometer, the SW13 switch must be set to the POT position. Alternatively, an external voltage applied to either the test point or SMA connector labeled VGIN can set the gain. SW13 must be set to the EXT position when an external gain control voltage is used.

#### LO Input

The local oscillator signal should be fed to the SMA Connector J21. This port is terminated in 50  $\Omega$ . The acceptable LO power input range is from -12 dBm to 0 dBm and must be at a frequency double that of the IF/MX frequency. Remember that the AD8348 uses a 2:1 frequency divider in the LO path to generate the internally required quadrature-phase-related LO signals.

#### IF Input

The IF input should be fed into the SMA connector IFIP. The VGA must be enabled when this port is used (SW12 in the IF position). When this IF input is chosen, the signal path includes a minimum-loss attenuator to transform a 50  $\Omega$  input source to the 200  $\Omega$  source impedance level for which the VGA was designed. This pad provides a very broadband input match at the expense of an 11.46 dB power attenuation in the input path. It is very important to take this into account when measuring the noise and distortion performance of the unmodified board using the IFIP input; the apparent noise figure will be degraded by 11.46 dB, and the apparent IIP3 will be 11.46 dB higher than actual. If full weak-signal performance is desired from the evaluation board, the attenuator (comprising R31 and R32) should be removed and replaced with a low-loss RF transformer providing the desired 4:1 impedance ratio. When a transformer is used, IFIN should be ac-coupled to ground and not driven differentially with IFIP.

#### MX Input

The evaluation board is by default set for a differential MX drive through a balun (T41) from a single-ended source fed into the MXIP SMA connector. When the MX inputs are used, the internal VGA is bypassed. To change to a differential driving source, T41 should be removed along with Resistor R42. The 0  $\Omega$  R43 and R44 resistors should be installed in place of T41 to bridge the gap between the input traces. This presents a nominal

differential impedance of 200  $\Omega$  (100  $\Omega$  per side). The differential inputs should then be fed into SMA connectors MXIP and MXIN.

#### **Mixer Outputs**

The I and Q mixer outputs are available through the IMXO and QMXO SMA connectors. These outputs are biased to VCMO and are not designed to drive loads smaller than 200  $\Omega$ . To prevent damage to test equipment that cannot tolerate dc biases, pads for series dc-blocking capacitors are provided. These pads are populated with 0  $\Omega$  by default.

#### **Baseband Outputs**

The baseband outputs are made available at the IOPP, IOPN, QOPP, and QOPN test points and SMA connectors. These outputs are not designed to be connected directly to 50  $\Omega$  loads and should be presented with loads of approximately 2 k $\Omega$  or greater.

The dc bias level of the baseband amplifier outputs are by default tied to VREF through LK11. If desired, the dc bias level can be changed by removing LK11 and driving a dc voltage onto the VCMO test point.

Figure 60. Evaluation Board Schematic

Rev. A | Page 25 of 28

Rev. A | Page 26 of 28

#### Table 6. Evaluation Board Configuration Options

| Component                                     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Default Condition                                                     |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Vs, GND                                       | Power supply and ground vector pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Not applicable                                                        |

| SW11, ENBL                                    | Device enable: Place SW11 in the ENBL position to connect the ENBL pin to V <sub>s</sub> . Place SW11 in the DENBL position to disable the device by grounding the Pin ENBL through a 50 $\Omega$ pull-down resistor. The device can also be enabled via an external voltage applied to ENBL or VENB.                                                                                                                                                                                                                                                                                                                                        | SW11 = ENBL                                                           |

| SW13, R15,<br>VGIN                            | Gain control selection: With SW13 in the POT position, the gain of the VGA can be set using the R15 potentiometer. With SW13 in the EXT position, the VGA gain can be set by an external voltage to the SMA connector VGIN. For VGA operation, the VGA must first be enabled by setting SW12 to the IF position.                                                                                                                                                                                                                                                                                                                             | SW13 = POT                                                            |

| SW12                                          | VGA enable selection: With SW12 in the IF position, the ENVG pin is connected to $V_s$ and the VGA is enabled. The IF input should be used when SW12 is in the IF position. With SW12 in the MX position, the ENVG pin is grounded and the VGA is disabled. The MX inputs should be used when SW12 is in the MX position.                                                                                                                                                                                                                                                                                                                    | SW12 = IF                                                             |

| IFIP, R31, R32                                | IF inputs: The single-ended IF signal should be connected to this SMA connector. R31 and R32 form an L pad that presents a 50 $\Omega$ termination to the driving source. This L pad introduces an 11.46 dB loss in the input signal path and should be taken into consideration when calculating the gain of the AD8348.                                                                                                                                                                                                                                                                                                                    | R31 = 57.6 Ω<br>R32 = 174 Ω                                           |

| MXIP, MXIN,<br>T41,<br>R41, R42,<br>C42, C43  | Mixer inputs: These inputs can be configured for either differential or single-ended operation. The evaluation board is by default set for differential MX drive through a balun (T41) from a single-ended source fed into the MXIP SMA connector. To change to a differential driving source, T41 should be removed along with Resistor R42. The 0 $\Omega$ Resistors R43 and R44 should be installed in place of T41 to bridge the gap between the input traces. This will present a nominal differential impedance of 200 $\Omega$ (100 $\Omega$ per side). The differential inputs should then be fed into SMA connectors MXIP and MXIN. | T41 = M/A-COM ETK4-2T;<br>R41= OPEN; C42, C43 =<br>1000 pF; R42 = 0 Ω |

| LK11, VCMO                                    | Baseband amplifier output bias: Installing LK11 connects VREF to VCMO. This sets the bias level<br>on the baseband amplifiers to VREF, which is equal to approximately 1 V. Alternatively, with<br>LK11 removed, the bias level of the baseband amplifiers can be set by applying an external<br>voltage to the VCMO test point.                                                                                                                                                                                                                                                                                                             | LK11 installed                                                        |

| C8, C9, R4, R5<br>(I and Q)                   | Baseband amplifier outputs and output filter: Additional low-pass filtering can be provided at the baseband output with these filters.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R4, R5 = 0 Ω                                                          |

| C10 (I and Q)                                 | Mixer output dc-blocking capacitors: The mixer outputs are biased to VCMO. To prevent damage to test equipment that cannot tolerate dc biases, C10 is provided to block the dc component, thus protecting the test equipment.                                                                                                                                                                                                                                                                                                                                                                                                                | C10 = 0 Ω                                                             |

| C1 to C7,<br>R1, R2,<br>L1 to L3<br>(I and Q) | Baseband filter: These components are provided for baseband filtering between the mixer outputs and the baseband amplifier inputs. The baseband amplifier input impedance is high and the filter termination impedance is set by R2. See Table 7 for the jumper settings.                                                                                                                                                                                                                                                                                                                                                                    | AII = OPEN                                                            |

| LK5 (I and Q)                                 | Offset compensation loop disable: Installing these jumpers will disable the offset compensation loop for the corresponding channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | LK5x = OPEN                                                           |

#### Table 7. Filter-Jumper Configuration Options

| Condition                           | LK1x | LK2x | LK3x | LK4x |

|-------------------------------------|------|------|------|------|

| xMXO to xAIN Directly               | •    |      | •    |      |

| xMXO to xAIN via Filter             |      | •    | •    |      |

| xMXO to J1x Directly, xAIN Unused   | •    |      |      | •    |

| xMXO to J1x via Filter, xAIN Unused |      | •    |      | •    |

| Drive xAIN from J1x                 |      |      |      | •    |

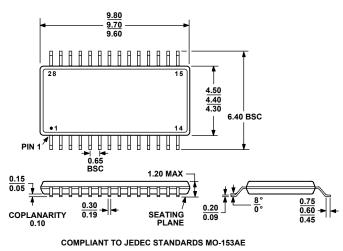

### **OUTLINE DIMENSIONS**

Figure 65. 28-Lead Thin Shrink Small Outline Package [TSSOP] (RU-28) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model                   | Temperature Range | Package Description                                                | Package Option |

|-------------------------|-------------------|--------------------------------------------------------------------|----------------|

| AD8348ARU               | -40°C to +85°C    | 28-Lead Thin Shrink Small Outline Package [TSSOP]                  | RU-28          |

| AD8348ARU-REEL7         | -40°C to +85°C    | 28-Lead Thin Shrink Small Outline Package [TSSOP] 7" Tape and Reel | RU-28          |

| AD8348ARUZ <sup>1</sup> | -40°C to +85°C    | 28-Lead Thin Shrink Small Outline Package [TSSOP]                  | RU-28          |

| AD8348ARUZ-REEL71       | -40°C to +85°C    | 28-Lead Thin Shrink Small Outline Package [TSSOP] 7" Tape and Reel | RU-28          |

| AD8348-EVAL             |                   | Evaluation Board                                                   |                |

$^{1}$  Z = Pb-free part.

©2006 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. C03678-0-4/06(A)

www.analog.com