# 73S8009C Versatile Power Management and Smart Card Interface IC

### Simplifying System Integration™

**DATA SHEET**

DS 8009C 025

February 2010

ISO/IEC 7816-3

#### **DESCRIPTION**

The Teridian 73S8009C is a versatile power management and single smart card interface circuit that is ideally suited for smart card reader products that are battery and/or USB bus-powered. In addition to its EMV 4.1 and ISO-7816-3 compliant smart card-to-host interface circuitry; it provides control, conversion, and regulation of power for a companion host processor circuit and power for the smart card. The 73S8009C can operate from a single 2.7 V to 6.5 V source supply, or a combination of battery power (4.0 V to 6.5 V) and USB power (4.4 V to 5.5 V).

The 73S8009C supports 5 V, 3 V, and 1.8 V smart cards. The smart card signals for RST, CLK, IO, and auxiliary signals AUX1 and AUX2 are level-shifted to the selected  $V_{\rm CC}$  value. Although the host controller is required to handle the detailed signal timing for activation and deactivation under normal conditions, the 73S8009C blocks any spurious signals on CLK, RST and IO during power-up (as  $V_{\rm CC}$  rises) and power-down. The 73S8009C contains two handshaking signals for the controller:  $\overline{\rm OFF}$  indicates that a card is present, and RDY indicates that  $V_{\rm CC}$  is at an acceptable value. The 73S8009C will perform emergency deactivation upon card removal, voltage faults, or over-current events

The power management circuitry of the 73S8009C allows operation from a wide range of voltages from multiple sources. V<sub>PC</sub> is converted by using an inductive, step-up power converter to the intermediate voltage, V<sub>P</sub>. V<sub>P</sub> is used by linear voltage regulators and switches to create the voltages  $V_{DD}$  and as required,  $V_{CC}$ .  $V_{DD}$  is used by the 73S8009C and is also made available for the companion controller circuit or other external circuits. The V<sub>BAT</sub> and V<sub>BUS</sub> pins provide inputs from alternate power sources as required. An internal switch in the 73S8009C acts as a single-pole, double-throw switch that selects either  $V_{BAT}$  or  $V_{BUS}$  to be connected to  $V_{PC}$ . When the voltage on V<sub>BUS</sub> is zero, V<sub>BAT</sub> is connected to V<sub>PC</sub>. When voltage is applied to V<sub>BUS</sub>, the switch selects V<sub>BUS</sub> as the source for power.

When power is supplied by  $V_{PC}$  or  $V_{BAT}$ , the 73S8009C is controlled by the ON\_OFF pin in the manner of a "push-on/push-off" button action. The OFF\_REQ and OFF\_ACK signals provide handshaking and control of the power "off" function by the controller. A SPST momentary switch to ground connected to ON\_OFF is all that is required for power control. Alternatively, the "off" state can be initiated from the host controller through OFF\_ACK. When the 73S8009C is "off," the current is less than 1  $\mu$ A.

When power is supplied via the  $V_{BUS}$  pin, the 73S8009C is unconditionally in the "power-on" state regardless of the action of the ON/OFF switch or OFF\_ACK signal. Power supply current operating from the  $V_{BUS}$  power when  $V_{CC}$  is off is less than 500  $\mu$ A to conform to USB "SUSPEND" requirements.

#### **APPLICATIONS**

- Handheld PINpad smart card readers for e-commerce, secure login, e-health, Gov't ID and loyalty

- Point of Sales & Transaction Terminals

- General Purpose Smart Card Readers

#### **ADVANTAGES**

- Ideally suited to USB bus-powered applications

- → Ideal for combo bus-powered and/or self-powered systems

- → Automatic battery switchover in bus powered systems

- Very low-power mode (sub-µA) with push-button ON/OFF switch input with de-bounce

- Provides 3.3 V / 40 mA power to external circuitry (host processor or peripheral circuits)

- The inductor-based DC-DC converter provides higher current and efficiency than usual charge-pump capacitor-based converters:

- → Ideal for battery-powered applications

#### **FEATURES**

- Smart card Interface:

- Complies with ISO-7816-3 and EMV 4.1 and derivative standards

- A DC-DC Converter provides 1.8 V/3 V/5 V to the card from a wide range of external power supply inputs

- Provides up to 65 mA to the card

- ISO-7816-3 Card emergency deactivation sequencer

- 2 voltage supervisors detect voltage drops on the V<sub>CC</sub> (card) and V<sub>DD</sub> (digital) power supplies

- Card over-current detection 150 mA max.

- 2 card detection inputs, 1 for either user polarity

- Auxiliary I/O lines for synchronous and ISO-7816-12 USB card support

- Card CLK clock frequency up to 20 MHz

- 6 kV ESD and short circuit protection on the card interface

- System Controller Interface:

- 5 Signal images of the card signals (RSTIN, CLKIN, I/OUC, AUX1UC and AUX2UC)

- 2 Inputs activate and select the card voltage (CMDVCC5 and CMDVCC3)

- 2 Outputs, interrupt to the system controller (OFF and RDY), to inform the system controller of the card presence / faults and status of the interface

- 1 Chip Select input

- 2 Handshaking signals for proper shutdown sequencing of all output supply voltages (OFF\_REQ, OFF\_ACK)

- ON/OFF Main System Switch:

- Input for an SPST momentary switch to ground

- DC-DC Converter:

- Step-up converter

- Generates an intermediary voltage V<sub>P</sub>

- Requires a single 10 μH Inductor

- System Power Supply requirements:

- When using VBUS: Standard USB +5 input (range +4.4 V to 5.5 V)

- When using V<sub>BAT</sub>: 4.0 V to 6.5 V

- When using V<sub>PC</sub>: 2.7 V to 6.5 V

- Automated detection of voltage presence -Priority on VBUS over VBAT

- Power Supply Output:

- V<sub>DD</sub> supply output available to power up external circuitry: 3.3 V ±0.3 V, 40 mA

- Industrial temperature range

- Small format QFN package

- RoHS compliant (6/6) lead-free package

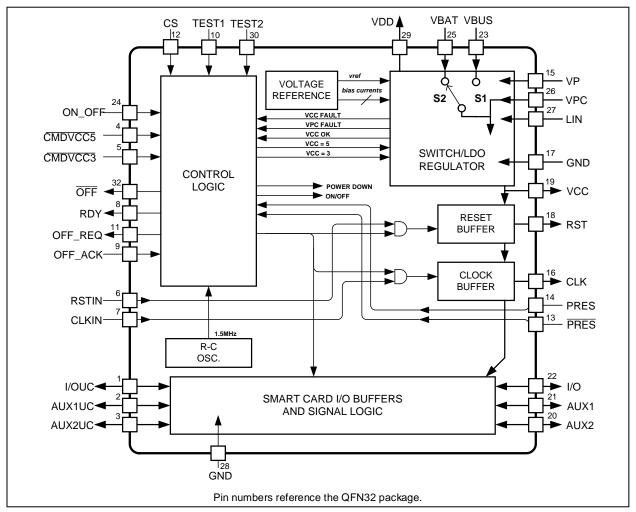

#### **FUNCTIONAL DIAGRAM**

Figure 1: 73S8009C Block Diagram

# **Table of Contents**

| 1 | Pinout |                                                |                                        |  |  |  |

|---|--------|------------------------------------------------|----------------------------------------|--|--|--|

| 2 | Elec   | ctrical Specifications                         | 10                                     |  |  |  |

|   | 2.1    | Absolute Maximum Ratings                       | 10                                     |  |  |  |

|   | 2.2    | Recommended Operating Conditions               |                                        |  |  |  |

|   | 2.3    |                                                |                                        |  |  |  |

|   | 2.4    | Digital Signals Characteristics                | 14                                     |  |  |  |

|   | 2.5    | DC Characteristics                             |                                        |  |  |  |

|   | 2.6    | Voltage / Temperature Fault Detection Circuits | 15                                     |  |  |  |

|   | 2.7    | Thermal Characteristics                        | 15                                     |  |  |  |

| 3 | App    | olications Information                         | 16                                     |  |  |  |

|   | 3.1    | Example 73S8009C Schematics                    | 16                                     |  |  |  |

|   | 3.2    | Power Supply and Converter                     |                                        |  |  |  |

|   | 3.3    | Interface Function - ON/OFF Modes              | 18                                     |  |  |  |

|   | 3.4    | System Controller Interface                    |                                        |  |  |  |

|   | 3.5    | Card Power Supply and Voltage Supervision      |                                        |  |  |  |

|   | 3.6    | Activation and De-activation Sequence          |                                        |  |  |  |

|   | 3.7    | OFF and Fault Detection                        |                                        |  |  |  |

|   | 3.8    | Chip Selection                                 |                                        |  |  |  |

|   | 3.9    | I/O Circuitry and Timing                       |                                        |  |  |  |

| 4 | Equ    | uivalent Circuits                              | 26                                     |  |  |  |

| 5 | Med    | chanical Drawing                               | 30                                     |  |  |  |

| 6 | Ord    | ering Information                              | 31                                     |  |  |  |

| 7 | Rela   | ated Documentation                             | 31                                     |  |  |  |

| 8 | Con    | ntact Information                              | 31                                     |  |  |  |

| _ |        |                                                | ······································ |  |  |  |

# **Figures**

| Figure 1: 73S8009C Block Diagram                                 | 3  |

|------------------------------------------------------------------|----|

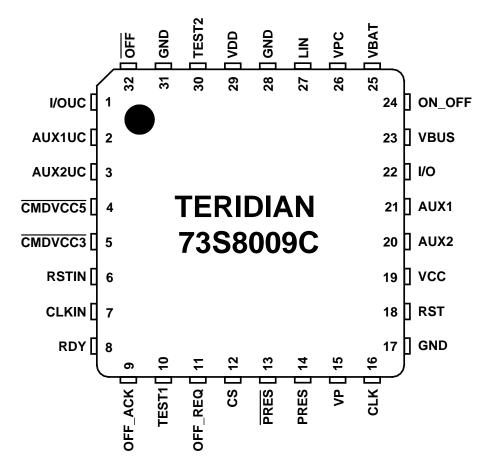

| Figure 2: 73S8009C 32-Pin QFN Pinout                             |    |

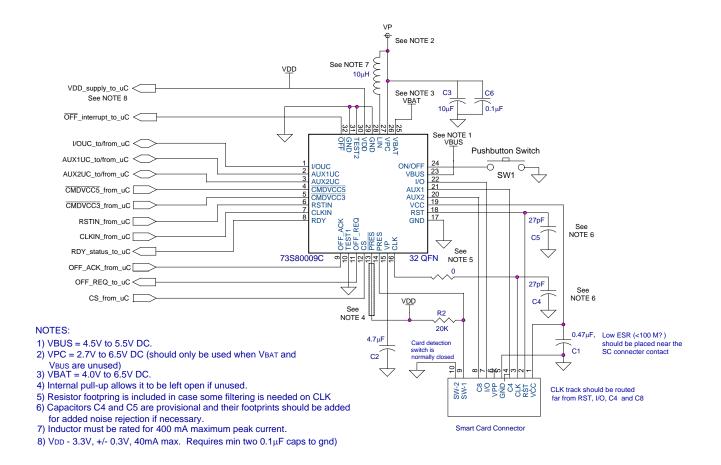

| Figure 3: Typical 73S8009C Application Schematic                 |    |

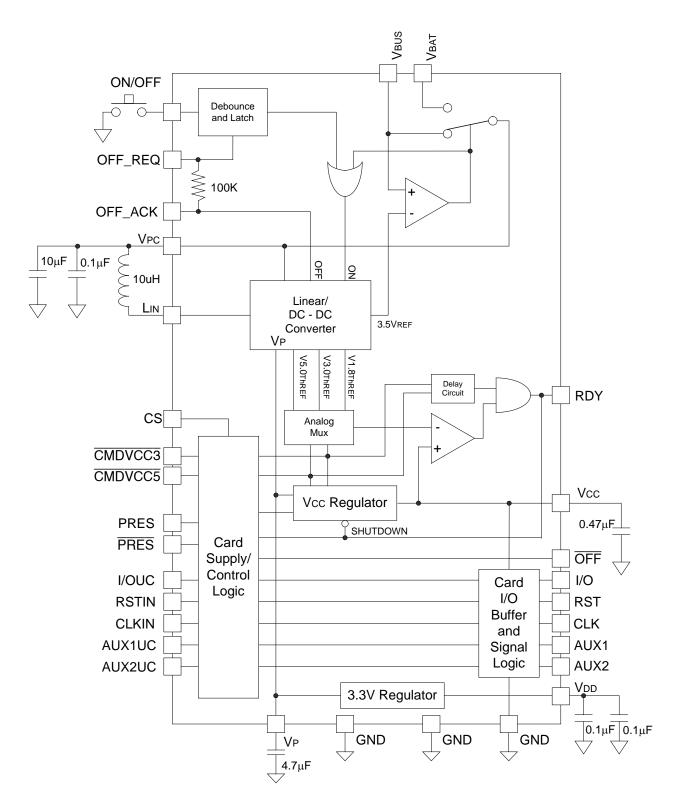

| Figure 4: 73S8009C Logical Block Diagram                         |    |

| Figure 5: Activation Sequence                                    |    |

| Figure 6: Deactivation Sequence                                  |    |

| Figure 7: OFF Activity                                           | 22 |

| Figure 8: CS Timing Definitions                                  |    |

| Figure 9: I/O and I/OUC State Diagram                            | 24 |

| Figure 10: I/O – I/OUC Delays - Timing Diagram                   | 25 |

| Figure 11: On_Off Pin                                            | 26 |

| Figure 12: Open Drain type – OFF and RDY                         |    |

| Figure 13: Power Input/Output Circuit, VDD, LIN, VPC, VCC, VP    |    |

| Figure 14: Smart Card CLK Driver Circuit                         |    |

| Figure 15: Smart Card RST Driver Circuit                         |    |

| Figure 16: Smart Card IO, AUX1, and AUX2 Interface Circuit       |    |

| Figure 17: Smart Card I/OUC, AUX1UC and AUX2UC Interface Circuit |    |

| Figure 18: General Input Circuit                                 |    |

| Figure 19: OFF_REQ Interface Circuit                             |    |

| Figure 20: 32-Pin QFN Package Dimensions                         | 30 |

| Tables                                                           |    |

| Table 1: 73S8009C Pin Definitions                                |    |

| Table 2: Absolute Maximum Device Ratings                         |    |

| Table 3: Recommended Operating Conditions                        |    |

| Table 4: DC Smart Card Interface Requirements                    |    |

| Table 5: Digital Signals Characteristics                         |    |

| Table 6: DC Characteristics                                      |    |

| Table 7: Voltage / Temperature Fault Detection Circuits          |    |

| Table 8: Thermal Characteristics                                 |    |

| Table 9: Order Numbers and Packaging Marks                       | 31 |

## 1 Pinout

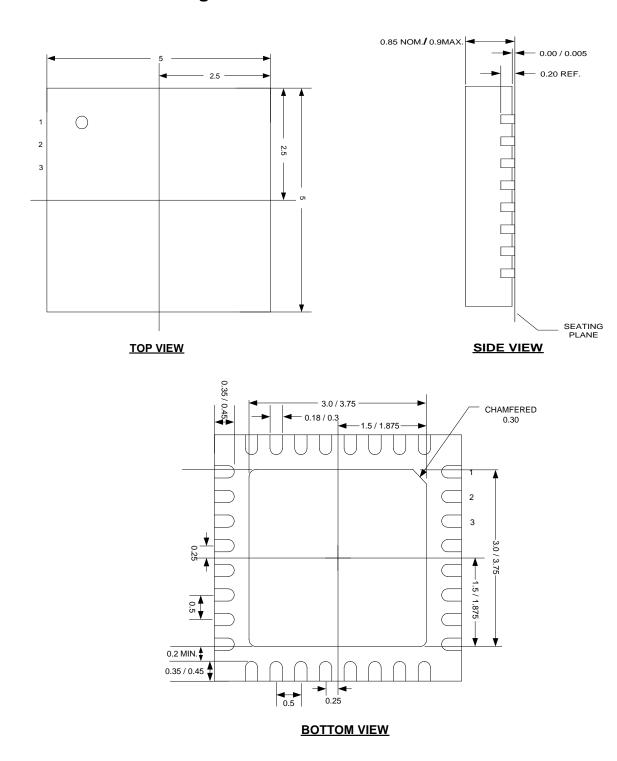

The 73S8009C is supplied as a 32-pin QFN package.

Figure 2: 73S8009C 32-Pin QFN Pinout

Table 1 describes the pin functions for the device.

Table 1: 73S8009C Pin Definitions

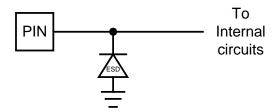

| Pin<br>Name | Pin<br>(QFN32) | Туре   | Equivalent<br>Circuit | Description                                                                                                                                                                                 |

|-------------|----------------|--------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Card Interf | ace            | I.     |                       |                                                                                                                                                                                             |

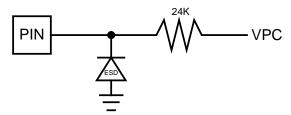

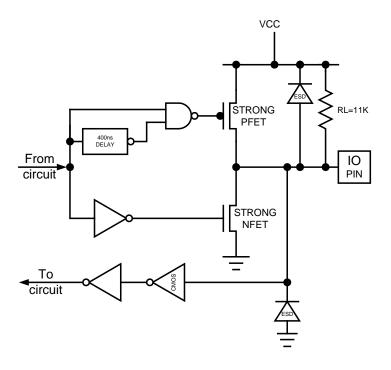

| I/O         | 22             | Ю      | Figure 16             | Card I/O: Data signal to/from card. Includes a pull-up resistor to $V_{\text{CC.}}$                                                                                                         |

| AUX1        | 21             | Ю      | Figure 16             | AUX1: Auxiliary data signal to/from card. Includes a pull-up resistor to V <sub>CC</sub> .                                                                                                  |

| AUX2        | 20             | Ю      | Figure 16             | AUX2: Auxiliary data signal to/from card. Includes a pull-up resistor to V <sub>CC</sub> .                                                                                                  |

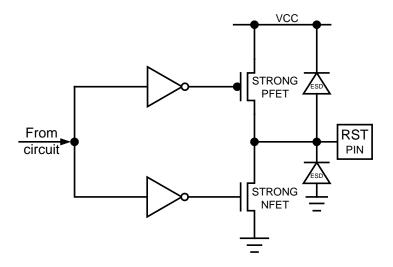

| RST         | 18             | 0      | Figure 15             | Card reset: provides reset (RST) signal to card. RST is the pass through signal on RSTIN. Internal control logic will hold RST low when card is not activated or VCC is too low.            |

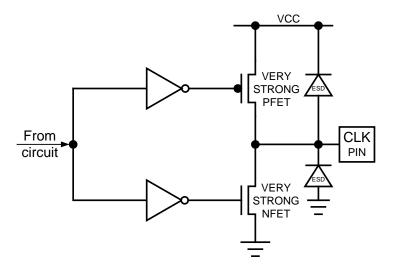

| CLK         | 16             | 0      | Figure 14             | Card clock: provides clock signal (CLK) to card. CLK is the pass through of the signal on pin CLKIN. Internal control logic will hold CLK low when card is not activated or VCC is too low. |

| PRES        | 14             | I      | Figure 18             | Card Presence switch: active high indicates card is present. Should be tied to GND when not used, but it Includes a high-impedance pull-down current source.                                |

| PRES        | 13             | I      | Figure 18             | Card Presence switch: active low indicates card is present. Should be tied to $V_{\text{DD}}$ when not used, but it Includes a high-impedance pull-up current source.                       |

| VCC         | 19             | PSO    | Figure 13             | Card power supply – logically controlled by sequencer, output of LDO regulator. Requires an external 0.47 $\mu$ F low ESR filter capacitor to GND.                                          |

| GND         | 17             | GND    | _                     | Card ground.                                                                                                                                                                                |

| Miscellane  | ous Inputs a   | nd Out | outs                  |                                                                                                                                                                                             |

| CLKIN       | 7              | I      | Figure 18             | Clock signal source for the card clock.                                                                                                                                                     |

| TEST1       | 10             | _      | _                     | Factory test pin. This pin must be tied to GND in typical applications.                                                                                                                     |

| TEST2       | 30             | _      | _                     | Factory test pin. This pin must be tied to GND in typical applications.                                                                                                                     |

| Power Sup   | ply and Gro    | und    |                       |                                                                                                                                                                                             |

| VDD         | 29             | PSO    | Figure 13             | System interface supply voltage and supply voltage for companion controller circuitry. Requires a minimum of two 0.1 $\mu$ F capacitors to ground for proper decoupling.                    |

| VPC         | 26             | PSI    | Figure 13             | Power supply source for main voltage converter circuit. A 10 $\mu$ F and a 0.1 $\mu$ F ceramic capacitor must be connected to this pin.                                                     |

| VBAT        | 25             |        |                       | Alternate power source input, typically from two series cells, V > 4 V.                                                                                                                     |

| Pin<br>Name        | Pin<br>(QFN32) | Туре | Equivalent<br>Circuit | Description                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|----------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VBUS               | 23             |      |                       | Alternate power source input from USB connector or hub.                                                                                                                                                                                                                                                                                                       |

| LIN                | 27             | PSI  | Figure 13             | Connection to 10 $\mu$ H inductor for internal step up converter. Note: inductor must be rated for 400 mA maximum peak current.                                                                                                                                                                                                                               |

| VP                 | 15             | PSO  | Figure 13             | Intermediate output of main converter circuit. Requires an external 4.7 µF low ESR filter capacitor to GND.                                                                                                                                                                                                                                                   |

| GND                | 28,31          |      | _                     | Ground.                                                                                                                                                                                                                                                                                                                                                       |

| Microcontro        | ller Interfac  | ce   |                       |                                                                                                                                                                                                                                                                                                                                                               |

| CS                 | 12             | I    | Figure 18             | When CS = 1, the control and signal pins are configured normally. When CS is set low, CMDVCC5, RSTIN, and CMDVCC3 are latched. I/OUC, AUX1UC, and AUX2UC are set to high-impedance pull-up mode and do not pass data to or from the smart card. Signals RDY and OFF are disabled to prevent a low output and the internal pull-up resistors are disconnected. |

| OFF                | 32             | 0    | Figure 12             | Interrupt signal to the processor. Active Low - Multifunction indicating fault conditions and card presence. Open drain output configuration – It includes an internal 20 k $\Omega$ pull-up to V <sub>DD</sub> . Pull-up is disabled in Power down state and CS = 0 modes.                                                                                   |

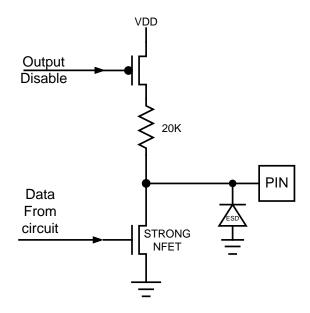

| I/OUC              | 1              | Ю    | Figure 17             | System controller data I/O to/from the card. Includes a pull-up resistor to $V_{\text{DD.}}$                                                                                                                                                                                                                                                                  |

| AUX1UC             | 2              | Ю    | Figure 17             | System controller auxiliary data I/O to/from the card. Includes a pull-up resistor to $V_{\text{DD}}$ .                                                                                                                                                                                                                                                       |

| AUX2UC             | 3              | Ю    | Figure 17             | System controller auxiliary data I/O to/from the card. Includes a pull-up resistor to $V_{\rm DD.}$                                                                                                                                                                                                                                                           |

| CMDVCC5<br>CMDVCC3 | 4<br>5         | I    | Figure 18             | Logic low on one or both of these pins will cause the LDO to ramp the Vcc supply to the smart card and smart card interface to the value described in the following table.  CMDVCC5 CMDVCC3 Vcc Output Voltage  0 0 1.8 V 0 1 5.0 V 1 0 3.0 V 1 LDO Off                                                                                                       |

| RSTIN              | 6              | ı    | Figure 18             | Note: See the description of the Card Power Supply for more detail on the operation of CMDVCC5 and CMDVCC3.  Reset Input: This signal is the reset command to the                                                                                                                                                                                             |

|                    |                |      | rigule 10             | card.                                                                                                                                                                                                                                                                                                                                                         |

| RDY                | 8              |      | Figure 12             | Signal to controller indicating the 73S8009C is ready because $V_{\text{CC}}$ is above the required value after $\overline{\text{CMDVCC5}}$ and/or $\overline{\text{CMDVCC3}}$ is asserted low. A 20 k $\Omega$ pull-up resistor to $V_{\text{DD}}$ is provided internally. Pull-up is disabled in Power down state and CS=0 modes.                           |

| Pin<br>Name | Pin<br>(QFN32) | Туре | Equivalent<br>Circuit | Description                                                                                                                                                                                                                                                                                                                                     |

|-------------|----------------|------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ON_OFF      | 24             | l    | Figure 11             | Power control pin. Connected to normally open SPST switch to ground. Closing switch for duration greater than de-bounce period will turn 73S8009C circuit "on." If 73S8009C is "on," closing switch will turn 73S8009C to "off" state after the de-bounce period and OFF_REQ/OFF_ACK handshake.                                                 |

| OFF_REQ     | 11             | 0    | Figure 19             | Digital output. Request to the host system controller to turn the 73S8009C off. If ON_OFF switch is closed (to ground) for de-bounce duration and circuit is "on," OFF_REQ will go high (Request to turn OFF). Connected to OFF_ACK via 100 k $\Omega$ internal resistor.                                                                       |

| OFF_ACK     | 9              | l    | Figure 18             | Setting OFF_ACK high will power "off" all analog functions and disconnect the 73S8009C from $V_{BAT}$ or $V_{PC}$ . The pin has an internal 100 k $\Omega$ resistor connection to OFF_REQ so that when not connected or no host interaction is required, the Acknowledge will be true and the circuit will turn "off" immediately with OFF_REQ. |

## 2 Electrical Specifications

This section provides the following:

- Absolute maximum ratings

- Recommended operating conditions

- Smart card interface requirements

- Digital signals characteristics

- Voltage / temperature fault detection circuits

- Thermal characteristics

### 2.1 Absolute Maximum Ratings

Table 2 lists the maximum operating conditions for the 73S8009C. Permanent device damage may occur if absolute maximum ratings are exceeded. Exposure to the extremes of the absolute maximum rating for extended periods may affect device reliability. The smart card interface pins are protected against short circuits to  $V_{\rm CC}$ , ground, and each other.

**Table 2: Absolute Maximum Device Ratings**

| Parameter                           | Rating                              |

|-------------------------------------|-------------------------------------|

| Supply Voltage V <sub>BUS</sub>     | -0.5 to 6.6 VDC                     |

| Supply Voltage V <sub>BAT</sub>     | -0.5 to 6.6 VDC                     |

| Supply Voltage V <sub>PC</sub>      | -0.5 to 6.6 VDC                     |

| $V_{DD}$                            | -0.5 to 4.0 VDC                     |

| Input Voltage for Digital Inputs    | -0.3 to (V <sub>DD</sub> +0.5) VDC  |

| Storage Temperature                 | -60 to 150°C                        |

| Pin Voltage (except card interface) | -0.3 to (V <sub>DD</sub> + 0.5) VDC |

| Pin Voltage (card interface)        | -0.3 to (V <sub>CC</sub> + 0.3) VDC |

| Pin Voltage, LIN pin                | 0.3 to 6.5 VDC                      |

| ESD Tolerance – Card interface pins | +/- 6 kV                            |

| ESD Tolerance – Other pins          | +/- 2 kV                            |

| Pin Current, except LIN             | ± 200 mA                            |

| Pin Current, LIN                    | + 500 mA in, -200 mA out            |

Note: ESD testing on smart card pins is HBM condition, 3 pulses, each polarity referenced to ground. Note: Smart Card pins are protected against shorts between any combinations of Smart Card pins.

# 2.2 Recommended Operating Conditions

Function operation should be restricted to the recommended operating conditions specified in Table 3.

**Table 3: Recommended Operating Conditions**

| Parameter                       | Rating           |

|---------------------------------|------------------|

| Supply voltage V <sub>PC</sub>  | 2.7 to 6.5 VDC   |

| Supply Voltage V <sub>BUS</sub> | 4.4 to 5.5 VDC   |

| Supply Voltage V <sub>BAT</sub> | 4.0 to 6.5 VDC   |

| Ambient operating temperature   | -40 °C to +85 °C |

## 2.3 Smart Card Interface Requirements

Table 4 lists the 73S8009C Smart Card interface requirements.

**Table 4: DC Smart Card Interface Requirements**

| Symbol             | Parameter                                      | Condition                                                                                   | Min  | Nom  | Max  | Unit |

|--------------------|------------------------------------------------|---------------------------------------------------------------------------------------------|------|------|------|------|

|                    | wer Supply (V <sub>cc</sub> ) Regulator        |                                                                                             |      |      | 1    | 1    |

| General            | Conditions: -40C < 85C, 2.7                    |                                                                                             |      | ı    | T    | 1    |

|                    |                                                | Inactive mode                                                                               | -0.1 | _    | 0.1  | V    |

|                    |                                                | Inactive mode I <sub>CC</sub> = 1 mA                                                        | -0.1 | _    | 0.4  | V    |

|                    |                                                | Active mode; I <sub>CC</sub> <65 mA; 5 V                                                    | 4.65 | _    | 5.25 | V    |

|                    |                                                | Active mode; I <sub>CC</sub> < 65 mA; 3 V                                                   | 2.85 | _    | 3.15 | V    |

|                    |                                                | Active mode; I <sub>CC</sub> < 40 mA; 1.8 V                                                 | 1.68 | _    | 1.92 | V    |

|                    |                                                | Active mode; single pulse of 100 mA for 2 μs; 5 V, fixed load = 25 mA                       | 4.6  | _    | 5.25 | V    |

| $V_{CC}$           | Card supply voltage including ripple and noise | Active mode; single pulse of 100 mA for 2 μs; 3 V, fixed load = 25 mA                       | 2.76 | _    | 3.15 | V    |

|                    |                                                | Active mode; current pulses of 40nAs with peak  I <sub>CC</sub>   <200 mA, t <400 ns; 5 V   | 4.6  | _    | 5.25 | V    |

|                    |                                                | Active mode; current pulses of 40nAs with peak  I <sub>CC</sub>   <200 mA, t <400 ns; 3 V   | 2.7  | _    | 3.15 | V    |

|                    |                                                | Active mode; current pulses of 20nAs with peak  I <sub>CC</sub>   <100 mA, t <400 ns; 1.8 V | 1.62 | _    | 1.92 | V    |

| $V_{CCrip}$        | V <sub>CC</sub> ripple                         | f <sub>RIPPLE</sub> = 20 kHz – 200 MHz                                                      |      | _    | 350  | mV   |

| I <sub>CCmax</sub> | Card supply output                             | Static load current, V <sub>CC</sub> >1.65                                                  |      | _    | 40   | mA   |

|                    | current                                        | Static load current, V <sub>CC</sub> >4.6 or 2.7 volts as selected                          |      | _    | 65   | mA   |

| I <sub>CCF</sub>   | I <sub>CC</sub> fault current                  | Class A, B (5 V and 3 V)                                                                    | 75   | _    | 150  | mA   |

|                    |                                                | Class C (1.8 V)                                                                             | 55   | _    | 130  | mA   |

| I <sub>SC</sub>    | Maximum current prior to shut-down             | Load current limit prior to Vcc shut-down                                                   | 80   | _    | 150  | mA   |

|                    |                                                | Load current limit prior to Vcc<br>shut-down for Vcc=1.8 V                                  | 60   | _    | 130  | mA   |

| Vs                 | Vcc slew rate, rise and fall                   | C = 0.5 μF                                                                                  | 0.10 | 0.30 | 0.70 | V/µs |

| $V_{rdy}$        | Vcc ready voltage (RDY                             | 5 V operation, Vcc rising                                | 4.6  | _    | _    | V  |

|------------------|----------------------------------------------------|----------------------------------------------------------|------|------|------|----|

|                  | = 1)                                               | 3 V operation, Vcc rising                                | 2.75 | _    | _    | V  |

|                  |                                                    | 1.8 V operation, Vcc rising                              | 1.65 | _    | _    | V  |

| V <sub>CCF</sub> | RDY = 0                                            | V <sub>CC</sub> = 5 V                                    | _    | _    | 4.6  | V  |

|                  | (V <sub>CC</sub> voltage supervisor threshold)     |                                                          |      |      |      |    |

| C <sub>VPC</sub> | External filter cap for V <sub>PC</sub>            |                                                          | 8.0  | 10.0 | 12.0 | μF |

| Сvр              | External filter cap for VP                         |                                                          | 2.0  | 4.7  | 6.8  | μF |

| C <sub>F</sub>   | External filter capacitor (V <sub>CC</sub> to GND) | $C_F$ should be ceramic with low ESR (<100 m $\Omega$ ). | 0.2  | 0.47 | 1.0  | μF |

| $C_{VDD}$        | VDD filter capacitor                               |                                                          | 0.2  | _    | 1.0  | μF |

| lvpcoff          | VPC supply current for Vcc=0                       | Vpc=5 V, Vcc=0 V (off)                                   |      |      | 400  | μА |

| Symbol                            | Parameter                                                                                                                                                        | Condition                                                                                                           | Min                   | Nom      | Max                   | Unit |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------|----------|-----------------------|------|

|                                   |                                                                                                                                                                  | als: I/O, AUX1, AUX2, and h                                                                                         |                       |          |                       |      |

|                                   |                                                                                                                                                                  | nd V <sub>INACT</sub> requirements do n                                                                             |                       | o I/OUC, | ı                     |      |

| $V_{OH}$                          | Output level, high (I/O, AUX1, AUX2)                                                                                                                             | I <sub>OH</sub> =0                                                                                                  | 0.9 * V <sub>CC</sub> | _        | V <sub>CC</sub> +0.1  | V    |

| V <sub>OH</sub>                   | Output level, high (I/OUC,                                                                                                                                       | I <sub>OH</sub> = -40 μA                                                                                            | 0.75 V <sub>CC</sub>  | _        | V <sub>CC</sub> +0.1  | V    |

|                                   | AUX1UC, AUX2UC)                                                                                                                                                  | I <sub>OH</sub> =0                                                                                                  | $0.9 V_{DD}$          | _        | V <sub>DD</sub> +0.1  | V    |

| $V_{OL}$                          | Output level, low (I/O,                                                                                                                                          | $I_{OH} = -40 \mu A$                                                                                                | $0.75  V_{DD}$        | _        | V <sub>DD</sub> +0.1  | V    |

|                                   | AUX1, AUX2)                                                                                                                                                      | I <sub>OL</sub> =1 mA                                                                                               | _                     | _        | 0.15 *V <sub>CC</sub> | V    |

| $V_{OL}$                          | Output level, low (I/OUC, AUX1UC, AUX2UC)                                                                                                                        | I <sub>OL</sub> =1 mA                                                                                               | _                     | _        | 0.3                   | V    |

| V <sub>IH</sub>                   | Input level, high (I/O, AUX1, AUX2)                                                                                                                              |                                                                                                                     | 0.6 * V <sub>CC</sub> | _        | V <sub>CC</sub> +0.30 | V    |

| V <sub>IH</sub>                   | Input level, high (I/OUC, AUX1UC, AUX2UC)                                                                                                                        |                                                                                                                     | 0.6 * V <sub>DD</sub> | _        | V <sub>DD</sub> +0.30 | V    |

| $V_{IL}$                          | Input level, low (I/O,<br>AUX1, AUX2)                                                                                                                            |                                                                                                                     | -0.15                 | _        | 0.2 * V <sub>CC</sub> | V    |

| $V_{IL}$                          | Input level, low (I/OUC, AUX1UC, AUX2UC)                                                                                                                         |                                                                                                                     | -0.15                 | _        | 0.2 * V <sub>DD</sub> | V    |

| V <sub>INACT</sub>                | Output voltage when                                                                                                                                              | I <sub>OL</sub> = 0                                                                                                 | _                     | _        | 0.1                   | V    |

|                                   | outside of session                                                                                                                                               | I <sub>OL</sub> = 1 mA                                                                                              | _                     | _        | 0.3                   | V    |

| I <sub>LEAK</sub>                 | Input leakage                                                                                                                                                    | $V_{IH} = V_{CC}$                                                                                                   | _                     | _        | 10                    | μА   |

| I <sub>IL</sub>                   | Input current, low (I/O, AUX1, AUX2)                                                                                                                             | V <sub>IL</sub> = 0                                                                                                 | _                     | _        | 0.65                  | mA   |

| I <sub>IL</sub>                   | Input current, low (I/OUC, AUX1UC, AUX2UC)                                                                                                                       | V <sub>IL</sub> = 0                                                                                                 | _                     | _        | 0.7                   | mA   |

| I <sub>SHORTL</sub>               | Short circuit output current                                                                                                                                     | For output low, shorted to $V_{CC}$ through 33 $\Omega$                                                             | _                     | _        | 15                    | mA   |

| I <sub>SHORTH</sub>               | Short circuit output current                                                                                                                                     | For output high, shorted to ground through 33 $\Omega$                                                              | _                     | _        | 15                    | mA   |

| t <sub>R</sub> , t <sub>F</sub>   | Output rise time, fall times                                                                                                                                     | For I/O, AUX1, AUX2,<br>C <sub>L</sub> = 80pF, 10% to 90%.<br>For I/OUC, AUX1UC,<br>AUX2UC, CL=50Pf, 10%<br>to 90%. | _                     | _        | 100                   | ns   |

| t <sub>IR</sub> , t <sub>IF</sub> | Input rise, fall times                                                                                                                                           |                                                                                                                     | _                     | _        | 1                     | μS   |

| R <sub>PU</sub>                   | Internal pull-up resistor                                                                                                                                        | Output stable for >200ns                                                                                            | 8                     | 11       | 14                    | kΩ   |

| $FD_MAX$                          | Maximum data rate                                                                                                                                                |                                                                                                                     | _                     | _        | 1                     | MHz  |

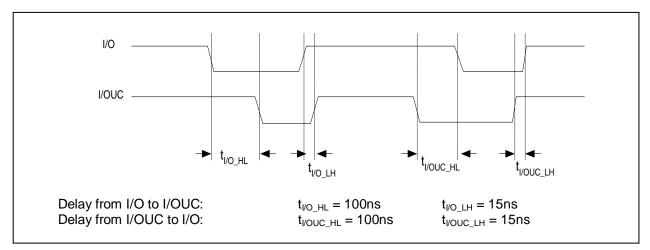

| $T_{\text{FDIO}}$                 | Delay, I/O to I/OUC, AUX1                                                                                                                                        | Edge from master to                                                                                                 | 60                    | 100      | 200                   | ns   |

| $T_{RDIO}$                        | to AUX1UC, AUX2 to<br>AUX2UC,I/OUC to I/O,<br>AUX1UC to AUX1, AUX2UC<br>to AUX2 (respectively falling<br>edge to falling edge and<br>rising edge to rising edge) | slave, measured at 50%                                                                                              | _                     | 15       | _                     | ns   |

| C <sub>IN</sub>                   | Input capacitance                                                                                                                                                |                                                                                                                     | _                     | _        | 10                    | pF   |

| Symbol                          | Parameter                              | Condition                                                          | Min                   | Nom | Max                      | Unit |

|---------------------------------|----------------------------------------|--------------------------------------------------------------------|-----------------------|-----|--------------------------|------|

| Reset a                         | nd Clock for card interface,           | RST, CLK                                                           |                       |     |                          |      |

| V <sub>OH</sub>                 | Output level, high                     | I <sub>OH</sub> =-200 μA                                           | 0.9 * V <sub>CC</sub> | _   | $V_{CC}$                 | V    |

| $V_{OL}$                        | Output level, low                      | I <sub>OL</sub> =200 μA                                            | 0                     | _   | 0.15<br>*V <sub>CC</sub> | V    |

| V <sub>INACT</sub>              | Output voltage when outside of session | I <sub>OL</sub> = 0                                                | _                     | _   | 0.1                      | V    |

| I <sub>RST_LIM</sub>            | Output current limit, RST              |                                                                    | _                     | _   | 30                       | mA   |

| I <sub>CLK_LIM</sub>            | Output current limit, CLK              |                                                                    | _                     | _   | 70                       | mA   |

| t <sub>R</sub> , t <sub>F</sub> | Output rise time, fall time            | C <sub>L</sub> = 35pF for CLK, 10% to 90%                          | _                     | _   | 12                       | ns   |

|                                 |                                        | C <sub>L</sub> = 200pF for RST, 10% to 90%                         | -                     | _   | 100                      | ns   |

| δ                               | Duty cycle for CLK                     | $C_L$ =35pF, $F_{CLK} \le 20$ MHz, CLKIN duty cycle is 48% to 52%. | 45                    | _   | 55                       | %    |

# 2.4 Digital Signals Characteristics

Table 5 lists the 73S8009C digital signals characteristics.

**Table 5: Digital Signals Characteristics**

| Symbol                     | Parameter                                         | Condition                | Min                    | Nom      | Max            | Unit        |

|----------------------------|---------------------------------------------------|--------------------------|------------------------|----------|----------------|-------------|

| Digital I/O<br>(except for | r I/OUC, AUX1UC, AUX2UC;                          | see Smart Card Interfac  | ce Requirem            | ents for | those spec     | ifications) |

| V <sub>IL</sub>            | Input Low Voltage                                 |                          | -0.3                   | _        | 0.8            | V           |

| VILOFFACK                  | Input low voltage for OFF_ACK pin                 | OFF_REQ pin = VDD        | -0.3                   | -        | 0.7            | V           |

| V <sub>IH</sub>            | Input High Voltage                                |                          | 1.8                    | -        | $V_{DD} + 0.3$ | V           |

| $V_{OL}$                   | Output Low Voltage                                | $I_{OL} = 2 \text{ mA}$  |                        | 1        | 0.45           | V           |

| V <sub>OH</sub>            | Output High Voltage                               | $I_{OH} = -1 \text{ mA}$ | V <sub>DD</sub> - 0.45 | -        |                | V           |

| R <sub>OUT</sub>           | Pull-up resistor; OFF, RDY                        |                          | 14                     | 20       | 26             | kΩ          |

| R <sub>ACK</sub>           | Resistor between OFF_REQ and 0FF_ACK              |                          | 70                     | 100      | 130            | kΩ          |

| I <sub>IL1</sub>           | Input Leakage Current                             | $GND < V_{IN} < V_{DD}$  | _                      | _        | 5              | μA          |

| t <sub>SL</sub>            | Time from CS goes high to interface active        |                          | 50                     | -        | -              | ns          |

| t <sub>DZ</sub>            | Time from CS goes low to interface inactive, Hi-Z |                          | 50                     | -        | -              | ns          |

| t <sub>IS</sub>            | Set-up time, control signals to CS rising edge    |                          | 50                     | ı        | _              | ns          |

| t <sub>SI</sub>            | Hold time, control signals from CS rising edge    |                          | _                      | -        | 50             | ns          |

| t <sub>ID</sub>            | Set-up time, control signals to CS fall           |                          | 50                     | -        | _              | ns          |

| t <sub>DI</sub>            | Hold time, control signals from CS fall           |                          | _                      | -        | 50             | ns          |

#### 2.5 DC Characteristics

Table 6 lists the DC characteristics.

**Table 6: DC Characteristics**

| Symbol               | Parameter                                | Condition                                       | Min | Nom  | Max | Unit |

|----------------------|------------------------------------------|-------------------------------------------------|-----|------|-----|------|

| $V_{DD}$             | V <sub>DD</sub> Supply Voltage           | 2.7v < VPC < 6.5v, I <sub>VDDEXT</sub> < 40 mA. | 3.0 | 3.3  | 3.6 | V    |

| I <sub>DDEXT</sub>   | V <sub>DD</sub> Current to External Load |                                                 | _   | _    | 40  | mA   |

| I <sub>VPC</sub>     | Supply Current                           | $Vpc = 2.7V$ , $V_{CC}$ off, $I_{DD} = 0$       | -   | 1.7  | _   | mA   |

|                      |                                          | $Vpc = 3.3V$ , $V_{CC}$ off, $I_{DD} = 0$       | _   | 1.1  | _   | mA   |

|                      |                                          | $Vpc = 5.0V$ , $V_{CC}$ off, $I_{DD} = 0$       | -   | 0.7  | _   | mA   |

|                      |                                          | OFF mode                                        | -   | 0.01 | 1   | μΑ   |

| VBUS <sub>ON</sub>   | VBUS detection threshold                 | V <sub>DD</sub> =3.3 V                          | 3.5 | 3.9  | 4.3 | V    |

| VBUS <sub>IDIS</sub> | VBUS discharge current                   |                                                 | 0.5 | 1.0  | 3   | mA   |

| VBUS <sub>STBY</sub> | VBUS standby current                     |                                                 |     | 370  | 500 | μА   |

# 2.6 Voltage / Temperature Fault Detection Circuits

Table 7 lists the voltage / temperature fault detection circuits.

**Table 7: Voltage / Temperature Fault Detection Circuits**

| Symbol              | Parameter                         | Condition               | Min | Nom | Max | Unit |

|---------------------|-----------------------------------|-------------------------|-----|-----|-----|------|

| $IV_{Pmax}$         | V <sub>P</sub> over-current fault |                         | _   | _   | 150 | mA   |

| I <sub>CCF</sub>    | Card overcurrent fault            |                         | 80  | _   | 150 | mA   |

| I <sub>CCF1P8</sub> | Card overcurrent fault            | V <sub>CC</sub> = 1.8 V | 60  | _   | 130 | mA   |

#### 2.7 Thermal Characteristics

Table 8 lists the thermal characteristics.

**Table 8: Thermal Characteristics**

| Symbol | Parameter                                  | Condition | Min | Nom | Max | Unit |

|--------|--------------------------------------------|-----------|-----|-----|-----|------|

| Tj     | Junction temperature                       |           | _   | _   | 125 | °C   |

| θ ја   | Thermal Resistance,<br>Junction-to-Ambient |           | _   | 70  | _   | °C/W |

| θ јс   | Thermal Resistance,<br>Junction-to-case    |           | _   | 6   | _   | °C/W |

# 3 Applications Information

This section provides general usage information for the design and implementation of the 73S8009C. The documents listed in Related Documentation provide more detailed information.

## 3.1 Example 73S8009C Schematics

Figure 3 shows a typical application schematic for the implementation of the 73S8009C with a main system switch. Note that minor changes may occur to the reference material from time to time and the reader is encouraged to contact Teridian for the latest information.

Figure 3: Typical 73S8009C Application Schematic

### 3.2 Power Supply and Converter

The power supply and converter circuit takes power from any one of three sources;  $V_{PC}$ ,  $V_{BUS}$ , and  $V_{BAT}$ .  $V_{PC}$  is specified to range from 2.7 to 6.5 volts and would typically be supplied by a single cell battery with a voltage range of 2.7 to approximately 3.1 volts.  $V_{PC}$  is also appropriate for system supplies of 3.3 or 5 volts.  $V_{BUS}$  is typically supplied by a connected USB cable and ranges in value from 4.5 to 5.5 volts (6.5 V maximum).  $V_{BAT}$  is expected to be supplied from a battery of two series connected cells with a voltage value of 4.0 V to 6.5 V.  $V_{BAT}$  and  $V_{BUS}$  are connected to  $V_{PC}$  by two FET switches configured as an SPDT switch (break-before-make). They are not enabled at the same time.  $V_{BUS}$  is automatically selected in lieu of  $V_{BAT}$  when  $V_{BUS}$  is present. If  $V_{PC}$  is provided and  $V_{BAT}$  or  $V_{BUS}$  are also used, the source of  $V_{PC}$  must be diode isolated from the  $V_{PC}$  pin to prevent current flow from  $V_{BAT}$  or  $V_{BUS}$  into the  $V_{PC}$  source.

The power supplied to the  $V_{PC}$  is up-converted to the voltage  $V_P$  utilizing an inductive, step-up converter. A series power inductor (nominal value = 10  $\mu$ H) is connected from  $V_{PC}$  to LIN, and a 10  $\mu$ F filter capacitor plus a 0.1  $\mu$ F capacitor must be connected to  $V_{PC}$ .  $V_P$  requires a 4.7  $\mu$ F filter capacitor and will have a nominal value of 5.5 V during normal operation.  $V_P$  is used by the smartcard interface circuits (CLK, RST, IO, AUX1, and AUX2) and is the source of the regulated smart card supply  $V_{CC}$ .  $V_{CC}$  can be programmed for values of 5 V, 3 V, and 1.8 V.  $V_{DD}$  is also produced from  $V_P$ .  $V_{DD}$  is used by the 73S8009C circuit for logic, input/output buffering, and analog functions as well as being capable of supplying up to 40 mA of current to external devices. Figure 4 shows the block diagram of the 73S8009C.

#### 3.3 Power ON/OFF

When no power is applied to the V<sub>BUS</sub> pin, a power ON/OFF function is provided such that the circuit will be inoperative during the "OFF" state, consuming minimum current from V<sub>PC</sub> and V<sub>BAT</sub>. If V<sub>BUS</sub> power is supplied, the functions of the ON/OFF switch and circuitry are overridden and the 73S8009C is in the "ON" state with V<sub>P</sub> and V<sub>DD</sub> available. Without V<sub>BUS</sub> applied, and in the OFF state, the circuit responds only to the ON OFF pin. The ON OFF pin shall be connected to a SPST switch to ground. If the circuit is OFF and the switch is closed for a de-bounce period of 50-100ms, the circuit shall go into the "ON" state wherein all functions are operating in normal fashion. If the circuit is in the "ON" state and the ON OFF pin is connected to ground for a period greater than the de-bounce period, OFF REQ will be asserted high and held. Typically, the OFF REQ signal is presented to a host controller that will assert OFF\_ACK high when it has completed all shutdown activities. When OFF\_ACK is set high, the circuit will de-activate the smart card interface if required and turn off all analog functions and the V<sub>DD</sub> supply for the logic and companion circuits. The OFF\_ACK pin is connected internally to OFF\_REQ with a resistor such that if OFF ACK is unconnected, the action of OFF REQ will assert OFF ACK high. In this configuration, the circuit shall go into the "OFF" state immediately upon OFF\_REQ = 1. The default state upon application of power is the "OFF" state unless power is supplied to the V<sub>BUS</sub> supply. Note that at any time. the controller may assert OFF ACK and the 73S8009C will go into the "OFF" state (when V<sub>BUS</sub> is not present.)

If power is applied to both  $V_{BAT}$  and  $V_{BUS}$ , the circuit will automatically consume power from only the  $V_{BUS}$  source. The circuit will be unconditionally "ON" when  $V_{BUS}$  is applied. If the  $V_{BUS}$  source is removed, the circuit will switchover to the VBAT input supply and remain in the "ON" state. The controller circuit firmware is required to assert OFF\_ACK based on no activity or  $V_{BUS}$  removal to reduce battery power consumption. When operating from  $V_{BUS}$ , and not calling for  $V_{CC}$ , the step-up converter becomes a simple switch connecting  $V_{BUS}$  to  $V_P$  in order to save power. This condition is appropriate for the USB "SUSPEND" state. The USB "SUSPEND" state requires the power supply current to be less than 500  $\mu$ A. In order to obtain and meet this low current limitation, the companion controller must be configured into a power-down condition using less than 20  $\mu$ A from  $V_{DD}$ .

Note: When using the VBUS input as the sole power source for an 'always on' configuration (ON\_OFF input not used), the OFF\_ACK and ON\_OFF inputs must be connected to ground.

Figure 4: 73S8009C Logical Block Diagram

### 3.4 System Controller Interface

Four separate digital inputs and two outputs allow direct control of the card interface from the host:

- Pin CS: Chip select control.

- Pin CMDVCC3 and/or CMDVCC5: When low, starts an activation sequence.

- Pin RSTIN: controls the card RST signal.

- Pin RDY: Indicates when smart card power supply is stable and ready.

- Pin OFF: Indicator of card presence and any card fault conditions.

Interrupt output to the host: When the card is not activated, the  $\overline{OFF}$  pin informs the host about the card presence only (Low = No card in the reader, high = card inserted). When  $\overline{CMDVCC}$  ( $\overline{3}/\overline{5}$  signals) is/are set low (card activation sequence requested from the host), low level on  $\overline{OFF}$  means a fault has been detected (e.g. card removal during card session, or voltage fault, or thermal / over-current fault) that automatically initiates a deactivation sequence. The smart card pass through signals are enabled when the RDY conditions are met.

### 3.5 Card Power Supply and Voltage Supervision

The 73S8009C smart card interface IC incorporates an LDO voltage regulator for the card power supply,  $V_{CC}$  ( $V_P$  to  $V_{CC}$  conversion uses an internal LDO). The voltage output is controlled by the digital input sequence of  $\overline{CMDVCC3}$  and  $\overline{CMDVCC5}$ . This regulator is able to provide 1.8V, 3V or 5V card voltage sourced from the  $V_P$  power supply. Internal digital circuitry is also powered by the  $V_P$  power supply (except for the ON/OFF circuitry which is powered from  $V_{PC}$ ). A card deactivation sequence is forced upon fault detected by an overcurrent condition or card removal event. The voltage regulator can provide a card current of 65 mA in compliance with EMV 4.1 for 3-V and 5-V cards and 40 mA for 1.8 V cards. The signals  $\overline{CMDVCC3}$  and  $\overline{CMDVCC5}$  control the turn-on, output voltage value, and turn-off of  $V_{CC}$ . When either signal is asserted low,  $V_{CC}$  will ramp to the selected value or if both signals are asserted low (within 400ns of each other),  $V_{CC}$  will ramp to 1.8 V. These signals are edge triggered. If  $\overline{CMDVCC5}$  is asserted low (to command  $V_{CC}$  to be 5 V) and at a much later time (greater than 2  $\mu$ s, typically),  $\overline{CMDVCC3}$  is asserted low, it will be ignored (and vice versa.)

At the assertion (low) of either or both  $\overline{CMDVCC}$  ( $\overline{3}/\overline{5}$  signals),  $V_{CC}$  will rise to the requested value. When  $V_{CC}$  rises to an acceptable value, and stays above that value for approximately 20  $\mu$ s, RDY will be set high. Approximately 510  $\mu$ s after the fall of  $\overline{CMDVCC}$  ( $\overline{3}/\overline{5}$ ), the circuit will check the see if  $V_{CC}$  is at or above the required minimum value (indicated by RDY=1) and if not, will begin an emergency deactivation sequence. During the 510  $\mu$ s time, card removal, or de-assertion of  $\overline{CMDVCC}$  ( $\overline{3}/\overline{5}$ ) shall also initiate an emergency deactivation sequence. The circuit provides over-current protection and limits Icc to 150 mA, maximum for self-protection. When an over-current condition is sensed, the circuit will invoke a de-activation sequence.

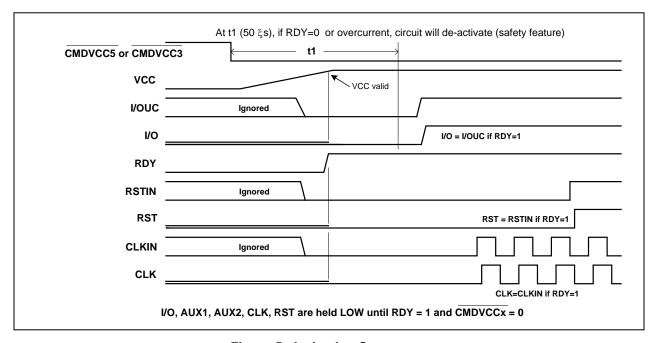

### 3.6 Activation and De-activation Sequence

The host controller is fully responsible for the activation sequencing of the smart card signals CLK, RST, I/O, AUX1 and AUX2. All these signals are held low by the 73S8009C when the card is in the deactivated state. Upon card activation (the fall of  $\overline{\text{CMDVCC}}$  ( $\overline{3}/\overline{5}$ )), all the signals are held low by the 73S8009C until RDY goes high. The host should set the signals RSTIN, I/OUC, CLKIN, AUX1UC and AUX2UC low prior to activating the card and allow RDY to go high before transitioning any of these signals. In order to initiate activation, the card must be present and  $\overline{\text{OFF}}$  must be high.

Figure 5: Activation Sequence

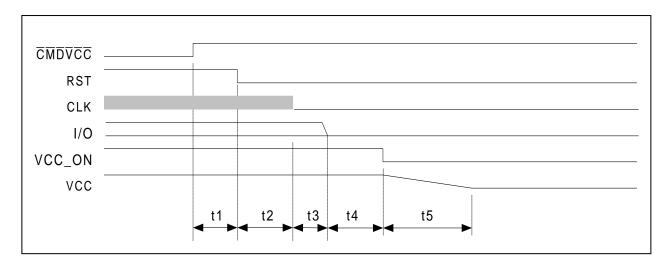

Deactivation is initiated either by the system controller by setting both  $\overline{\text{CMDVCC}}$  ( $\overline{3}/\overline{5}$ ) high, or automatically in the event of hardware faults or assertion of the OFF\_ACK signal. Hardware faults are over-current, under-voltage, and card extraction during the session. The host can manage the I/O signals, CLKIN, RSTIN, and  $\overline{\text{CMDVCC}}$  ( $\overline{3}/\overline{5}$ ) to create other de-activation sequences for non-emergency situations.

The following steps show the deactivation sequence and the timing of the card control signals when the system controller sets the CMDVCC(x)B high:

- 1. RST goes low at the end of time t1.

- 2. De-assert CLK at the end of time t2.

- 3. I/O goes low at the end of time t3. Exit reception mode.

- 4. De-assert internal VCC\_ON at the end of time t4. After a delay, VCC is de-asserted.

Note: Since the 73S8009C does not control the waveshape of CLK (it is determined by the input form the host CLKIN), there is no guarantee that the duty cycle of the last CLK high pulse will conform to duty cycle requirements during an emergency deactivation.

Figure 6: Deactivation Sequence

### 3.7 OFF and Fault Detection

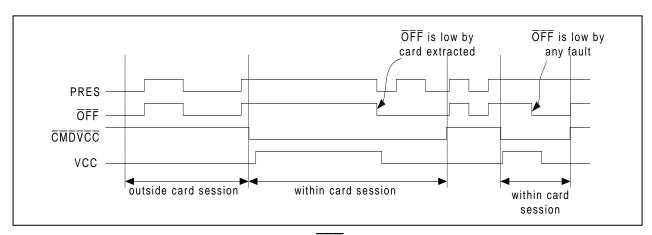

There are two different cases that the system controller can monitor the  $\overline{\text{OFF}}$  signal: to query regarding the card presence outside card sessions, or for fault detection during card sessions.

Outside a card session: In this condition,  $\overline{\text{CMDVCC}}$  ( $\overline{3}/\overline{5}$ ) are always high,  $\overline{\text{OFF}}$  is low if the card is not present, and high if the card is present. Because it is outside a card session, no fault detection can occur and it will not act upon the  $\overline{\text{OFF}}$  signal. No deactivation is required during this time.

During a card session:  $\overline{\text{CMDVCC3}}$  and/or  $\overline{\text{CMDVCC5}}$  is always low, and  $\overline{\text{OFF}}$  falls low if the card is extracted or if any fault detection is detected. At the same time that  $\overline{\text{OFF}}$  is set low, the sequencer starts the deactivation process and the host should stop all transitions on the signal lines.

Figure 7 shows the timing diagram for the signals  $\overline{\text{CMDVCC}}$  ( $\overline{3}/\overline{5}$ ), PRES, and  $\overline{\text{OFF}}$  during a card session and outside the card session.

Figure 7: OFF Activity

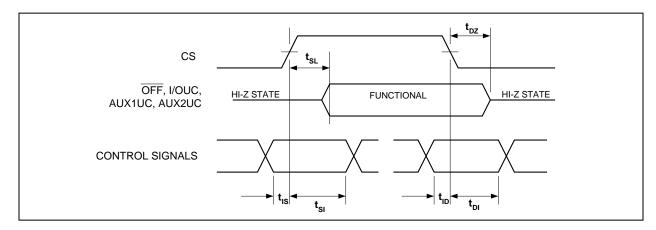

#### 3.8 Chip Selection

The CS pin allows multiple circuits to operate in parallel, driven from the same host control bus. When CS is high, the pins RSTIN,  $\overline{CMDVCC5}$ ,  $\overline{CMDVCC3}$  and CLKIN control the chip as described. The pins I/OUC, AUX1UC, and AUX2UC have 11 k $\Omega$  pull-up resistors and operate to transfer data to the smart card via I/O, AUX1, and AUX2 when the smart card is activated. The signals  $\overline{OFF}$  and RDY have 20 k $\Omega$  pull-up resistors.

When CS goes low, the states of the pins RSTIN,  $\overline{\text{CMDVCC}}$ 5,  $\overline{\text{CMDVCC}}$ 6, and CLKIN are latched and held internally. The pull-up for pins I/OUC, AUX1UC, and AUX2UC become a very weak pull-up of approximately 3  $\mu$ A. No transfer of data is possible between I/OUC, AUX1UC, AUX2UC and the smart-card signals I/O, AUX1, and AUX2. The signals  $\overline{\text{OFF}}$  and RDY are set to high impedance and the internal pull-up resistors of 20 k $\Omega$  are disconnected. With regard to de-activation, CS does not affect the operation of the fault sensing circuits and card sense input.

Figure 8: CS Timing Definitions

### 3.9 I/O Circuitry and Timing

The states of the I/O, AUX1, and AUX2 pins are low after power on reset and they are in high when the activation sequencer turns on the I/O reception state. See the Activation and De-activation Sequence section for more details on when the I/O reception is enabled. The states of I/OUC, AUX1UC, and AUX2UC are high after power on reset.

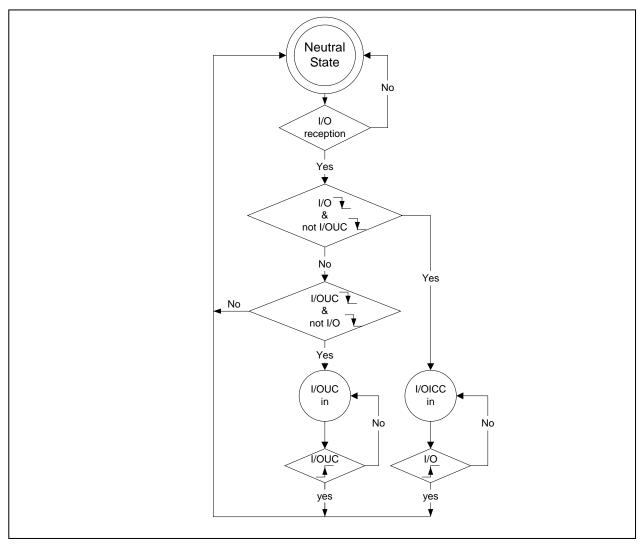

Within a card session and when the I/O reception state is turned on, the first I/O line on which a falling edge is detected becomes the input I/O line and the other becomes the output I/O line. When the input I/O line rising edge is detected, then both I/O lines return to their neutral state. Figure 9 shows the state diagram of how the I/O and I/OUC lines are managed to become input or output.

Figure 9: I/O and I/OUC State Diagram

The delay between the I/O signals is shown in Figure 10.

Figure 10: I/O - I/OUC Delays - Timing Diagram

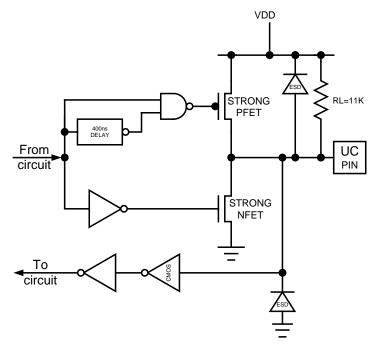

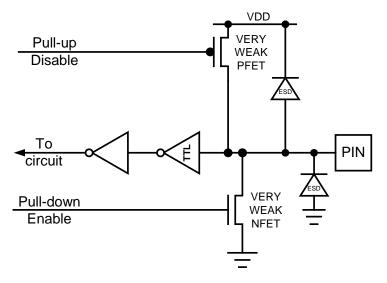

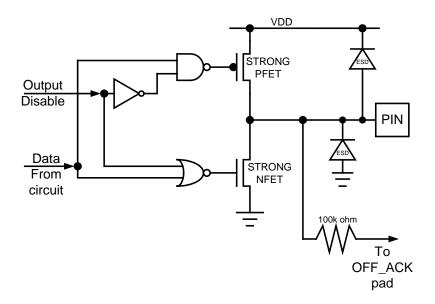

# 4 Equivalent Circuits

This section provides illustrations of circuits equivalent to those described in the Pinout section.

Figure 11: On\_Off Pin

Figure 12: Open Drain type – OFF and RDY

Figure 13: Power Input/Output Circuit, VDD, LIN, VPC, VCC, VP

Figure 14: Smart Card CLK Driver Circuit

Figure 15: Smart Card RST Driver Circuit

Figure 16: Smart Card IO, AUX1, and AUX2 Interface Circuit

Figure 17: Smart Card I/OUC, AUX1UC and AUX2UC Interface Circuit

Note: Pins  $\overline{\text{CMDVCC5}}$ ,  $\overline{\text{CMDVCC3}}$ , CS have the pull-up enabled. Pins RSTIN, CLKIN, PRES, EXT\_RST have the pull-down enabled. Pin OFF\_ACK has a 100 k $\Omega$  resistor connected to pin OFF\_REQ internally.

Figure 18: General Input Circuit

Notes: Strong PFET or NFET is approximately 100  $\Omega$ . Very strong PFET or NFET is approximately 50  $\Omega$ .

Medium strength PFET is approximately 1 k $\Omega$ .

Very weak PFET or NFET is approximately 1  $M\Omega$ .

The diodes represent ESD protection devices that will conduct current if forward biased.

Figure 19: OFF\_REQ Interface Circuit

# 5 Mechanical Drawings

Figure 20: 32-Pin QFN Package Dimensions

# 6 Ordering Information

Table 9 lists the order numbers and packaging marks used to identify 73S8009C products.

**Table 9: Order Numbers and Packaging Marks**

| Part Description                                   | Order Number     | Packaging Mark |

|----------------------------------------------------|------------------|----------------|

| 73S8009C-32QFN<br>32-pin Lead-Free QFN             | 73S8009C-32IM/F  | 73S8009C       |

| 73S8009C-32QFN<br>32-pin Lead-Free QFN Tape / Reel | 73S8009C-32IMR/F | 73S8009C       |

## 7 Related Documentation

The following 73S8009C document is available from Teridian Semiconductor Corporation:

73S8009C Data Sheet 73S8009C Demo Board User Manual

## 8 Contact Information

For more information about Teridian Semiconductor products or to check the availability of the 73S8009C, contact us at:

6440 Oak Canyon Road Suite 100 Irvine, CA 92618-5201

Telephone: (714) 508-8800 FAX: (714) 508-8878

Email: scr.support@teridian.com

For a complete list of worldwide sales offices, go to http://www.teridian.com.

### **Revision History**

| Revision | Date      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | 2/15/2007 | First publication.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.1      | 12/5/2007 | Replaced 32QFN punched with SAWN. Updated 32QFN package mark.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.2      | 1/21/2008 | Changed the dimension of the bottom view 32-pin QFN package.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.3      | 8/28/2009 | Added Pin Current, LIN to Table 2.  Added Section 2.7, Thermal Characteristics.  Added a note to the end of Section 3.6.  Added Section 4, Equivalent Circuits.  Added Section 7 Related Documentation and Section 8 Contact Information section.                                                                                                                                                                                                                                                                                                                       |

| 1.4      | 1/5/2010  | Formatted to new documentation style. Miscellaneous editorial changes.  Changed the name of the "ON/OFF" pin to "ON_OFF" throughout the document.  In Figure 1, corrected the name of the "IOUC" pin to "I/OUC".  In Table 1, corrected the OFF_ACK name, pin number and type information. In Table 7, changed "I <sub>DDmax</sub> " to "I <sub>VPmax</sub> ".  At the end of Section 3.3, added a note about using VBUS input.  In Section 3.5, deleted "A voltage supervisor checks the value of the voltage V <sub>CC</sub> " and added "and 40 mA for 1.8 V cards". |

| 1.5      | 2/4/2010  | Removed all references to the 20QFN package. Added C6 to the schematic in Figure 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Teridian Semiconductor Corporation is a registered trademark of Teridian Semiconductor Corporation. All other trademarks are the property of their respective owners.

Simplifying System Integration is a trademark of Teridian Semiconductor Corporation.

This Data Sheet is proprietary to Teridian Semiconductor Corporation (TSC) and sets forth design goals for the described product. The data sheet is subject to change. TSC assumes no obligation regarding future manufacture, unless agreed to in writing. If and when manufactured and sold, this product is sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement and limitation of liability. Teridian Semiconductor Corporation (TSC) reserves the right to make changes in specifications at any time without notice. Accordingly, the reader is cautioned to verify that a data sheet is current before placing orders. TSC assumes no liability for applications assistance.

Teridian Semiconductor Corp., 6440 Oak Canyon, Suite 100, Irvine, CA 92618 TEL (714) 508-8800, FAX (714) 508-8877, http://www.teridian.com