## **LP3988**

# Micropower, 150mA Ultra Low-Dropout CMOS Voltage Regulator With Power Good

# **General Description**

The LP3988 is a 150mA low dropout regulator designed specially to meet requirements of Portable battery-applications. The LP3988 is designed to work with a space saving, small  $1\mu F$  ceramic capacitor. The LP3988 features an Error Flag output that indicates a faulty output condition.

The LP3988's performance is optimized for battery powered systems to deliver low noise, extremely low dropout voltage and low quiescent current. Regulator ground current increases only slightly in dropout, further prolonging the battery life.

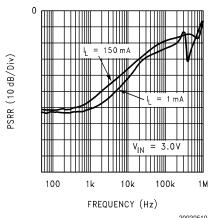

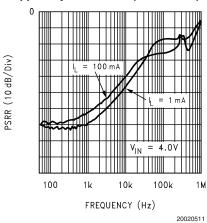

Power supply rejection is better than 60 dB at low frequencies and starts to roll off at 10 kHz. High power supply rejection is maintained down to lower input voltage levels common to battery operated circuits.

The device is ideal for mobile phone and similar battery powered wireless applications. It provides up to 150 mA, from a 2.5V to 6V input, consuming less than 1  $\mu$ A in disable mode and has fast turn-on time less than 200 $\mu$ s.

The LP3988 is available 5 pin SOT-23 package and 5 bump thin micro SMD package. Performance is specified for -40°C to +125°C temperature range and is available in 1.85, 2.5, 2.6, 2.85, 3.0 and 3.3V output voltages.

- 40dB PSRR at 10kHz

- ≤1 µA quiescent current when shut down

- Fast Turn-On time: 100 µs (typ.)

- 80 mV typ dropout with 150mA load

- -40 to +125°C junction temperature range for operation

- 1.85V, 2.5V, 2.6V, 2.85V, 3.0V, and 3.3V

### **Features**

- 5 bump thin micro SMD package

- SOT-23-5 package

- Power-good flag output

- Logic controlled enable

- Stable with ceramic and high quality tantalum capacitors

- Fast turn-on

- Thermal shutdown and short-circuit current limit

## **Applications**

- CDMA cellular handsets

- Wideband CDMA cellular handsets

- GSM cellular handsets

- Portable information appliances

- Tiny 3.3V ± 5% to 2.85V, 150mA converter

# **Key Specifications**

- 2.5 to 6.0V input range

- 150mA guaranteed output

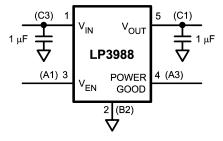

# **Typical Application Circuit**

Note: Pin numbers in parentheses indicate micro SMD package pin out

20020502

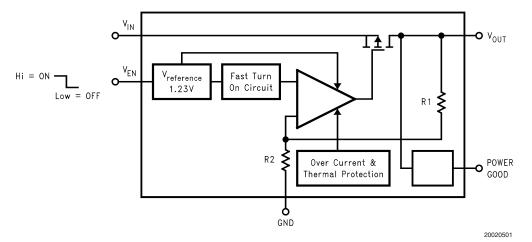

# **Block Diagram**

# **Pin Descriptions**

| Name             | micro SMD | SOT | Function                                                                                                                                        |

|------------------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>EN</sub>  | A1        | 3   | Enable Input Logic, Enable High                                                                                                                 |

| GND              | B2        | 2   | Common Ground                                                                                                                                   |

| V <sub>OUT</sub> | C1        | 5   | Output Voltage of the LDO                                                                                                                       |

| V <sub>IN</sub>  | C3        | 1   | Input Voltage of the LDO                                                                                                                        |

| Power Good       | АЗ        | 4   | Power Good Flag (output): open-drain output, connected to an external pull-up resistor. Active low indicates an output voltage out of tolerance |

|                  |           |     | condition.                                                                                                                                      |

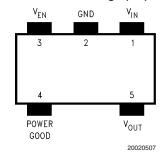

# **Connection Diagrams**

SOT-23-5 Package (MF)

Top View See NS Package Number MF05A

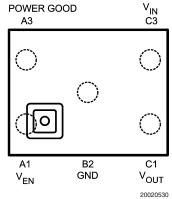

## 5 Bump micro SMD Package (TLA)

Top View

See NS Package Number TLA05

# **Ordering Information**

## SOT23-5 Package

| Output<br>Voltage (V) | Grade | LP3988 Supplied as 1000<br>Units, Tape and Reel | LP3988 Supplied as 3000<br>Units, Tape and Reel | Package Marking |

|-----------------------|-------|-------------------------------------------------|-------------------------------------------------|-----------------|

| 2.5                   | STD   | LP3988IMF-2.5                                   | LP3988IMFX-2.5                                  | LFSB            |

| 2.6                   | STD   | LP3988IMF-2.6                                   | LP3988IMFX-2.6                                  | LDJB            |

| 2.85                  | STD   | LP3988IMF-2.85                                  | LP3988IMFX-2.85                                 | LDLB            |

| 3.0                   | STD   | LP3988IMF-3.0                                   | LP3988IMFX-3.0                                  | LFAB            |

| 3.3                   | STD   | LP3988IMF-3.3                                   | LP3988IMFX-3.3                                  | LH5B            |

## 5 Bump Thin Micro SMD Package

| Output<br>Voltage (V) | Grade | LP3988 Supplied as 250<br>Units, Tape and Reel | LP3988 Supplied as 3000<br>Units, Tape and Reel |

|-----------------------|-------|------------------------------------------------|-------------------------------------------------|

| 1.85                  | STD   | LP3988ITL-1.85                                 | LP3988ITLX-1.85                                 |

| 2.6                   | STD   | LP3988ITL-2.6                                  | LP3988ITLX-2.6                                  |

| 2.85                  | STD   | LP3988ITL-2.85                                 | LP3988ITLX-2.85                                 |

# **Absolute Maximum Ratings** (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

$V_{IN}$  -0.3 to 6.5 V  $V_{OUT}$ ,  $V_{EN}$ , PowerGood(applies only to micro SMD) -0.3 V to  $(V_{IN}+0.3$ V), with 6V max Junction Temperature  $150^{\circ}$ C Storage Temperature  $-65^{\circ}$ C to  $+150^{\circ}$ C Lead Temp, Pad Temp.  $235^{\circ}$ C Power Dissipation (Note 3)

Power Dissipation (Note 3)

SOT23-5

364mW

micro SMD

355mW

ESD Rating (Note 4)

Human Body Model 2kV

Machine Model

SOT23-5 (Note 13) 150V

micro SMD 200V

## Operating Ratings (Notes 1, 2)

$V_{IN}(Note 15)$  2.5V to 6V  $V_{OUT}$ ,  $V_{EN}$  0 to  $V_{IN}$  Junction Temperature  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$

Junction-to-Ambient Thermal

Resistance ( $\theta_{JA}$ )

SOT23-5 220°C/W micro SMD 255°C/W

Maximum Power Dissipation (Note 5)

SOT23-5 250mW micro SMD 244mW

## **Electrical Characteristics**

Unless otherwise specified:  $V_{EN} = 1.8V$ ,  $V_{IN} = V_{OUT} + 0.5V$ ,  $C_{IN} = 1 \mu F$ ,  $I_{OUT} = 1 mA$ ,  $C_{OUT} = 1 \mu F$ . Typical values and limits appearing in standard typeface are for  $T_J = 25^{\circ}C$ . Limits appearing in **boldface type** apply over the entire junction temperature range for operation,  $-40^{\circ}C$  to  $+125^{\circ}C$ . (Note 6) (Note 7)

| Symbol           | Parameter                       | Conditions                                                               | Тур   | Limit |       | Units                 |

|------------------|---------------------------------|--------------------------------------------------------------------------|-------|-------|-------|-----------------------|

|                  |                                 |                                                                          |       | Min   | Max   | Ullits                |

|                  | Output Voltage                  |                                                                          |       | -2    | 2     |                       |

|                  | Tolerance                       | –20°C ≦ T <sub>J</sub> ≦ 125°C, SOT23-5                                  |       | -3    | 3     | % of                  |

|                  |                                 | -40°C ≦ T <sub>J</sub> ≦ 125°C, SOT23-5                                  |       | -3.5  | 3.5   | V <sub>OUT(nom)</sub> |

| A\/              |                                 | $-40^{\circ}$ C $\leq$ T <sub>J</sub> $\leq$ 125 $^{\circ}$ C, micro SMD |       | -3    | 3     |                       |

| $\Delta V_{OUT}$ | Line Regulation Error           | $V_{IN} = V_{OUT (NOM)} + 0.5V \text{ to } 6.0V$                         |       | -0.15 | 0.15  | %/V                   |

|                  |                                 |                                                                          |       | -0.2  | 0.2   |                       |

|                  | Load Regulation Error           | I <sub>OUT</sub> = 1 mA to 150 mA                                        |       |       | 0.005 | %/mA                  |

|                  | (Note 8)                        |                                                                          |       |       | 0.007 |                       |

|                  |                                 | $V_{IN} = V_{OUT(nom)} + 1V,$                                            | 65    |       |       |                       |

|                  |                                 | f = 1  kHz,                                                              |       |       |       |                       |

| PSRR             | Power Supply Rejection Ratio    | I <sub>OUT</sub> = 50 mA ( <i>Figure 3</i> )                             |       |       |       | dB                    |

| ronn             | Power Supply Rejection Ratio    | $V_{IN} = V_{OUT(nom)} + 1V,$                                            | 45    |       |       | д ив                  |

|                  |                                 | f = 10 kHz,                                                              |       |       |       |                       |

|                  |                                 | I <sub>OUT</sub> = 50 mA ( <i>Figure 3</i> )                             |       |       |       |                       |

| IQ               | Quiescent Current               | $V_{EN} = 1.4V$ , $I_{OUT} = 0$ mA                                       | 85    |       | 120   |                       |

|                  |                                 | $V_{EN} = 1.4V$ , $I_{OUT} = 0$ to 150 mA                                | 140   |       | 200   | μA                    |

|                  |                                 | $V_{EN} = 0.4V$                                                          | 0.003 |       | 1.0   | 1                     |

|                  | Dropout Voltage (Note 9)        | I <sub>OUT</sub> = 1 mA                                                  | 1     |       | 5     |                       |

|                  |                                 | I <sub>OUT</sub> = 150 mA                                                | 80    |       | 115   | mV                    |

|                  |                                 |                                                                          |       |       | 150   |                       |

| I <sub>sc</sub>  | Short Circuit Current Limit     | (Note 10)                                                                | 600   |       |       | mA                    |

| e <sub>n</sub>   | Output Noise Voltage            | BW = 10 Hz to 100 kHz,                                                   | 220   |       |       | \ /                   |

|                  |                                 | $C_{OUT} = 1\mu F$                                                       |       |       |       | μVrms                 |

| C <sub>OUT</sub> | Output Capacitor                | Capacitance (Note 11)                                                    |       | 1     | 20    | μF                    |

|                  |                                 | ESR (Note 11)                                                            |       | 5     | 500   | mΩ                    |

| TSD              | Thermal Shutdown Temperature    |                                                                          | 160   |       |       | °C                    |

|                  | Thermal Shutdown Hysteresis     |                                                                          | 20    |       |       | °C                    |

| Enable Cor       | ntrol Characteristics (Note 12) | I                                                                        | 1     | 1     |       | ı                     |

| I <sub>EN</sub>  | Maximum Input Current at EN     | V <sub>EN</sub> = 0 and V <sub>IN</sub> = 6.0V                           |       |       | 0.1   | μA                    |

### **Electrical Characteristics** (Continued)

Unless otherwise specified:  $V_{EN} = 1.8V$ ,  $V_{IN} = V_{OUT} + 0.5V$ ,  $C_{IN} = 1 \mu F$ ,  $I_{OUT} = 1 mA$ ,  $C_{OUT} = 1 \mu F$ . Typical values and limits appearing in standard typeface are for  $T_J = 25^{\circ}C$ . Limits appearing in **boldface type** apply over the entire junction temperature range for operation,  $-40^{\circ}C$  to  $+125^{\circ}C$ . (Note 6) (Note 7)

| Symbol           | Parameter                             | Conditions                                    | Тур  | Limit |     | Units |

|------------------|---------------------------------------|-----------------------------------------------|------|-------|-----|-------|

|                  |                                       |                                               |      | Min   | Max | Units |

| V <sub>IL</sub>  | Logic Low Input threshold             | V <sub>IN</sub> = 2.5V to 6.0V                |      |       | 0.5 | V     |

| V <sub>IH</sub>  | Logic High Input threshold            | V <sub>IN</sub> = 2.5V to 6.0V                |      | 1.2   |     | V     |

| Power Good       | d                                     |                                               |      |       | •   |       |

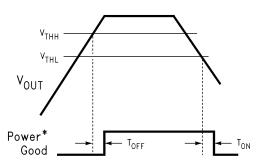

|                  | Power Good                            | % of V <sub>OUT</sub> (PG ON) Figure 2        |      |       |     |       |

| $V_{THL}$        | Low threshold                         | % of V <sub>OUT</sub> (PG OFF) Figure 2 (Note | 93   | 90    | 95  | %     |

| $V_{THH}$        | High Threshold                        | 14)                                           | 95   | 92    | 98  |       |

| V <sub>OL</sub>  | PG Output Logic Low Voltage           | $I_{PULL-UP} = 100\mu A$ , fault condition    | 0.02 |       | 0.1 | V     |

| I <sub>PGL</sub> | PG Output Leakage Current             | PG Off, V <sub>PG</sub> = 6V                  | 0.02 |       |     | μA    |

| T <sub>ON</sub>  | Power Good Turn On time,<br>(Note 9)  | V <sub>IN</sub> = 4.2V                        | 10   |       |     | μs    |

| T <sub>OFF</sub> | Power Good Turn Off time,<br>(Note 9) | V <sub>IN</sub> = 4.2V                        | 10   |       |     | μs    |

**Note 1:** Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

Note 2: All voltages are with respect to the potential at the GND pin.

Note 3: The Absolute Maximum power dissipation depends on the ambient temperature and can be calculated using the formula:

$$P_D = (T_J - T_A)/\theta_{JA}$$

where  $T_J$  is the junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance. The 364mW rating appearing under Absolute Maximum Ratings for the SOT23-5 package results from substituting the Absolute Maximum junction temperature, 150°C, for  $T_J$ , 70°C for  $T_A$ , and 220°C/W for  $\theta_{JA}$ . More power can be dissipated safely at ambient temperatures below 70°C. Less power can be dissipated safely at ambient temperatures above 70°C. The Absolute Maximum power dissipation can be increased by 4.5mW for each degree below 70°C, and it must be derated by 4.5mW for each degree above 70°C. Same principle applies to the micro SMD package.

Note 4: The human body model is 100pF discharged through 1.5kΩ resistor into each pin. The machine model is a 200 pF capacitor discharged directly into each pin.

Note 5: Like the Absolute Maximum power dissipation, the maximum power dissipation for operation depends on the ambient temperature. The 250mW rating appearing under Operating Ratings for the SOT23-5 package results from substituting the maximum junction temperature for operation, 125°C, for  $T_J$ , 70°C for  $T_A$ , and 220°C/W for  $\theta_{JA}$  into (Note 3) above. More power can be dissipated at ambient temperatures below 70°C. Less power can be dissipated at ambient temperatures above 70°C. The maximum power dissipation for operation can be increased by 4.5mW for each degree below 70°C, and it must be derated by 4.5mW for each degree above 70°C. Same principle applies to the micro SMD package.

Note 6: All limits are guaranteed. All electrical characteristics having room-temperature limits are tested during production with  $T_J = 25^{\circ}C$  or correlated using Statistical Quality Control (SQC) methods. All hot and cold limits are guaranteed by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

Note 7: The target output voltage, which is labeled  $V_{OUT(nom)}$ , is the desired voltage option.

Note 8: An increase in the load current results in a slight decrease in the output voltage and vice versa.

Note 9: Dropout voltage is the input-to-output voltage difference at which the output voltage is 100mV below its nominal value.

Note 10: Short circuit current is measured on input supply line after pulling down  $V_{OUT}$  to 95%  $V_{OUT(nom)}$ -

Note 11: Guaranteed by design. The capacitor tolerance should be ±30% or better over the full temperature range. The full range of operating conditions such as temperature, DC bias and even capacitor case size for the capacitor in the application should be considered during device selection to ensure this minimum capacitance specification is met. X7R capacitor types are recommended to meet the full device temperature range.

Note 12: Turn-on time is time measured between the enable input just exceeding  $V_{IH}$  and the output voltage just reaching 95% of its nominal value.

Note 13: 100V machine model for Power-good flag, pin 4.

Note 14: The low and high thresholds are generated together. Typically a 2.6% difference is seen between these thresholds.

Note 15: The minimum  $V_{IN}$  is dependant on the device output option.

$For \ Vout_{(NOM)} < 2.5V, \ V_{IN(MIN)} \ will \ equal \ 2.5V. \ For \ Vout_{(NOM)} >= 2.5V, \ V_{IN(MIN)} \ will \ equal \ Vout_{(NOM)} + 200mV.$

<sup>\*</sup>Power good pin pulled up to  $V_{OUT}$  through an external pull-up resistor.

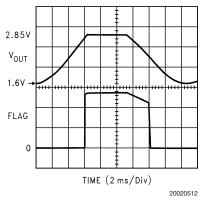

**FIGURE 1. Power Good Flag Timing**

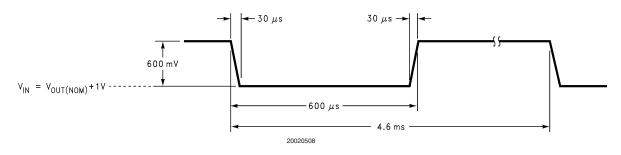

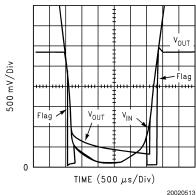

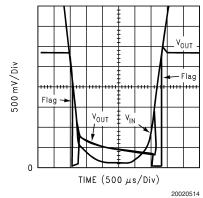

FIGURE 2. Line Transient response Input Perturbation

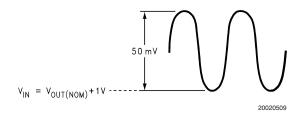

FIGURE 3. PSRR Input Perturbation

**Typical Performance Characteristics** Unless otherwise specified,  $C_{IN} = C_{OUT} = 1 \mu F$  Ceramic,  $V_{IN} = V_{OUT} + 0.2V$ ,  $T_A = 25^{\circ}C$ , Enable pin is tied to  $V_{IN}$ .

## Ripple Rejection Ratio (LM3988-2.6)

# Typical Performance Characteristics Unless otherwise specified, $C_{IN}$ = $C_{OUT}$ = 1 $\mu$ F Ceramic, $V_{IN}$ = $V_{OUT}$ + 0.2V, $T_A$ = 25°C, Enable pin is tied to $V_{IN}$ . (Continued)

Power-Good Response Time (LP3988-2.85) (flag pin pulled to  $V_{OUT}$  through a 100K $\Omega$  resistor)

Power-Good Response Time (LP3988-2.85) (flag pin pulled to  $\text{V}_{\text{IN}}$  through a 100K  $\!\Omega$  resistor)

Power-Good Response Time (LP3988-2.85) (flag pin pulled to  $V_{OUT}$  through a 100K  $\!\Omega$  resistor)

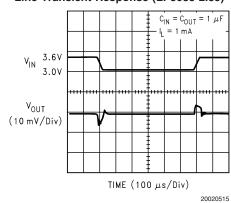

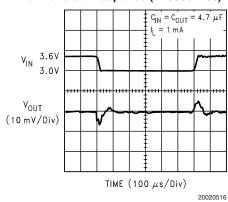

Line Transient Response (LP3988-2.85)

Line Transient Response (LP3988-2.85)

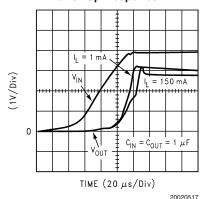

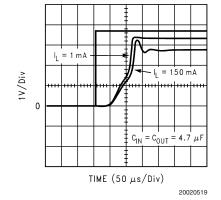

**Power-Up Response**

# Typical Performance Characteristics Unless otherwise specified, $C_{IN} = C_{OUT} = 1 \mu F$ Ceramic, $V_{IN} = V_{OUT} + 0.2V$ , $T_A = 25^{\circ}C$ , Enable pin is tied to $V_{IN}$ . (Continued)

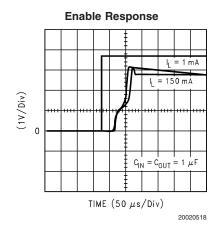

**Enable Response**

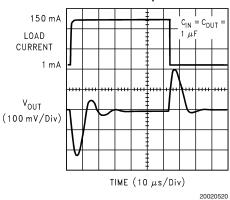

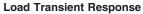

### **Load Transient Response**

# **Application Hints**

#### **EXTERNAL CAPACITORS**

Like any low-dropout regulator, the LP3988 requires external capacitors for regulator stability. The LP3988 is specifically designed for portable applications requiring minimum board space and smallest components. These capacitors must be correctly selected for good performance.

#### INPUT CAPACITOR

An input capacitance of  $\approx 1 \mu F$  is required between the LP3988 input pin and ground (the amount of the capacitance may be increased without limit).

This capacitor must be located a distance of not more than 1cm from the input pin and returned to a clean analog ground. Any good quality ceramic, tantalum, or film capacitor may be used at the input.

**Important:** Tantalum capacitors can suffer catastrophic failures due to surge current when connected to a low-impedance source of power (like a battery or a very large capacitor). If a tantalum capacitor is used at the input, it must be guaranteed by the manufacturer to have a surge current rating sufficient for the application.

There are no requirements for the ESR on the input capacitor, but tolerance and temperature coefficient must be considered when selecting the capacitor to ensure the capacitance will be  $\approx 1 \mu F$  over the entire operating temperature range.

#### **OUTPUT CAPACITOR**

The LP3988 is designed specifically to work with very small ceramic output capacitors. A ceramic capacitor (dielectric types Z5U, Y5V or X7R) in 1 to 22  $\mu\text{F}$  range with 5m $\Omega$  to 500m $\Omega$  ESR range is suitable in the LP3988 application circuit.

It may also be possible to use tantalum or film capacitors at the output, but these are not as attractive for reasons of size and cost (see next section Capacitor Characteristics).

The output capacitor must meet the requirement for minimum amount of capacitance and also have an ESR (Equivalent Series Resistance) value which is within a stable range (5 m $\Omega$  to 500 m $\Omega$ ).

#### **NO-LOAD STABILITY**

The LP3988 will remain stable and in regulation with no external load. This is specially important in CMOS RAM keep-alive applications.

#### CAPACITOR CHARACTERISTICS

The LP3988 is designed to work with ceramic capacitors on the output to take advantage of the benefits they offer: for capacitance values in the range of 1µF to 4.7µF range, ceramic capacitors are the smallest, least expensive and have the lowest ESR values (which makes them best for eliminating high frequency noise). The ESR of a typical 1µF ceramic capacitor is in the range of 20 m $\Omega$  to 40 m $\Omega$ , which easily meets the ESR requirement for stability by the LP3988.

The ceramic capacitor's capacitance can vary with temperature. Most large value ceramic capacitors ( $\approx 2.2 \mu F$ ) are manufactured with Z5U or Y5V temperature characteristics, which results in the capacitance dropping by more than 50% as the temperature goes from 25°C to 85°C.

A better choice for temperature coefficient in a ceramic capacitor is X7R, which holds the capacitance within  $\pm 15\%$ .

Tantalum capacitors are less desirable than ceramic for use as output capacitors because they are more expensive when comparing equivalent capacitance and voltage ratings in the  $1\mu F$  to  $4.7\mu F$  range.

Another important consideration is that tantalum capacitors have higher ESR values than equivalent size ceramics. This means that while it may be possible to find a tantalum capacitor with an ESR value within the stable range, it would have to be larger in capacitance (which means bigger and more costly) than a ceramic capacitor with the same ESR value. It should also be noted that the ESR of a typical tantalum will increase about 2:1 as the temperature goes from 25°C down to -40°C, so some guard band must be allowed.

#### **ON/OFF INPUT OPERATION**

The LP3988 is turned off by pulling the  $V_{EN}$  pin low, and turned on by pulling it high. If this feature is not used, the  $V_{EN}$  pin should be tied to  $V_{IN}$  to keep the regulator output on at all time. To assure proper operation, the signal source used to drive the  $V_{EN}$  input must be able to swing above and below the specified turn-on/off voltage thresholds listed in the Electrical Characteristics section under  $V_{IL}$  and  $V_{IH}$ .

#### **FAST ON-TIME**

The LP3988 utilizes a speed up circuitry to ramp up the internal  $V_{\mathsf{REF}}$  voltage to its final value to achieve a fast output turn on time.

# **Physical Dimensions** inches (millimeters) unless otherwise noted .115±.003 [2.92±0.07] .075 [1.91] В .063±.003 [1.6±0.07] .112±.006 [2.84±0.15] LAND PATTERN RECOMMENDATION R.004 MIN TYP R.004 MIN TYP [0.1] .0060+:0015 [0.152+0.038] △ .004 [0.1] C 5X .0170±.0025 [0.432±0.063] [0.432±0.063] SEATING PLANE .002-.006 [0.05-0.15] TYP .014-.022 [0.36-0.55] TYP CONTROLLING DIMENSION IS INCH VALUES IN [ ] ARE MILLIMETERS MF05A (Rev B) 5-Lead Small Outline Package (MF) **NS Package Number MF05A** $5x \varnothing_{0.250}^{0.275}$ DIMENSIONS ARE IN MILLIMETERS DIMENSIONS IN ( ) FOR REFERENCE ONLY (0.433) В LAND PATTERN RECOMMENDATION SYMM C → $\begin{array}{c} 0.125 \\ 0.050 \end{array}$ 0.433 TOP SIDE COATING 0.5 BUMP A1 CORNER SILICON-Α $5x \varnothing_{0.305}^{0.335}$ ( 0.001( C A( B( B) TLA05XXX (Rev B) Thin micro SMD, 5 bump Package (TLA05) **NS Package Number TLA05AEA** The dimensions for X1, X2 and X3 are as given: X1 = 1.006mm +/- 0.03mm X2 = 1.463mm +/- 0.03mm X3 = 0.6mm +/- 0.075mm

#### **Notes**

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center Email: new feedback@nsc.c

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.