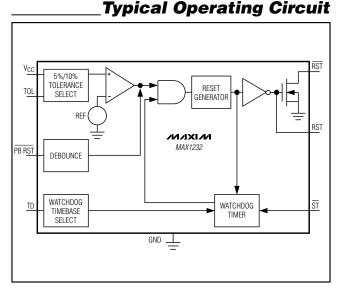

## **General Description**

The MAX1232 microprocessor ( $\mu$ P) supervisory circuit provides  $\mu$ P housekeeping and power-supply supervision functions while consuming only 1/10th the power of the DS1232. The MAX1232 enhances circuit reliability in  $\mu$ P systems by monitoring the power supply, monitoring the software execution, and providing a debounced manual reset input. The MAX1232 is a plug-in upgrade of the Dallas DS1232.

A reset pulse of at least 250ms duration is supplied on power-up, power-down, and low-voltage brownout conditions (5% or 10% supply tolerances can be selected digitally). Also featured is a debounced manual reset input that forces the reset outputs to their active states for a minimum of 250ms. A digitally programmable watchdog timer monitors software execution and can be programmed for timeout settings of 150ms, 600ms, or 1.2s. The MAX1232 requires no external components.

#### **Applications**

Computers Controllers Intelligent Instruments Automotive Systems Critical µP Power Monitoring

###

\_ Maxim Integrated Products 1

**Features**S1232

Ile +4.5V

s Min

600ms

- Consumes 1/10th the Power of the DS1232

- Precision Voltage Monitor—Adjustable +4.5V or +4.75V

- ◆ Power-OK/Reset Pulse Width-250ms Min

- No External Components

- Adjustable Watchdog Timer—150ms, 600ms, or 1.2s

- Debounced Manual Reset Input for External Override

- Available in 8-Pin PDIP/SO and 16-Pin Wide SO Packages

### Ordering Information

| PART       | TEMP RANGE   | PIN-PACKAGE |

|------------|--------------|-------------|

| MAX1232C/D | 0°C to +70°C | Dice*       |

| MAX1232CPA | 0°C to +70°C | 8 PDIP      |

| MAX1232CSA | 0°C to +70°C | 8 SO        |

#### Ordering Information continued on last page.

\*Contact factory for dice specifications.

PB RST 1

TD 2

TOL 3

N.C. 1

N.C. 3

TD 4

N.C. 5

TOL 6

GND 8

N.C. 7

PB RST 2

TOP VIFW

Devices in PDIP and SO packages are available in both leaded and lead-free packaging. Specify lead free by adding the + symbol at the end of the part number when ordering. Lead free not available for CERDIP package.

**ΜΛΧΙΜ**

MAX1232

DIP/SO

ΜΛΧΙΜ

WIDE SO

MAX1232

## Pin Configurations

8 V<sub>CC</sub>

6 RST

5 RST

16 N.C.

15 V<sub>CC</sub>

14 N.C.

13 ST 12 N.C.

11 RST

10 N.C.

9 RST

7 ST

#### **ABSOLUTE MAXIMUM RATINGS**

Voltage on Any Pin (with respect to GND).....-1V to +7V Operating Temperature Range C Suffix.....0°C to +70°C E Suffix....-40°C to +85°C M Suffix ....-55°C to +125°C

| Storage Temperature Range    | 65°C to +160°C |

|------------------------------|----------------|

| Lead Temperature (soldering, | 10s)+300°C     |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Recommended DC Operating Conditions**

$(T_A = T_{MIN} \text{ to } T_{MAX})$

| PARAMETER                              | SYMBOL          | CONDITIONS | MIN  | TYP | MAX                   | UNITS |

|----------------------------------------|-----------------|------------|------|-----|-----------------------|-------|

| Supply Voltage                         | V <sub>CC</sub> |            | 4.5  | 5.0 | 5.5                   | V     |

| ST and PBRST Input High Level (Note 1) | V <sub>IH</sub> |            | 2.0  |     | V <sub>CC</sub> + 0.3 | V     |

| ST and PBRST Input Low Level           | VIL             |            | -0.3 |     | +0.8                  | V     |

### **DC Electrical Characteristics**

(V<sub>CC</sub> = +4.5V to +5.5V,  $T_A = T_{MIN}$  to  $T_{MAX}$ )

| PARAMETER                               | SYMBOL | CONDITIONS       | MIN  | ТҮР  | МАХ  | UNITS |

|-----------------------------------------|--------|------------------|------|------|------|-------|

| Input Leakage ST, TOL                   | ١L     |                  | -1.0 |      | +1.0 | μA    |

| Output Current RST                      | IOH    | $V_{OH} = 2.4V$  | -1.0 | -12  |      | mA    |

| Output Current RST, RST                 | IOL    | $V_{OL} = 0.4 V$ | 2.0  | 10   |      | mA    |

| Operating Current (Note 2)              | Icc    |                  |      | 50   | 200  | μA    |

| V <sub>CC</sub> 5% Trip Point (Note 3)  | VCCTP  | TOL = GND        | 4.50 | 4.62 | 4.74 | V     |

| V <sub>CC</sub> 10% Trip Point (Note 3) | VCCTP  | $TOL = V_{CC}$   | 4.25 | 4.37 | 4.49 | V     |

### Capacitance (Note 4)

$(T_A = +25^{\circ}C)$

| PARAMETER                   | SYMBOL | CONDITIONS | MIN | ТҮР | МАХ | UNITS |

|-----------------------------|--------|------------|-----|-----|-----|-------|

| Input Capacitance ST, TOL   | CIN    |            |     |     | 5   | рF    |

| Output Capacitance RST, RST | Соит   |            |     |     | 7   | рF    |

### **AC Electrical Characteristics**

$(V_{CC} = +5V \pm 10\%, T_A = T_{MIN} \text{ to } T_{MAX})$

| PARAMETER                                                     | SYMBOL           | CONDITIONS                        | MIN  | ТҮР  | МАХ  | UNITS |

|---------------------------------------------------------------|------------------|-----------------------------------|------|------|------|-------|

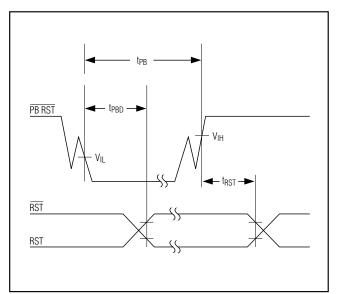

| PBRST (Note 5)                                                | t <sub>PB</sub>  | Figure 3                          | 20   |      |      | ms    |

| PBRST Delay                                                   | <b>t</b> PBD     | Figure 3                          | 1    | 4    | 20   | ms    |

| Reset Active Time                                             | t <sub>RST</sub> |                                   | 250  | 610  | 1000 | ms    |

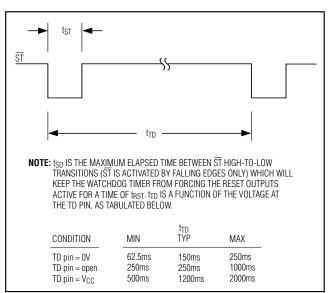

| ST Pulse Width                                                | tst              | Figure 4                          | 75   |      |      | ns    |

|                                                               |                  | Figure 4, TD pin = 0V             | 62.5 | 150  | 250  |       |

| ST Timeout Period                                             | t <sub>TD</sub>  | TD pin = open                     | 250  | 600  | 1000 | ms    |

|                                                               |                  | TD pin = $V_{CC}$                 | 500  | 1200 | 2000 |       |

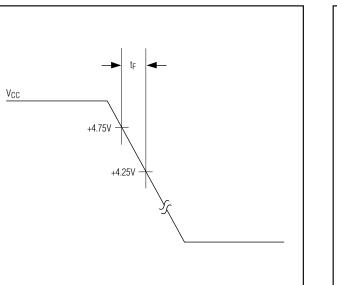

| V <sub>CC</sub> Fall Time (Note 4)                            | tF               | Figure 5                          | 10   |      |      | μs    |

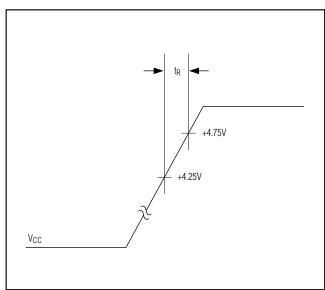

| V <sub>CC</sub> Rise Time (Note 4)                            | tB               | Figure 6                          | 0    |      |      | μs    |

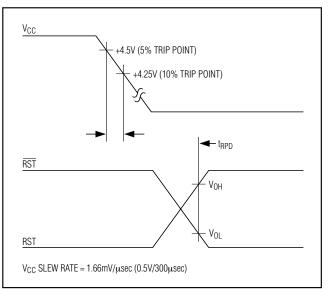

| $V_{CC}$ Detect to RST High and $\overline{RST}$ Low          | t <sub>BPD</sub> | Figure 7, V <sub>CC</sub> falling |      |      | 100  | ns    |

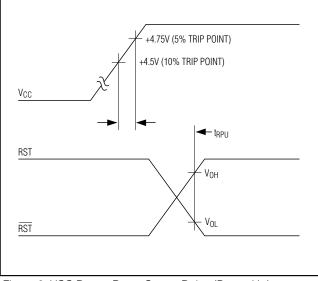

| $V_{CC}$ Detect to RST Low and $\overline{RST}$ Open (Note 6) | tBPU             | Figure 8, V <sub>CC</sub> rising  | 250  | 610  | 1000 | ms    |

Note 1:  $\overline{PBRST}$  is internally pulled up to V<sub>CC</sub> with an internal impedance of typically 40k $\Omega$ .

Note 2: Measured with outputs open.

Note 3: All voltages referenced to GND.

Note 4: Guaranteed by desing.

Note 5: PBRST must be held low for a minimum of 20ms to guarantee a reset.

**Note 6:** t<sub>R</sub> = 5µs.

### **Pin Description**

| <b></b>                       |        |                 |                                                                                                                                                                                                                                          |  |  |

|-------------------------------|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIN                           |        | NAME            | FUNCTION                                                                                                                                                                                                                                 |  |  |

| WIDE SO                       | DIP/SO |                 | T ONCTION                                                                                                                                                                                                                                |  |  |

| 1, 3, 5, 7, 10,<br>12, 14, 16 | _      | N.C.            | No Connection                                                                                                                                                                                                                            |  |  |

| 2                             | 1      | PBRST           | Pushbutton Reset Input. A debounced active-low input that ignores pulses less than 1ms in duration and is guaranteed to recognize inputs of 20ms or greater.                                                                             |  |  |

| 4                             | 2      | TD              | Time Delay Set. The watchdog timebase select input ( $t_{TD}$ = 150ms for TD = 0V, $t_{TD}$ = 600ms for TD = open, $t_{TD}$ = 1.2s for TD = V <sub>CC</sub> ).                                                                           |  |  |

| 6                             | 3      | TOL             | Tolerance Input. Connect to GND for 5% tolerance or to $V_{CC}$ for 10% tolerance.                                                                                                                                                       |  |  |

| 8                             | 4      | GND             | Ground                                                                                                                                                                                                                                   |  |  |

| 9                             | 5      | RST             | Reset Output (Active High). Goes active:<br>(1) If VCC falls below the selected reset voltage threshold<br>(2) If <u>PBRST</u> is forced low<br>(3) If <u>ST</u> is not strobed within the minimum timeout period<br>(4) During power-up |  |  |

| 11                            | 6      | RST             | Reset Output (Active Low, Open-Drain). See RST.                                                                                                                                                                                          |  |  |

| 13                            | 7      | ST              | Strobe Input. Input for watchdog timer.                                                                                                                                                                                                  |  |  |

| 15                            | 8      | V <sub>CC</sub> | The +5V Power-Supply Input                                                                                                                                                                                                               |  |  |

#### **Detailed Description**

#### **Power Monitor**

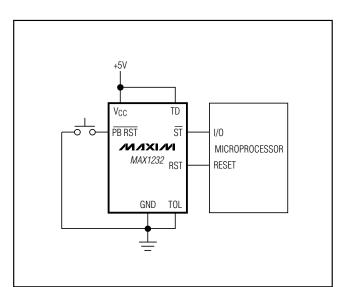

A voltage detector monitors VCC and holds the reset outputs (RST and RST) in their active states whenever V<sub>CC</sub> is below the selected 5% or 10% tolerance (4.62V or 4.37V, typically). To select the 5% level, connect TOL to ground. To select the 10% level, connect TOL to V<sub>CC</sub>. The reset outputs will remain in their active states until V<sub>CC</sub> has been continuously in-tolerance for a minimum of 250ms (the reset active time) to allow the power supply and  $\mu$ P to stabilize.

The RST output both sinks and sources current, while the  $\overline{\text{RST}}$  output, an open-drain MOSFET, sinks current only and must be pulled high.

#### **Pushbutton Reset Input**

The MAX1232's debounced manual reset input (PBRST) manually forces the reset outputs into their active states. The reset outputs go active after PBRST has been held low for a time tPBD, the pushbutton reset delay time. The reset outputs remain in their active states for a minimum of 250ms after PBRST rises above VIH (Figure 3).

A mechanical pushbutton or an active logic signal can drive the PBRST input. The debounced input ignores input pulses less than 1ms and is guaranteed to recognize pulses of 20ms or greater. The PBRST input has an internal pullup to  $V_{CC}$  of about 100µA; therefore, an external pullup resistor is not necessary.

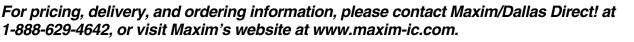

The microprocessor drives the  $\overline{ST}$  input with an input/output (I/O) line. The microprocessor must toggle the  $\overline{ST}$  input within a set period (as determined by TD) to verify proper software execution. If a hardware or software failure keeps  $\overline{ST}$  from toggling within the minimum timeout period— $\overline{ST}$  is activated only by falling edges (a high-to-low transition)—the MAX1232 reset outputs are forced to their active states for 250ms (Figure 2). This typically initiates the microprocessor's power-up routine. If the interruption continues, new reset pulses are generated each timeout period until  $\overline{ST}$  is strobed. The timeout period is determined by the TD input connected to GND, 600ms with TD floating, or 1200ms with TD connected to V<sub>CC</sub>.

The software routine that strobes  $\overline{ST}$  is critical. The code must be in a section of software that executes frequently enough so the time between toggles is less than the watchdog timeout period. One common technique controls the microprocessor I/O line from two sections of the program. The software might set the I/O line high while operating in the foreground mode, and set it low while in the background or interrupt mode. If both modes do not execute correctly, the watchdog timer issues reset pulses.

Figure 1. Pushbutton Reset

Figure 2. Watchdog Timer

MAX1232

Figure 3. Pushbutton Reset. The debounced PBRST input ignores input pulses less than 1ms and is guaranteed to recognize pulses of 20ms or greater.

Figure 4. Watchdog Strobe Input

Figure 5. Power-Down Slew Rate

Figure 6. Power-Up Slew Rate

MAX1232

**MAX1232**

Figure 7. VCC Detect Reset Output Delay (Power-Down)

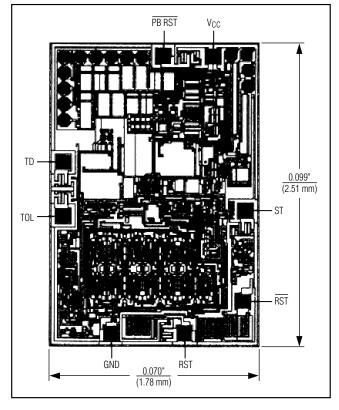

#### Chip Topography

Figure 8. VCC Detect Reset Output Delay (Power-Up)

### Ordering Information (continued)

| PART       | TEMP RANGE      | PIN-PACKAGE |

|------------|-----------------|-------------|

| MAX1232CWE | 0°C to +70°C    | 16 Wide SO  |

| MAX1232EPA | -40°C to +85°C  | 8 PDIP      |

| MAX1232ESA | -40°C to +85°C  | 8 SO        |

| MAX1232EWE | -40°C to +85°C  | 16 Wide SO  |

| MAX1232MJA | -55°C to +125°C | 8 CERDIP    |

#### Ordering Information continued on last page.

\*Contact factory for dice specifications.

Devices in PDIP and SO packages are available in both leaded and lead-free packaging. Specify lead free by adding the + symbol at the end of the part number when ordering. Lead free not available for CERDIP package.

#### **Package Information**

For the latest package outline information, go to **www.maxim-ic.com/packages**.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

6

© 2005 Maxim Integrated Products

MAXIM is a registered trademark of Maxim Integrated Products, Inc.