# HIGH-SIDE CURRENT SENSE AMPLIFIER

#### **Features**

- Complete, unidirectional high-side current sense capability

- 0.2% full-scale accuracy

- +5 to +36 V supply operation

- 85 dB power supply rejection

- 90 µA max supply current

- 9 µA shutdown current

- Operating Temperature Range: -40 to +85 °C

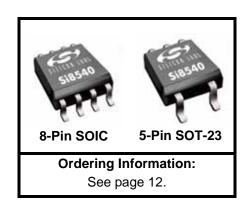

- 5-pin SOT-23 or 8-Pin SOIC package

- RoHS-compliant

#### **Applications**

- Battery chargers

- Smart battery packs

- DC motor control

- Backup systems

- Current control applications

# Description

The Si8540 is a unidirectional, 36 V (max), high-side current sense amplifier for use in applications requiring current monitoring and/or control. This device draws bias current from the high-side line to which it is attached, eliminating the need for an external supply. It measures current from 0.1 to 10 A by sensing the voltage across an external sense resistor (or PCB trace) from dc to 20 kHz and can achieve measurement accuracies of 0.2% (typical) at full load. The device output is a current signal proportional to measured current and is easily converted to a scaled voltage using a single external resistor. The Si8540 is available in compact SOT-23 or SOIC-8 packages.

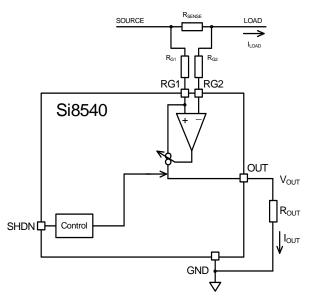

#### **Functional Block Diagram**

Patents pending

# TABLE OF CONTENTS

| <u>Section</u>                             | <u>Page</u> |

|--------------------------------------------|-------------|

| 1. Electrical Specifications               |             |

| 2. Typical Application Schematic           |             |

| 3. Functional Description                  |             |

| 3.1. Application Information               |             |

| 4. Typical Performance Data                |             |

| 5. Pin Descriptions                        |             |

| 6. Ordering Guide                          |             |

| 6.1. Device Marking                        |             |

| 7. Package Outline: 8-Pin Narrow Body SOIC |             |

| 8. Land Pattern: 8-Pin Narrow Body SOIC    |             |

| 9. Package Outline: SOT-23                 |             |

| 10. Land Pattern: SOT-23                   |             |

| Document Change List                       |             |

| Contact Information                        |             |

# 1. Electrical Specifications

**Table 1. Absolute Maximum Ratings**

| Parameter                                                                                                                                          | Value       | Unit     |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|

| Voltage at RG1, RG2, SHDN to GND                                                                                                                   | -0.3 to +40 | V        |

| Differential Input Voltage, RG1 to RG2                                                                                                             | ±0.3        | V        |

| Voltage at OUT                                                                                                                                     | -0.3 to +8  | V        |

| Current into SHDN, GND, OUT, RG1, RG2                                                                                                              | ±50         | mA       |

| Continuous Power Dissipation (T <sub>A</sub> = +70 °C)<br>8-pin SOIC derate 5.88 mW/°C above +70 °C*<br>5-pin SOT23 derate 7.1 mW/°C above +70 °C* | 471<br>571  | mW<br>mW |

| Operating Temperature Range                                                                                                                        | -40 to +85  | °C       |

| Junction Temperature, T <sub>JMAX</sub>                                                                                                            | Up to +150  | °C       |

\*Note: The device is mounted on a standard PCB with a 100 mm<sup>2</sup> copper foil connected to the GND pin, no airflow. Permanent device damage may occur if the absolute maximum ratings are exceeded, and prolonged use at the absolute maximum ratings may affect reliability. It is recommended that the device operate within the limits indicated in Table 2, "DC and AC Characteristics".

Table 2. DC and AC Characteristics

(Unless otherwise specified:  $V_{RG1}$  = +5 to +36 V, RG1 = RG2 = 200,  $V_{SENSE}$  = 0 V,  $T_A$  = -40 to +85 °C)

| Parameter                              | Symbol                              | Test Condition                                                                                                                     | Min | Тур        | Max                         | Unit     |

|----------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------------|-----------------------------|----------|

| Operating Voltage                      | V <sub>RG1</sub>                    |                                                                                                                                    | 5   | _          | 36                          | V        |

| Operating Frequency                    | F                                   |                                                                                                                                    | 0   | 20         | _                           | kHz      |

| Total Input Current                    | I <sub>RG1</sub> +I <sub>RG2</sub>  | I <sub>LOAD</sub> = 0 A                                                                                                            | _   | 46         | 90                          | μΑ       |

| Input Currents                         | I <sub>RG1</sub> , I <sub>RG2</sub> | I <sub>LOAD</sub> = 0 A                                                                                                            |     | 23         | 45                          | μΑ       |

| Input Current Matching                 | I <sub>OS</sub>                     | I <sub>RG1</sub> – I <sub>RG2</sub>                                                                                                |     | ±0.4       | ±1.5                        | μΑ       |

| Sense Voltage <sup>1</sup>             | V <sub>SENSE</sub>                  |                                                                                                                                    | _   | 100        | _                           | mV       |

| OUT Current Accuracy                   | I <sub>RG</sub> /I <sub>OUT</sub>   | V <sub>SENSE</sub> = 100 mV                                                                                                        |     | ±0.2       | ±1.5                        | %        |

| No-Load OUT Error                      |                                     | V <sub>RG1</sub> = 10 V, V <sub>SENSE</sub> = 0 V                                                                                  |     | 0.5        | 15                          | μΑ       |

| Low-Level OUT Error                    |                                     | V <sub>RG1</sub> = 10 V, V <sub>SENSE</sub> = 3 mV                                                                                 | _   | ±0.5       | <u>+</u> 10                 | μΑ       |

| Power-Supply Rejection                 | PSR                                 | V <sub>SENSE</sub> = 100 mV                                                                                                        |     | -85        | _                           | dB       |

| Shutdown Supply Current                | I <sub>RG1</sub> +I <sub>RG2</sub>  | V <sub>SHDN</sub> = 2.4 V                                                                                                          | _   | 3.5        | 9                           | μΑ       |

| SHDN Input Low Voltage                 | V <sub>IL</sub>                     |                                                                                                                                    | _   | _          | 0.3                         | V        |

| SHDN Input Low Current                 | I <sub>IL</sub>                     | V <sub>SHDN</sub> = 0 V                                                                                                            | _   | _          | 1.0                         | μΑ       |

| SHDN Input High Voltage                | V <sub>IH</sub>                     |                                                                                                                                    | 2.4 | _          |                             | V        |

| SHDN Input High Current                | l <sub>IH</sub>                     | V <sub>SHDN</sub> = 2.4 V                                                                                                          |     | _          | 1.0                         | μΑ       |

| OUT Output Voltage Range               | V <sub>OUT</sub>                    | V <sub>OUT</sub> clamped at 8 V                                                                                                    | 0   | _          | V <sub>RG1</sub> – 3.5 (<8) | V        |

| OUT Output Resistance<br>(Internal)    |                                     | I <sub>OUT</sub> = 1.5 mA                                                                                                          | 1   | 3          | _                           | ΜΩ       |

| OUT Rise, Fall Time                    |                                     | $V_{SENSE} = 5 \text{ mV to } 150 \text{ mV},$ $R_{OUT} = 2 = k\Omega,$ $C_{OUT} = 50 \text{ pF, } 10\% \text{ to } 90\%$ (Note 2) | _   | 0.4<br>0.5 | _                           | µs<br>µs |

| OUT Settling Time to 1% of Final Value |                                     | $V_{SENSE}$ = 5 to 150 mV,<br>$R_{OUT}$ = 2 k $\Omega$ ,<br>$C_{OUT}$ = 50 pF (Note 2)                                             | _   | 1 2        | _                           | µs<br>µs |

| Maximum Output Current                 | I <sub>OUT</sub>                    | For I <sub>OUT</sub> > 1.5 mA the internal current limitation starts to limit the output current                                   | 1.5 |            | 10                          | mA       |

- V<sub>SENSE</sub> is the voltage across the sense resistor.

C<sub>OUT</sub> is the load capacitance seen by the OUT pin.

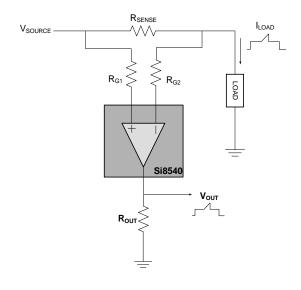

# 2. Typical Application Schematic

Figure 1. Connecting the Si8540 in a Power Control Application

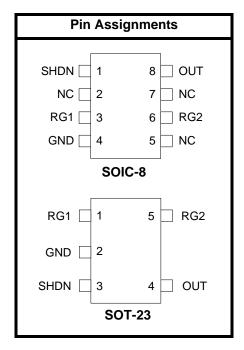

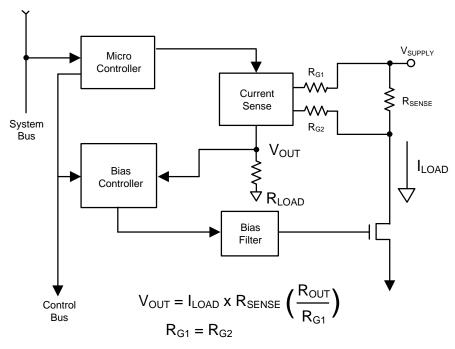

# 3. Functional Description

The Si8540 is designed to operate over an input common-mode range of 5 to 36 V. Figure 2 shows an example Si8540 application with external sense resistor,  $R_{SENSE}$ , external current gain-setting resistors,  $R_{G1}$  and  $R_{G2}$ , and output scaling resistor,  $R_{OUT}$ . The supply current flowing into the Si8540 inverting and non-inverting inputs ( $R_{G1}$ ,  $R_{G2}$ ) is negligible compared to  $I_{LOAD}$  and, as a result, has no appreciable effect on measurement accuracy. The internal current sense amplifier measures the differential input voltage,  $V_{SENSE}$ , and generates an output current proportional to  $I_{LOAD}$ . Resistor  $R_{OUT}$  converts this current to a voltage, and its value determines the output signal gain. The Si8540 is placed in a low-power shutdown mode when SHDN is at  $V_{IH}$ .

Figure 2. Si8540 Application Circuit

#### 3.1. Application Information

The Si8540 can sense a wide range of currents with different sense resistor values. Table 3 lists typical operational values.

| Table 3. Recommended Current Sense Resistor for a Given Full-Scale Load Current |                   |                         |                     |                      |                 |                                |

|---------------------------------------------------------------------------------|-------------------|-------------------------|---------------------|----------------------|-----------------|--------------------------------|

| Full-scale<br>Load                                                              | Current-<br>Sense | Gain-Setting Resistors, | Output<br>Resistor, | Full-Scale<br>Output | Scale<br>Factor | Typical Error at and 100% of I |

| Full-scale<br>Load<br>Current | Current-<br>Sense<br>Resistor | Gain-Setting<br>Resistors,<br>RG1 = RG2 (Ω) | Output<br>Resistor,<br>R <sub>OUT</sub> | Full-Scale<br>Output<br>Voltage, | Scale<br>Factor<br>V <sub>OUT</sub> /I <sub>SENSE</sub> | and | l Error a<br>100% o<br>₋oad (% | f Full |

|-------------------------------|-------------------------------|---------------------------------------------|-----------------------------------------|----------------------------------|---------------------------------------------------------|-----|--------------------------------|--------|

| I <sub>SENSE</sub> (A)        | $R_{SENSE}$ (m $\Omega$ )     |                                             | <b>(k</b> Ω <b>)</b>                    | V <sub>OUT</sub> (V)             | (V/A)                                                   | 1%  | 10%                            | 100%   |

| 0.1                           | 1000                          | 200                                         | 5                                       | 2.5                              | 25                                                      | 10  | 1                              | 0.2    |

| 1                             | 100                           | 200                                         | 5                                       | 2.5                              | 2.5                                                     | 10  | 1                              | 0.2    |

| 5                             | 20                            | 100                                         | 2                                       | 2                                | 0.4                                                     | 5   | 1                              | 0.2    |

| 10                            | 5                             | 50                                          | 2                                       | 2                                | 0.2                                                     | 5   | 1                              | 0.4    |

### 3.1.1. Selecting R<sub>SENSE</sub>

Selecting R<sub>SENSE</sub> involves making the best trade-off between power efficiency and accuracy. Low R<sub>SENSE</sub> values dissipate less power while higher values maximize accuracy. In general, it is best to choose a relatively high value for R<sub>SENSE</sub> in applications where the measured current is small. For higher current applications, the sense resistor should be able to dissipate the heat from its power loss; otherwise, its value may drift or it may fail open, possibly causing a large differential voltage across RG1 and RG2 that may damage the device. In most applications, R<sub>SENSE</sub> should have low inductance to reduce the impact of any high-frequency components in the current being measured (low inductance metal film resistors are recommended). Also, note that the Si8540 requires at least 3.5 V of voltage headroom between the voltage at pin RG1 and pin OUT. This voltage headroom decreases as R<sub>SENSE</sub> increases. A good guideline for determining the maximum value for R<sub>SENSE</sub> is shown in the following equation:

$R_{SENSEmax} = (V_{SOURCE} - V_{OUTmax} - 3.5 \text{ V})/I_{LOAD}$

Where:

V<sub>SOURCE</sub> is the high-side voltage

V<sub>OUTmax</sub> is the full-scale output voltage at the OUT pin

I<sub>LOAD</sub> is the current passing through R<sub>SENSE</sub> measured by the Si8540

#### 3.1.2. Selecting RG1 and RG2

The values of resistors  $R_{G1}$  and  $R_{G2}$  determine the sense amp current-gain. These two resistors must have the same value, and resulting current gain is equal to  $R_{SENSE}$  /  $R_{G}$  (where  $R_{G} = R_{G1} = R_{G2}$ ).

The minimum value of  $R_G$  is determined by the maximum current at the OUT pin (1.5 mA) and by the resistance between the internal current sense amp input and the sense resistor (approximately 0.2  $\Omega$ ). As the value of  $R_G$  is reduced, the input resistance becomes a larger portion of the total gain-setting resistance. This gain error can be compensated by trimming  $R_G$  or  $R_{OUT}$ . A good guideline for determining the maximum value for  $R_G$  is shown in the following equation:

$R_{Gmax} = (V_{SENSEmax} / 1.5 \text{ mA})$

Where:

R<sub>Gmax</sub> is the largest value for RG1 and RG2

$V_{SENSEmax}$  is the value of  $V_{SENSE}$  at maximum  $I_{LOAD}$

Note that for a given value of  $V_{SENSE}$ , a decrease of the  $R_G$  resistor values causes a corresponding increase in current at the OUT pin. This causes additional power to be dissipated in  $R_{OUT}$  rather than in the load, which can reduce efficiency. Note also that mismatches in the currents passing  $R_{G1}$  and  $R_{G2}$  (IOS) together with  $R_G$  affect the full scale error.

This error can be reduced by lowering the values of  $R_{G1}$ ,  $R_{G2}$  and/or lowering their tolerances. This error can also be reduced by increasing the value of  $R_{SENSE}$ .

#### 3.1.3. Choosing R<sub>OUT</sub>

$R_{OUT}$  must be chosen to generate the required full-scale output voltage at the full scale  $I_{OUT}$ , which, in turn, is determined by  $R_{G1}$ ,  $R_{G2}$ , and  $R_{SENSE}$ . The upper limit of  $R_{OUT}$  is determined by the input impedance of the device that it drives. This input impedance should be much larger than  $R_{OUT}$ ; otherwise, measurement accuracy will be degraded. A good guideline for choosing the value of  $R_{OUT}$  is shown in the following equation:

(V<sub>OUTfullscale</sub> x R<sub>G</sub>) / (I<sub>LOAD</sub> x R<sub>SENSE</sub>)

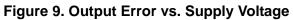

# 4. Typical Performance Data

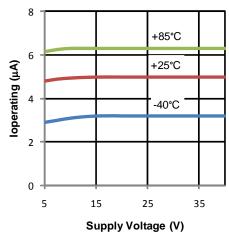

Figure 3. Supply Current vs. Supply Voltage

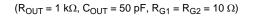

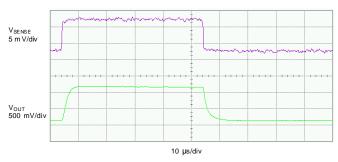

$(R_{OUT}$  = 2 k $\Omega$ ,  $C_{OUT}$  = 50 pF,  $R_{G1}$  =  $R_{G2}$  = 200  $\Omega$ )

10 µs/div

Figure 4. Transient Response 1

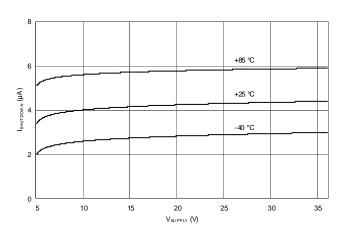

Figure 5. Shutdown Supply Current vs Supply Voltage

Figure 6. Transient Response 2

$$(R_{OUT} = 2~k\Omega,~C_{OUT} = 50~pF,~R_{G1} = R_{G2} = 200~\Omega,~V_{SENSE} = 100~mV)$$

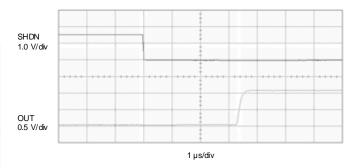

Figure 7. Startup Delay

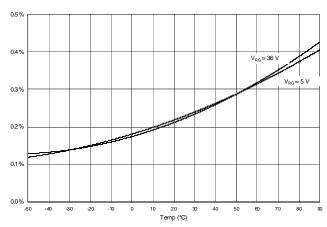

Figure 8. Output Error vs. Temperature

Rev. 1.1 9

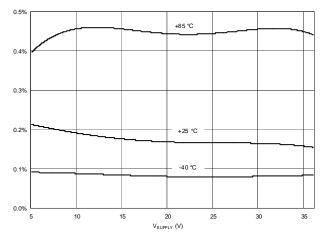

Figure 10. Output Error vs. Sense Voltage

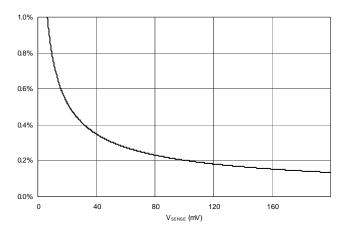

# 5. Pin Descriptions

Figure 11. Pin Configuration

**Table 4. Pin Descriptions**

| Pin Number |       | Name | Description                                                             |

|------------|-------|------|-------------------------------------------------------------------------|

| SOIC       | SOT23 |      |                                                                         |

| 1          | 3     | SHDN | Shutdown input. Ground for normal operation. High voltage for shutdown. |

| 2          | _     | NC   | Do not connect this pin.                                                |

| 3          | 1     | RG1  | Power-side input.                                                       |

| 4          | 2     | GND  | Ground.                                                                 |

| 5          | _     | NC   | Do not connect this pin.                                                |

| 6          | 5     | RG2  | Load-side input.                                                        |

| 7          | _     | NC   | Do not connect this pin.                                                |

| 8          | 4     | OUT  | Current output.                                                         |

# 6. Ordering Guide

| Ordering Part # <sup>1</sup> | Temperature Range | Package             |

|------------------------------|-------------------|---------------------|

| Si8540-B-FW                  | −40 to +85 °C     | SOT-23 <sup>2</sup> |

| Si8540-B-FS                  | −40 to +85 °C     | SOIC-8 <sup>3</sup> |

- 1. Tape and reel options are specified by adding an "R" suffix to the ordering part number. Example: "Si8450-B-FWR" indicates the SOT-23 package option in a tape and reel carrier.

- 2. Moisture sensitivity level (MSL) is (MSL2A) for SOT-23 package with peak reflow temperature of (260 °C) according to JEDEC industry-standard classifications.

- 3. Moisture sensitivity level (MSL) is (MSL2A) for SOIC-8 package with peak reflow temperature of (260 °C) according to JEDEC industry-standard classifications.

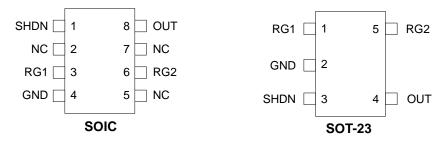

# 6.1. Device Marking

## 6.1.1. SOIC Package Top Mark

Figure 12. SOIC Package Top Mark

**Table 5. SOIC Package Top Mark Table**

| Line 1 Marking: | Base Part Number                                    | Si8540                                                  |

|-----------------|-----------------------------------------------------|---------------------------------------------------------|

| Line 2 Marking: | TTTTTT = Mfg Code                                   | Manufacturing trace code.                               |

| Line 3 Marking: | Assembly build date:<br>YY = Year<br>WW = Work Week | Corresponds to the year and work week of the mold date. |

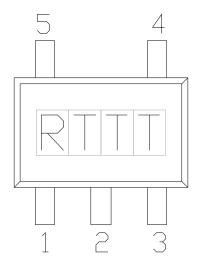

## 6.1.2. SOT-23 Package Top Mark

Figure 13. SOT-23 Package Top Mark

Table 6. SOT-23 Package Top Mark Table

| Line 1 Marking: | 1 | R = Device revision (B)   |

|-----------------|---|---------------------------|

|                 |   | TTT = Assembly trace code |

Rev. 1.1 13

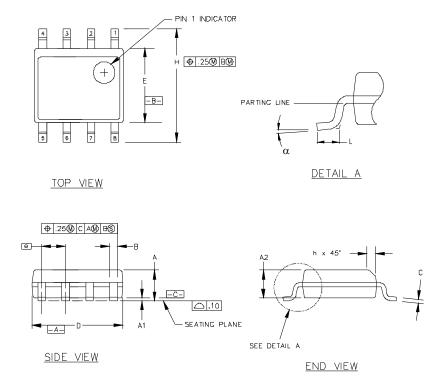

# 7. Package Outline: 8-Pin Narrow Body SOIC

Figure 14 illustrates the package details for the Si8540. Table 7 lists the values for the dimensions shown in the illustration.

Figure 14. SOIC Package

**Table 7. SOIC Package Diagram Dimensions**

| Cumbal | Millimeters |          |  |

|--------|-------------|----------|--|

| Symbol | Min         | Max      |  |

| A      | 1.35        | 1.75     |  |

| A1     | 0.10        | 0.25     |  |

| A2     | 1.40 REF    | 1.55 REF |  |

| В      | 0.33        | 0.51     |  |

| С      | 0.19        | 0.25     |  |

| D      | 4.80        | 5.00     |  |

| E      | 3.80        | 4.00     |  |

| е      | 1.27 BSC    |          |  |

| Н      | 5.80        | 6.20     |  |

| h      | 0.25        | 0.50     |  |

| L      | 0.40        | 1.27     |  |

| œ      | 0°          | 8°       |  |

#### Notes:

- 1. All dimensions shown are in millimeters (mm).

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1982.

- **3.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020B specification for Small Body Components.

14 Rev. 1.1

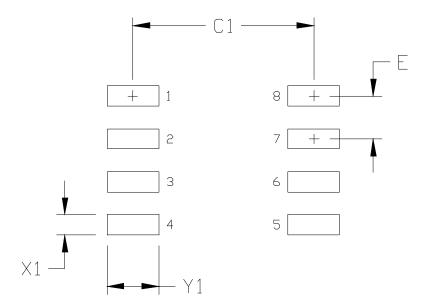

# 8. Land Pattern: 8-Pin Narrow Body SOIC

Figure 15 illustrates the recommended land pattern details for the Si8540 in an 8-pin narrow-body SOIC. Table 8 lists the values for the dimensions shown in the illustration.

Figure 15. PCB Land Pattern: 8-Pin Narrow Body SOIC

Table 8. PCM Land Pattern Dimensions (8-Pin Narrow Body SOIC)

| Dimension | Feature            | (mm) |

|-----------|--------------------|------|

| C1        | Pad Column Spacing | 5.40 |

| E         | Pad Row Pitch      | 1.27 |

| X1        | Pad Width          | 0.60 |

| Y1        | Pad Length         | 1.55 |

- 1. This Land Pattern Design is based on IPC-7351 pattern SOIC127P600X173-8N for Density Level B (Median Land Protrusion).

- 2. All feature sizes shown are at Maximum Material Condition (MMC) and a card fabrication tolerance of 0.05 mm is assumed.

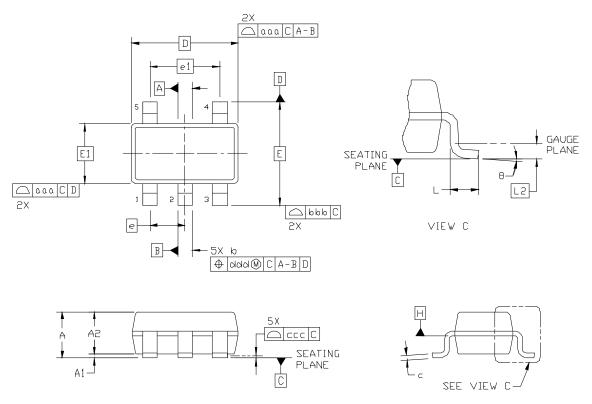

# 9. Package Outline: SOT-23

Figure 16 illustrates the package details for the SOT-23. Table 9 lists the values for the dimensions shown in the illustration.

Figure 16. SOT-23 Package

**Table 9. SOT-23 Package Diagram Dimensions**

| Dimension | Min      | Max  |  |

|-----------|----------|------|--|

| Α         | _        | 1.45 |  |

| A1        | 0.00     | 0.15 |  |

| A2        | 0.90     | 1.30 |  |

| b         | 0.30     | 0.50 |  |

| С         | 0.08     | 0.20 |  |

| D         | 2.90 BSC |      |  |

| Е         | 2.80 BSC |      |  |

| E1        | 1.60 BSC |      |  |

| е         | 0.95     | BSC  |  |

| Dimension | Min      | Max  |

|-----------|----------|------|

| E1        | 1.90 BSC |      |

| L         | 0.30     | 0.60 |

| L2        | 0.25 BSC |      |

| θ         | 0°       | 8°   |

| aaa       | 0.15     |      |

| bbb       | 0.20     |      |

| CCC       | 0.10     |      |

| ddd       | 0.20     |      |

|           |          |      |

#### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to the JEDEC Solid State Outline MO-178, Variation AA.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020D specification for Small Body Components.

16 Rev. 1.1

# 10. Land Pattern: SOT-23

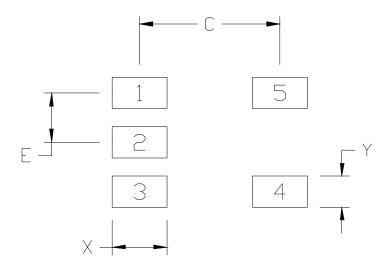

Figure 17 illustrates the recommended land pattern details for the SOT-23 device. Table 10 lists the values for the dimensions shown in the illustration.

Figure 17. SOT-23 Land Pattern

**Table 10. SOT-23 Land Pattern Dimensions**

| Dimension | (mm) |

|-----------|------|

| С         | 2.70 |

| E         | 0.95 |

| X         | 1.05 |

| Y         | 0.60 |

#### Notes:

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on the IPC-7351 guidelines.

- **4.** All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

#### **Card Assembly**

- **5.** A No-Clean, Type-3 solder paste is recommended.

- **6.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020D specification for Small Body Components.

# **DOCUMENT CHANGE LIST**

# Revision 2.5 (July 2007 Integration Associates) to Revision 1.0 (March 2010 Silicon Laboratories)

- Reformatted document from IA2410 and renamed Si8540.

- Updated "Functional Block Diagram" on page 1.

- Updated " Description" on page 1.

- Updated Table 2 on page 5.

- OUT current accuracy changed from ±1 to ±1.5%. (max)

- No-Load OUT Error changed from 5 to 15 μA (max)

- Low-Level OUT Error changed from ±5 to ±10 μA (max)

- Temperature output error test conditions note updated to include temperature range of -40 to TBD° C.

- Updated "3. Functional Description" on page 7.

- Updated "3.1.1. Selecting R<sub>SENSE</sub>" on page 8.

- Updated "3.1.2. Selecting RG1 and RG2" on page 8.

- Updated "3.1.3. Choosing R<sub>OUT</sub>" on page 8.

- Removed temperature sensing function throughout.

- Added recommended PCB Land Pattern sections.

- Reformatted document from "IA2410 Rev 2.5" (Integration Associates) and renamed and rereleased as "Si8540 Rev 1.0" (which obsoletes the previous preliminary internal revision 2.6).

#### **Revision 1.0 to Revision 1.1**

- MSL for the SOT-23 package improved to MSL2A (see "6. Ordering Guide" on page 12).

- Added "6.1. Device Marking" on page 13.

# Si8540

# **CONTACT INFORMATION**

Silicon Laboratories Inc.

400 West Cesar Chavez Austin, TX 78701 Tel: 1+(512) 416-8500

Fax: 1+(512) 416-9669 Toll Free: 1+(877) 444-3032

Please visit the Silicon Labs Technical Support web page: https://www.silabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.

20 Rev. 1.1