# Power Operational Amplifier

### **FEATURES**

- HIGH INTERNAL DISSIPATION 200 WATTS

- HIGH VOLTAGE, HIGH CURRENT 200V, 20A

- HIGH SLEW RATE 50V/µS

- 4 WIRE CURRENT LIMIT SENSING

- LOW DISTORTION

- EXTERNAL SLEEP MODE CONTROL

- OPTIONAL BOOST VOLTAGE INPUTS

- EVALUATION KIT SEE EK09

#### APPLICATIONS

- SONAR TRANSDUCER DRIVER

- LINEAR AND ROTARY MOTOR DRIVES

- YOKE/MAGNETIC FIELD EXCITATION

- PROGRAMMABLE POWER SUPPLIES TO ±95V

- AUDIO UP TO 400W

#### DESCRIPTION

The PA04 is a high voltage MOSFET power operational amplifier that extends the performance limits of power amplifiers in slew rate and power bandwidth, while maintaining high current and power dissipation ratings.

The PA04 is a highly flexible amplifier. The sleep mode feature allows ultra-low quiescent current for standby operation or load protection by disabling the entire amplifier. Boost voltage inputs allow the small signal portion of the amplifier to operate at a higher voltage than the high current output stage. The amplifier is then biased to achieve close linear swings to the supply rails at high currents for extra efficient operation. External compensation tailors performance to user needs. A four wire sense technique allows precision current limiting without the need to consider internal or external milliohm parasitic resistance in the output line.

The JEDEC MO-127 12-pin Power Dip™ package (see Package Outlines) is hermetically sealed and isolated from the internal circuits. The use of compressible thermal washers will void product warranty.

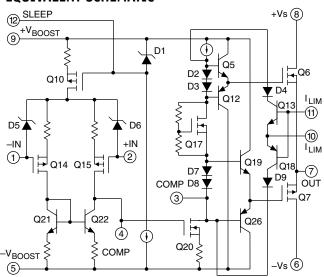

#### **EQUIVALENT SCHEMATIC**

12-PIN DIP PACKAGE STYLE CR

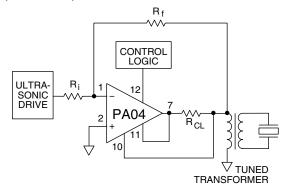

#### TYPICAL APPLICATION

The high power bandwidth and high voltage output of the PA04 allows driving sonar transducers via a resonant circuit including the transducer and a matching transformer. The load circuit appears resistive to the PA04. Control logic turns off the amplifier in sleep mode.

Sonar Transducer Driver

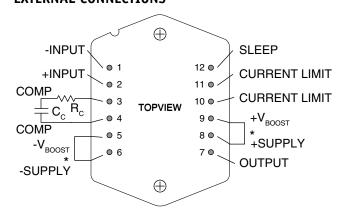

## **EXTERNAL CONNECTIONS**

#### PHASE COMPENSATION

| Gain | $C_{c}$ | $R_c$ |  |  |

|------|---------|-------|--|--|

| 1    | 470pF   | 120Ω  |  |  |

| >3   | 220pF   | 120Ω  |  |  |

| >10  | 100pF   | 120Ω  |  |  |

$\rm C_{_{\rm C}}$  RATED FOR FULL SUPPLY VOLTAGE \*See "BOOST OPERATION" paragraph.

ABSOLUTE MAXIMUM RATINGS

SUPPLY VOLTAGE,  $+V_s$  to  $-V_s$

**BOOST VOLTAGE**

OUTPUT CURRENT, within SOA POWER DISSIPATION, internal INPUT VOLTAGE, differential INPUT VOLTAGE, common mode TEMPERATURE, pin solder - 10s TEMPERATURE, junction<sup>2</sup>

TEMPERATURE, storage

OPERATING TEMPERATURE RANGE, case

200V

SUPPLY VOLTAGE +20V

20A 200W ±20V ±V<sub>s</sub> 300°C 150°C

-65 to +150°C -55 to +125°C

#### **SPECIFICATIONS**

| SI ECHICATIONS                                                                                                                                           |                                                                                                                                                                                                    | PA04                                                           |                                                                |                       | <b>PA04A</b> |                         |               | I                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|-----------------------|--------------|-------------------------|---------------|-----------------------------------|

| PARAMETER                                                                                                                                                | TEST CONDITIONS 1                                                                                                                                                                                  | MIN                                                            | TYP                                                            | MAX                   | MIN          | TYP                     | MAX           | UNITS                             |

| INPUT OFFSET VOLTAGE, initial OFFSET VOLTAGE, vs. temperature OFFSET VOLTAGE, vs. supply OFFSET VOLTAGE, vs. power BIAS CURRENT, initial                 | Full temperature range Full temperature range                                                                                                                                                      |                                                                | 5<br>30<br>15<br>30                                            | 10<br>50<br>50        |              | 2<br>10<br>*<br>10<br>5 | 5<br>30<br>20 | mV<br>μV/°C<br>μV/V<br>μV/W<br>pA |

| BIAS CURRENT, INITIAL BIAS CURRENT, vs. supply OFFSET CURRENT, initial INPUT IMPEDANCE, DC INPUT CAPACITANCE COMMON MODE VOLTAGE RANGE                   | Full temperature range                                                                                                                                                                             | ±V <sub>B</sub> -8                                             | .01<br>10<br>10 <sup>11</sup><br>13                            | 50                    | *            | 5 * * *                 | 20            | pA/V<br>pA<br>Ω<br>pF<br>V        |

| COMMON MODE REJECTION, DC INPUT NOISE                                                                                                                    | Full temp. range, $V_{CM} = \pm 20V$<br>100kHz BW, $R_S = 1K\Omega$                                                                                                                                | 86                                                             | 98<br>10                                                       |                       | *            | *                       |               | dΒ<br>μVrms                       |

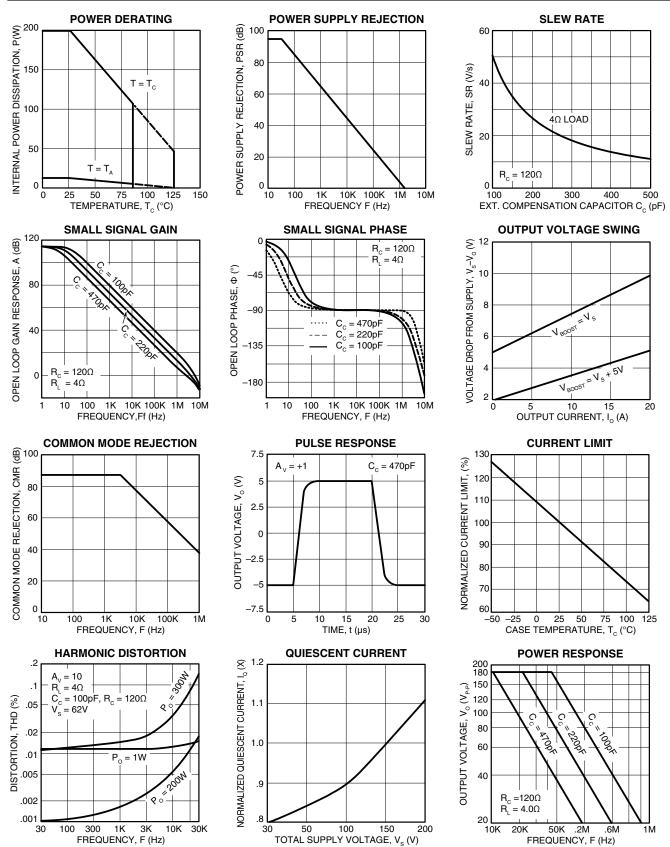

| GAIN OPEN LOOP, @ 15Hz GAIN BANDWIDTH PRODUCT POWER BANDWIDTH                                                                                            | Full temperature range, $C_c$ = 100pF $I_o$ = 10A $R_L$ = 4.5 $\Omega$ , $V_o$ = 180V p-p $C_c$ = 100pF, $R_c$ = 120 $\Omega$                                                                      | 94                                                             | 102<br>2<br>90                                                 |                       | *            | * *                     |               | dB<br>MHz<br>kHz                  |

| PHASE MARGIN                                                                                                                                             | Full temperature range                                                                                                                                                                             |                                                                | 60                                                             |                       |              | *                       |               | 0                                 |

| OUTPUT VOLTAGE SWING VOLTAGE SWING CURRENT, peak SETTLING TIME to .1% SLEW RATE CAPACITIVE LOAD RESISTANCE                                               | $I_{o}=15A$ $V_{\text{BOOST}}=\text{Vs}+5\text{V}, I_{o}=20A$ $A_{v}=1, \ 10\text{V step}, \ R_{c}=4\Omega$ $A_{v}=10, \ C_{c}=100\text{pF}, \ R_{c}=120\Omega$ Full temperature range, $A_{v}=+1$ | ±V <sub>s</sub> -8.8<br>±V <sub>s</sub> -6.8<br>20<br>40<br>10 | ±V <sub>s</sub> -7.5<br>±V <sub>s</sub> -5.5<br>2.5<br>50<br>2 |                       | * * *        | * * * * *               |               | V<br>V<br>A<br>μs<br>V/μs<br>nF   |

| POWER SUPPLY VOLTAGE CURRENT, quiescent, boost supply CURRENT, quiescent, total CURRENT, quiescent, total, sleep mode                                    | Full temperature range Full temperature range                                                                                                                                                      | ±15                                                            | ±75<br>30<br>70<br>3                                           | ±100<br>40<br>90<br>5 | *            | *<br>*<br>*             | *<br>*<br>*   | V<br>mA<br>mA<br>mA               |

| THERMAL RESISTANCE, AC, junction to case <sup>3</sup> RESISTANCE, DC, junction to case RESISTANCE <sup>4</sup> , junction to air TEMPERATURE RANGE, case | Full temperature range, F>60Hz Full temperature range, F<60Hz Full temperature range Meets full range specification                                                                                | -25                                                            | .3<br>.5<br>12                                                 | .4<br>.6<br>85        | *            | * *                     | * *           | °C/W<br>°C/W<br>°C/W<br>°C        |

#### NOTES: \*

- The specification of PA04A is identical to the specification for PA04 in applicable column to the left.

- 1. Unless otherwise noted:  $T_c = 25$ °C,  $C_c = 470$ pF,  $R_c = 120$  ohms. DC input specifications are  $\pm$  value given. Power supply voltage is typical rating.  $\pm V_{BOOST} = \pm V_{S}$ .

2. Long term operation at the maximum junction temperature will result in reduced product life. Derate internal power dissipation to

- achieve high MTTF. For guidance, refer to the heatsink data sheet.

- 3. Rating applies if the output current alternates between both output transistors at a rate faster than 60 Hz.

- 4. The PA04 must be used with a heatsink or the quiescent power may drive the unit to junction temperatures higher than 150°C.

#### **CAUTION**

The PA04 is constructed from MOSFET transistors. ESD handling procedures must be observed.

The internal substrate contains beryllia (BeO). Do not break the seal. If accidentally broken, do not crush, machine, or subject to temperatures in excess of 850°C to avoid generating toxic fumes.

# Product Innova tionFrom

#### **GENERAL**

Please read Application Note 1 "General Operating Considerations" which covers stability, supplies, heat sinking, mounting, current limit, SOA interpretation, and specification interpretation. Visit www.cirrus.com for design tools that help automate tasks such as calculations for stability, internal power dissipation, current limit; heat sink selection; Apex Precision Power's complete Application Notes library; Technical Seminar Workbook; and Evaluation Kits.

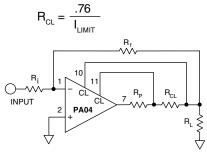

#### **CURRENT LIMIT**

The two current limit sense lines are to be connected directly across the current limit sense resistor. For the current limit to work correctly pin 11 must be connected to the amplifier output side and pin 10 connected to the load side of the current limit resistor,  $R_{\rm cl.}$ , as shown in Figure 1. This connection will bypass any parasitic resistances, Rp, formed by sockets and solder joints as well as internal amplifier losses. The current limiting resistor may not be placed anywhere in the output circuit except where shown in Figure 1.

The value of the current limit resistor can be calculated as follows:

Figure 1. Current Limit.

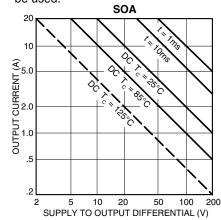

# SAFE OPERATING AREA (SOA)

The MOSFET output stage of this power operational amplifier has two distinct limitations:

- The current handling capability of the MOSFET geometry and the wire bonds.

- 2. The junction temperature of the output MOSFETs.

NOTE: The output stage is protected against transient flyback. However, for protection against sustained, high energy flyback, external fast-recovery diodes should be used.

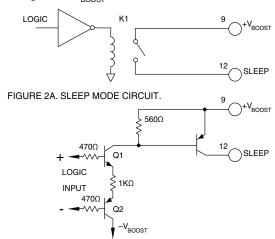

#### SLEEP MODE OPERATION

In the sleep mode, pin 12 (sleep) is tied to pin 9 ( $+V_{\text{BOOST}}$ ). This disables the amplifier's internal reference and the amplifier shuts down except for a trickle current of 3 mA which flows into pin 12. Pin 12 should be left open if the sleep mode is not required.

Several possible circuits can be built to take advantage of this mode. In Figure 2A a small signal relay is driven by a logic gate. This removes the requirement to deal with the common mode voltage that exists on the shutoff circuitry since the sleep mode is referenced to the  $+V_{\text{BOOST}}$  voltage.

In Figure 2B, circuitry is used to level translate the sleep mode input signal. The differential input activates sleep mode with a differential logic level signal and allows common mode voltages to  $\pm V_{\text{ROOST}}$

FIGURE 2B. SLEEP MODE CIRCUIT.

#### **BOOST OPERATION**

With the V<sub>BOOST</sub> feature the small signal stages of the amplifier are operated at higher supply voltages than the amplifier's high current output stage. +V<sub>BOOST</sub> (pin 9) and –V<sub>BOOST</sub> (pin 5) are connected to the small signal circuitry of the amplifier. +V<sub>S</sub> (pin 8) and –V<sub>S</sub> (pin 6) are connected to the high current output stage. An additional 5V on the V<sub>BOOST</sub> pins is sufficient to allow the small signal stages to drive the output transistors into saturation and improve the output voltage swing for extra efficient operation when required. When close swings to the supply rails is not required the +V<sub>BOOST</sub> and +V<sub>S</sub> pins must be strapped together as well as the –V<sub>BOOST</sub> and –V<sub>S</sub> pins. The boost voltage pins must not be at a voltage lower than the V<sub>S</sub> pins.

#### COMPENSATION

The external compensation components  $\rm C_c$  and  $\rm R_c$  are connected to pins 3 and 4. Unity gain stability can be achieved at any compensation capacitance greater than 330 pF with at least 60 degrees of phase margin. At higher gains more phase shift can be tolerated in most designs and the compensation capacitance can accordingly be reduced, resulting in higher bandwidth and slew rate. Use the typical operating curves as a guide to select  $\rm C_c$  and  $\rm R_c$  for the application.

# CONTACTING CIRRUS LOGIC SUPPORT

For all Apex Precision Power product questions and inquiries, call toll free 800-546-2739 in North America. For inquiries via email, please contact apex.support@cirrus.com.

International customers can also request support by contacting their local Cirrus Logic Sales Representative. To find the one nearest to you, go to www.cirrus.com

#### IMPORTANT NOTICE

Cirrus Logic, Inc. and its subsidiaries ("Cirrus") believe that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. No responsibility is assumed by Cirrus for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained herein and gives consent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits or other products of Cirrus. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs, Apex Precision Power, Apex and the Apex Precision Power logo designs are trademarks of Cirrus Logic, Inc. All other brand and product names in this document may be trademarks or service marks of their respective owners.