Data Sheet September 21, 2010 FN7357.6

# 350MHz Fixed Gain Amplifiers with Enable

The EL5106 and EL5306 are fixed gain amplifiers with a bandwidth of 350MHz. This makes these amplifiers ideal for today's high speed video and monitor applications. They feature internal gain setting resistors and can be configured in a gain of +1, -1 or +2.

With a supply current of just 1.5mA and the ability to run from a single supply voltage from 5V to 12V, these amplifiers are also ideal for handheld, portable or battery powered equipment.

The EL5106 and EL5306 also incorporate an enable and disable function to reduce the supply current to  $25\mu A$  typical per amplifier. Allowing the  $\overline{CE}$  pin to float or applying a low logic level will enable the amplifier.

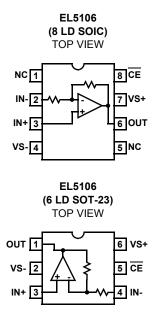

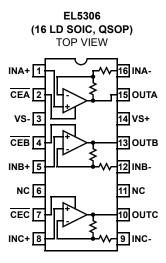

The EL5106 is offered in the 6 Ld SOT-23 and the industry-standard 8 Ld SOIC packages and the EL5306 is available in the 16 Ld SOIC and 16 Ld QSOP packages. All operate over the industrial temperature range of -40°C to +85°C.

### Features

- Pb-free available (RoHS compliant)

- Gain selectable (+1, -1, +2)

- $350MHz 3dB BW (A_V = 2)$

- · 1.5mA supply current per amplifier

- · Fast enable/disable

- · Single and dual supply operation, from 5V to 12V

- · Available in SOT-23 packages

- 450MHz, 3.5mA product available (EL5108 and EL5308)

## **Applications**

- · Battery powered equipment

- · Handheld, portable devices

- · Video amplifiers

- · Cable drivers

- · RGB amplifiers

## **Ordering Information**

| PART NUMBER             | PART MARKING  | PACKAGE                        | PKG. DWG. # |

|-------------------------|---------------|--------------------------------|-------------|

| EL5106IWZ-T7* (Note 1)  | BAFA (Note 2) | 6 Ld SOT-23 (Pb-free)          | P6.064A     |

| EL5106IWZ-T7A* (Note 1) | BAFA (Note 2) | 6 Ld SOT-23 (Pb-free)          | P6.064A     |

| EL5106IS                | 5106IS        | 8 Ld SOIC (150 mil)            | M8.15E      |

| EL5106ISZ (Note 1)      | 5106ISZ       | 8 Ld SOIC (150 mil) (Pb-free)  | M8.15E      |

| EL5106ISZ-T7* (Note 1)  | 5106ISZ       | 8 Ld SOIC (150 mil) (Pb-free)  | M8.15E      |

| EL5106ISZ-T13* (Note 1) | 5106ISZ       | 8 Ld SOIC (150 mil) (Pb-free)  | M8.15E      |

| EL5306ISZ (Note 1)      | EL5306ISZ     | 16 Ld SOIC (150 mil) (Pb-free) | M8.15E      |

| EL5306ISZ-T7* (Note 1)  | EL5306ISZ     | 16 Ld SOIC (150 mil) (Pb-free) | M8.15E      |

| EL5306ISZ-T13* (Note 1) | EL5306ISZ     | 16 Ld SOIC (150 mil) (Pb-free) | M8.15E      |

| EL5306IUZ (Note 1)      | 5306IUZ       | 16 Ld QSOP (150 mil) (Pb-free) | MDP0040     |

| EL5306IUZ-T7* (Note 1)  | 5306IUZ       | 16 Ld QSOP (150 mil) (Pb-free) | MDP0040     |

| EL5306IUZ-T13* (Note 1) | 5306IUZ       | 16 Ld QSOP (150 mil) (Pb-free) | MDP0040     |

<sup>\*</sup>Please refer to TB347 for details on reel specifications. NOTES:

- These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100%

matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations).

Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC

J STD-020.

- 2. The part marking is located on the bottom of the part.

# **Pinouts**

# **Absolute Maximum Ratings** (T<sub>A</sub> = +25°C)

###

### **Thermal Information**

| Storage Temperature                         | 65°C to +150°C |

|---------------------------------------------|----------------|

| Ambient Operating Temperature               | 40°C to +85°C  |

| Operating Junction Temperature              | +125°C         |

| Power Dissipation                           | See Curves     |

| Pb-free Reflow Profile                      | see link below |

| http://www.intersil.com/pbfree/Pb-FreeRefle | ow.asp         |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

# **Electrical Specifications** $V_S$ + = +5V, $V_S$ - = -5V, $R_L$ = 150 $\Omega$ , $T_A$ = +25°C Unless Otherwise Specified.

| PARAMETER                       | DESCRIPTION                                     | CONDITIONS                                         | MIN  | TYP   | MAX  | UNIT   |

|---------------------------------|-------------------------------------------------|----------------------------------------------------|------|-------|------|--------|

| AC PERFORMA                     | NCE                                             |                                                    | ·    |       |      |        |

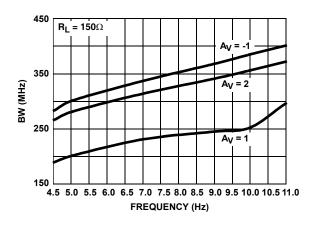

| BW                              | -3dB Bandwidth                                  | A <sub>V</sub> = +1                                |      | 250   |      | MHz    |

|                                 |                                                 | A <sub>V</sub> = -1                                |      | 380   |      | MHz    |

|                                 |                                                 | A <sub>V</sub> = +2                                |      | 350   |      | MHz    |

| BW1                             | 0.1dB Bandwidth                                 |                                                    |      | 20    |      | MHz    |

| SR                              | Slew Rate                                       | $V_O = -2.5V$ to +2.5V, $A_V = +2$                 | 3000 | 4500  |      | V/µs   |

| ts                              | 0.1% Settling Time                              | $V_{OUT}$ = -2.5V to +2.5V, $A_V$ = 2              |      | 16    |      | ns     |

| e <sub>N</sub>                  | Input Voltage Noise                             |                                                    |      | 2.8   |      | nV/√Hz |

| i <sub>N</sub> +                | IN+ Input Current Noise                         |                                                    |      | 6     |      | pA/√Hz |

| dG                              | Differential Gain Error (Note 3)                | A <sub>V</sub> = +2                                |      | 0.02  |      | %      |

| dP                              | Differential Phase Error (Note 3)               | A <sub>V</sub> = +2                                |      | 0.04  |      | 0      |

| DC PERFORMA                     | NCE                                             |                                                    |      |       |      |        |

| V <sub>OS</sub>                 | Offset Voltage                                  |                                                    | -10  | 1     | 10   | mV     |

| T <sub>C</sub> V <sub>OS</sub>  | Input Offset Voltage Temperature<br>Coefficient | Measured from T <sub>MIN</sub> to T <sub>MAX</sub> |      | 5     |      | μV/°C  |

| AE                              | Gain Error                                      | $V_{O}$ = -3V to +3V, $R_{L}$ = 150 $\Omega$       |      | 1     | 2.5  | %      |

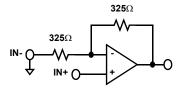

| R <sub>F</sub> , R <sub>G</sub> | Internal R <sub>F</sub> and R <sub>G</sub>      |                                                    |      | 325   |      | Ω      |

| INPUT CHARAC                    | CTERISTICS                                      |                                                    |      |       |      |        |

| CMIR                            | Common Mode Input Range                         |                                                    | ±3   | ±3.3  |      | V      |

| +I <sub>IN</sub>                | + Input Current                                 |                                                    |      | 1.5   | 7    | μA     |

| R <sub>IN</sub>                 | Input Resistance                                | at I <sub>N</sub> +                                |      | 2     |      | МΩ     |

| C <sub>IN</sub>                 | Input Capacitance                               |                                                    |      | 1     |      | pF     |

| OUTPUT CHAR                     | ACTERISTICS                                     |                                                    |      |       |      |        |

| Vo                              | Output Voltage Swing                            | $R_L = 150\Omega$ to GND                           | ±3.4 | ±3.6  |      | V      |

|                                 |                                                 | $R_L = 1k\Omega$ to GND                            | ±3.7 | ±3.85 |      | V      |

| lout                            | Output Current                                  | $R_L = 10\Omega$ to GND                            | 60   | 100   |      | mA     |

| SUPPLY                          |                                                 |                                                    |      |       |      | •      |

| I <sub>SON</sub>                | Supply Current - Enabled (per amplifier)        | No load, V <sub>IN</sub> = 0V                      | 1.35 | 1.5   | 1.82 | mA     |

| I <sub>SOFF</sub>               | Supply Current - Disabled (per amplifier)       | No load, V <sub>IN</sub> = 0V                      |      | 12    | 25   | μA     |

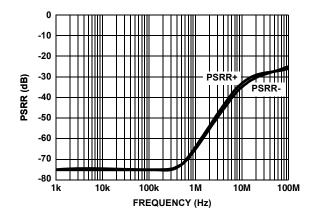

| PSRR                            | Power Supply Rejection Ratio                    | DC, V <sub>S</sub> = ±4.75V to ±5.25V              |      | 75    |      | dB     |

**Electrical Specifications**  $V_S$ + = +5V,  $V_S$ - = -5V,  $R_L$  = 150 $\Omega$ ,  $T_A$  = +25°C Unless Otherwise Specified. **(Continued)**

| PARAMETER         | DESCRIPTION                          | CONDITIONS            | MIN                 | TYP | MAX                 | UNIT |  |  |  |  |

|-------------------|--------------------------------------|-----------------------|---------------------|-----|---------------------|------|--|--|--|--|

| ENABLE            |                                      |                       |                     |     |                     |      |  |  |  |  |

| t <sub>EN</sub>   | Enable Time                          |                       |                     | 280 |                     | ns   |  |  |  |  |

| t <sub>DIS</sub>  | Disable Time                         |                       |                     | 400 |                     | ns   |  |  |  |  |

| I <sub>IHCE</sub> | CE Pin Input High Current            | CE = V <sub>S</sub> + | 1                   | 5   | 25                  | μA   |  |  |  |  |

| I <sub>ILCE</sub> | CE Pin Input Low Current             | CE = V <sub>S</sub> - | +1                  | 0   | -1                  | μA   |  |  |  |  |

| V <sub>IHCE</sub> | CE Input High Voltage for Power-down |                       | V <sub>S</sub> + -1 |     |                     | V    |  |  |  |  |

| V <sub>ILCE</sub> | CE Input Low Voltage for Enable      |                       |                     |     | V <sub>S</sub> + -3 | V    |  |  |  |  |

### NOTE:

3. Standard NTSC test, AC signal amplitude =  $286 \text{mV}_{P-P}$ , f = 3.58 MHz

# Pin Descriptions

| EL5106<br>(SO8) | EL5106<br>(SOT23-6) | EL5306<br>(SO16,<br>QSOP16) | PIN<br>NAME                   | FUNCTION            | EQUIVALENT CIRCUIT    |

|-----------------|---------------------|-----------------------------|-------------------------------|---------------------|-----------------------|

| 1, 5            |                     | 6, 11                       | NC                            | Not connected       |                       |

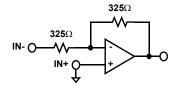

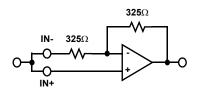

| 2               | 4                   | 9, 12, 16                   | IN-<br>INC-, INB-,<br>INA-    | Inverting input     | IN+ D RG IN-          |

| 3               | 3                   | 1, 5, 8                     | IN+<br>INA+, INB+,<br>INC+    | Non-inverting input | (Reference Circuit 1) |

| 4               | 2                   | 3                           | VS-                           | Negative supply     |                       |

| 6               | 1                   | 10, 13, 15                  | OUT<br>OUTC,<br>OUTB,<br>OUTA | Output              | CIRCUIT 2             |

| 7               | 6                   | 14                          | VS+                           | Positive supply     |                       |

| 8               | 5                   | 2, 4, 7                     | CE,<br>CEA,<br>CEB,<br>CEC    | Chip enable         | CIRCUIT 3             |

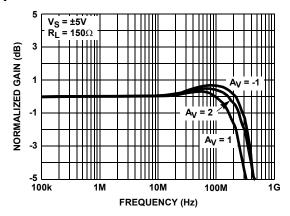

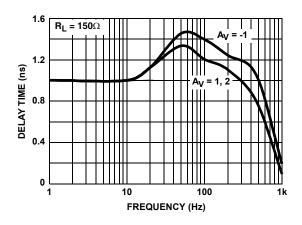

# **Typical Performance Curves**

FIGURE 1. FREQUENCY RESPONSE

FIGURE 3. GROUP DELAY vs FREQUENCY

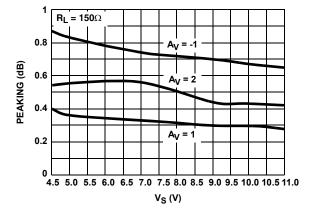

FIGURE 5. PEAKING vs SUPPLY VOLTAGE

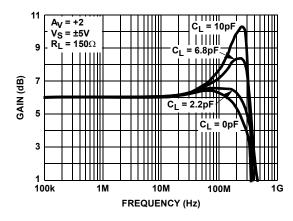

FIGURE 2. FREQUENCY RESPONSE FOR VARIOUS  $\mathbf{C_L}$

FIGURE 4. BANDWIDTH vs SUPPLY VOLTAGE

FIGURE 6. POWER SUPPLY REJECTION RATIO vs FREQUENCY

# Typical Performance Curves (Continued)

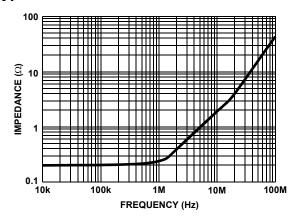

FIGURE 7. OUTPUT IMPEDANCE vs FREQUENCY

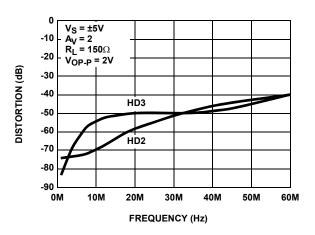

FIGURE 9. HARMONIC DISTORTION vs FREQUENCY

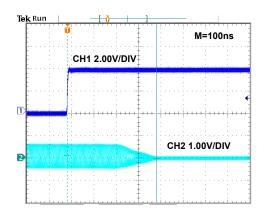

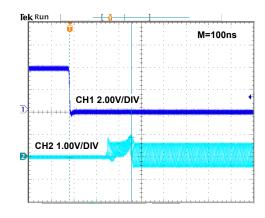

FIGURE 11. DISABLED RESPONSE

6

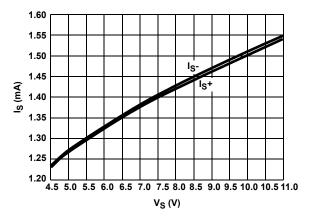

FIGURE 8. SUPPLY CURRENT vs SUPPLY VOLTAGE (PER AMPLIFIER)

FIGURE 10. ENABLED RESPONSE

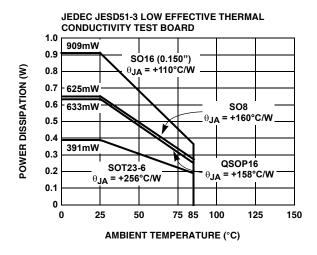

FIGURE 12. PACKAGE POWER DISSIPATION VS AMBIENT TEMPERATURE

## Typical Performance Curves (Continued)

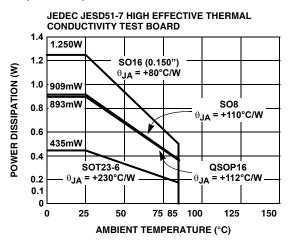

FIGURE 13. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

## Applications Information

### **Product Description**

The EL5106 and EL5306 are fixed gain amplifier that offers a wide -3dB bandwidth of 350MHz and a low supply current of 1.5mA. They work with supply voltages ranging from a single 5V to 12V and they are also capable of swinging to within 1.2V of either supply on the output. These combinations of high bandwidth and low power make the EL5106 and EL5306 the ideal choice for many low-power/high-bandwidth applications such as portable, handheld, or battery-powered equipment.

For varying bandwidth and higher gains, consider the EL5191 with 1GHz on a 9mA supply current or the EL5162 with 300MHz on a 4mA supply current. Versions include single, dual, and triple amp packages with 5 Ld SOT-23, 16 Ld QSOP, and 8 Ld SOIC or 16 Ld SOIC outlines.

# Power Supply Bypassing and Printed Circuit Board Layout

As with any high frequency device, good printed circuit board layout is necessary for optimum performance. Low impedance ground plane construction is essential. Surface mount components are recommended, but if leaded components are used, lead lengths should be as short as possible. The power supply pins must be well bypassed to reduce the risk of oscillation. The combination of a  $4.7\mu F$  tantalum capacitor in parallel with a  $0.01\mu F$  capacitor has been shown to work well when placed at each supply pin.

### Disable/Power-Down

The EL5106 and EL5306 amplifiers can be disabled placing their output in a high impedance state. When disabled, the amplifier supply current is reduced to <25 $\mu$ A. The EL5106 and EL5306 are disabled when its  $\overline{\text{CE}}$  pin is pulled up to within 1V of the positive supply. Similarly, the amplifier is enabled by floating or pulling the  $\overline{\text{CE}}$  pin to at least 3V below

the positive supply. For  $\pm 5V$  supply, this means that the amplifier will be enabled when  $\overline{CE}$  is 2V or less, and disabled when  $\overline{CE}$  is above 4V. Although the logic levels are not standard TTL, this choice of logic voltages allow the EL5106 and EL5306 to be enabled by tying  $\overline{CE}$  to ground, even in 5V single supply applications. The  $\overline{CE}$  pin can be driven from CMOS outputs.

### **Gain Setting**

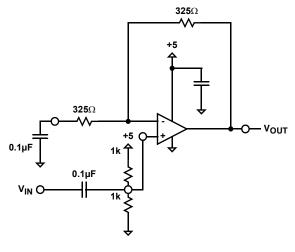

The EL5106 and EL5306 are built with internal feedback and gain resistors. The internal feedback resistors have equal value; as a result, the amplifier can be configured into gain of +1, -1, and +2 without any external resistors. Figure 14 shows the amplifier in gain of +2 configuration. The gain error is ±2% maximum. Figure 15 shows the amplifier in gain of -1 configuration. For gain of +1, IN+ and IN- should be connected together as shown in Figure 16. This configuration avoids the effects of any parasitic capacitance on the IN- pin. Since the internal feedback and gain resistors change with temperature and process, external resistor should not be used to adjust the gain settings.

FIGURE 14.  $A_V = +2$

intersil

FIGURE 15. A<sub>V</sub> = -1

FIGURE 16.  $A_V = +1$

# Supply Voltage Range and Single-Supply Operation

The EL5106 and EL5306 have been designed to operate with supply voltages having a span of greater than or equal to 5V and less than 11V. In practical terms, this means that the EL5106 and EL5306 will operate on dual supplies ranging from ±2.5V to ±5V. With single-supply, the EL5106 and EL5306 will operate from 5V to 10V.

As supply voltages continue to decrease, it becomes necessary to provide input and output voltage ranges that can get as close as possible to the supply voltages. The EL5106 and EL5306 have an input range which extends to within 2V of either supply. So, for example, on ±5V supplies, the EL5106 and EL5306 have an input range which spans ±3V. The output range is also quite large, extending to within 1V of the supply rail. On a ±5V supply, the output is therefore capable of swinging from -4V to +4V. Single-supply output range is larger because of the increased negative swing due to the external pull-down resistor to ground. Figure 16 shows an AC-coupled, gain of +2, +5V single supply circuit configuration.

FIGURE 17.

### Video Performance

For good video performance, an amplifier is required to maintain the same output impedance and the same frequency response as DC levels are changed at the output. This is especially difficult when driving a standard video load of  $150\Omega$ , because of the change in output current with DC level. Previously, good differential gain could only be achieved by running high idle currents through the output transistors (to reduce variations in output impedance). Special circuitries have been incorporated in the EL5106 and EL5306 to reduce the variation of output impedance with current output. This results in dG and dP specifications of 0.02% and 0.04°, while driving  $150\Omega$  at a gain of 2.

### Output Drive Capability

In spite of its low 1.5mA of supply current per amplifier, the EL5106 and EL5306 are capable of providing a maximum of  $\pm 125$ mA of output current.

### **Driving Cables and Capacitive Loads**

When used as a cable driver, double termination is always recommended for reflection-free performance. For those applications, the back-termination series resistor will decouple the EL5106 and EL5306 from the cable and allow extensive capacitive drive. However, other applications may have high capacitive loads without a back-termination resistor. In these applications, a small series resistor (usually between  $5\Omega$  and  $50\Omega$ ) can be placed in series with the output to eliminate most peaking.

### **Current Limiting**

The EL5106 and EL5306 have no internal current-limiting circuitry. If the output is shorted, it is possible to exceed the Absolute Maximum Rating for output current or power dissipation, potentially resulting in the destruction of the device.

### **Power Dissipation**

With the high output drive capability of the EL5106 and EL5306, it is possible to exceed the +125°C Absolute Maximum junction temperature under certain very high load current conditions. Generally speaking when  $R_L$  falls below about  $25\Omega_{\rm i}$  it is important to calculate the maximum junction temperature  $(T_{JMAX})$  for the application to determine if power supply voltages, load conditions, or package type need to be modified for the EL5106 and EL5306 to remain in the safe operating area. These parameters are calculated as shown in Equation 1:

$$T_{JMAX} = T_{MAX} + (\theta_{JA} \times n \times PD_{MAX})$$

(EQ. 1)

where:

T<sub>MAX</sub> = Maximum ambient temperature

$\theta_{JA}$  = Thermal resistance of the package

n = Number of amplifiers in the package

PD<sub>MAX</sub> = Maximum power dissipation of each amplifier in the package

PD<sub>MAX</sub> for each amplifier can be calculated as shown in Equation 2:

$$PD_{MAX} = (2 \times V_{S} \times I_{SMAX}) + \left[ (V_{S} - V_{OUTMAX}) \times \frac{V_{OUTMAX}}{R_{L}} \right]$$

(EQ. 2)

where:

V<sub>S</sub> = Supply voltage

I<sub>SMAX</sub> = Maximum bias supply current

V<sub>OUTMAX</sub> = Maximum output voltage (required)

R<sub>I</sub> = Load resistance

# **Revision History**

| DATE   | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6/4/09 | FN7357.6 | Removed obsolete, leaded devices EL5106IW-T7, EL5106IW-T7A; EL5106IS-T7, EL5306IS-T7, EL5306IS-T7, EL5306IS-T13; EL5306IS, EL5306IS-T7, EL5306IS-T13; EL5306IU, EL5306IU-T7, EL5306IU-T13 Corrected Figure references in "Gain Setting" on page 7 (Fig 14 callout was referencing Fig 13; Fig 15 callout was referencing Fig 14; Fig 16 callout was referencing Fig 15). Updated pin descriptions to match pin names of EL5306. Applied Intersil Standards: Updated Pb-free bullet in Features, Updated ordering information by removing tape and reel column and adding standard reference note and updating note to match lead finish, updated caution statement to legal's suggested verbiage. Changed date and Rev'd to 6. Updated POD MDP0038 toP6.064A - P6.064A replaces 6 Ld SOT-23 (same dimensions, just MDP0038 had both 5 & 6 Ld SOT23s w/dimensions listed in table) Updated POD MDP0027 to M8.15E - M8.15E replaces MDP0027 8 Ld SOIC (same dimensions, just MDP0027 had 8, 14, 16, 20, 24, 28 Ld SOICS with dimensions listed in table) P1, added Note 2 "The part marking is located on the bottom of the part" for SOT-23 package |

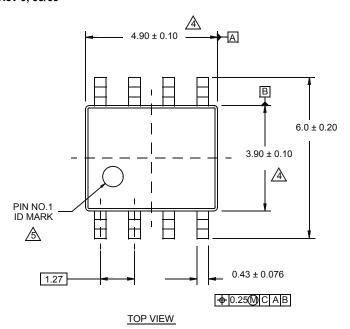

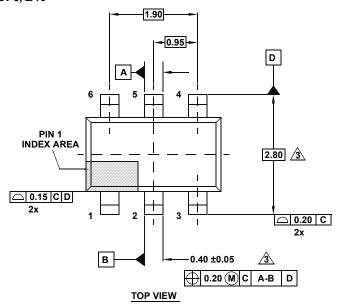

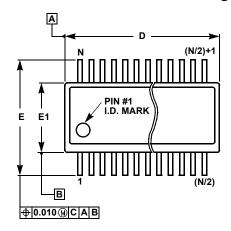

# **Package Outline Drawing**

M8.15E

8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

Rev 0, 08/09

### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal ± 0.05

- Dimension does not include interlead flash or protrusions.

Interlead flash or protrusions shall not exceed 0.25mm per side.

- 5. The pin #1 identifier may be either a mold or mark feature.

- 6. Reference to JEDEC MS-012.

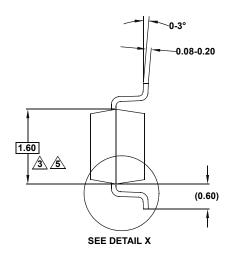

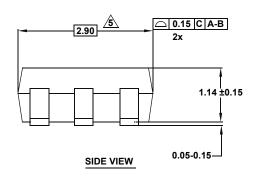

# **Package Outline Drawing**

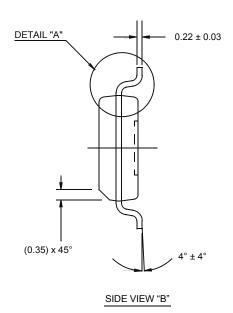

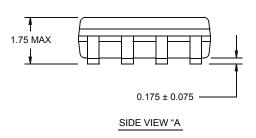

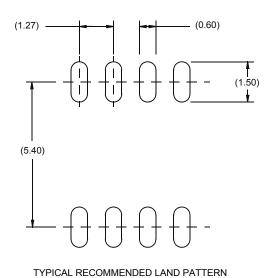

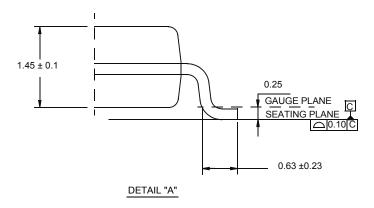

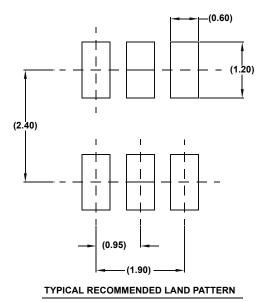

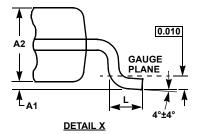

# P6.064A

**6 LEAD SMALL OUTLINE TRANSISTOR PLASTIC PACKAGE** Rev 0, 2/10

**END VIEW**

11

### NOTES:

- 1. Dimensions are in millimeters. Dimensions in ( ) for Reference Only.

- Dimensioning and tolerancing conform to ASME Y14.5M-1994.

- Dimension is exclusive of mold flash, protrusions or gate burrs.

- Foot length is measured at reference to guage plane.

- This dimension is measured at Datum "H".

- Package conforms to JEDEC MO-178AA.

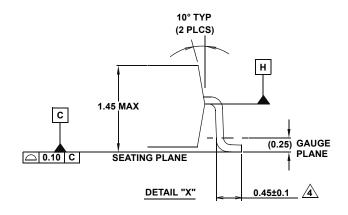

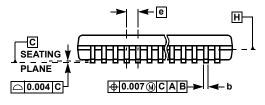

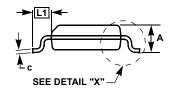

# Quarter Size Outline Plastic Packages Family (QSOP)

#### MDP0040

### QUARTER SIZE OUTLINE PLASTIC PACKAGES FAMILY

|        | INCHES |        |        |           |       |

|--------|--------|--------|--------|-----------|-------|

| SYMBOL | QSOP16 | QSOP24 | QSOP28 | TOLERANCE | NOTES |

| Α      | 0.068  | 0.068  | 0.068  | Max.      | -     |

| A1     | 0.006  | 0.006  | 0.006  | ±0.002    | -     |

| A2     | 0.056  | 0.056  | 0.056  | ±0.004    | -     |

| b      | 0.010  | 0.010  | 0.010  | ±0.002    | -     |

| С      | 0.008  | 0.008  | 0.008  | ±0.001    | -     |

| D      | 0.193  | 0.341  | 0.390  | ±0.004    | 1, 3  |

| Е      | 0.236  | 0.236  | 0.236  | ±0.008    | -     |

| E1     | 0.154  | 0.154  | 0.154  | ±0.004    | 2, 3  |

| е      | 0.025  | 0.025  | 0.025  | Basic     | -     |

| L      | 0.025  | 0.025  | 0.025  | ±0.009    | -     |

| L1     | 0.041  | 0.041  | 0.041  | Basic     | -     |

| N      | 16     | 24     | 28     | Reference | -     |

Rev. F 2/07

#### NOTES:

- Plastic or metal protrusions of 0.006" maximum per side are not included.

- Plastic interlead protrusions of 0.010" maximum per side are not included.

- 3. Dimensions "D" and "E1" are measured at Datum Plane "H".

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com