May 20, 2009

# LMP7732

# 2.9 nV/sqrt(Hz) Low Noise, RRIO Amplifier

### **General Description**

The LMP7732 is a dual low noise, rail-to-rail input and output, low voltage amplifier. The LMP7732 is part of the LMP® amplifier family and is ideal for precision and low noise applications with low voltage requirements.

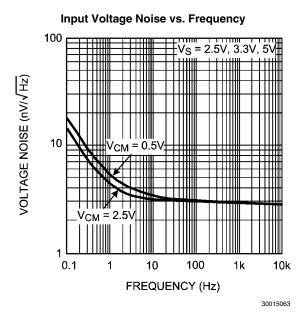

This operational amplifier offers low voltage noise of 2.9 nV/  $\sqrt{Hz}$  with a 1/f corner of only 3 Hz. The LMP7732 has bipolar junction input stages with a bias current of only 1.5 nA. This low input bias current, complemented by the very low level of voltage noise, makes the LMP7732 an excellent choice for photometry applications.

The LMP7732 provides a wide GBW of 22 MHz while consuming only 4 mA of current. This high gain bandwidth along with the high open loop gain of 130 dB enables accurate signal conditioning in applications with high closed loop gain requirements.

The LMP7732 has a supply voltage range of 1.8V to 5.5V, making it an ideal choice for battery operated portable applications.

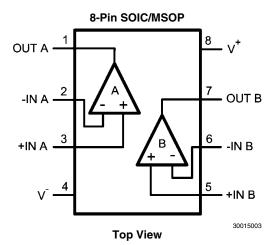

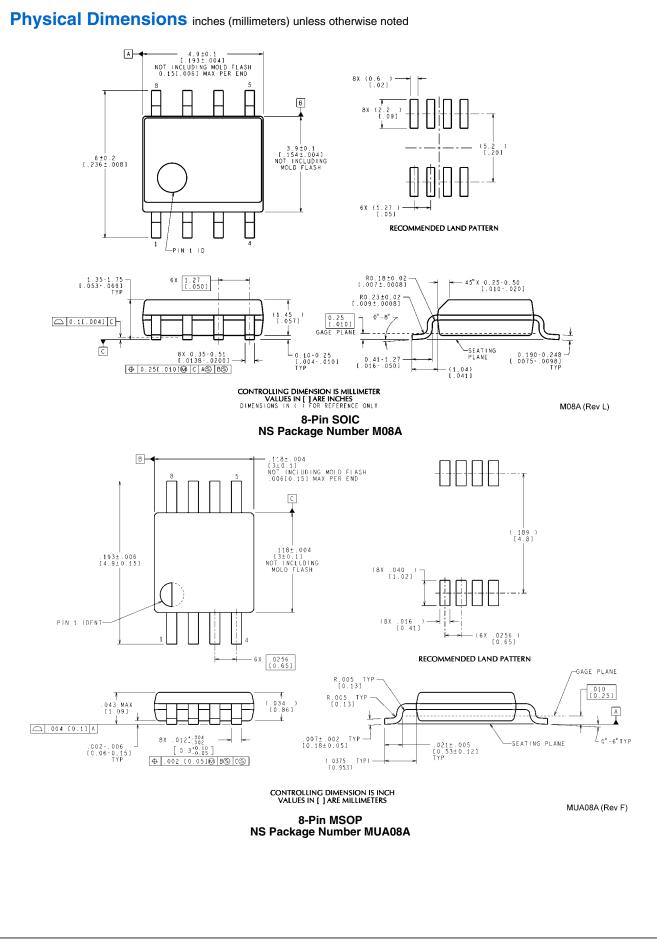

The LMP7732 is offered in the 8-Pin SOIC and MSOP packages.

The LMP7731 is the single version of this product and is offered in the 5-Pin SOT-23 and 8-Pin SOIC packages.

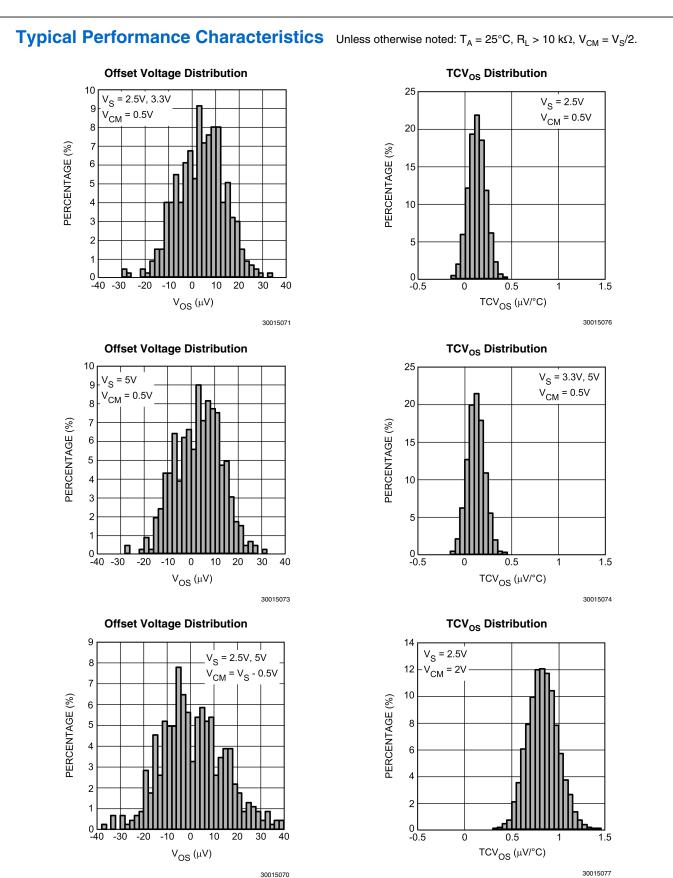

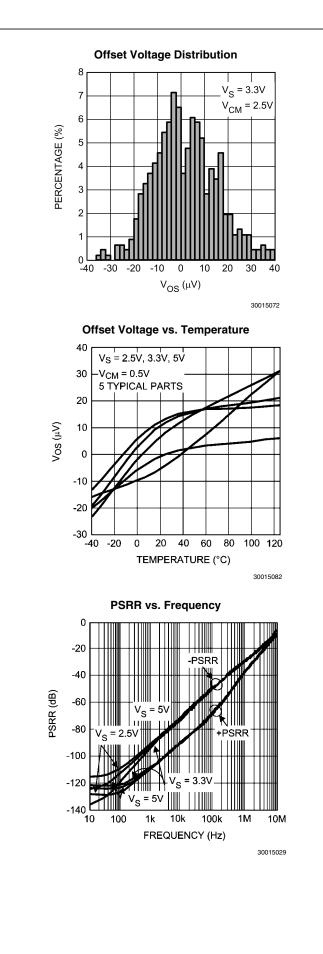

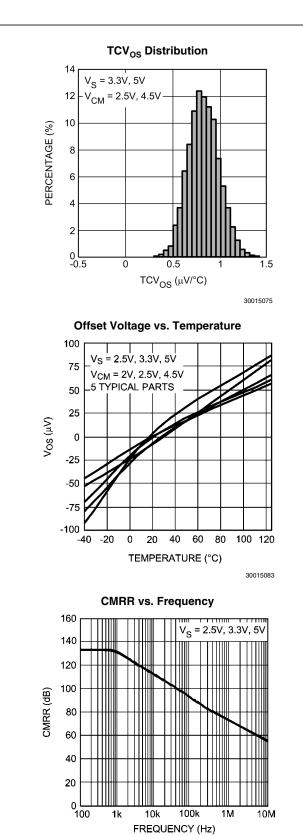

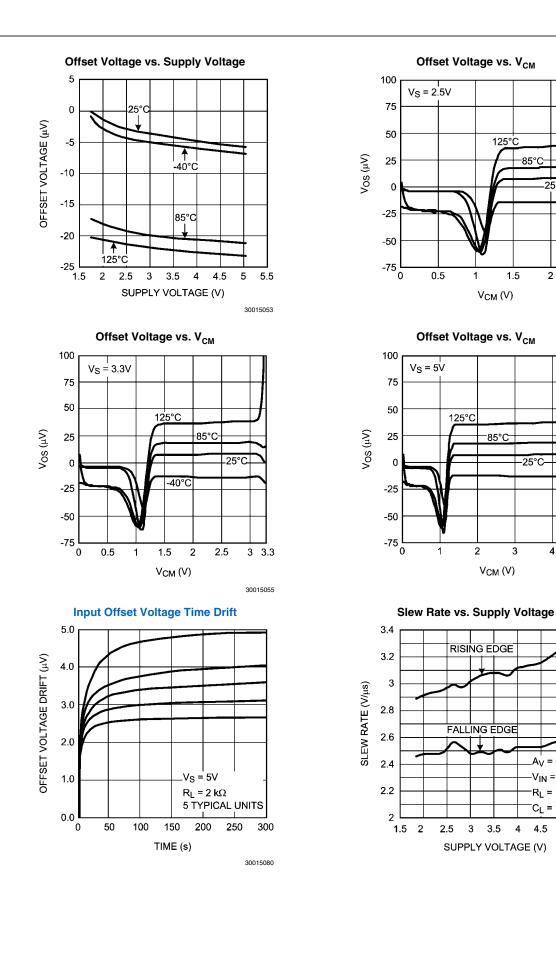

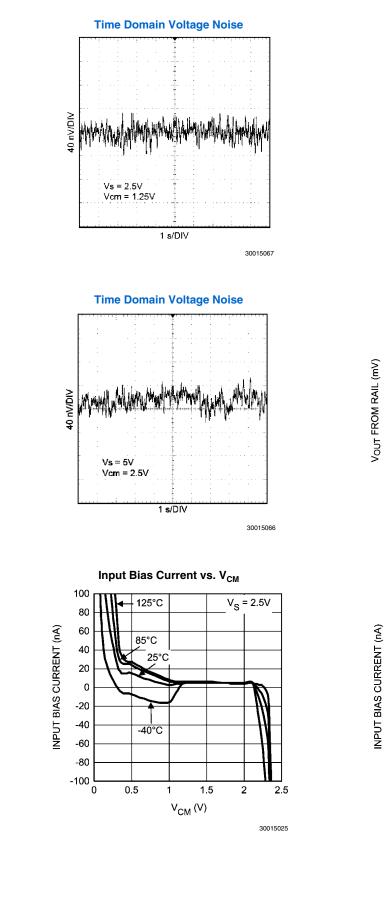

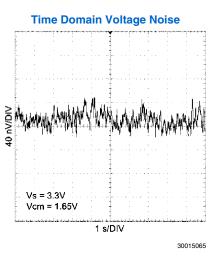

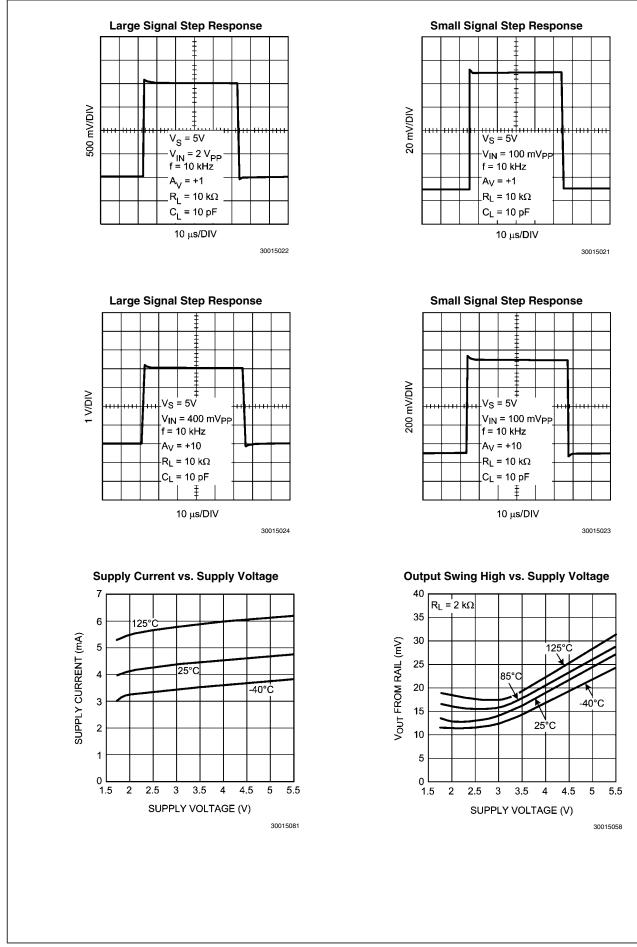

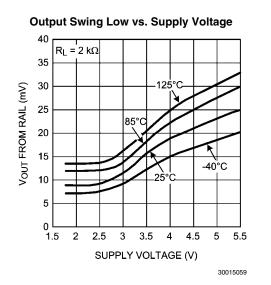

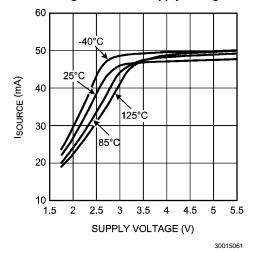

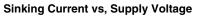

## **Typical Performance Characteristics**

### **Features**

(Typical values,  $T_A = 25^{\circ}C$ ,  $V_S = 5V$ )

| Input voltage noise                             |                |

|-------------------------------------------------|----------------|

| — f = 3 Hz                                      | 3.3 nV/√Hz     |

| f = 1 kHz                                       | 2.9 nV/√Hz     |

| CMRR                                            | 130 dB         |

| Open loop gain                                  | 130 dB         |

| GBW                                             | 22 MHz         |

| Slew rate                                       | 2.4 V/µs       |

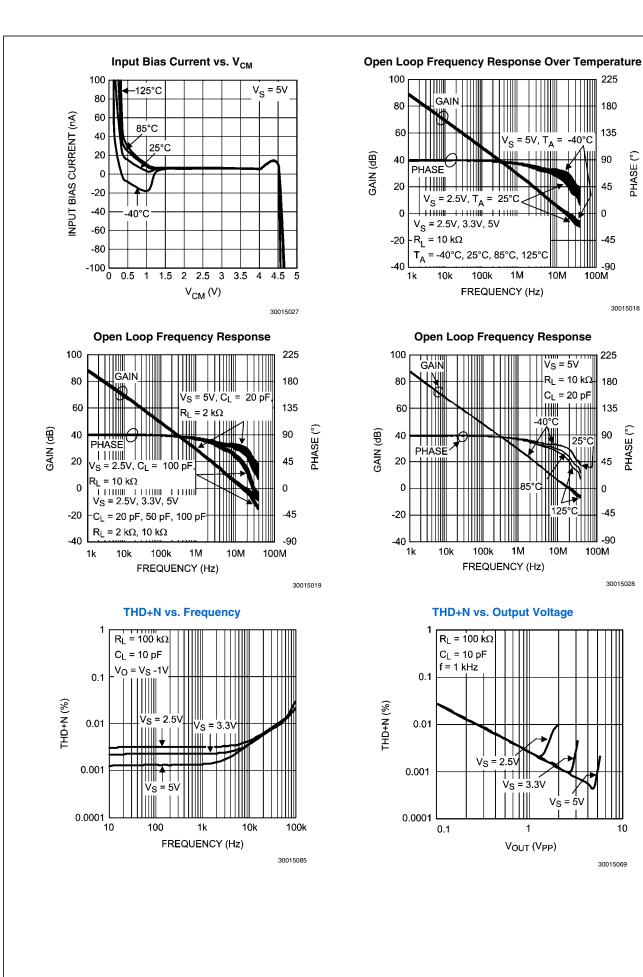

| THD @ f = 10 kHz, $A_V = 1$ , $R_L = 2 k\Omega$ | 0.001%         |

| Supply current                                  | 4.4 mA         |

| Supply voltage range                            | 1.8V to 5.5V   |

| Operating temperature range                     | –40°C to 125°C |

| Input bias current                              | ±1.5 nA        |

|                                                 |                |

RRIO

### Applications

- Gas analysis instruments

- Photometric instrumentation

- Medical instrumentation

### Input Current Noise vs. Frequency 100 V<sub>S</sub> = 2.5V, 3.3V, 5 CURRENT NOISE (pA/VHz) = 0.5 10 V<sub>CM</sub> = 2.5\ 1 0.1 1 10 100 1k 10k FREQUENCY (Hz)

30015064

# MP7732 2.9 nV/sqrt(Hz) Low Noise, RRIO Amplifier

LMP® is a registered trademark of National Semiconductor Corporation.

300150

© 2009 National Semiconductor Corporation

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| ESD Tolerance (Note 2)               |       |

|--------------------------------------|-------|

| Human Body Model                     |       |

| For inputs pins only                 | 2000V |

| For all other pins                   | 2000V |

| Machine Model                        | 200V  |

| Charge Device Model                  | 1000V |

| V <sub>IN</sub> Differential         | ±2V   |

| Supply Voltage ( $V_S = V^+ - V^-$ ) | 6.0V  |

|                                      |       |

| Storage Temperature Range          | –65°C to 150°C |

|------------------------------------|----------------|

| Junction Temperature (Note 3)      | +150°C max     |

| Soldering Information              |                |

| Infrared or Convection (20 sec)    | 235°C          |

| Wave Soldering Lead Temp. (10 sec) | 260°C          |

### **Operating Ratings** (Note 1)

| Temperature Range                            | –40°C to 125°C |

|----------------------------------------------|----------------|

| Supply Voltage ( $V_S = V^+ - V^-$ )         | 1.8V to 5.5V   |

| Package Thermal Resistance ( $\theta_{JA}$ ) |                |

| 8-Pin SOIC                                   | 190 °C/W       |

| 8-Pin MSOP                                   | 235°C/W        |

### 2.5V Electrical Characteristics (Note 4)

Unless otherwise specified, all limits are guaranteed for  $T_A = 25^{\circ}C$ ,  $V^+ = 2.5V$ ,  $V^- = 0V$ ,  $V_{CM} = V^+/2$ ,  $R_L > 10 \text{ k}\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                                                           | Conditions                                                                                                                 | Min<br>(Note 6)   | Typ<br>(Note 5) | Max<br>(Note 6)     | Units |

|-------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|---------------------|-------|

| V <sub>OS</sub>   | Input Offset Voltage<br>(Note 7) $V_{CM} = 2.0V$<br>$V_{CM} = 0.5V$ | V <sub>CM</sub> = 2.0V                                                                                                     |                   | ±9              | ±500<br><b>±600</b> | υM    |

|                   |                                                                     | $V_{CM} = 0.5V$                                                                                                            |                   | ±9              | ±500<br><b>±600</b> | μV    |

| TCV <sub>os</sub> | Input Offset Voltage Temperature Drift                              | V <sub>CM</sub> = 2.0V                                                                                                     |                   | ±0.5            | ±5.5                | µV/°C |

| 10V <sub>OS</sub> |                                                                     | $V_{CM} = 0.5V$                                                                                                            |                   | ±0.2            | ±5.5                | μν/ Ο |

| 1                 | Input Pice Current                                                  | V <sub>CM</sub> = 2.0V                                                                                                     |                   | ±1              | ±30<br><b>±45</b>   | ۳Å    |

| I <sub>B</sub>    | Input Bias Current                                                  | $V_{CM} = 0.5V$                                                                                                            |                   | ±12             | ±50<br><b>±75</b>   | nA    |

| 1                 | Input Offset Current                                                | V <sub>CM</sub> = 2.0V                                                                                                     |                   | ±1              | ±50<br><b>±75</b>   | nA    |

| I <sub>OS</sub>   |                                                                     | V <sub>CM</sub> = 0.5V                                                                                                     |                   | ±11             | ±60<br><b>±80</b>   |       |

| TCI <sub>OS</sub> | Input Offset Current Drift                                          | $V_{CM} = 0.5V$ and $V_{CM} = 2.0V$                                                                                        |                   | 0.0474          |                     | nA/°C |

| CMRR              | Common Mode Rejection Ratio                                         | $\begin{array}{l} 0.15 V \leq V_{CM} \leq 0.7 V \\ 0.23 V \leq V_{CM} \leq 0.7 V \end{array}$                              | 101<br><b>89</b>  | 120             |                     | dD    |

| CIVINN            |                                                                     | $1.5V \le V_{CM} \le 2.35V$<br>$1.5V \le V_{CM} \le 2.27V$                                                                 | 105<br><b>99</b>  | 129             |                     | dB    |

| PSRR              | Power Supply Rejection Ratio                                        | 2.5V ≤ V+ ≤ 5V                                                                                                             | 111<br><b>105</b> | 129             |                     | dB    |

|                   |                                                                     | $1.8V \leq V^+ \leq 5.5V$                                                                                                  |                   | 117             |                     |       |

| CMVR              | Common Mode Voltage Range                                           | Large Signal CMRR ≥ 80 dB                                                                                                  | 0                 |                 | 2.5                 | V     |

| A <sub>VOL</sub>  | Onen Loon Voltage Gain                                              | $\begin{aligned} R_L &= 10 \text{ k}\Omega \text{ to V}^{+\!/2} \\ V_{OUT} &= 0.5 \text{V to } 2.0 \text{V} \end{aligned}$ | 112<br><b>104</b> | 130             |                     | dB    |

| ~VOL              | Open Loop Voltage Gain                                              | $R_L = 2 k\Omega$ to V+/2<br>V <sub>OUT</sub> = 0.5V to 2.0V                                                               | 109<br><b>90</b>  | 119             |                     | uВ    |

| Symbol           | Parameter                            | Conditions                                                                                                 | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6)   | Units            |  |

|------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-------------------|------------------|--|

|                  | Output Voltage Quing High            | $R_L = 10 \text{ k}\Omega \text{ to } V^+/2$                                                               |                 | 4               | 50<br><b>75</b>   |                  |  |

| V                | Output Voltage Swing High            | $R_L = 2 k\Omega$ to V+/2                                                                                  |                 | 13              | 50<br><b>75</b>   | mV from          |  |

| V <sub>OUT</sub> |                                      | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                                                                |                 | 6               | 50<br><b>75</b>   | either rail      |  |

|                  | Output Voltage Swing Low             | $R_L = 2 k\Omega$ to V+/2                                                                                  |                 | 9               | 50<br><b>75</b>   |                  |  |

| 1                | Output Current                       | Sourcing, V <sub>OUT</sub> = V+/2<br>V <sub>IN</sub> (diff) = 100 mV                                       | 22<br>12        | 31              |                   |                  |  |

| I <sub>OUT</sub> | Output Current                       | Sinking, $V_{OUT} = V^+/2$<br>$V_{IN}$ (diff) = -100 mV                                                    | 15<br><b>10</b> | 44              |                   | mA               |  |

|                  | Supply Current                       | V <sub>CM</sub> = 2.0V                                                                                     |                 | 4.0             | 5.4<br><b>6.8</b> |                  |  |

| I <sub>S</sub>   |                                      | $V_{CM} = 0.5V$                                                                                            |                 | 4.6             | 6.2<br><b>7.8</b> | - mA             |  |

| SR               | Slew Rate                            | $A_V = +1, C_L = 10 \text{ pF}, R_L = 10 \text{ k}\Omega \text{ to V}^+/2$<br>$V_{OUT} = 2 \text{ V}_{PP}$ |                 | 2.4             |                   | V/µs             |  |

| GBW              | Gain Bandwidth                       | $C_{L} = 20 \text{ pF}, \text{ R}_{L} = 10 \text{ k}\Omega \text{ to V}^{+}/2$                             |                 | 21              |                   | MHz              |  |

| G <sub>M</sub>   | Gain Margin                          | $C_{L} = 20 \text{ pF}, \text{ R}_{L} = 10 \text{ k}\Omega \text{ to V}^{+}/2$                             |                 | 14              |                   | dB               |  |

| Φ <sub>M</sub>   | Phase Margin                         | $C_{L} = 20 \text{ pF}, \text{ R}_{L} = 10 \text{ k}\Omega \text{ to V}^{+}/2$                             |                 | 60              |                   | deg              |  |

| D                |                                      | Differential Mode                                                                                          |                 | 38              |                   | kΩ               |  |

| R <sub>IN</sub>  | Input Resistance                     | Common Mode                                                                                                |                 | 151             |                   | MΩ               |  |

| THD+N            | Total Harmonic Distortion + Noise    | $A_V = 1$ , $f_O = 1$ kHz, Amplitude = 1V                                                                  |                 | 0.002           |                   | %                |  |

|                  | Input Referred Voltage Noise Density | f = 1 kHz, V <sub>CM</sub> = 2.0V                                                                          |                 | 3.0             |                   | nV/√Hz           |  |

| e <sub>n</sub>   |                                      | f = 1 kHz, V <sub>CM</sub> = 0.5V                                                                          |                 | 3.0             |                   | _ nv/√Hz         |  |

|                  | Input Voltage Noise                  | 0.1 Hz to 10 Hz                                                                                            |                 | 75              |                   | nV <sub>PP</sub> |  |

| i <sub>n</sub>   | Input Referred Current Noise Density | f = 1 kHz, V <sub>CM</sub> = 2.0V                                                                          | ļ               | 1.1             |                   | pA/√Hz           |  |

| 'n               |                                      | f = 1 kHz, V <sub>CM</sub> = 0.5V                                                                          |                 | 2.3             |                   | pav√ Hz          |  |

# 3.3V Electrical Characteristics (Note 4)

Unless otherwise specified, all limits are guaranteed for  $T_A = 25^{\circ}C$ ,  $V^+ = 3.3V$ ,  $V^- = 0V$ ,  $V_{CM} = V^+/2$ ,  $R_L > 10 \text{ k}\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol             | Parameter                              | Conditions             | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6)     | Units |

|--------------------|----------------------------------------|------------------------|-----------------|-----------------|---------------------|-------|

|                    | Input Offset Voltage                   | V <sub>CM</sub> = 2.5V |                 | ±6              | ±500<br><b>±600</b> |       |

| V <sub>OS</sub>    | (Note 7)                               | V <sub>CM</sub> = 0.5V |                 | ±6              | ±500<br><b>±600</b> | μV    |

| TCV <sub>os</sub>  | Input Offset Voltage Temperature Drift | V <sub>CM</sub> = 2.5V |                 | ±0.5            | ±5.5                |       |

| 10 v <sub>os</sub> |                                        | V <sub>CM</sub> = 0.5V |                 | ±0.2            | ±5.5                | μV/°C |

| 1                  | Input Bias Current                     | V <sub>CM</sub> = 2.5V |                 | ±1.5            | ±30<br><b>±45</b>   | 54    |

| I <sub>B</sub>     |                                        | V <sub>CM</sub> = 0.5V |                 | ±13             | ±50<br><b>±77</b>   | nA    |

| I <sub>OS</sub>    | Input Offset Current                   | V <sub>CM</sub> = 2.5V |                 | ±1              | ±50<br><b>±70</b>   | 54    |

|                    |                                        | V <sub>CM</sub> = 0.5V |                 | ±11             | ±60<br><b>±80</b>   | nA    |

LMP7732

# LMP7732

| Symbol            | Parameter                            | Conditions                                                                     | Min<br>(Note 6)  | Typ<br>(Note 5) | Max<br>(Note 6)          | Units            |  |

|-------------------|--------------------------------------|--------------------------------------------------------------------------------|------------------|-----------------|--------------------------|------------------|--|

| TCI <sub>OS</sub> | Input Offset Current Drift           | $V_{CM} = 0.5V$ and $V_{CM} = 2.5V$                                            |                  | 0.048           | , ,                      | nA/°C            |  |

|                   |                                      | $0.15V \le V_{CM} \le 0.7V$                                                    | 101              | 120             |                          |                  |  |

| CMRR              | Common Mode Rejection Ratio          | $0.23V \le V_{CM} \le 0.7V$                                                    | 89               |                 |                          |                  |  |

|                   |                                      | $1.5V \le V_{CM} \le 3.15V$                                                    | 105              | 130             |                          | dB               |  |

|                   |                                      | $1.5V \le V_{CM} \le 3.07V$                                                    | 99               |                 |                          |                  |  |

|                   |                                      | 2.5V ≤ V+ ≤ 5.0V                                                               | 111              | 129             |                          |                  |  |

| PSRR              | Power Supply Rejection Ratio         |                                                                                | 105              |                 |                          | dB               |  |

|                   |                                      | 1.8V ≤ V+ ≤ 5.5V                                                               |                  | 117             |                          |                  |  |

| CMVR              | Common Mode Voltage Range            | Large Signal CMRR ≥ 80 dB                                                      | 0                |                 | 3.3                      | V                |  |

|                   |                                      | $R_L = 10 \text{ k}\Omega \text{ to V}$ +/2                                    | 112              | 130             |                          |                  |  |

| A <sub>VOL</sub>  | Open Loop Voltage Gain               | $V_{OUT} = 0.5V$ to 2.8V                                                       | 104              |                 |                          | dB               |  |

| VOL               |                                      | $R_{\rm L} = 2 \ \rm k\Omega \ to \ V^{+}/2$                                   | 110<br><b>92</b> | 119             |                          |                  |  |

|                   |                                      | $V_{OUT} = 0.5V$ to 2.8V                                                       | 92               |                 | 50                       |                  |  |

|                   | Output Voltage Swing High            | $R_L = 10 \text{ k}\Omega \text{ to } V^+/2$                                   |                  | 5               | 50<br><b>75</b>          | mV from          |  |

|                   |                                      |                                                                                |                  |                 | 50                       |                  |  |

| V                 |                                      | $R_L = 2 k\Omega$ to V+/2                                                      |                  | 14              | 75                       |                  |  |

| V <sub>OUT</sub>  | Output Voltage Swing Low             | $R_{\rm L} = 10 \text{ k}\Omega$ to V+/2                                       |                  | 9               | 50                       | either ra        |  |

|                   |                                      |                                                                                |                  |                 | 75                       |                  |  |

|                   |                                      | $R_L = 2 k\Omega$ to V+/2                                                      |                  | 13              | 50<br><b>75</b>          | l                |  |

|                   | Output Current                       | Sourcing, V <sub>OUT</sub> = V <sup>+</sup> /2                                 | 28               | 45              | /3                       |                  |  |

|                   |                                      | $V_{IN}$ (diff) = 100 mV                                                       | 22               |                 |                          | mA               |  |

| I <sub>OUT</sub>  |                                      | Sinking, $V_{OUT} = V^{+}/2$                                                   | 25               | 48              |                          |                  |  |

|                   |                                      | $V_{IN}$ (diff) = -100 mV                                                      | 20               |                 |                          |                  |  |

|                   |                                      | V <sub>CM</sub> = 2.5V                                                         |                  | 4.2             | 5.6<br><b>7.0</b><br>6.4 | - mA             |  |

| I <sub>S</sub>    | Supply Current                       |                                                                                |                  |                 |                          |                  |  |

|                   |                                      | V <sub>CM</sub> = 0.5V                                                         |                  | 4.8             | 6.4<br><b>8.0</b>        |                  |  |

|                   |                                      | $A_V = +1, C_L = 10 \text{ pF}, R_L = 10 \text{ k}\Omega \text{ to V}^+/2$     |                  |                 |                          |                  |  |

| SR                | Slew Rate                            | $V_{OUT} = 2 V_{PP}$                                                           |                  | 2.4             |                          | V/µs             |  |

| GBW               | Gain Bandwidth                       | $C_L = 20 \text{ pF}, \text{ R}_L = 10 \text{ k}\Omega \text{ to V}^+/2$       |                  | 22              |                          | MHz              |  |

| G <sub>M</sub>    | Gain Margin                          | $C_{L} = 20 \text{ pF}, \text{ R}_{L} = 10 \text{ k}\Omega \text{ to V}^{+/2}$ |                  | 14              |                          | dB               |  |

| Φ <sub>M</sub>    | Phase Margin                         | $C_{L} = 20 \text{ pF}, \text{ R}_{L} = 10 \text{ k}\Omega \text{ to V}$ +/2   |                  | 62              |                          | deg              |  |

| THD+N             | Total Harmonic Distortion + Noise    | $A_{V} = 1, f_{O} = 1 \text{ kHz}, \text{ Amplitude} = 1V \qquad 0.002$        |                  |                 | %                        |                  |  |

| Р                 | Innut Desistance                     | Differential Mode                                                              |                  | 38              |                          | kΩ               |  |

| R <sub>IN</sub>   | Input Resistance                     | Common Mode                                                                    |                  | 151             |                          | MΩ               |  |

|                   | Input Referred Voltage Noise Density | f = 1 kHz, V <sub>CM</sub> = 2.5V                                              |                  | 2.9             |                          | nV/√H:           |  |

| e <sub>n</sub>    | Input Referred Voltage Noise Density | f = 1 kHz, V <sub>CM</sub> = 0.5V                                              |                  | 2.9             |                          | nv/√H:           |  |

|                   | Input Voltage Noise                  | 0.1 Hz to 10 Hz                                                                |                  | 75              |                          | nV <sub>PP</sub> |  |

| i                 | Input Referred Current Noise Density | f = 1 kHz, V <sub>CM</sub> = 2.5V                                              |                  | 1.1             |                          |                  |  |

| i <sub>n</sub>    |                                      | f = 1 kHz, V <sub>CM</sub> = 0.5V                                              |                  | 2.1             |                          | pA/√Hz           |  |

# 5V Electrical Characteristics (Note 4)

Unless otherwise specified, all limits are guaranteed for  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V^+/2$ ,  $R_L > 10 \text{ k}\Omega$  to  $V^+/2$ . Boldface limits apply at the temperature extremes.

| Symbol            | Parameter                              | Conditions                                                                                    | Min<br>(Note 6)   | Typ<br>(Note 5) | Max<br>(Note 6)     | Units                  |

|-------------------|----------------------------------------|-----------------------------------------------------------------------------------------------|-------------------|-----------------|---------------------|------------------------|

| V <sub>os</sub>   | Input Offset Voltage                   | $V_{CM} = 4.5V$                                                                               |                   | ±6              | ±500<br><b>±600</b> |                        |

| <b>V</b> OS       | (Note 7)                               | $V_{CM} = 0.5V$                                                                               |                   | ±6              | ±500<br><b>±600</b> | μV                     |

| TCV <sub>os</sub> | Input Offset Voltage Temperature Drift | V <sub>CM</sub> = 4.5V                                                                        |                   | ±0.5            | ±5.5                | μV/°C                  |

| 03                |                                        | V <sub>CM</sub> = 0.5V                                                                        |                   | ±0.2            | ±5.5                | P                      |

| I <sub>B</sub>    | Input Bias Current                     | V <sub>CM</sub> = 4.5V                                                                        |                   | ±1.5            | ±30<br><b>±50</b>   | nA                     |

| D                 | '<br>                                  | V <sub>CM</sub> = 0.5V                                                                        |                   | ±14             | ±50<br><b>±85</b>   |                        |

| laa               | Input Offset Current                   | V <sub>CM</sub> = 4.5V                                                                        |                   | ±1              | ±50<br><b>±70</b>   | nA                     |

| l <sub>os</sub>   |                                        | $V_{CM} = 0.5V$                                                                               |                   | ±11             | ±65<br><b>±80</b>   |                        |

| TCI <sub>OS</sub> | Input Offset Current Drift             | $V_{CM} = 0.5V$ and $V_{CM} = 4.5V$                                                           |                   | 0.0482          |                     | nA/°C                  |

| CMRR              |                                        | $\begin{array}{l} 0.15 V \leq V_{CM} \leq 0.7 V \\ 0.23 V \leq V_{CM} \leq 0.7 V \end{array}$ | 101<br><b>89</b>  | 120             |                     |                        |

|                   | Common Mode Rejection Ratio            | $1.5V \le V_{CM} \le 4.85V$                                                                   | 105               | 130             |                     | dB                     |

|                   |                                        | $1.5V \le V_{CM} \le 4.77V$                                                                   | 99                |                 |                     |                        |

| PSRR              | Power Supply Rejection Ratio           | $2.5V \le V^+ \le 5V$                                                                         | 111<br><b>105</b> | 129             |                     |                        |

|                   |                                        | 1.8V ≤ V+ ≤ 5.5V                                                                              | 105               | 117             |                     | dB                     |

| CMVR              | Common Mode Voltage Range              | Large Signal CMRR ≥ 80 dB                                                                     | 0                 |                 | 5                   | v                      |

|                   |                                        | $R_1 = 10 \text{ k}\Omega \text{ to V+/2}$                                                    | 112               | 130             | <u> </u>            | - dB                   |

| •                 |                                        | $V_{OUT}^{L} = 0.5V$ to 4.5V                                                                  | 104               |                 |                     |                        |

| A <sub>VOL</sub>  | Open Loop Voltage Gain                 | $R_L = 2 k\Omega$ to V+/2                                                                     | 110               | 119             |                     |                        |

|                   |                                        | V <sub>OUT</sub> = 0.5V to 4.5V                                                               | 94                |                 |                     |                        |

|                   | Output Maltana Outpat Link             | $R_L = 10 \text{ k}\Omega \text{ to } V^+/2$                                                  |                   | 8               | 50<br><b>75</b>     |                        |

| V                 | Output Voltage Swing High              | $R_L = 2 k\Omega$ to V+/2                                                                     |                   | 24              | 50<br><b>75</b>     | mV from<br>either rail |

| V <sub>OUT</sub>  | Outrut Mathema Outra Law               | $R_L = 10 \text{ k}\Omega$ to V+/2                                                            |                   | 9               | 50<br><b>75</b>     |                        |

|                   | Output Voltage Swing Low               | $R_L = 2 k\Omega$ to V+/2                                                                     |                   | 23              | 50<br><b>75</b>     |                        |

| _                 |                                        | Sourcing, $V_{OUT} = V^{+/2}$<br>$V_{ N}$ (diff) = 100 mV                                     | 33<br>27          | 47              |                     | - mA                   |

| I <sub>OUT</sub>  | Output Current                         | Sinking, $V_{OUT} = V^{+/2}$<br>$V_{IN}$ (diff) = -100 mV                                     | 30<br><b>25</b>   | 49              |                     |                        |

|                   |                                        | $V_{CM} = 4.5V$                                                                               |                   | 4.4             | 6.0<br><b>7.4</b>   |                        |

| I <sub>S</sub>    | Supply Current                         | V <sub>CM</sub> = 0.5V                                                                        |                   | 5.0             | 6.8<br><b>8.4</b>   | - mA                   |

| SR                | Slew Rate                              | $A_V$ = +1, $C_L$ = 10 pF, $R_L$ = 10 kΩ to V+/2<br>V <sub>OUT</sub> = 2 V <sub>PP</sub>      |                   | 2.4             | 7.7                 | V/µs                   |

|                   |                                        |                                                                                               |                   |                 |                     |                        |

LMP7732

| Symbol          | Parameter                            | Conditions                                                               | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6) | Units            |  |

|-----------------|--------------------------------------|--------------------------------------------------------------------------|-----------------|-----------------|-----------------|------------------|--|

| G <sub>M</sub>  | Gain Margin                          | $C_L = 20 \text{ pF}, \text{ R}_L = 10 \text{ k}\Omega \text{ to V}^+/2$ |                 | 12              |                 | dB               |  |

| Φ <sub>M</sub>  | Phase Margin                         | $C_L = 20 \text{ pF}, \text{ R}_L = 10 \text{ k}\Omega \text{ to V}^+/2$ |                 | 65              |                 | deg              |  |

| Р               | Input Resistance                     | Differential Mode                                                        |                 | 38              |                 | kΩ               |  |

| R <sub>IN</sub> |                                      | Common Mode                                                              |                 | 151             |                 | MΩ               |  |

| THD+ N          | Total Harmonic Distortion + Noise    | $A_V = 1$ , $f_O = 1$ kHz, Amplitude = 1V                                |                 | 0.001           |                 | %                |  |

|                 |                                      | f = 1 kHz, V <sub>CM</sub> = 4.5V                                        |                 | 2.9             |                 |                  |  |

| e <sub>n</sub>  | Input Referred Voltage Noise Density | f = 1 kHz, V <sub>CM</sub> = 0.5V                                        |                 | 2.9             |                 | nV/√Hz           |  |

|                 | Input Voltage Noise                  | 0.1 Hz to 10 Hz                                                          |                 | 75              |                 | nV <sub>PP</sub> |  |

| :               | Input Referred Current Noise Depoits | f = 1 kHz, V <sub>CM</sub> = 4.5V                                        |                 | 1.1             |                 |                  |  |

| 'n              | Input Referred Current Noise Density | f = 1 kHz, V <sub>CM</sub> = 0.5V                                        |                 | 2.2             |                 | pA/√Hz           |  |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics Tables.

Note 2: Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC) Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

**Note 3:** The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ , and  $T_{A}$ . The maximum allowable power dissipation at any ambient temperature is  $P_{D} = (T_{J(MAX)} - T_{A})/|\theta_{JA}|$ . All numbers apply for packages soldered directly onto a PC board.

**Note 4:** Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ . Absolute maximum Ratings indicate junction temperature limits beyond which the device maybe permanently degraded, either mechanically or electrically.

Note 5: Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

Note 6: All limits are guaranteed by testing, statistical analysis or design.

Note 7: Ambient production test is performed at 25°C with a variance of  $\pm 3^{\circ}C.$

### **Connection Diagram**

### **Ordering Information**

| Package     | Part Number | Package Marking | Transport Media          | NSC Drawing |

|-------------|-------------|-----------------|--------------------------|-------------|

| 8-Pin SOIC  | LMP7732MA   | LMP7732MA       | 95 units/Rails           | M08A        |

| 0-PIII 3010 | LMP7732MAX  | LIVIP7732IVIA   | 2.5k Units Tape and Reel | IVIUOA      |

|             | LMP7732MM   |                 | 1k Units Tape and Reel   |             |

| 8-Pin MSOP  | LMP7732MME  | AZ3A            | 250 Units Tape and Reel  | MUA08A      |

|             | LMP7732MMX  |                 | 3.5k Units Tape and Reel |             |

www.national.com

www.national.com

LMP7732

-85°C-

25

2

-25°C-

3

-40°C

5

30015056

4

A<sub>V</sub> = +1

VIN = 1 VPP

R<sub>L</sub> = 10 kΩ

<sup>-</sup>C<sub>L</sub> = 10 pF

30015020

4 4.5 5 5.5

-40°C

2.5

30015054

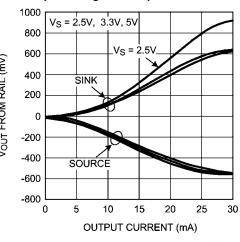

**Output Voltage vs. Output Current**

30015057

www.national.com

-45

-90

25°C

-90

100M

PHASE (°)

100M

PHASE (°)

40°C

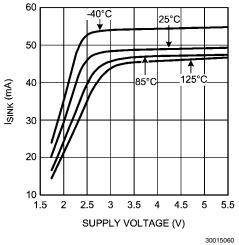

Sourcing Current vs. Supply Voltage

# **Application Notes**

### LMP7732

The LMP7732 is a dual low noise, rail-to-rail input and output, low voltage amplifier.

The low input voltage noise of only 2.9  $nV/\sqrt{Hz}$  with a 1/f corner at 3 Hz makes the LMP7732 ideal for sensor applications where DC accuracy is of importance.

The LMP7732 has high gain bandwidth of 22 MHz. This wide bandwidth enables the use of the amplifier at higher gain settings while retaining ample usable bandwidth for the application. This is particularly beneficial when system designers need to use sensors with very limited output voltage range as it allows larger gains in one stage which in turn increases signal to noise ratio.

The LMP7732 has a proprietary input bias cancellation circuitry on the input stages. This allows the LMP7732 to have only about 1.5 nA bias current with a bipolar input stage. This low input bias current, paired with the inherent lower input voltage noise of bipolar input stages makes the LMP7732 an excellent choice for precision applications. The combination of low input bias current, low input offset voltage, and low input voltage noise enables the user to achieve unprecedented accuracy and higher signal integrity.

National Semiconductor is heavily committed to precision amplifiers and the market segment they serve. Technical support and extensive characterization data is available for sensitive applications or applications with a constrained error budget.

The LMP7732 comes in the 8-Pin SOIC and MSOP packages. These small packages are ideal solutions for area constrained PC boards and portable electronics.

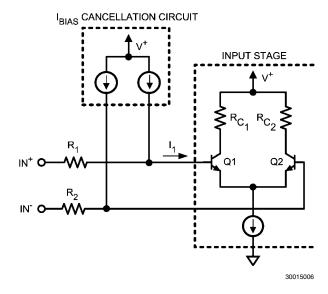

### INPUT BIAS CURRENT CANCELLATION

The LMP7732 has proprietary input bias current cancellation circuitry on its input stage.

The LMP7732 has rail-to-rail input. This is achieved by having a p-input and n-input stage in parallel. *Figure 1* only shows one of the input stages as the circuitry is symmetrical for both stages. *Figure 1* shows that as the common mode voltage gets closer to one of the extreme ends, current  $I_1$  significantly increases. This increased current shows as an increase in voltage drop across resistor  $R_1$  equal to  $I_1 * R_1$  on IN+ of the amplifier. This voltage contributes to the offset voltage of the amplifier. When common mode voltage is in the mid-range, the transistors are operating in the linear region and  $I_1$  is significantly small. The voltage drop due to  $I_1$  across  $R_1$  can be ignored as it is orders of magnitude smaller than the amplifier's input offset voltage. As the common mode voltage gets closer to one of the rails, the offset voltage generated due to  $I_1$  increases and becomes comparable to the amplifiers offset voltage.

FIGURE 1. Input Bias Current Cancellation

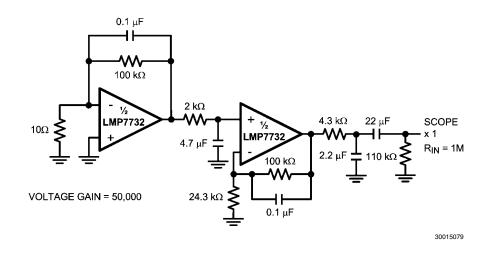

### **INPUT VOLTAGE NOISE MEASUREMENT**

The LMP7732 has very low input voltage noise. The peak-topeak input voltage noise of the LMP7732 can be measured using the test circuit shown in *Figure 2*

FIGURE 2. 0.1 Hz to 10 Hz Noise Test Circuit

The frequency response of this noise test circuit at the 0.1 Hz corner is defined by only one zero. The test time for the 0.1 Hz to 10 Hz noise measurement using this configuration should not exceed 10 seconds, as this time limit acts as an

additional zero to reduce or eliminate the contributions of noise from frequencies below 0.1 Hz.

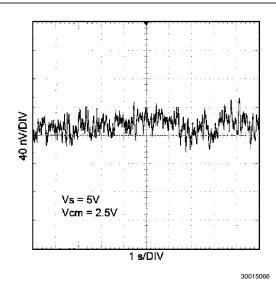

*Figure 3* shows typical peak-to-peak noise for the LMP7732 measured with the circuit in *Figure 2*.

FIGURE 3. 0.1 Hz to 10 Hz Input Voltage Noise

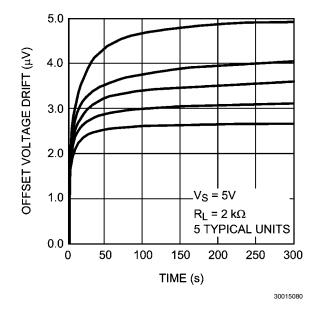

Measuring the very low peak-to-peak noise performance of the LMP7732, requires special testing attention. In order to achieve accurate results, the device should be warmed up for at least five minutes. This is so that the input offset voltage of the op amp settles to a value. During this warm up period, the offset can typically change by a few  $\mu$ V because the chip temperature increases by about 30°C. If the 10 seconds of the measurement is selected to include this warm up time, some of this temperature change might show up as the measured noise. *Figure 4* shows the start-up drift of five typical LMP7732 units.

FIGURE 4. Start-Up Input Offset Voltage Drift

During the peak-to-peak noise measurement, the LMP7732 must be shielded. This prevents offset variations due to airflow. Offset can vary by a few nV due to this airflow and that can invalidate measurements of input voltage noise with a magnitude which is in the same range. For similar reasons, sudden motions must also be restricted in the vicinity of the test area. The feed-through which results from this motion could increase the observed noise value which in turn would invalidate the measurement.

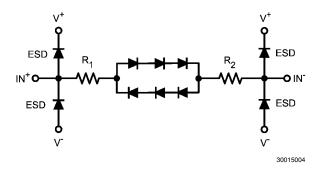

### **DIODES BETWEEN THE INPUTS**

The LMP7732 has a set of anti-parallel diodes between their input pins, as shown in *Figure 5*. These diodes are present to protect the input stage of the amplifiers. At the same time, they limit the amount of differential input voltage that is allowed on the input pins. A differential signal larger than the voltage needed to turn on the diodes might cause damage to the diodes. The differential voltage between the input pins should be limited to  $\pm 3$  diode drops or the input current needs to be limited to  $\pm 20$  mA.

FIGURE 5. Anti-Parallel Diodes between Inputs

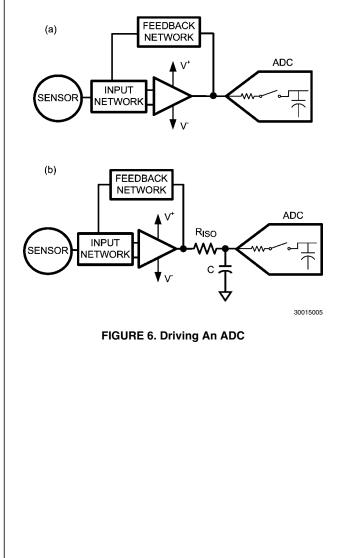

### **DRIVING AN ADC**

LMP7732

Analog to Digital Converters, ADCs, usually have a sampling capacitor on their input. When the ADC's input is directly connected to the output of the amplifier a charging current flows from the amplifier to the ADC. This charging current causes a momentary glitch that can take some time to settle. There are different ways to minimize this effect. One way is to slow down the sampling rate. This method gives the amplifier sufficient time to stabilize its output. Another way to minimize the glitch, caused by the switch capacitor, is to have an external capacitor connected to the input of the ADC. This capacitor is chosen so that its value is much larger than the internal switching capacitor and it will hence provide the charge needed to quickly and smoothly charge the ADC's sampling capacitor. Since this large capacitor will be loading the output of the amplifier as well, an isolation resistor is needed between the output of the amplifier and this capacitor. The isolation resistor, R<sub>ISO</sub>, separates the additional load capacitance from the output of the amplifier and will also form a low-pass filter and can be designed to provide noise reduction as well as anti-aliasing. The draw back of having  $\mathsf{R}_{\mathsf{ISO}}$  is that it reduces signal swing since there is some voltage drop across it.

*Figure 6* (a) shows the ADC directly connected to the amplifier. To minimize the glitch in this setting, a slower sample rate needs to be used. *Figure 6* (b) shows  $R_{ISO}$  and an external capacitor used to minimize the glitch.

LMP7732

# Notes

| Pr                             | oducts                       | Desig                           | n Support                      |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |

| Voltage Reference              | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |

| PowerWise® Solutions           | www.national.com/powerwise   | Solutions                       | www.national.com/solutions     |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |

| Wireless (PLL/VCO)             | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2009 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959

National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com