2.7V to 12V

# **LPV511**

# Micropower, Rail-to-Rail Input and Output Operational Amplifier

# **General Description**

The LPV511 is a micropower operational amplifier that operates from a voltage supply range as wide as 2.7V to 12V with guaranteed specifications at 3V, 5V and 12V. The LPV511 exhibits an excellent speed to power ratio, drawing only 880 nA of supply current with a bandwidth of 27 kHz. These specifications make the LPV511 an ideal choice for battery powered systems that require long life through low supply current, such as instrumentation, sensor conditioning and battery current monitoring.

The LPV511 has an input range that includes both supply rails for ground and high side battery sensing applications. The LPV511 output swings within 100 mV of either rail to maximize the signal's dynamic range in low supply applications. In addition, the output is capable of sourcing 650  $\mu$ A of current when powered by a 12V battery.

The LPV511 is fabricated on National's advanced VIP50C process.

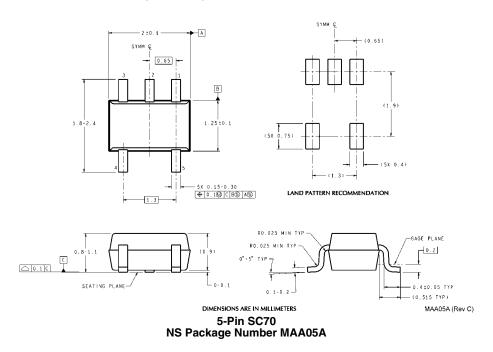

The LPV511 is available in the space saving SC70 package which makes it ideal for portable electronics with area constrained PC boards.

## **Features**

(Typical at 3V supply unless otherwise noted)

Wide supply voltage range

| Slew rate                    | 7.7 V/ms |

|------------------------------|----------|

| Supply current               | 880 nA   |

| Output short circuit current | 1.35 mA  |

■ Rail-to-rail input

Rail-to-rail output 100 mV from rails Bandwidth ( $C_1 = 50$  pF,  $R_1 = 1$  M $\Omega$ ) 27 kHz

Unity gain stable

# **Applications**

- Battery powered systems

- Security systems

- Micropower thermostats

- Solar powered systems

- Portable instrumentation

- Micropower filter

- Remote sensor amplifier

# **Typical Application**

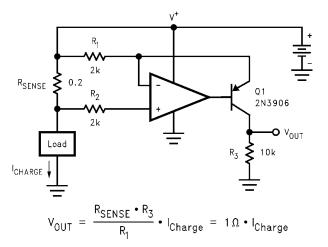

**High Side Battery Current Sensor**

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

ESD Tolerance (Note 2)

Human Body2 KVMachine Model200V $V_{IN}$  Differential2.1VSupply Voltage (V+ - V-)13.2VVoltage at Input/Output pinsV+ +0.3V, V- -0.3VStorage Temperature Range-65°C to +150°CShort Circuit Duration(Note 4)

Junction Temperature (Note 3) +150°C

Soldering Information

Infrared or Convection (20 sec) 235°C

Wave Soldering Lead Temp. (10

260°C

# **Operating Ratings** (Note 1)

Temperature Range (Note 3)  $-40^{\circ}$ C to  $+85^{\circ}$ C Supply Voltage (V<sup>+</sup> – V<sup>-</sup>) 2.7V to 12V

Package Thermal Resistance ( $\theta_{JA}$  (Note 3))

5-Pin SC70 456°C/W

# **3V Electrical Characteristics** (Note 5)

Unless otherwise specified, all limits are guaranteed for  $T_J$  = 25°C, V+ = 3V, V- = 0V,  $V_{CM}$  =  $V_O$  = V+/2, and  $R_L$  = 100 k $\Omega$  to V+/2 . Boldface limits apply to the temperature range of -40°C to 85°C.

| Symbol             | Parameter                              | Conditions                                      | Min<br>(Note 6)       | Typ<br>(Note 7) | Max<br>(Note 6)    | Units |

|--------------------|----------------------------------------|-------------------------------------------------|-----------------------|-----------------|--------------------|-------|

| V <sub>OS</sub>    | Input Offset Voltage                   |                                                 |                       | ±0.2            | ±3<br><b>±3.8</b>  | mV    |

| TC V <sub>os</sub> | Input Offset Voltage Drift             | (Note 8)                                        |                       | ±0.3            | ±15                | μV/°C |

| I <sub>B</sub>     | Input Bias Current (Note 9)            | $V_{CM} = 0.5V$                                 | -1000<br><b>-1600</b> | -320            |                    | 4     |

|                    |                                        | $V_{CM} = 2.5V$                                 |                       | 110             | 800<br><b>1900</b> | pА    |

| I <sub>os</sub>    | Input Offset Current                   |                                                 |                       | ±10             |                    | pА    |

| CMRR               | Common Mode Rejection Ratio            | V <sub>CM</sub> Stepped from 0V to 1.5V         | 77<br><b>70</b>       | 100             |                    |       |

|                    |                                        | V <sub>CM</sub> Stepped from 2.4V to 3V         | 75<br><b>68</b>       | 115             |                    | dB    |

|                    |                                        | V <sub>CM</sub> Stepped from 0.5V to 2.5V       | 60<br><b>56</b>       | 80              |                    |       |

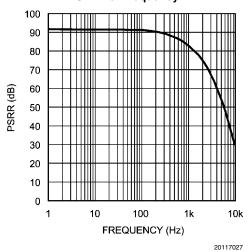

| PSRR               | Power Supply Rejection Ratio           | $V^{+} = 2.7V \text{ to 5V}, V_{CM} = 0.5V$     | 72<br><b>68</b>       | 114             |                    |       |

|                    |                                        | $V^{+} = 3V \text{ to } 5V, V_{CM} = 0.5V$      | 76<br><b>72</b>       | 115             |                    | dB    |

|                    |                                        | $V^{+} = 5V$ to 12V, $V_{CM} = 0.5V$            | 84<br><b>80</b>       | 117             |                    |       |

| CMVR               | Input Common-Mode Voltage<br>Range     | CMRR ≥ 50 dB                                    | -0.1<br><b>0</b>      |                 | 3.1<br><b>3.0</b>  | V     |

| A <sub>VOL</sub>   | Large Signal Voltage Gain              | Sinking, $V_O = 2.5V$<br>Sourcing, $V_O = 0.5V$ | 75<br><b>70</b>       | 105             |                    | dB    |

| V <sub>O</sub>     | Output Swing High                      | V <sub>ID</sub> = 100 mV                        | 2.85<br><b>2.8</b>    | 2.90            |                    | V     |

|                    | Output Swing Low                       | $V_{ID} = -100 \text{ mV}$                      |                       | 100             | 150<br><b>200</b>  | mV    |

| I <sub>sc</sub>    | Output Short Circuit Current (Note 10) | Sourcing<br>V <sub>ID</sub> = 100 mV            |                       | -500            | -225               |       |

|                    |                                        | Sinking<br>V <sub>ID</sub> = -100 mV            | 225                   | 1350            |                    | μA    |

| I <sub>S</sub>     | Supply Current                         |                                                 |                       | 0.88            | 1.2<br><b>1.5</b>  | μA    |

| SR                 | Slew Rate (Note 11)                    | $A_V = +1$ , $V_O$ ramps from 0.5V to 2.5V      | 5.25<br><b>3.10</b>   | 7.7             |                    | V/ms  |

| Symbol         | Parameter                    | Conditions                                     | Min      | Тур      | Max      | Units     |

|----------------|------------------------------|------------------------------------------------|----------|----------|----------|-----------|

|                |                              |                                                | (Note 6) | (Note 7) | (Note 6) |           |

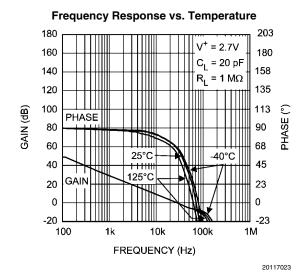

| GBW            | Gain Bandwidth Product       | $R_L = 1 \text{ M}\Omega, C_L = 50 \text{ pF}$ |          | 27       |          | kHz       |

|                | Phase Margin                 | $R_L = 1 \text{ M}\Omega, C_L = 50 \text{ pF}$ |          | 53       |          | deg       |

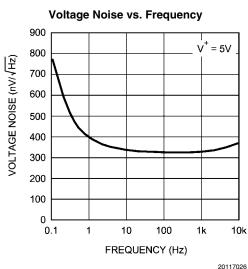

| e <sub>n</sub> | Input-Referred Voltage Noise | f = 100 Hz                                     |          | 320      |          | nV/√Hz    |

| i <sub>n</sub> | Input-Referred Current Noise | f = 10 Hz                                      |          | .02      |          | . 4 / 11= |

|                |                              | f = 1 kHz                                      |          | .01      |          | pA/√Hz    |

# **5V Electrical Characteristics** (Note 5)

Unless otherwise specified, all limits are guaranteed for  $T_J = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ , and  $R_L = 100~k\Omega$  to  $V^+/2$ . Boldface limits apply to the temperature range of  $-40^{\circ}C$  to  $85^{\circ}C$ .

| Symbol             | Parameter                              | Conditions                                        | Min                   | Тур      | Max                | Units  |

|--------------------|----------------------------------------|---------------------------------------------------|-----------------------|----------|--------------------|--------|

|                    |                                        |                                                   | (Note 6)              | (Note 7) | (Note 6)           |        |

| V <sub>os</sub>    | Input Offset Voltage                   |                                                   |                       | ±0.2     | ±3<br><b>±3.8</b>  | mV     |

| TC V <sub>OS</sub> | Input Offset Voltage Drift             | (Note 8)                                          |                       | ±0.3     | ±15                | μV/°C  |

| I <sub>B</sub>     | Input Bias Current (Note 9)            | $V_{CM} = 0.5V$                                   | -1000<br><b>-1600</b> | -320     |                    | nΛ     |

|                    |                                        | V <sub>CM</sub> = 4.5V                            |                       | 110      | 800<br><b>1900</b> | pА     |

| I <sub>os</sub>    | Input Offset Current                   |                                                   |                       | ±10      |                    | pA     |

| CMRR               | Common Mode Rejection Ratio            | V <sub>CM</sub> Stepped from 0V to 2.5V           | 80<br><b>73</b>       | 115      |                    |        |

|                    |                                        | V <sub>CM</sub> Stepped from 4.4 to 5V            | 75<br><b>68</b>       | 107      |                    | dB     |

|                    |                                        | V <sub>CM</sub> Stepped from 0.5 to 4.5V          | 65<br><b>62</b>       | 87       |                    |        |

| PSRR               | Power Supply Rejection Ratio           | $V^{+} = 2.7V$ to 5V, $V_{CM} = 0.5V$             | 72<br><b>68</b>       | 114      |                    |        |

|                    |                                        | $V^{+} = 3V \text{ to } 5V, V_{CM} = 0.5V$        | 76<br><b>72</b>       | 115      |                    | dB     |

|                    |                                        | $V^{+} = 5V$ to 12V, $V_{CM} = 0.5V$              | 84<br><b>80</b>       | 117      |                    |        |

| CMVR               | Input Common-Mode Voltage<br>Range     | CMRR ≥ 50 dB                                      | -0.1<br><b>0</b>      |          | 5.1<br><b>5</b>    | V      |

| A <sub>VOL</sub>   | Large Signal Voltage Gain              | Sinking, V <sub>O</sub> = 4.5V                    | 78                    | 110      |                    | 40     |

|                    |                                        | Sourcing, V <sub>O</sub> = 0.5V                   | 73                    | 110      |                    | dB     |

| V <sub>O</sub>     | Output Swing High                      | V <sub>ID</sub> = 100 mV                          | 4.8<br><b>4.75</b>    | 4.89     |                    | V      |

|                    | Output Swing Low                       | $V_{ID} = -100 \text{ mV}$                        |                       | 110      | 200<br><b>250</b>  | mV     |

| I <sub>sc</sub>    | Output Short Circuit Current (Note 10) | Sourcing to V-<br>V <sub>ID</sub> = 100 mV        |                       | -550     | -225               |        |

|                    |                                        | Sinking to V+ V <sub>ID</sub> = -100 mV           | 225                   | 1350     |                    | μΑ     |

| I <sub>s</sub>     | Supply Current                         |                                                   |                       | 0.97     | 1.2<br><b>1.5</b>  | μΑ     |

| SR                 | Slew Rate (Note 11)                    | $A_V = +1$ , $V_O$ ramps from 0.5V to 4.5V        | 5.25<br><b>3.10</b>   | 7.5      |                    | V/ms   |

| GBW                | Gain Bandwidth Product                 | $R_L = 1 \text{ M}\Omega$ , $C_L = 50 \text{ pF}$ |                       | 27       |                    | kHz    |

|                    | Phase Margin                           | $R_L = 1 \text{ M}\Omega$ , $C_L = 50 \text{ pF}$ |                       | 53       |                    | deg    |

| e <sub>n</sub>     | Input-Referred Voltage Noise           | f = 100 Hz                                        |                       | 320      |                    | nV/√Hz |

3

| Symbol         | Parameter                    | Conditions | Min      | Тур      | Max      | Units           |

|----------------|------------------------------|------------|----------|----------|----------|-----------------|

|                |                              |            | (Note 6) | (Note 7) | (Note 6) |                 |

| i <sub>n</sub> | Input-Referred Current Noise | f = 10 Hz  |          | .02      |          | . A / /II=      |

|                |                              | f = 1 kHz  |          | .01      |          | p <b>A</b> /√Hz |

# 12V Electrical Characteristics (Note 5)

Unless otherwise specified, all limits are guaranteed for  $T_J = 25^{\circ}C$ ,  $V^+ = 12V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ , and  $R_L = 100 \text{ k}\Omega$  to  $V^+/2$ . Boldface limits apply to the temperature range of  $-40^{\circ}C$  to  $85^{\circ}C$ .

| Symbol             | Parameter                              | Conditions                                       | Min<br>(Note 6)        | Typ<br>(Note 7) | Max<br>(Note 6)    | Units  |

|--------------------|----------------------------------------|--------------------------------------------------|------------------------|-----------------|--------------------|--------|

| V <sub>OS</sub>    | Input Offset Voltage                   |                                                  |                        | ±0.2            | ±3<br>±3.8         | mV     |

| TC V <sub>os</sub> | Input Offset Voltage Drift             | (Note 8)                                         |                        | ±0.3            | ±15                | μV/°C  |

| I <sub>B</sub>     | Input Bias Current (Note 9)            | V <sub>CM</sub> = 0.5V                           | -1000<br>- <b>1600</b> | -320            |                    | 4      |

|                    |                                        | V <sub>CM</sub> = 11.5V                          |                        | 110             | 800<br><b>1900</b> | pА     |

| I <sub>OS</sub>    | Input Offset Current                   |                                                  |                        | ±10             |                    | рА     |

| CMRR               | Common Mode Rejection Ratio            | V <sub>CM</sub> Stepped from 0V to +6V           | 75<br><b>70</b>        | 115             |                    |        |

|                    |                                        | V <sub>CM</sub> Stepped from 11.4V to 12V        | 75<br><b>68</b>        | 110             |                    | dB     |

|                    |                                        | V <sub>CM</sub> Stepped from 0.5V to 11.5        | 70<br><b>65</b>        | 97              |                    |        |

| PSRR               | Power Supply Rejection Ratio           | $V^{+} = 2.7V$ to 5V, $V_{CM} = 0.5V$            | 72<br><b>68</b>        | 114             |                    |        |

|                    |                                        | V+ = 3V to 5V, V <sub>CM</sub> = 0.5V            | 76<br><b>72</b>        | 115             |                    | dB     |

|                    |                                        | V+ = 5V to 12V, V <sub>CM</sub> = 0.5V           | 84<br><b>80</b>        | 117             |                    |        |

| CMVR               | Input Common-Mode Voltage<br>Range     | CMRR ≥ 50 dB                                     | -0.1<br><b>0</b>       |                 | 12.1<br><b>12</b>  | V      |

| A <sub>VOL</sub>   | Large Signal Voltage Gain              | Sinking, $V_O = 0.5V$<br>Sourcing, $V_O = 11.5V$ | 89<br><b>84</b>        | 110             |                    | dB     |

| V <sub>O</sub>     | Output Swing High                      | V <sub>ID</sub> = 100 mV                         | 11.8<br><b>11.72</b>   | 11.85           |                    | V      |

|                    | Output Swing Low                       | $V_{ID} = -100 \text{ mV}$                       |                        | 150             | 200<br><b>280</b>  | mV     |

| I <sub>SC</sub>    | Output Short Circuit Current (Note 10) | Sourcing<br>V <sub>ID</sub> = 100 mV             |                        | -650            | -200               | _      |

|                    |                                        | Sinking $V_{ID} = -100 \text{ mV}$               | 200                    | 1300            |                    | μΑ     |

| I <sub>S</sub>     | Supply Current                         |                                                  |                        | 1.2             | 1.75<br><b>2.5</b> | μΑ     |

| SR                 | Slew Rate (Note 11)                    | $A_V = +1$ , $V_O$ ramped from 1V to 11V         | 5.25<br><b>3.10</b>    | 7.0             |                    | V/ms   |

| GBW                | Gain Bandwidth Product                 | $R_L = 1 \text{ M}\Omega, C_L = 50 \text{ pF}$   |                        | 25              |                    | kHz    |

|                    | Phase Margin                           | $R_L = 1 \text{ M}\Omega, C_L = 50 \text{ pF}$   |                        | 52              |                    | deg    |

| e <sub>n</sub>     | Input-Referred Voltage Noise           | f = 100 Hz                                       |                        | 320             |                    | nV/√Hz |

| i <sub>n</sub>     | Input-Referred Current Noise           | Referred Current Noise f = 10 Hz .               |                        | .02             |                    |        |

|                    |                                        | f = 1 kHz                                        |                        | .01             |                    | pA/√Hz |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics Tables.

**Note 2:** Human Body Model:  $1.5 \text{ k}\Omega$  in series with 100 pF. Machine Model:  $0\Omega$  in series with 200 pF.

Note 3: The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ , and  $T_{A}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / \theta_{JA}$ . All numbers apply for packages soldered directly onto a PC board.

Note 4: Output short circuit duration is infinite for V+ < 6V at room temperature and below. For V+ > 6V, allowable short circuit duration is 1.5 ms.

Note 5: Electrical table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device.

Note 6: Limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlations using the Statistical Quality Control (SQC) method.

Note 7: Typical values represent the most likely parametric norm at the time of characterization.

**Note 8:** Offset voltage drift is guaranteed by design and/or characterization and is not tested in production. Offset voltage drift is determined by dividing the change in V<sub>OS</sub> at temperature extremes into the total temperature change.

Note 9: Positive current corresponds to current flowing into the device.

Note 10: The Short Circuit Test is a momentary test. See (Note 4).

Note 11: Slew rate is the average of the rising and falling slew rates.

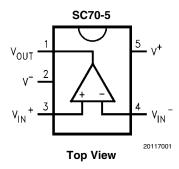

# **Connection Diagram**

# **Ordering Information**

| Package     | Part Number | Package Marking | Transport Media               | NSC Drawing |

|-------------|-------------|-----------------|-------------------------------|-------------|

| 5-Pin SC70  | LPV511MG    | A01             | 1k Units Tape and Reel MA005A |             |

| 5-PIII 5070 | LPV511MGX   | A91             | 3k Units Tape and Reel        | IVIAUUSA    |

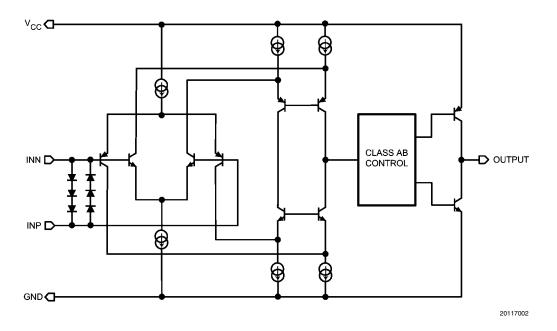

# **Simplified Schematic**

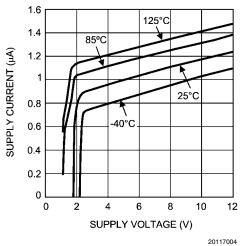

# **Typical Performance Characteristics** At $T_J = 25$ °C, unless otherwise specified.

## Supply Current vs. Supply Voltage

#### Level Office Wellers and Level Occurrent Manda

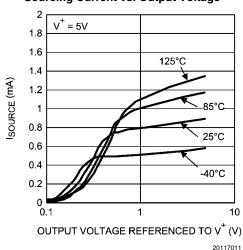

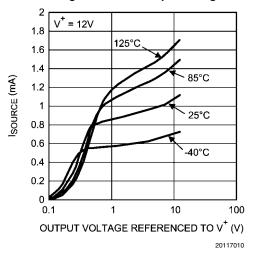

## Sourcing Current vs. Output Voltage

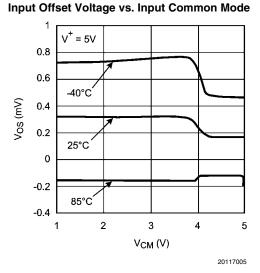

## Input Offset Voltage vs. Input Common Mode

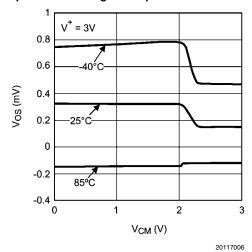

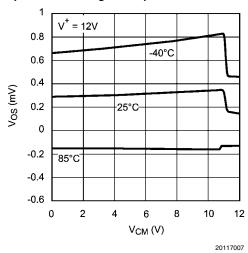

## Input Offset Voltage vs. Input Common Mode

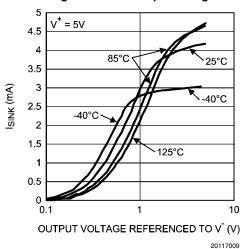

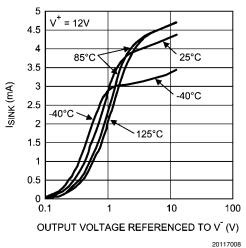

## Sinking Current vs. Output Voltage

## Sourcing Current vs. Output Voltage

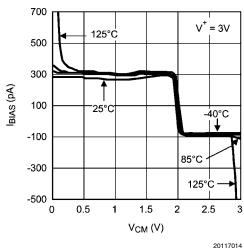

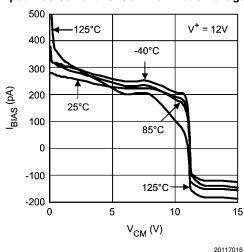

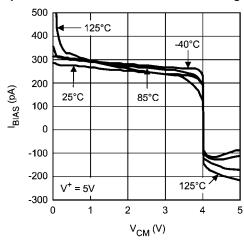

## Input Bias Current vs. Common Mode Voltage

Input Bias Current vs. Common Mode Voltage

## Sinking Current vs. Output Voltage

Input Bias Current vs. Common Mode Voltage

PSRR vs. Frequency

20117015

www.national.com

8

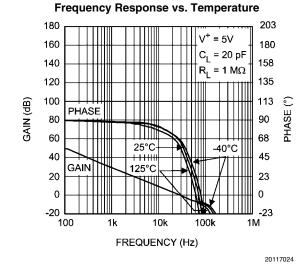

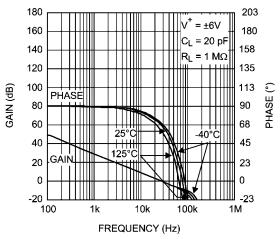

## Frequency Response vs. Temperature

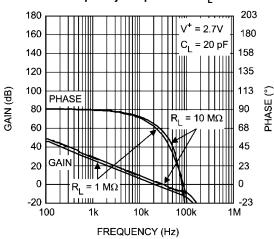

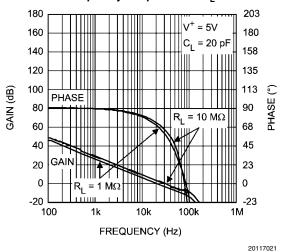

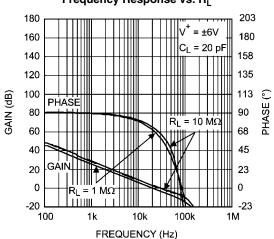

## Frequency Response vs. R<sub>L</sub>

20117022

Frequency Response vs. R<sub>L</sub>

20117019

20117020

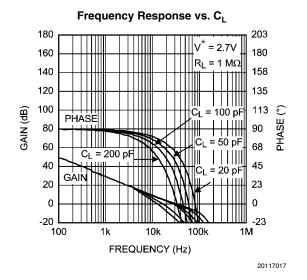

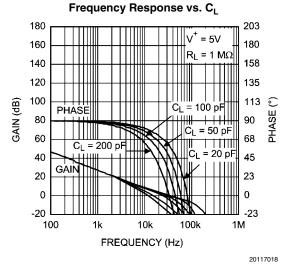

Frequency Response vs. C<sub>L</sub> GAIN (dB) C<sub>L</sub> = 200 pF

1M

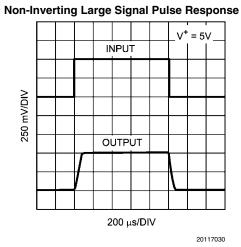

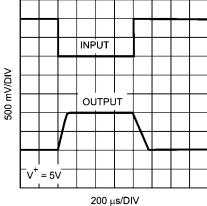

## **Non-Inverting Small Signal Pulse Response**

10k

FREQUENCY (Hz)

100k

-20

1k

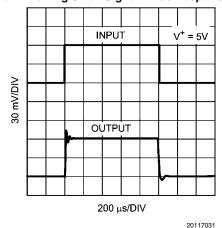

#### **Inverting Small Signal Pulse Response**

#### 20117032

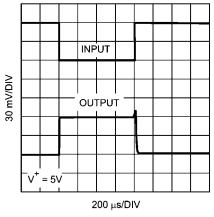

# Inverting Large Signal Pulse Response

20117033

# **Application Notes**

The LPV511 is fabricated with National Semiconductor's state-of-the-art VIP50C process.

#### **INPUT STAGE**

The LPV511 has a rail-to-rail input which provides more flexibility for the system designer. As can be seen from the simplified schematic, rail-to-rail input is achieved by using in parallel, one PNP differential pair and one NPN differential pair. When the common mode input voltage ( $V_{CM}$ ) is near V  $^+$ , the NPN pair is on and the PNP pair is off. When  $V_{CM}$  is near V-, the NPN pair is off and the PNP pair is on. When  $V_{CM}$  is between V+ and V-, internal logic decides how much current each differential pair will get. This special logic ensures stable and low distortion amplifier operation within the entire common mode voltage range.

Because both input stages have their own offset voltage ( $V_{OS}$ ) characteristic, the offset voltage of the LPV511 becomes a function of  $V_{CM}$ .  $V_{OS}$  has a crossover point at 1.0V below V+. Refer to the ' $V_{OS}$  vs.  $V_{CM}$ ' curve in the Typical Performance Characteristics section. Caution should be taken in situations where the input signal amplitude is comparable to the  $V_{OS}$  value and/or the design requires high accuracy. In these situations, it is necessary for the input signal to avoid the crossover point.

The input bias current,  $I_B$  will change in value and polarity as the input crosses the transition region. In addition, parameters such as PSRR and CMRR which involve the input offset voltage will also be affected by changes in  $V_{CM}$  across the differential pair transition region.

Differential input voltage is the difference in voltage between the non-inverting (+) input and the inverting input (–) of the op amp. Due to the three series diodes across the two inputs, the absolute maximum differential input voltage is  $\pm 2.1 \text{V}$ . This may not be a problem to most conventional op amp designs; however, designers should avoid using the LPV511 as a comparator.

#### **OUTPUT STAGE**

The LPV511 output voltage swing 100 mV from rails @ 3V supply, which provides the maximum possible dynamic range at the output. This is particularly important when operating on low supply voltages.

The LPV511 Maximum Output Voltage Swing defines the maximum swing possible under a particular output load. The

LPV511 output swings 110 mV from the rail @ 5V supply with an output load of 100  $k\Omega.$

#### **DRIVING CAPACITIVE LOAD**

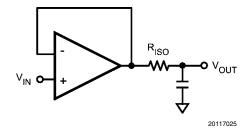

The LPV511 is internally compensated for stable unity gain operation, with a 27 kHz typical gain bandwidth. However, the unity gain follower is the most sensitive configuration to capacitive load. Direct capacitive loading reduces the phase margin of the op amp. When the output is required to drive a large capacitive load, greater than 100 pF, a small series resistor at the output of the amplifier improves the phase margin (see *Figure 1*).

In Figure 1 , the isolation resistor  $R_{\rm ISO}$  and the load capacitor  $C_{\rm L}$  form a pole to increase stability by adding more phase margin to the overall system. The desired performance depends on the value of  $R_{\rm ISO}$ . The bigger the  $R_{\rm ISO}$  resistor value, the more stable  $V_{\rm OUT}$  will be. But the DC accuracy is degraded when the  $R_{\rm ISO}$  gets bigger. If there were a load resistor in Figure 1, the output voltage would be divided by  $R_{\rm ISO}$  and the load resistor.

FIGURE 1. Resistive Isolation of Capacitive Load

#### **POWER SUPPLIES AND LAYOUT**

The LPV511 operates from a single 2.7V to 12V power supply. It is recommended to bypass the power supplies with a 0.1  $\mu$ F ceramic capacitor placed close to the V+ and V- pins. Ground layout improves performance by decreasing the amount of stray capacitance and noise at the op amp's inputs and outputs. To decrease stray capacitance, minimize PC board trace lengths and resistor leads, and place external components close to the op amps's pins.

# **Typical Applications**

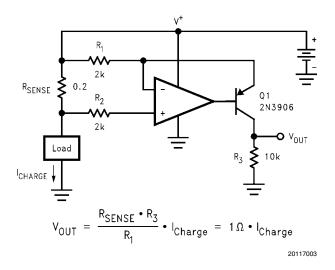

#### **BATTERY CURRENT SENSING**

The rail-to-rail common mode input range and the very low quiescent current make the LPV511 ideal to use in high side and low side battery current sensing applications. The high side current sensing circuit in *Figure 2* is commonly used in a battery charger to monitor the charging current in order to prevent over charging. A sense resistor  $R_{\text{SENSE}}$  is connected to the battery directly.

FIGURE 2. High Side Current Sensing

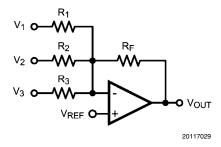

#### **SUMMING AMPLIFIER**

The LPV511 operational amplifier is a perfect fit in a summing amplifier circuit because of the rail-to-rail input and output and the sub-micro Amp quiescent current. In this configuration, the amplifier outputs the sum of the three input voltages.

The ratio of the sum and the output voltage is defined using feedback and input resistors.

$$V_{OUT} = R_F \left( \frac{V_{REF} - V_1}{R_1} + \frac{V_{REF} - V_2}{R_2} + \frac{V_{REF} - V_3}{R_3} \right) + V_{REF}$$

FIGURE 3. Summing Amplifier Circuit

# Physical Dimensions inches (millimeters) unless otherwise noted

# **Notes**

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email:

Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530-85-86 Em: il-europe.support@nsc.com

Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560