# Low Cost, General-Purpose High Speed JFET Amplifier

**AD825**

#### **FEATURES**

**High speed**

41 MHz, -3 dB bandwidth

125 V/µs slew rate

80 ns settling time

Input bias current of 20 pA and noise current of 10 fA/√Hz

Input voltage noise of 12 nV/√Hz

Fully specified power supplies: ±5 V to ±15 V

Low distortion: -76 dB at 1 MHz

High output drive capability

**Drives unlimited capacitance load**

50 mA min output current

No phase reversal when input is at rail

**Available in 8-lead SOIC**

#### **APPLICATIONS**

**CCDs**

Low distortion filters

Mixed gain stages

Audio amplifiers

Photo detector interfaces

ADC input buffers

DAC output buffers

## **GENERAL DESCRIPTION**

The AD825 is a superbly optimized operational amplifier for high speed, low cost, and dc parameters, making it ideally suited for a broad range of signal conditioning and data acquisition applications. The ac performance, gain, bandwidth, slew rate, and drive capability are all very stable over temperature. The AD825 also maintains stable gain under varying load conditions.

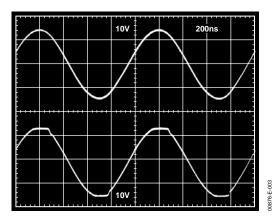

The unique input stage has ultralow input bias current and input current noise. Signals that go to either rail on this high performance input do not cause phase reversals at the output. These features make the AD825 a good choice as a buffer for MUX outputs, creating minimal offset and gain errors.

The AD825 is fully specified for operation with dual  $\pm 5$  V and  $\pm 15$  V supplies. This power supply flexibility, and the low supply current of 6.5 mA with excellent ac characteristics under all supply conditions, makes the AD825 well-suited for many demanding applications.

#### Rev. F

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

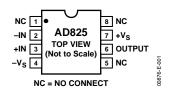

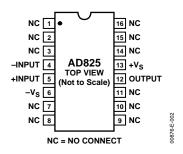

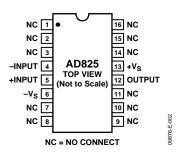

#### CONNECTION DIAGRAMS

Figure 1. 8-Lead Plastic SOIC (R) Package

Figure 2. 16-Lead Plastic SOIC (R-16) Package

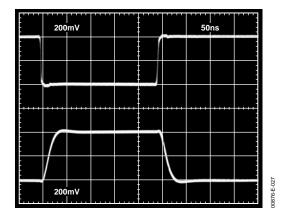

Figure 3. Performance with Rail-to-Rail Input Signals

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

# **AD825**

# **TABLE OF CONTENTS**

| Specifications                      | 3  |

|-------------------------------------|----|

| Absolute Maximum Ratings            | 5  |

| Pin Configurations                  | 5  |

| ESD Caution                         | 5  |

| Typical Performance Characteristics | 6  |

| Driving Capacitive Loads            | 10 |

| Theory of Operation                 | 10 |

| Input Consideration                 | 10 |

| Grounding and Bypassing             | 10 |

| Second-Order Low-Pass Filter        | 11 |

| Outline Dimensions                  | 12 |

| Ordering Guide                      | 12 |

## **REVISION HISTORY**

| 10/04—Data Sheet Changed from Rev. E to Rev. F |    |

|------------------------------------------------|----|

| Changes to Figure 1                            | 1  |

| Changes to Figure 4                            | 5  |

| Changes to Figure 21                           |    |

| 3/04—Data Sheet Changed from Rev. D to Rev. E  |    |

| Changes to Specifications                      | 3  |

| Addition of 16-Lead SOIC Pin Configuration     | 5  |

| Changes to Figure 27                           | 9  |

| Updated Outline Dimensions                     |    |

| Updated Ordering Guide                         |    |

| 2/01—Data Sheet Changed from Rev. C to Rev. D  |    |

| Addition of 16-lead SOIC package (R-16)        |    |

| Connection Diagram                             | 4  |

| Addition to Absolute Maximum Ratings           |    |

| Addition to Ordering Guide (R-16)              |    |

| Addition of 16-lead SOIC package (R-16)        |    |

| Outline Dimensions                             | 11 |

# **SPECIFICATIONS**

All limits are determined to be at least four standard deviations away from mean value. At  $T_A = 25$ °C,  $V_S = \pm 15$  V, unless otherwise noted. Table 1.

|                                 |                                                         |            | AD825A |                    |     |                    |

|---------------------------------|---------------------------------------------------------|------------|--------|--------------------|-----|--------------------|

| Parameter                       | Conditions                                              | <b>V</b> s | Min    | Тур                | Max | Unit               |

| DYNAMIC PERFORMANCE             |                                                         |            |        |                    |     |                    |

| Unity Gain Bandwidth            |                                                         | ±15 V      | 23     | 26                 |     | MHz                |

| Bandwidth for 0.1 dB Flatness   | Gain = +1                                               | ±15 V      | 18     | 21                 |     | MHz                |

| –3 dB Bandwidth                 | Gain = +1                                               | ±15 V      | 44     | 46                 |     | MHz                |

| Slew Rate                       | $R_{LOAD} = 1 \text{ k}\Omega, G = +1$                  | ±15 V      | 125    | 140                |     | V/µs               |

| Settling Time to 0.1%           | 0 V to 10 V Step, $A_V = -1$                            | ±15 V      |        | 150                | 180 | ns                 |

| to 0.1%                         | 0 V to 10 V Step, $A_V = -1$                            | ±15 V      |        | 180                | 220 | ns                 |

| Total Harmonic Distortion       | $F_C = 1 \text{ MHz, } G = -1$                          | ±15 V      |        | -77                |     | dB                 |

| Differential Gain Error         | NTSC                                                    | ±15 V      |        | 1.3                |     | %                  |

| $(R_{LOAD} = 150 \Omega)$       | Gain = +2                                               |            |        |                    |     |                    |

| Differential Phase Error        | NTSC                                                    | ±15 V      |        | 2.1                |     | Degrees            |

| $(R_{LOAD} = 150 \Omega)$       | Gain = +2                                               |            |        |                    |     |                    |

| INPUT OFFSET VOLTAGE            |                                                         | ±15 V      |        | 1                  | 2   | mV                 |

|                                 | T <sub>MIN</sub> to T <sub>MAX</sub>                    |            |        |                    | 5   | mV                 |

| Offset Drift                    |                                                         |            |        | 10                 |     | μV/°C              |

| INPUT BIAS CURRENT              |                                                         | ±15 V      |        | 15                 | 40  | рA                 |

|                                 | T <sub>MIN</sub>                                        |            | 5      |                    |     | pA                 |

|                                 | T <sub>MAX</sub>                                        |            |        |                    | 700 | pA                 |

| INPUT OFFSET CURRENT            |                                                         | ±15 V      |        | 20                 | 30  | рA                 |

|                                 | T <sub>MIN</sub>                                        |            | 5      |                    |     | pA                 |

|                                 | T <sub>MAX</sub>                                        |            |        |                    | 440 | pA                 |

| OPEN-LOOP GAIN                  | $V_{OUT} = \pm 10 \text{ V}$                            | ±15 V      |        |                    |     |                    |

|                                 | $R_{LOAD} = 1 k\Omega$                                  |            | 70     | 76                 |     | dB                 |

|                                 | $V_{OUT} = \pm 7.5 \text{ V}$                           | ±15 V      |        |                    |     |                    |

|                                 | $R_{LOAD} = 1 k\Omega$                                  |            | 70     | 76                 |     | dB                 |

|                                 | $V_{OUT} = \pm 7.5 \text{ V}$                           | ±15 V      |        |                    |     |                    |

|                                 | $R_{LOAD} = 150 \text{ k}\Omega \text{ (50 mA Output)}$ |            | 68     | 74                 |     | dB                 |

| COMMON-MODE REJECTION           | $V_{CM} = \pm 10$                                       | ±15 V      | 71     | 80                 |     | dB                 |

| INPUT VOLTAGE NOISE             | f = 10 kHz                                              | ±15 V      |        | 12                 |     | nV/√ <del>Hz</del> |

| INPUT CURRENT NOISE             | f = 10 kHz                                              | ±15 V      |        | 10                 |     | fA/√Hz             |

| INPUT COMMON-MODE VOLTAGE RANGE |                                                         | ±15 V      |        | ±13.5              |     | V                  |

| OUTPUT VOLTAGE SWING            | $R_{LOAD} = 1 k\Omega$                                  | ±15 V      | 13     | ±13.3              |     | V                  |

|                                 | $R_{LOAD} = 500 \Omega$                                 | ±15 V      | 12.9   | ±13.2              |     | V                  |

| Output Current                  |                                                         | ±15 V      | 50     |                    |     | mA                 |

| Short-Circuit Current           |                                                         | ±15 V      |        | 100                |     | mA                 |

| INPUT RESISTANCE                |                                                         | -          |        | 5×10 <sup>11</sup> |     | Ω                  |

| INPUT CAPACITANCE               |                                                         |            |        | 6                  |     | pF                 |

| OUTPUT RESISTANCE               | Open Loop                                               |            |        | 8                  |     | Ω                  |

| POWER SUPPLY                    |                                                         |            |        | =                  |     |                    |

| Quiescent Current               |                                                         | ±15 V      |        | 6.5                | 7.2 | mA                 |

|                                 | T <sub>MIN</sub> to T <sub>MAX</sub>                    | ±15 V      |        |                    | 7.5 | mA                 |

# **AD825**

All limits are determined to be at least four standard deviations away from mean value. At  $T_A = 25$ °C,  $V_S = \pm 5$  V unless otherwise noted. **Table 2.**

|                                 |                                              | AD825A     |      |                    | T   |                    |

|---------------------------------|----------------------------------------------|------------|------|--------------------|-----|--------------------|

| Parameter                       | Conditions                                   | <b>V</b> s | Min  | Тур                | Max | Unit               |

| DYNAMIC PERFORMANCE             |                                              |            |      |                    |     |                    |

| Unity Gain Bandwidth            |                                              | ±5 V       | 18   | 21                 |     | MHz                |

| Bandwidth for 0.1 dB Flatness   | Gain = +1                                    | ±5 V       | 8    | 10                 |     | MHz                |

| −3 dB Bandwidth                 | Gain = +1                                    | ±5 V       | 34   | 37                 |     | MHz                |

| Slew Rate                       | $R_{LOAD} = 1 \text{ k}\Omega, G = -1$       | ±5 V       | 115  | 130                |     | V/µs               |

| Settling Time to 0.1%           | −2.5 V to +2.5 V                             | ±5 V       |      | 75                 | 90  | ns                 |

| to 0.01%                        | −2.5 V to +2.5 V                             | ±5 V       |      | 90                 | 110 | ns                 |

| Total Harmonic Distortion       | $F_{C} = 1 \text{ MHz, } G = -1$             | ±5 V       |      | -76                |     | dB                 |

| Differential Gain Error         | NTSC                                         | ±5 V       |      | 1.2                |     | %                  |

| $(R_{LOAD} = 150 \Omega)$       | Gain = +2                                    |            |      |                    |     |                    |

| Differential Phase Error        | NTSC                                         | ±5 V       |      | 1.4                |     | Degrees            |

| $(R_{LOAD} = 150 \Omega)$       | Gain = +2                                    |            |      |                    |     |                    |

| INPUT OFFSET VOLTAGE            |                                              | ±5 V       |      | 1                  | 2   | mV                 |

|                                 | T <sub>MIN</sub> to T <sub>MAX</sub>         |            |      |                    | 5   | mV                 |

| Offset Drift                    |                                              |            |      | 10                 |     | μV/°C              |

| INPUT BIAS CURRENT              |                                              | ±5 V       |      | 10                 | 30  | рА                 |

|                                 | T <sub>MIN</sub>                             |            | 5    |                    |     | рА                 |

|                                 | T <sub>MAX</sub>                             |            |      |                    | 600 | рА                 |

| INPUT OFFSET CURRENT            |                                              | ±5 V       |      | 15                 | 25  | рА                 |

|                                 | T <sub>MIN</sub>                             |            | 5    |                    |     | рА                 |

| Offset Current Drift            | T <sub>MAX</sub>                             |            |      |                    | 280 | рА                 |

| OPEN-LOOP GAIN                  | V <sub>OUT</sub> = ±2.5                      | ±5 V       |      |                    |     |                    |

|                                 | $R_{LOAD} = 500 \Omega$                      |            | 64   | 66                 |     | dB                 |

|                                 | $R_{LOAD} = 150 \Omega$                      |            | 64   | 66                 |     | dB                 |

| COMMON-MODE REJECTION           | $V_{CM} = \pm 2 V$                           | ±5 V       | 69   | 80                 |     | dB                 |

| INPUT VOLTAGE NOISE             | f = 10 kHz                                   | ±5 V       |      | 12                 |     | nV/√ <del>Hz</del> |

| INPUT CURRENT NOISE             | f = 10 kHz                                   | ±5 V       |      | 10                 |     | fA/√Hz             |

| INPUT COMMON-MODE VOLTAGE RANGE |                                              | ±5 V       |      | ± 3.5              |     | V                  |

| OUTPUT VOLTAGE SWING            | $R_{LOAD} = 500 \Omega$                      |            | +3.2 | ±3.4               |     | V                  |

|                                 | $R_{LOAD} = 150 \Omega$                      | ±5 V       | +3.1 | ±3.2               |     | V                  |

| Output Current                  |                                              | ±5 V       | 50   |                    |     | mA                 |

| Short-Circuit Current           |                                              |            |      | 80                 |     | mA                 |

| INPUT RESISTANCE                |                                              |            |      | 5×10 <sup>11</sup> |     | Ω                  |

| INPUT CAPACITANCE               |                                              |            |      | 6                  |     | pF                 |

| OUTPUT RESISTANCE               | Open Loop                                    |            |      | 8                  |     | Ω                  |

| POWER SUPPLY                    |                                              |            |      |                    |     |                    |

| Ouiescent Current               |                                              | ±5 V       |      | 6.2                | 6.8 | mA                 |

|                                 | T <sub>MIN</sub> to T <sub>MAX</sub>         | ±5 V       |      | <b></b>            | 7.5 | mA                 |

| POWER SUPPLY REJECTION          | $V_S = \pm 5 \text{ V to } \pm 15 \text{ V}$ |            | 76   | 88                 |     | dB                 |

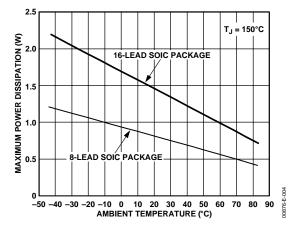

# **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                                    | Rating          |

|----------------------------------------------|-----------------|

| Supply Voltage                               | ±18 V           |

| Internal Power Dissipation <sup>1</sup>      |                 |

| Small Outline (R)                            | See Figure 6    |

| Input Voltage (Common Mode)                  | ±V <sub>S</sub> |

| Differential Input Voltage                   | ±V <sub>S</sub> |

| Output Short-Circuit Duration                | See Figure 6    |

| Storage Temperature Range (R, R-16)          | −65°C to +125°C |

| Operating Temperature Range                  | -40°C to +85°C  |

| Lead Temperature Range<br>(Soldering 10 sec) | 300°C           |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

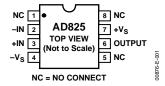

# PIN CONFIGURATIONS

Figure 4. 8-Lead SOIC

Figure 5. 16-Lead SOIC

Figure 6. Maximum Power Dissipation vs. Temperature

## **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>1</sup> Specification is for device in free air: 8-lead SOIC package:  $\theta_{JA}$  = 155°C/W 16-lead SOIC package:  $\theta_{JA}$  = 85°C/W

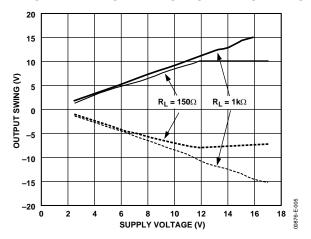

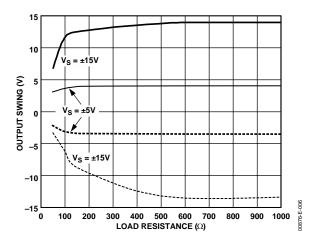

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 7. Output Voltage Swing vs. Supply Voltage

Figure 8. Output Voltage Swing vs. Load Resistance

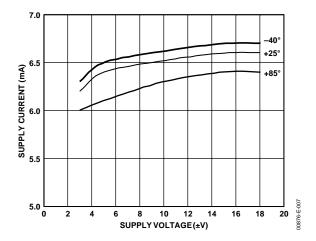

Figure 9. Quiescent Supply Current vs. Supply Voltage for Various Temperatures

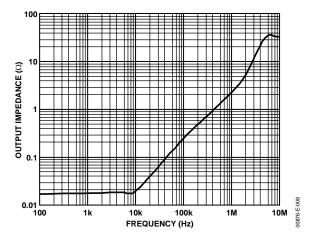

Figure 10. Closed-Loop Output Impedance vs. Frequency

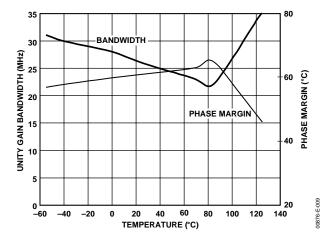

Figure 11. Unity Gain Bandwidth and Phase Margin vs. Temperature

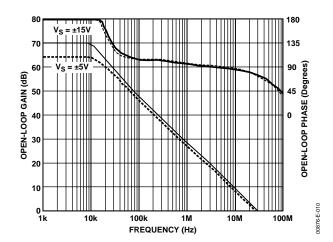

Figure 12. Open-Loop Gain and Phase Margin vs. Frequency

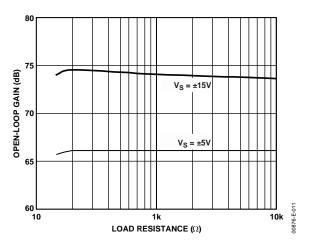

Figure 13. Open-Loop Gain vs. Load Resistance

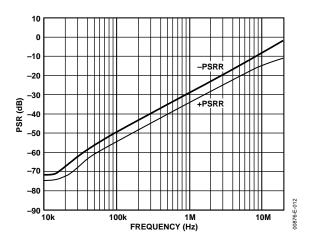

Figure 14. Power Supply Rejection vs. Frequency

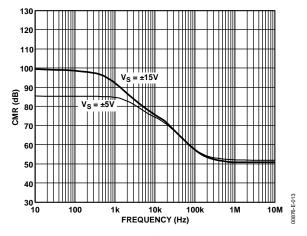

Figure 15. Common-Mode Rejection vs. Frequency

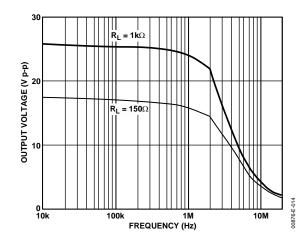

Figure 16. Large Signal Frequency Response; G = +2

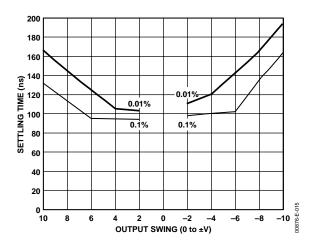

Figure 17. Output Swing and Error vs. Settling Time

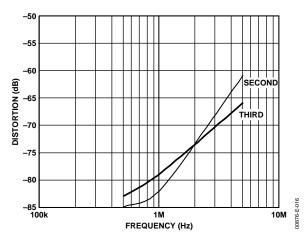

Figure 18. Harmonic Distortion vs. Frequency

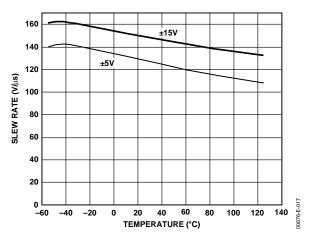

Figure 19. Slew Rate vs. Temperature

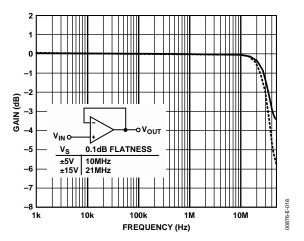

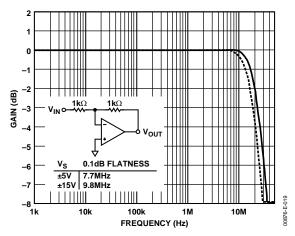

Figure 20. Closed-Loop Gain vs. Frequency, Gain = +1

Figure 21. Closed-Loop Gain vs. Frequency, Gain = -1

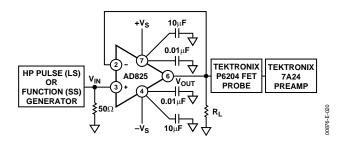

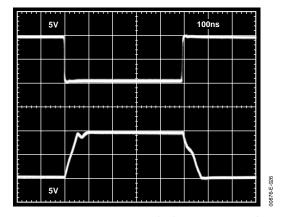

Figure 22. Noninverting Amplifier Connection

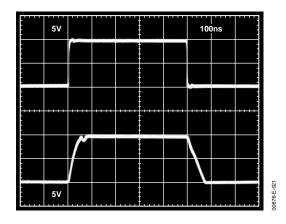

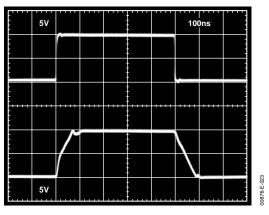

Figure 23. Noninverting Large Signal Pulse Response,  $R_L = 1 \text{ k}\Omega$

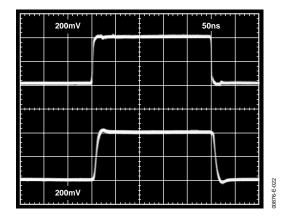

Figure 24. Noninverting Small Signal Pulse Response,  $R_L = 1 \ k\Omega$

Figure 25. Noninverting Large Signal Pulse Response,  $R_L = 150 \, \Omega$

Figure 26. Noninverting Small Signal Pulse Response,  $R_{L}$  = 150  $\Omega$

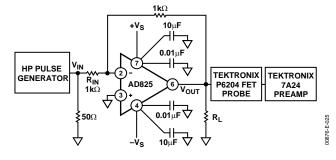

Figure 27. Inverting Amplifier Connection

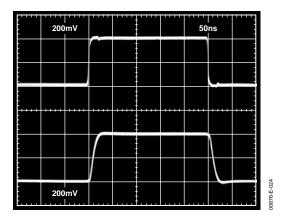

Figure 28. Inverting Large Signal Pulse Response,  $R_L = 1 \ k\Omega$

Figure 29. Inverting Small Signal Pulse Response,  $R_L = 1 \text{ k}\Omega$

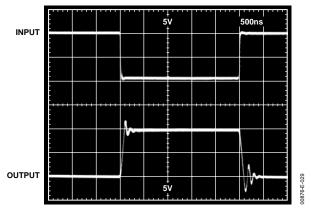

# DRIVING CAPACITIVE LOADS

The internal compensation of the AD825, together with its high output current drive, permits excellent large signal performance while driving extremely high capacitive loads.

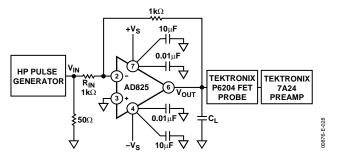

Figure 30. Inverting Amplifier Driving a Capacitive Load

Figure 31. Inverting Amplifier Pulse Response While Driving a 400 pF Capacitive Load

# THEORY OF OPERATION

The AD825 is a low cost, wideband, high performance FET input operational amplifier. With its unique input stage design, the AD825 ensures no phase reversal, even for inputs that exceed the power supply voltages, and its output stage is designed to drive heavy capacitive or resistive loads with small changes relative to no load conditions.

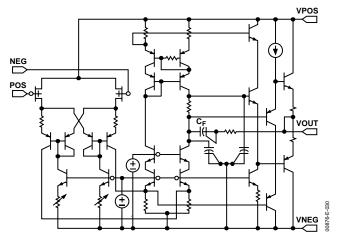

The AD825 (Figure 32) consists of common-drain, common-base FET input stage driving a cascoded, common-base matched NPN gain stage. The output buffer stage uses emitter followers in a Class AB amplifier that can deliver large current to the load while maintaining low levels of distortion.

Figure 32. Simplified Schematic

The capacitor,  $C_F$ , in the output stage, enables the AD825 to drive heavy capacitive loads. For light loads, the gain of the output buffer is close to unity,  $C_F$  is bootstrapped, and not much happens. As the capacitive load is increased, the gain of the output buffer is decreased and the bandwidth of the amplifier is reduced through a portion of  $C_F$  adding to the dominant pole. As the capacitive load is further increased, the amplifier's bandwidth continues to drop, maintaining the stability of the AD825.

### INPUT CONSIDERATION

The AD825 with its unique input stage ensures no phase reversal for signals as large as or even larger than the supply voltages. Also, layout considerations of the input transistors ensure functionality even with a large differential signal.

The need for a low noise input stage calls for a larger FET transistor. One should consider the additional capacitance that is added to ensure stability. When filters are designed with the AD825, one needs to consider the input capacitance (5 pF to 6 pF) of the AD825 as part of the passive network.

#### **GROUNDING AND BYPASSING**

The AD825 is a low input bias current FET amplifier. Its high frequency response makes it useful in applications, such as photodiode interfaces, filters, and audio circuits. When designing high frequency circuits, some special precautions are in order. Circuits must be built with short interconnects, and resistances should have low inductive paths to ground. Power supply leads should be bypassed to common as close as possible to the amplifier pins. Ceramic capacitors of 0.1  $\mu F$  are recommended.

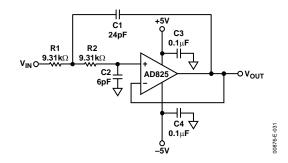

## **SECOND-ORDER LOW-PASS FILTER**

A second-order Butterworth low-pass filter can be implemented using the AD825 as shown in Figure 33. The extremely low bias currents of the AD825 allow the use of large resistor values and, consequently, small capacitor values without concern for developing large offset errors. Low current noise is another factor in permitting the use of large resistors without having to worry about the resultant voltage noise.

With the values shown, the corner frequency will be 1 MHz. The equations for component selection are shown below. Note that the noninverting input (and the inverting input) has an input capacitance of 6 pF. As a result, the calculated value of C1 (12 pF) is reduced to 6 pF.

$$C1 = \frac{1.414}{2\pi f_{CUTOFF}R1}$$

$$C2 \left( farads \right) = \frac{0.707}{2\pi f_{CUTOFF} R1}$$

$R1 = R2 = User Selected (Typically 10 k\Omega to 100 k\Omega)$

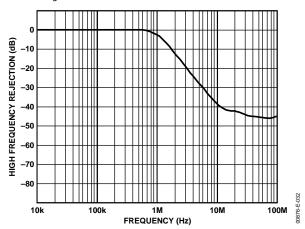

A plot of the filter frequency response is shown in Figure 34; better than 40 dB of high frequency rejection is provided.

Figure 33. Second-Order Butterworth Low-Pass Filter

Figure 34. Frequency Response of Second-Order Butterworth Filter

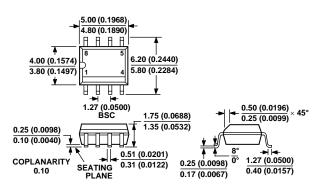

# **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MS-012AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

Figure 35. 8-Lead Standard Small Outline Package [SOIC] Narrow Body (R-8) Dimensions shown in millimeters (inches)

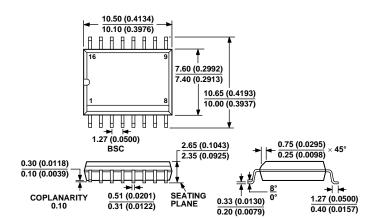

COMPLIANT TO JEDEC STANDARDS MS-013AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

Figure 36. 16-Lead Standard Small Outline Package [SOIC] Wide Body (R-16) Dimensions shown in millimeters (inches)

## **ORDERING GUIDE**

| Model                          | Temperature Range | Package Description             | Package Option |

|--------------------------------|-------------------|---------------------------------|----------------|

| AD825AR                        | -40°C to +85°C    | 8-Lead SOIC                     | R-8            |

| AD825AR-REEL                   | −40°C to +85°C    | 8-Lead SOIC, 13" Tape and Reel  | R-8            |

| AD825AR-REEL7                  | −40°C to +85°C    | 8-Lead SOIC, 7" Tape and Reel   | R-8            |

| AD825AR-16                     | −40°C to +85°C    | 16-Lead SOIC                    | R-16           |

| AD825AR-16-REEL                | -40°C to +85°C    | 16-Lead SOIC, 13" Tape and Reel | R-16           |

| AD825AR-16-REEL7               | -40°C to +85°C    | 16-Lead SOIC, 7" Tape and Reel  | R-16           |

| AD825ARZ-16 <sup>1</sup>       | −40°C to +85°C    | 16-Lead SOIC                    | R-16           |

| AD825ARZ-16-REEL <sup>1</sup>  | −40°C to +85°C    | 16-Lead SOIC, 13" Tape and Reel | R-16           |

| AD825ARZ-16-REEL7 <sup>1</sup> | −40°C to +85°C    | 16-Lead SOIC, 7" Tape and Reel  | R-16           |

| AD825ACHIPS                    |                   | Die                             |                |

<sup>&</sup>lt;sup>1</sup> Z = Pb-free part.

www.analog.com