# dsPIC30F FAMILY REFERENCE MANUAL

### dsPIC30F Family Reference Manual Errata Sheet

The dsPIC30F Family Reference Manual (DS70046B) correctly describes the function of the dsPIC30F devices, except for the anomalies described below.

All of the issues listed will be addressed in future releases of the Family Reference Manual.

### **Errata Summary**

The following list summarizes the errata described in further detail through the remainder of this document:

- Typographical errors in several register descriptions, bit descriptions, and source code examples have been corrected.

- The conditions leading to a Stack Error Trap have been clarified.

- Restrictions on the instructions that can be used at or near the end of a DO loop have been clarified.

- 4. The timing for Program Space Visibility (PSV) operations has been clarified and the effect of instruction stalls on PSV has been corrected.

- The function of the NVMADRU register has been documented.

- Run-Time Self Programming (RTSP) can be used to program 32 instruction locations at one time, not 4 instructions as the current documentation indicates

- Causes of Address Error Traps have been clarified.

- 8. Control bits for tuning the 8 MHz RC oscillator have been documented.

- 9. Clock switching operation has been clarified.

- 10. Differences in QEI DFLTCON register among device variants has been documented.

- The 10-bit A/D sampling requirements have been changed.

- 12. The 12-bit A/D sampling requirements have been changed.

- Wake-up operation from Sleep and Idle modes has been clarified.

### 1. Page 2-2, Section 2.1 Introduction

On page 2-2, Section 2.1 Introduction, paragraph 5 should be replaced with the following:

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space. Furthermore, RAM may be connected to the program memory bus **on devices with an external bus** and used to extend the internal data RAM.

### 2. Page 2-10, Section 2.3.3 Stack Pointer Overflow

On page 2-10, Section 2.3.3 Stack Pointer Overflow, the last sentence in paragraph 2 should be replaced by the following:

If the contents of the Stack Pointer (W15) are greater than the contents of the SPLIM register by 2 and a push operation is performed, a Stack Error Trap will not occur. The Stack Error Trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a Stack Error Trap when the stack grows beyond address  $0 \times 2000$  in RAM, initialize the SPLIM with the value,  $0 \times 1$  FFE.

Note:

A Stack Error Trap may be caused by any instruction that uses the contents of the W15 register to generate an effective address (EA). Thus, if the contents of W15 are greater than the contents of the SPLIM register by 2, and a CALL instruction is executed, or if an interrupt occurs, a Stack Error Trap will be generated.

## 3. Page 2-34, Section 2.9.2.5 DO Loop Restrictions

On page 2-34, Section 2.9.2.5 DO Loop Restrictions, the following paragraph and bullets should be added to the end of this section:

The instruction that is executed two instructions before the last instruction in a DO loop should not modify any of the following:

- •CPU priority level governed by the IPL (SR<7:5>) bits

- •Peripheral Interrupt Enable bits governed by the IEC0, IEC1 and IEC2 registers

- Peripheral Interrupt Priority bits governed by the IPC0 through IPC11 registers

If the restrictions above are not followed, the DO loop may execute incorrectly.

## 4. Page 2-34, Section 2.9.2.5.1 Last Instruction Restrictions

On page 2-34, Section 2.9.2.5.1 Last Instruction Restrictions, the following bullet should be added to the end of the bulleted list:

6. DISI instruction

# 5. Page 2-37, Section 2.10.2.4 Instruction Stalls and Program Space Visibility

On page 2-37, Section 2.10.2.4 Instruction Stalls and Program Space Visibility should be replaced with the following:

### 2.10.2.4 Instruction Stalls and Program Space Visibility (PSV)

When program space (PS) is mapped to data space by enabling the PSV (CORCON<2>) bit, and the X space EA falls within the visible program space window, the read or write cycle is redirected to the address in program space. Accessing data from program space takes up to 3 instruction cycles.

Instructions operating in PSV address space are subject to RAW data dependencies and consequent instruction stalls, just like any other instruction.

Consider the following code segment:

```

ADD W0, [W1], [W2++]; PSV = 1, W1=0x8000, PSVPAG=0xAA MOV [W2], [W3]

```

This sequence of instructions would take 5 instruction cycles to execute. 2 instruction cycles are added to perform the PSV access via W1. Furthermore, an instruction stall cycle is inserted to resolve the RAW data dependency caused by W2.

# 6. Page 2-39, Table 2-8 dsPIC30F Core Register Map (Continued)

On page 2-39, Table 2-8 dsPIC30F Core Register Map (Continued), in the first row of the table, correct bits names for bit 8 through bit 12 in the CORCON register as follows:

TABLE 1: CORCON BIT NAMES

| Bit Location in CORCON | Bit Name<br>(Incorrect) | Bit Name<br>(Please read as) |  |  |

|------------------------|-------------------------|------------------------------|--|--|

| 12                     | -                       | US                           |  |  |

| 11                     | US                      | EDT                          |  |  |

| 10                     | EDT                     | DL2                          |  |  |

### 7. Page 3-19, Register 3-1: MODCON: Modulo and Bit-Reversed Addressing Control Register, bit 7-4

On page 3-19, Register 3-1: MODCON: Modulo and Bit-Reversed Addressing Control Register, the description for bit4 through bit7 should be modified as follows. All other bit definitions do not change and hence are not described:

Register 3-1: MODCON: Modulo and Bit-Reversed Addressing Control Register

| Upper Byte: |        |     |     |       |       |        |       |  |

|-------------|--------|-----|-----|-------|-------|--------|-------|--|

| R/W-0       | R/W-0  | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 |  |

| XMODEN      | YMODEN | _   | _   |       | BWM   | l<3:0> |       |  |

| bit 15      |        |     |     |       |       |        | bit 8 |  |

| Lower Byte | :     |        |       |       |       |        |       |

|------------|-------|--------|-------|-------|-------|--------|-------|

| R/W-0      | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 |

|            | YWN   | 1<3:0> |       |       | XWM   | 1<3:0> |       |

| bit 7      |       |        |       | ,     |       |        | bit 0 |

bit 7-4 YWM<3:0>: Y AGU W Register Select for Modulo Addressing bits

1111 = Modulo addressing disabled

1110 = W14 selected for modulo addressing

1101 = W13 selected for **modulo** addressing

0000 = W0 selected for modulo addressing

Note:

A write to the MODCON register should not be followed by an instruction that performs an indirect read operation using a W register. Unexpected results may occur. Some instructions perform an implicit indirect read. These are: POP, RETURN, RETFIE, RETLW and ULNK.

| Legend:           |                  |                      |                    |  |

|-------------------|------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |  |

| -n - Value at POR | '1' - Rit is set | '0' - Bit is cleared | y – Rit is unknown |  |

### 8. Page 4-10, Section 4.4.3 PSV Timing

On page 4-10, Section 4.4.3 PSV Timing should be replaced with the following:

### 4.4.3 PSV Timing

Instructions that use PSV will require two extra instruction cycles to complete execution, except the following instructions that require only one extra cycle to complete execution:

- -The MAC class of instructions with data pre-fetch operands

- -All MOV instructions including the MOV. D instruction

The additional instruction cycles are used to fetch the PSV data on the program memory bus.

### 4.4.3.1 Using PSV in a REPEAT Loop

Instructions that use PSV within a REPEAT loop eliminate the extra instruction cycle(s) required for the data access from program memory, hence incurring no overhead in execution time. However, the following iterations of the REPEAT loop will incur an overhead of two instruction cycles to complete execution:

- -The first iteration

- -The last iteration

- -Instruction execution prior to exiting the loop due to an interrupt

- -Instruction execution upon re-entering the loop after an interrupt is serviced

#### 4.4.3.2 PSV and Instruction Stalls

Refer to Item 5 in this FRM Errata Document for more information about instruction stalls using PSV.

### Page 5-5, Table 5-1 NVMCON Register Values

On page 5-5, Table 5-1 NVMCON Register Values should be replaced with the following:

Table 5-1: NVMCON Register Values

| NVMCON Register Values for RTSP Program and Erase Operations |                             |                         |              |  |  |  |  |

|--------------------------------------------------------------|-----------------------------|-------------------------|--------------|--|--|--|--|

| Memory Type                                                  | Operation                   | Data Size               | NVMCON Value |  |  |  |  |

| Flash PM                                                     | Erase                       | 1 row (32 instr. words) | 0x4041       |  |  |  |  |

| FIASII FIVI                                                  | Program                     | 1 row (32 instr. words) | 0x4001       |  |  |  |  |

|                                                              | Erase                       | 1 data word             | 0x4044       |  |  |  |  |

| Data EEPROM                                                  | Liase                       | 16 data words           | 0x4045       |  |  |  |  |

| Dala EEPHOW                                                  | Drogram                     | 1 data word             | 0x4004       |  |  |  |  |

|                                                              | Program                     | 16 data words           | 0x4005       |  |  |  |  |

| Configuration Register                                       | Write <sup>(see Note)</sup> | 1 config. register      | 0x4008       |  |  |  |  |

**Note:** The device configuration registers may be written to a new value without performing an erase cycle.

### Page 5-6, Section 5.3.2 NVMADR Register

On page 5-6, Section 5.3.2 NVMADR Register should be replaced with the following:

### 5.3.2 NVM Address Registers

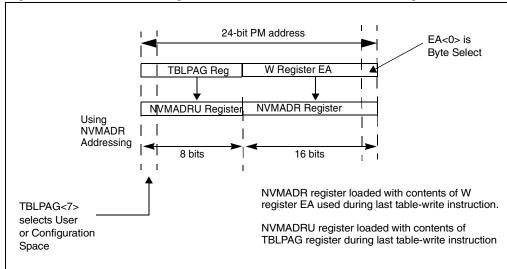

There are two NVM Address Registers - NVMADRU and NVMADR. These two registers when concatenated form the 24-bit effective address (EA) of the selected row or word for programming operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA.

The register pair, NVMADRU:NVMADR, capture the EA<23:0> of the last table-write instruction that has been executed and select the row of Flash or EEPROM memory to write/erase. Figure 5-2 shows how the program memory EA is formed for programming and erase operations.

Although the NVMADRU and NVMADR registers are automatically loaded by the table-write instructions, the user can also directly modify their contents before the programming operation begins. A write to these registers will be required prior to an erase operation, because no table-write instructions are required for any erase operation.

Figure 5-2: NVM Addressing with TBLPAG and NVM Address Registers

### 11. Page 5-7, Register 5-1 NVMCON

On page 5-7, Register 5-1: NVMCON: Non-Volatile Memory Control Register, the definition of the WREN and PROGOP bits should be modified as follows. All other bit definitions do not change and hence are not described here.

### Register 5-1: NVMCON: Non-Volatile Memory Control Register

| Upper Byte | e:    |          |     |     |     |     |       |

|------------|-------|----------|-----|-----|-----|-----|-------|

| R/S-0      | R/W-0 | R/W-0    | U-0 | U-0 | U-0 | U-0 | U-0   |

| WR         | WREN  | WRERR    | _   | _   | _   | _   | _     |

| bit 15     |       | <u> </u> |     |     | •   |     | bit 8 |

| Lower Byte | e:    |       |        |       |       |       |       |

|------------|-------|-------|--------|-------|-------|-------|-------|

| R/W-0      | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|            |       |       | PROGOP | <7:0> |       |       |       |

| bit 7      |       |       |        |       |       |       | bit 0 |

bit 14 WREN: Write (Erase or Program) Enable bit

1 = Enable an erase or program operation

0 = No operation allowed (Device clears this bit on completion of the write/erase operation)

bit 7-0 **PROGOP<7:0>:** Programming Operation Command Byte bits

### Erase Operations:

0x41 = Erase 1 row (32 instruction words) from 1 panel of program Flash

0x44 = Erase 1 data word from data Flash

0x45 = Erase 1 row (16 data words) from data Flash

### **Programming Operations:**

0x01 = Program 1 row (32 instruction words) into Flash program memory

0x04 = Program 1 data word into data EEPROM

0x05 = Program 1 row (16 data words) into data EEPROM

0x08 = Program 1 data word into device configuration register

### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

S = Settable bit -n =Value at POR 1' =Bit is set

'0' = Bit is cleared x = Bit is unknown

### 12. Page 5-8, Register 5-2: NVMADR: Non-Volatile Memory Address Register, bit 15-0

On page 5-8, Register 5-2: NVMADR: Non-Volatile Memory Address Register, bit 15-0 should be replaced with the following: :

| Upper Byte | ):    |       |         |        |       |       |       |

|------------|-------|-------|---------|--------|-------|-------|-------|

| R/W-x      | R/W-x | R/W-x | R/W-x   | R/W-x  | R/W-x | R/W-x | R/W-x |

|            |       |       | NVMADR< | <15:8> |       |       |       |

| bit 15     |       |       |         | •      | •     |       | bit 8 |

| Lower Byte | <b>)</b> :  |       |       |       |       |       |       |  |

|------------|-------------|-------|-------|-------|-------|-------|-------|--|

| R/W-x      | R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |

|            | NVMADR<7:0> |       |       |       |       |       |       |  |

| bit 7      |             |       |       |       |       |       | bit 0 |  |

### bit 15-0 NVMADR<15:0>: NV Memory Write Address bits

Selects the location to program **or erase** in program or data Flash memory.

This register may be read or written by user. This register will contain the address of EA<15:0> of the last table write instruction executed, until written by the user.

Note:

The NVMADRU register function is similar to the NVMADR register and holds the upper 8 bits of the location to be programmed or erased. The value of the TBLPAG register is automatically loaded into the NVMADRU register during a table write instruction.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 13. Page 5-10, Section 5.4.2.1 Flash Program Memory Programming Algorithm

On page 5-10, Section 5.4.2.1 Flash Program Memory Programming Algorithm should be replaced with the following:

### 5.4.2.1 Flash Program Memory Programming Algorithm

The user can erase and program Flash Program Memory by rows (32 instruction words). The general process is as follows:

- Read one row of program Flash (32 instruction words) and store into data RAM as a data "image". The RAM image must be read from an even 32-word program memory address boundary.

- 2. Update the RAM data image with the new program memory data.

- 3. Erase program Flash row.

- Setup NVMCON register to erase 1 row of Flash program memory.

- Write address of row to be erased into NVMADRU and NVMADR registers.

- · Disable interrupts.

- Write the key sequence to NVMKEY to enable the erase.

- Set the WR bit. This will begin erase cycle.

- CPU will stall for the duration of the erase cycle.

- The WR bit is cleared when erase cycle ends.

- Re-enable interrupts.

- 4. Write 32 instruction words of data from RAM into the Flash program memory write latches.

- 5. Program 32 instruction words into program Flash.

- Setup NVMCON to program one row of Flash program memory.

- · Disable interrupts.

- Write the key sequence to NVMKEY to enable the program cycle.

- Set the WR bit. This will begin the program cycle.

- CPU will stall for duration of the program cycle.

- The WR bit is cleared by the hardware when program cycle ends.

- Re-enable interrupts.

- Repeat steps 1 through 6, as needed, to program the desired amount of Flash program memory

**Note:** The user should remember that the minimum amount of program memory that can be modified using RTSP is 32 instruction word locations. Therefore, it is important that an image of these locations be stored in general purpose RAM before an erase cycle is initiated. An erase cycle must be performed on any previously written locations before any programming is done.

### Page 5-11, Section 5.4.2.2 Erasing a Row of Program Memory

On page 5-11, Section 5.4.2.2 Erasing a Row of Program Memory should be replaced with the following:

### 5.4.2.2 Erasing a Row of Program Memory

The following is a code sequence that can be used to erase a row (32 instructions) of program memory. The NVMCON register is configured to erase one row of program memory. The NVMADRU and NVMADR registers are loaded with the address of the row to be erased. The program memory must be erased at 'even' row boundaries. Therefore, the 6 LSbits of the value written to the NVMADR register have no effect when a row is erased.

The erase operation is initiated by writing a special unlock, or key sequence to the NVMKEY register before setting the WR control bit (NVMCON<15>). The unlock sequence needs to be executed in the exact order shown without interruption. Therefore, interrupts should be disabled prior to writing the sequence.

Two NOP instructions should be inserted in the code at the point where the CPU will resume operation. Finally, interrupts can be enabled (if required).

```

; Setup NVMCON to erase one row of Flash program memory

#0x4041,W0

MOV

VOM

WO NVMCON

; Setup address pointer to row to be ERASED

#tblpage(PROG ADDR),W0

MOV

WO NVMADRU

#tbloffset(PROG_ADDR),W0

VOM

W0,NVMADR

MOV

; Disable interrupts, if enabled

PUSH SR

MOV #0x00E0,W0

IOR

SR

; Write the KEY sequence

#0x55,W0

MOV

MOV WO,

NVMKEY

MOV #0xAA, W0

MOV WO,

NVMKEY

; Start the erase operation

BSET NVMCON, #WR

Insert two NOPs after the erase cycle (required)

; Re-enable interrupts, if needed

```

**Note:** When erasing a row of program memory, the user writes the upper 8 bits of the erase address directly to the NVMADRU and NVMADR registers. Together, the contents of the NVMADRU and NVMADR registers form the complete address of the program

memory row to be erased.

The NVMADRU and NVMADR registers specify the address for all Flash erase and program operations. However, these two registers do not have to be directly written by the user for Flash program operations. This is because the table write instructions used to write the program memory data automatically transfers the TBLPAG register contents and the table write address into the NVMADRU and NVMADR registers.

The above code example could be modified to perform a 'dummy' table write operation to capture the program memory erase address.

### 15. Page 5-12, Section 5.4.2.3 Loading Write Latches

On page 5-12, Section 5.4.2.3 Loading Write Latches should be replaced with the following:

### 5.4.2.3 Loading Write Latches

The following is a sequence of instructions that can be used to load the 768-bits of write latches (32 instruction words). Four TBLWTL and four TBLWTH instructions are needed to load the write latches selected by the table pointer.

The TBLPAG register is loaded with the 8 MSbits of the program memory address. The user does not need to write the NVMADRU:NVMADR register-pair for a Flash programming operation. The 24-bits of the program memory address are automatically captured into the NVMADRU:NVMADR register-pair when each table write instruction is executed. The program memory must be programmed at an 'even' 32 instruction word address boundary. In effect, the 6 LSbits of the value captured in the NVMADR register are not used during the programming operation.

The row of 32 instruction words do not necessarily have to be written in sequential order. The 6 LSbits of the table write address determine which of the latches will be written. However, all 32 instruction words should be written for each programming cycle to overwrite old data.

**Note:** The following code example is the 'Load\_Write\_Latch' code referred to in subquent examples.

```

; Set up a pointer to the first program memory location to be written.

#tblpage(PROG ADDR),W0

MOV

W0 TBLPAG

VOM

#tbloffset(PROG_ADDR),W0

; Perform the TBLWT instructions to write the latches

; W0 is incremented in the TBLWTH instruction to point to the

; next instruction location.

MOV

#LOW WORD 0, W2

MOV

#HIGH BYTE 0,W3

TBLWTL W2 [W0]

TBLWTH W3 [W0++]

; 1st_program_word

MOV #LOW WORD 1, W2

#HIGH BYTE 1,W3

TBLWTL W2 [W0]

TBLWTH W3, [W0++]

; 2nd program word

MOV #LOW WORD 2, W2

#HIGH_BYTE_2,W3

MOV

TBLWTL W2, [W0]

TBLWTH W3 [W0++]

; 3rd program word

MOV #LOW_WORD_3,W2

MOV #HIGH_BYTE_3,W3

TBLWTL W2 [W0]

TBLWTH W3, [W0++]

; 4th_program_word

#LOW_WORD_31,W2

#HIGH BYTE 31,W3

MOV

MOV

TBLWTL W2 [W0]

TBLWTH W3, [W0++]

; 32nd_program_word

```

# 16. Page 6-6, Section 6.2 Non-Maskable Traps

On page 6-6, Section 6.2 Non-Maskable Traps, the second paragraph should be replaced with the following:

The dsPIC30F has **four** implemented sources of non-maskable traps:

- Oscillator Failure Trap

- Stack Error Trap

- Address Error Trap

- Arithmetic Error Trap

### 17. Page 6-7, Section 6.2.2 Hard Traps

On page 6-7, Section 6.2.2 Hard Traps, paragraph 1 should be replaced with the following:

Hard traps include exceptions of priority level 13 through level 15, inclusive. The **address** error (level 13) and oscillator error (level 14) traps fall into this category.

### Page 6-8, Section 6.2.2.3 Address Error Trap (Hard Trap, Level 13)

On page 6-8, Section 6.2.2.3 Address Error Trap (Hard Trap, Level 13), the following additional circumstances under which an Address Error Trap may occur, should be included in the numbered list of items:

- 4.Execution of a "BRA #literal" instruction or a "GOTO #literal" instruction, where literal is an unimplemented program memory address.

- 5.Executing instructions after modifying the PC to point to unimplemented program memory addresses. The PC may be modified by loading a value into the stack and executing a RETURN instruction.

## 19. Page 6-10, Section 6.2.5 Wake-up from SLEEP and IDLE

On page 6-10, Section 6.2.5 Wake-up from SLEEP and IDLE, the existing note should be replaced with the following:

Note: User interrupt sources that are assigned to CPU priority level 0 cannot wake the CPU from SLEEP or IDLE mode, because the interrupt source is effectively disabled. To use an interrupt as a wake-up source, the CPU priority level for the interrupt must be assigned to CPU priority level 1 or greater.

# 20. Page 6-43, Table 6-3: Special Function Registers Associated with Interrupt Controller

On page 6-43, Table 6-3: Special Function Registers Associated with Interrupt Controller, row 3, Bit 0, SFR Name: IFS0, should be replaced with the following:

**INTOIF**

### 21. Page 7-7, Register 7-1 OSCCON

On page 7-7, Register 7-1: OSCCON, the register description should be modified as follows to include the TUN<3:0> bits for the on-chip Fast RC oscillator. All other bit definitions do not change and hence are not described.

Register 7-1: OSCCON: Oscillator Control Register

| Upper Byte          | e:    |     |     |      |      |       |        |

|---------------------|-------|-----|-----|------|------|-------|--------|

| R/W-0               | R/W-0 | R-y | R-y | U-0  | U-0  | R/W-y | R/W-y  |

| TUN3 TUN2 COSC<1:0> |       |     |     | TUN1 | TUN0 | NOSC  | C<1:0> |

| bit 15              |       |     |     |      |      |       | bit 8  |

| Lower Byte | :     |      |     |       |     |         |       |

|------------|-------|------|-----|-------|-----|---------|-------|

| R/W-0      | R/W-0 | R-0  | U-0 | R/W-0 | U-0 | R/W-0   | R/W-0 |

| POST       | <1:0> | LOCK | -   | CF    | _   | LPOSCEN | OSWEN |

| bit 7      |       |      |     |       | •   |         | bit 0 |

bit 15-14 **TUN<3:2>:** Upper 2 bits of the TUN bit-field. Refer to the description of TUN<1:0> (OSCCON<11:10>) bits for details.

### bit 11-10 **TUN<1:0>:** Lower 2 bits of the TUN bit-field.

The four bit field specified by TUN<3:0> allows the user to tune the internal fast RC oscillator which has a nominal frequency of 8 MHz. The user may be able to tune the frequency of the FRC oscillator within a range of +/- 12% (or 960 kHz) in steps of 1.5% around the factory-calibrated frequency setting, as follows:

**TUN<3:0>** = 0111 provides the highest frequency

. . . . . .

**TUN<3:0>** = 0000 provides the factory-calibrated frequency

----

TUN<3:0> = 1000 provides the lowest frequency

**Note:** Refer to the device-specific data sheet for the tuning range and tuning step size for the FRC ocillator on your device.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

y = Value set from configuration bits on POR or BOR

**Note:** The OSCCON register description and functionality may vary depending on the clock sources available on the selected device. Please refer to the specific device data sheet for additional details on this register..

### 22. Page 7-23, Section 7.17.3 Clock Switching Tips

On page 7-23, Section 7.17.3 Clock Switching Tips, add the following note to the end:

Note:

The application should not attempt to switch to a clock of frequency lower than 100 KHz when the fail-safe clock monitor is enabled. If such clock switching is performed, the device may generate an oscillator fail trap and switch to the Fast RC oscillator.

## 23. Page 7-24, Section 7.17.7.2 Aborting a Clock Switch

On page 7-24, Section 7.17.7.2 Aborting a Clock Switch, should be replaced with the following:

### 7.17.7.2 Aborting a Clock Switch

The following code sequence would be used to ABORT an unsuccessful clock switch:

```

#OSCCON,W1

VOM

; pointer to OSCCON

#0x46,W2

; first unlock code

MOV.B

; second unlock code

#0x57,W3

MOV.B

W2, [W1]

; write first unlock code

MOV.B

MOV.B W3, [W1]

; write second unlock code

OSCCON, #OSWEN

BCLR

; ABORT the switch

```

# 24. Page 10-4, Section 10.3.6 Wake-up from SLEEP on Interrupt

On page 10-4, Section 10.3.6 Wake-up from SLEEP on Interrupt, the following text should be added:

User interrupt sources that are assigned to CPU priority level 0 cannot wake the CPU from SLEEP mode, because the interrupt source is effectively disabled. To use an interrupt as a wake-up source, the CPU priority level for the interrupt must be assigned to CPU priority level 1 or greater.

### 25. Page 10-4, Section 10.4 IDLE Mode

On page 10-4, Section 10.4 IDLE Mode, the following text should be added:

User interrupt sources that are assigned to CPU priority level 0 cannot wake the CPU from IDLE mode, because the interrupt source is effectively disabled. To use an interrupt as a wake-up source, the CPU priority level for the interrupt must be assigned to CPU priority level 1 or greater.

# 26. Page 15-6, Register 15-2: PTMR: PWM Time Base Register, bit 14-0

On page 15-6, Register 15-2: PTMR: PWM Time Base Register, the description of bit 0 through bit 14 should be replaced as follows. All other bit definitions do not change and hence are not described.

### Register 15-2: PTMR: PWM Time Base Register

| Upper Byte | <b>)</b> : |       |       |           |       |       |       |

|------------|------------|-------|-------|-----------|-------|-------|-------|

| R-0        | R/W-0      | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

| PTDIR      |            |       | PT    | MR <14:8> |       |       |       |

| bit 15     |            |       |       |           |       |       | bit 8 |

| Lower Byte | e:    |       |       |       |       |       |       |

|------------|-------|-------|-------|-------|-------|-------|-------|

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|            |       |       | PTMR  | <7:0> |       |       |       |

| bit 7      |       |       |       |       |       |       | bit 0 |

### bit 14-0 PTMR <14:0>: PWM Timebase Register Count Value

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 27. Page 15-32, Section 15.10 PWM Fault Pins

On page 15-32, Section 15.10 PWM Fault Pins, paragraph 2 should be replaced with the following:

The fault pins may have other multiplexed functions depending on the dsPIC device variant. When used as a fault input, each fault pin is readable via its corresponding PORT register. The FLTA and FLTB pins function as active low inputs so that it is easy to wire-OR many sources to the same input through an external pull-up resistor. When not used with the PWM module, these pins may be used as general purpose I/O or **another multiplexed function**. Each fault pin has its own interrupt vector, interrupt flag bit, interrupt enable bit, and interrupt priority bits associated with it.

### 28. Page 15-32, Section 15.10.1 Fault Pin Enable Bits

On page 15-32, Section 15.10.1 Fault Pin Enable Bits, paragraph 2 should be replaced with the following:

If all enable bits are cleared in the FLTACON or FLTBCON registers, then that fault input pin has no effect on the PWM module and **no fault interrupts will be produced**.

### 29. Page 17-9, Register 17-4 ADCHS

On page 17-9, Section 17-4 ADCHS, the following note should be added to the ADCHS register description:

Note:

The ADCHS register description and functionality will vary depending on the number of A/D inputs available on the selected device. Please refer to the specific device datasheet for additional details on this register.

# 30. Page 17-14, Section 17.7 Selecting the A/D Conversion Clock

On page 17-14, Section 17.7 Selecting the A/D Conversion Clock, paragraph 3 should be replaced with the following:

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 154 nsec (for VDD = 5V).

Also remove Table 17-1: Typical TAD vs. Device Operating Frequencies.

# 31. Page 17-37, Table 17-5 Converting Three Inputs, Four Times and Four Inputs, One time Per Interrupt

On page 17-37, Table 17-5 Converting Three Inputs, Four Times and Four Inputs, One Timer Per Interrupt, the initialization of the SMPI <3:0> (ADCON2<5:2>) bits should be modified as follows:

SMPI < 3:0 > = 0011

# 32. Page 17-46, Section 17.16 A/D Sampling Requirements

The entire Section 17.16 should be replaced with the following text and figures:

The analog input model of the 10-bit A/D converter is shown in Figure 17-21. The total sampling time for the A/D is a function of the internal amplifier settling time and the holding capacitor charge time.

For the A/D converter to meet its specified accuracy, the charge holding capacitor (Chold) must be allowed to fully charge to the voltage level on the analog input pin. The source impedance (Rs), the interconnect impedance (Ric), and the internal sampling switch (Rss) impedance combine to directly affect the time required to charge the capacitor Chold. The combined impedance of the analog sources must therefore be small enough to fully charge the holding capacitor within the chosen sample time. To minimize the effects of pin leakage currents on the accuracy of the A/D converter, the maximum recommended source impedance, Rs, is 5 k $\Omega$ . After the analog input channel is selected (changed), this sampling function must be completed prior to starting the conversion. The internal holding capacitor will be in a discharged state prior to each sample operation.

At least 1 TAD time period should be allowed between conversions for the sample time. For more details, see the device electrical specifications.

**VDD**  $\text{RIC} \leq 250\Omega$ Rss  $\leq$  3 k $\Omega$ Sampling Switch VT = 0.6VRss • CHOLD capacitance CPIN leakage VT = 0.6V= 4.4 pF± 500 nA Legend: CPIN = input capacitance Vт = threshold voltage I leakage = leakage current at the pin due to various junctions Rıc = interconnect resistance Rss = sampling switch resistance CHOLD = sample/hold capacitance (from DAC) Note: CPIN value depends on device package and is not tested. Effect of CPIN negligible if Rs  $\leq$  5 k $\Omega$ .

Figure 17-21: 10-bit A/D Converter Analog Input Model

## 33. Page 18-12, Section 18.7 Selecting the A/D Conversion Clock

On page 18-12, Section 18.7 Selecting the A/D Conversion Clock, paragraph 3 should be replaced with the following:

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 667 nsec (for VDD = 5V).

Also remove Table 18-1: Typical TAD vs. Device Operating Frequencies.

# 34. Page 18-27, Section 18.15 A/D Sampling Requirements

The entire Section 18.15 should be replaced with the following text and figures:

The analog input model of the 12-bit A/D converter is shown in Figure 18-11. The total sampling time for the A/D is a function of the internal amplifier settling time and the holding capacitor charge time.

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the voltage level on the analog input pin. The source impedance (Rs), the interconnect impedance (RIC), and the internal sampling switch (Rss) impedance combine to directly affect the time required to charge the capacitor CHOLD. The combined impedance of the analog sources must therefore be small enough to fully charge the holding capacitor within the chosen sample time. To minimize the effects of pin leakage currents on the accuracy of the A/D converter, the maximum recommended source impedance, Rs, is 2.5 k $\Omega$ . After the analog input channel is selected (changed), this sampling function must be completed prior to starting the conversion. The internal holding capacitor will be in a discharged state prior to each sample operation.

At least 1 TAD time period should be allowed between conversions for the sample time. For more details, see the device electrical specifications.

12-bit A/D Converter Analog Input Model Figure 18-11:  $V_{DD}$  $Ric \le 250\Omega$ Rss ≤ 3 k $\Omega$ Sampling Switch VT = 0.6VRss CHOLD = DAC capacitance I leakage VT = 0.6V= 18 pF+ 500 nA Legend: CPIN = input capacitance Vт = threshold voltage I leakage = leakage current at the pin due to various junctions Ric = interconnect resistance = sampling switch resistance CHOLD = sample/hold capacitance (from DAC) Note: CPIN value depends on device package and is not tested. Effect of CPIN negligible if Rs  $\leq$  2.5 k $\Omega$ .

# 35. Page 19-10, Section 19.4.1 Enabling the UART, Page 19-13, Section 19.5.3 Setup for UART Transmit and Page 19-20, Section 19.9 Initialization

Add the following note to these subsections:

Note: The UTXEN bit should not be set until the UARTEN bit has been set. Otherwise, UART transmissions will not be enabled.

### 36. Page 19-13, Section 19.5.3 Setup for UART Transmit

On page 19-13, Section 19.5.3 Setup for UART Transmit, delete Step 3 in this section.

# 37. Page 19-17, Section 19.6.4 Setup for UART Reception

On page 19-17, Section 19.6.4 Setup for UART Reception, delete Step 3 in this section.

### 38. Page 19-20, Section 19.9 Initialization

On page 19-20, Section 19.9 Initialization, Example 19-2 and Example 19-3 should be replaced with the following:

Example 19-2: 8-bit Transmit/Receive (UART1)

```

#baudrate,W0 ; Set Baudrate

MOV

W0, U1BRG

BSET IPC2, #U1TXIP2 ; Set UART TX interrupt priority

BCLR IPC2, #U1TXIP1 ;

BCLR IPC2, #U1TXIPO ;

BSET IPC2,#U1RXIP2 ; Set UART RX interrupt priority BCLR IPC2,#U1RXIP1 ;

BCLR IPC2,#U1RXIP0

U1STA

CLR

MOV

#0x8800,W0

; Enable UART for 8-bit data,

; no parity, 1 STOP bit,

; no wakeup

MOV

W0,U1MODE

BSET

U1STA, #UTXEN

; Enable transmit

IECO, #U1TXIE

BSET

; Enable transmit interrupts

BSET

IEC0,#U1RXIE

; Enable receive interrupts

```

Example 19-3: 8-bit Transmit/Receive (UART1), Address Detect Enabled

```

#baudrate,W0 ; Set Baudrate

MOV

W0,U1BRG

BSET IPC2, #U1TXIP2 ; Set UART TX interrupt priority

BCLR IPC2, #U1TXIP1 ;

BCLR IPC2, #U1TXIPO ;

BSET IPC2,#U1RXIP2 ; Set UART RX interrupt priority

BCLR IPC2,#U1RXIP1

BCLR IPC2,#U1RXIP0

;

BSET U1STA, #ADDEN

; Enable address detect

; UART1 enabled for 9-bit data,

MOV

#0x8883,W0

; no parity, 1 STOP bit,

; wakeup enabled

MOV

W0,U1MODE

U1STA, #UTXEN

BSET

; Enable transmit

IECO,#U1TXIE ; Enable transmit interrupts

BSET

IECO,#U1RXIE ; Enable receive interrupts

BSET

```

### 39. Page 21-9, Register 21-1 I2CCON

On page 21-9, Register 21-1: I2CCON: I<sup>2</sup>C Control Register, the description of the ACKDT bit should be corrected as follows. All other bit definitions do not change and hence are not described.

Register 21-1: I2CCON: I<sup>2</sup>C Control Register

| <b>Upper Byte</b> | :   |         |             |        |       |        |       |

|-------------------|-----|---------|-------------|--------|-------|--------|-------|

| R/W-0             | U-0 | R/W-0   | R/W-1<br>HC | R/W-0  | R/W-0 | R/W-0  | R/W-0 |

| I2CEN             | _   | I2CSIDL | SCLREL      | IPMIEN | A10M  | DISSLW | SMEN  |

| bit 15            |     |         |             |        |       |        | bit 8 |

| <b>Lower Byte</b> | :     |       |       |       |       |       |       |

|-------------------|-------|-------|-------|-------|-------|-------|-------|

| R/W-0             | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                   |       |       | HC    | HC    | HC    | HC    | HC    |

| GCEN              | STREN | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   |

| bit 7             |       |       |       |       |       |       | bit 0 |

bit 5 **ACKDT:** Acknowledge Data bit (When operating as I<sup>2</sup>C Master. Applicable during master receive.) Value that will be transmitted when the software initiates an Acknowledge sequence.

1 = Send NACK during acknowledge

0 = Send ACK during acknowledge

| Legena:      |                   |

|--------------|-------------------|

| R = Readable | C = Clearable bit |

U = Unimplemented bit, read as '0'

W = Writable HS = Set by Hardware S = Settable bit

HC = Cleared by Hardware '0' = Bit cleared at POR x = Bit is unknown at POR

'1' = Bit is set at POR

### 40. I<sup>2</sup>C Interrupt Bit Names

Table 2 below, shows changes to the nomenclature of the I<sup>2</sup>C module's interrupt enable, status flag and priority bits. These changes should be applied to the entire document.

TABLE 2: INTERRUPT CONTROLLER REGISTER MAP: I<sup>2</sup>C BIT NAMES

| Bit Location in SFR | Bit Name<br>(Incorrect) | Bit Name<br>(Please read as) |

|---------------------|-------------------------|------------------------------|

| IFS0<14>            | BCLIF                   | MI2CIF                       |

| IFS0<13>            | I2CIF                   | SI2CIF                       |

| IEC0<14>            | BCLIE                   | MI2CIE                       |

| IEC0<13>            | I2CIE                   | SI2CIE                       |

| IPC3<10:8>          | BCLIP<2:0>              | MI2CIP<2:0>                  |

| IPC3<6:4>           | I2CIP<2:0>              | SI2CIP<2:0>                  |

# 41. Page 22-12, Equation 22-1 DCI Bit Clock Generator Value

On page 22-12, Equation 22-1: DCI Bit Clock Generator Value, should be replaced by the following:

### **Equation 22-1: DCI Bit Clock Generator Value**

$$BCG<11:0> = \frac{fCY}{2fCSCK} - 1$$

# 42. Page 22-24, Section 22.5.5.3 I<sup>2</sup>S Data Justification

On page 22-24, Section 22.5.5.3 I<sup>2</sup>S Data Justification, paragraph 2 should be replaced by the following:

If DJST = 1, the  $I^2S$  data transfers will be MSb left justified. The MSb of the data word will be presented on the CSDO pin during the same serial clock cycle as the rising or falling edge of the FS signal. After the data word has been transmitted, the state of the CSDO pin is dictated by the CSDOM (DCICON1<6>) bit.

### 43. Page 23-38, Section 23.5.2 Disable Mode

On page 23-38, Section 23.5.2 Disable Mode, add the following note to the end.

Note

Typically, if the CAN module is allowed to transmit in a particular mode of operation and a transmission is requested immediately after the CAN module has been placed in that mode of operation, the module waits for 11 consecutive recessive bits on the bus before starting transmission. If the user switches to Disable Mode within this 11-bit period, then this transmission is aborted and the corresponding TXABT bit is set and TXREQ bit is cleared.

# 44. Pages 23-22 through 23-27, Table 23-1 and Table 23-2 CAN1/CAN2 Register Map

On pages 23-22 through 23-27 in Tables 23-1 and 23-2, the nomenclature of the CAN module transmit and receive buffer registers as well as the addresses of the CAN2 module registers should be changed/corrected as follows:

XXXX MIDE • EID<13:6> EID<13:6> EID<13:6> SID<5:0> SID<5:0> SID<5:0> SID<5:0> SID<5:0> SID<5:0> 1 1 Bit EID<17:14> EID<17:14> EID<17:14> EID<17:14> SID<10:6> SID<10:6> SID<10:6> EID<5:0> EID<5:0> **CAN1 REGISTER MAP** 5 4 31A 31E ADR 30C 312 316 32C 33C 30A 30E 310 318 32A 32E 330 33A 300 302 304 306 308 314 320 322 324 326 328 332 334 336 338 **TABLE 23-1:** File Name C1RXM1EIDH C1RXM0EIDH C1RXM1EIDL C1RXF0EIDH C1RXF3EIDH C1RXF4EIDH C1RXF1EIDH C1RXF2EIDH C1RXF5EIDH C1RXM0EIDL C1RXF0EIDL C1RXF1EIDL C1 RXF2EIDL C1 RXF3EIDL C1RXF4EIDL C1RXM0SID C1RXM1SID C1RXF5SID C1RXF5EIDL C1RXF1SID C1RXF3SID C1RXF4SID C1RXF0SID C1RXF2SID nunsed nunsed nunsed nunsed nunsed

| TABLE 23-1: | CAN | CAN1 REGISTER MAP (CONTINU | ISTER | MAP (      | CONTI          | NUED)                    |     |           |           |           |           |            |                          |            |   |            |          |       |

|-------------|-----|----------------------------|-------|------------|----------------|--------------------------|-----|-----------|-----------|-----------|-----------|------------|--------------------------|------------|---|------------|----------|-------|

| File Name   | ADR |                            |       |            |                |                          |     |           |           | Bit       |           |            |                          |            |   |            |          | RESET |

|             |     | 15                         | 14    | 13         | 12             | 11                       | 10  | 6         | 8         | 7         | 9         | 2          | 4                        | 3          | 2 | ٢          | 0        |       |

| C1TX2SID    | 340 |                            |       | SID<10:6>  |                |                          | Ι   | Ι         | 1         |           |           | SID<5:0>   | <0                       |            |   | SRR        | TX       | XXXX  |

| C1TX2EID    | 342 |                            | EID<  | EID<17:14> |                | I                        | Ι   | _         | Ι         |           |           |            | EID<13:6>                | 2>         |   |            |          | XXXX  |

| C1TX2DLC    | 342 |                            |       | EID.       | EID<5:0>       |                          |     | TX<br>RTR | TX<br>RB1 | TX<br>RB0 |           | DLC<3:0>   | <0:                      |            | 1 | Ι          | -        | XXXX  |

| C1TX2B1     | 346 |                            |       | Ľ          | Transmit B     | Transmit Buffer 0 Byte 1 | 1 6 |           |           |           |           | Trar       | Transmit Buffer 0 Byte 0 | 0 Byte 0   |   |            |          | XXXX  |

| C1TX2B2     | 348 |                            |       | L          | Transmit B     | Transmit Buffer 0 Byte 3 | e 3 |           |           |           |           | Trar       | Transmit Buffer 0 Byte 2 | . 0 Byte 2 |   |            |          | XXXX  |

| C1TX2B3     | 34A |                            |       | -          | Fransmit B     | Transmit Buffer 0 Byte 5 | 9 e |           |           |           |           | Trar       | Transmit Buffer 0 Byte 4 | . 0 Byte 4 |   |            |          | XXXX  |

| C1TX2B4     | 34C |                            |       | r-<br>     | Fransmit B     | Transmit Buffer 0 Byte 7 | 2 £ |           |           |           | i         | Trar       | Transmit Buffer 0 Byte 6 | 0 Byte 6   |   |            |          | XXXX  |

| C1TX2CON    | 34E | 1                          | T     | I          | I              | 1                        | 1   | I         | 1         | I         | TX<br>ABT | TX<br>LARB | TX                       | TX BE      | 1 | TXPRI[1:0] | 1:0]     | 0000  |

| C1TX1SID    | 350 |                            |       | SID<10:6>  | ^              |                          | I   | Ι         | _         |           |           | SID<5:0>   | <0                       |            |   | SRR        | TX<br>DE | XXXX  |

| C1TX1EID    | 352 |                            | EID<  | EID<17:14> |                | 1                        | 1   | -         | 1         |           |           |            | EID<13:6>                | <b>~</b>   |   |            |          | XXXX  |

| C1TX1DLC    | 352 |                            |       | EID        | EID<5:0>       |                          |     | TX<br>RTR | TX<br>RB1 | TX<br>RB0 |           | DLC<3:0>   | <0:                      |            | I | Ι          | I        | XXXX  |

| C1TX1B1     | 356 |                            |       | r-         | Fransmit B     | Transmit Buffer 0 Byte 1 | 1   |           |           |           |           | Trar       | Transmit Buffer 0 Byte 0 | . 0 Byte 0 |   |            |          | XXXX  |

| C1TX1B2     | 358 |                            |       |            | Fransmit B     | Transmit Buffer 0 Byte 3 | 93  |           |           |           |           | Trar       | Transmit Buffer 0 Byte 2 | . 0 Byte 2 |   |            |          | XXXX  |

| C1TX1B3     | 35A |                            |       | -          | Fransmit B     | Transmit Buffer 0 Byte 5 | e 5 |           |           |           |           | Trar       | Transmit Buffer 0 Byte 4 | . 0 Byte 4 |   |            |          | XXXX  |

| C1TX1B4     | 35C |                            |       |            | Fransmit B     | Transmit Buffer 0 Byte 7 | 2 £ |           |           |           | i         | Trar       | Transmit Buffer 0 Byte 6 | 0 Byte 6   |   |            |          | XXXX  |

| C1TX1CON    | 35E | T                          | I     | I          | T              | T                        | I   | I         | Ι         | I         | TX<br>ABT | TX<br>LARB | TX<br>ERR                | TX<br>REQ  | I | TXPRI[1:0] | 1:0]     | 0000  |

| C1TX0SID    | 360 |                            |       | SID<10:6>  | ^              |                          | Ι   | Ι         | _         |           |           | SID<5:0>   | <0                       |            |   | SRR        | TX       | XXXX  |

| C1TX0EID    | 362 |                            | EID<  | EID<17:14> |                | 1                        | 1   | 1         | 1         |           | ļ         |            | EID<13:6>                | <u>ئ</u>   |   |            |          | XXXX  |

| C1TX0DLC    | 362 |                            |       | EID.       | EID<5:0>       |                          |     | TX<br>RTR | TX<br>RB1 | TX<br>RB0 |           | DLC<3:0>   | <0:                      |            | I | I          | I        | XXXX  |

| C1TX0B1     | 366 |                            |       |            | Transmit Buffe | uffer 0 Byte 1           | 1   |           |           |           |           | Trar       | Transmit Buffer 0 Byte 0 | . 0 Byte 0 |   |            |          | XXXX  |

| C1TX0B2     | 368 |                            |       |            | Fransmit B     | Transmit Buffer 0 Byte 3 | 93  |           |           |           |           | Trar       | Transmit Buffer 0 Byte 2 | . 0 Byte 2 |   |            |          | XXXX  |

| C1TX0B3     | 36A |                            |       |            | Fransmit B     | Transmit Buffer 0 Byte 5 | e 5 |           |           |           |           | Trar       | Transmit Buffer 0 Byte 4 | . 0 Byte 4 |   |            |          | XXXX  |

| C1TX0B4     | 36C |                            |       | -          | Fransmit B     | Transmit Buffer 0 Byte 7 | 2 Z |           |           |           |           | Trar       | Transmit Buffer 0 Byte 6 | 0 Byte 6   | • |            |          | XXXX  |

| C1TX0CON    | 36E | I                          | I     | I          | I              | I                        | I   | I         | I         | I         | TX<br>ABT | TX<br>LARB | X H                      | X S        | I | TXPRI[1:0] | 1:0]     | 0000  |

|             |     |                            |       |            |                |                          |     |           |           |           |           |            |                          |            |   |            |          |       |

0480

0000

0000

0000

XXXX

0000

0000

RXB0 RXB0 F 준립 분토이 X 님 PRSEG[2:0] FILHIT[2:0] JTOFF HXB1 RXB1 DLC[3:0] DLC[3:0] ICODE[2:0] RXB0 DBEN TXB0 TXB0 BRP[5:0] Receive Buffer 1 Byte 0 Receive Buffer 1 Byte 6 Receive Buffer 0 Byte 4 Receive Buffer 0 Byte 6 Receive Buffer 1 Byte 2 Receive Buffer 0 Byte Receive Error Counter TXB1 TXB1 XX H S EID<13:6>

RX

RB0 SEG1PH[2:0] TXB2 TXB2 Ж. Во X H X H ER E ERR OPMODE[2:0] SAM WAK WAK SEG2 PHTS ₹ F X I 퐀긆 ₹ ⊒ Bit E WARN RX RB1 X H REQOP[2:0] RX WARN X F X E TX VARN Receive Buffer 1 Byte 7 Receive Buffer 0 Byte 5 Receive Buffer 0 Byte 7 Receive Buffer 1 Byte 1 Error Counter CAN1 REGISTER MAP (CONTINUED) RXBP CAN ABAT TXBP EID<0:5> TXBO CSIDL 5 RXB1 OVR WAK 4 RXB0 OVR CAN ADR 37A 37C 376 386 388 38A 370 372 374 378 37E 382 38C 38E 392 39A 39C 3FE 394 **TABLE 23-1:** File Name C1RX1CON C1RX0CON C1RX1DLC C1RX1DLC C1RX1SID C1RX1SID C1RX1EID C1RX1B4 C1RX1EID C1RX1B3 C1RX1B1 C1RX1B2 C1RX0B2 C1RX0B3 C1RX0B4 Reserved C1RX0B1 C1CFG2 C1CTRL C1CFG1 C1INTF C1INTE C1EC

0000

XXXX

XXXX

XX XX XX

XXXX

XXXX

XXXX

Legend: x = Unknown

|            | 90. |    |    |     |          |   |           |            |   |     |   |          |           |      |   |   |       | 1000   |

|------------|-----|----|----|-----|----------|---|-----------|------------|---|-----|---|----------|-----------|------|---|---|-------|--------|

| FIIE Name  | AUR |    |    |     |          |   |           |            |   | BIT |   |          |           |      |   |   |       | AESE I |

|            |     | 15 | 14 | 13  | 12       | Ξ | 9         | 6          | 8 | 7   | 9 | 2        | 4         | ဗ    | 2 | - | 0     |        |

| C2RXF0SID  | 3C0 | _  | -  | -   |          |   | SID<10:6> |            |   |     |   | SID<5:0> | <0:       |      |   | _ | EXIDE | XXXX   |

| C2RXF0EIDH | 3C2 | _  | 1  | _   | Ι        |   | EID<1     | EID<17:14> |   |     |   |          | EID<13:6> | 3:6> |   |   |       | XXXX   |

| C2RXF0EIDL | 3C4 |    |    | EID | EID<5:0> |   |           | _          | I | _   | 1 | I        | Ι         | 1    | I | _ | -     | XXXX   |

| pesnun     | 3C6 | -  | 1  | -   | 1        | Ι | Ι         | Ι          | - | -   | 1 | I        | Ι         | Ι    | 1 | _ | _     | XXXX   |

| C2RXF1SID  | 3C8 | Ι  | -  | Ι   |          |   | SID<10:6> |            |   |     |   | SID<5:0> | <0:       |      |   | _ | EXIDE | XXXX   |

| C2RXF1EIDH | 3CA | _  | 1  | _   | 1        |   | EID<1     | EID<17:14> |   |     |   |          | EID<13:6> | 3:6> |   |   |       | XXXX   |

| C2RXF1EIDL | 3CC |    |    | EID | EID<5:0> |   |           | Ι          | 1 | 1   | 1 | 1        | 1         | 1    | 1 | _ | _     | XXXX   |

| pesnun     | 3CE | _  | 1  | -   | 1        | Ι | Ι         | Ι          | 1 | 1   | 1 | 1        | Ι         | 1    | I | _ | _     | XXXX   |

| C2RXF2SID  | 3D0 | _  | 1  | -   |          |   | SID<10:6> |            |   |     |   | SID<5:0> | <0:       |      |   | _ | EXIDE | XXXX   |

| C2RXF2EIDH | 3D2 | 1  | 1  | -   | 1        |   | EID<1     | EID<17:14> |   |     |   |          | EID<13:6> | 3:6> |   |   |       | XXXX   |

| C2RXF2EIDL | 3D4 |    |    | EID | EID<5:0> |   |           | Ι          | I | I   | 1 | I        | I         | 1    | I |   | I     | XXXX   |

| nnused     | 3D6 | _  | 1  | -   | 1        | 1 | -         | _          | _ | -   | _ | _        | 1         | 1    | 1 | _ | -     | XXXX   |

| C2RXF3SIDH | 3D8 | _  |    | _   |          |   | SID<10:6> |            |   |     |   | SID<5:0> | <0:       |      |   | _ | EXIDE | XXXX   |

| C2RXF3EID  | 3DA | _  | -  | -   | Ι        |   | EID<1     | EID<17:14> |   |     |   |          | EID<13:6> | 3:6> |   |   |       | XXXX   |

| C2RXF3EIDL | 3DC |    |    | EID | EID<5:0> |   |           | _          | _ | -   | _ | _        | 1         | 1    | Ι | _ | _     | XXXX   |

| nnused     | 3DE | _  | -  | _   | -        | Ι | _         | _          | _ | -   | _ | _        | 1         | 1    | Ι | _ | _     | XXXX   |

| C2RXF4SID  | 3E0 | _  |    | -   |          |   | SID<10:6> |            |   |     |   | SID<5:0> | <0:       |      |   | _ | EXIDE | XXXX   |

| C2RXF4EIDH | 3E2 | _  | -  | _   | -        |   | EID<1     | EID<17:14> |   |     |   |          | EID<13:6> | 3:6> |   |   |       | XXXX   |

| C2RXF4EIDL | 3E4 |    |    | EID | EID<5:0> |   |           | _          | I | _   | 1 | I        | Ι         | 1    | I | _ | -     | XXXX   |

| nnused     | 3E6 | Ι  | 1  | Ι   | 1        | Ι | Ι         | Ι          | _ | Ι   | Ι | Ι        | 1         | 1    | 1 | _ | _     | XXXX   |

| C2RXF5SID  | 3E8 | I  |    |     |          |   | SID<10:6> |            |   |     |   | SID<5:0> | <0:       |      |   | _ | EXIDE | XXXXX  |

| C2RXF5EIDH | 3EA | _  | -  | _   | 1        |   | EID<1     | EID<17:14> |   |     |   |          | EID<13:6> | 3:6> |   |   |       | XXXX   |

| C2RXF5EIDL | 3EC |    |    | EID | EID<5:0> |   |           | Ι          | _ | Ι   | Ι | Ι        | 1         | 1    | 1 | _ | _     | XXXX   |

| nunsed     | 3EE | 1  | I  | 1   | 1        | 1 | 1         | Ι          | I | Ι   | 1 | I        | 1         | 1    | 1 | 1 | I     | XXXX   |

| C2RXM0SID  | 3F0 | _  | _  | _   |          |   | SID<10:6> |            |   |     |   | SID<5:0> | <0:5      |      |   | _ | MIDE  | XXXX   |

| C2RXM0EIDH | 3F2 | 1  | 1  | 1   | 1        |   | EID<1     | EID<17:14> |   |     |   |          | EID<13:6> | 3:6> |   |   |       | XXXX   |

| C2RXM0EIDL | 3F4 |    |    | EID | EID<5:0> |   |           | _          | _ | -   | _ | _        | 1         | 1    | Ι | _ | _     | XXXX   |

| nnused     | 3F6 | _  |    | _   | -        | Ι | _         | _          | _ | -   | _ | _        | 1         | 1    | Ι | _ | _     | XXXX   |

| C2RXM1SID  | 3F8 | _  | -  | -   |          |   | SID<10:6> |            |   |     |   | SID<5:0> | <0:       |      |   | _ | MIDE  | XXXX   |

| C2RXM1EIDH | 3FA | _  | -  | _   | Ι        |   | EID<1     | EID<17:14> |   |     |   |          | EID<13:6> | 3:6> |   |   |       | XXXX   |

| C2RXM1EIDL | ЗЕС |    |    | EID | EID<5:0> |   |           | _          | _ | -   | _ | _        | 1         | 1    | Ι | _ | _     | XXXX   |

| nunsed     | 3FE | I  | 1  | I   | 1        | 1 | 1         | I          | 1 | 1   | 1 | 1        | 1         | 1    | I | 1 | 1     | XXXX   |

|            |     |    |    |     |          |   |           |            |   |     |   |          |           |      |   |   |       |        |

**CAN2 REGISTER MAP**

RESET 0000 0000 0000 XXXX TX IDE 조립 TXPRI[1:0] TXPRI[1:0] TXPRI[1:0] Transmit Buffer 0 Byte 0 Transmit Buffer 0 Byte 6 Transmit Buffer 0 Byte 4 Transmit Buffer 0 Byte 2 Transmit Buffer 0 Byte 4 Transmit Buffer 0 Byte 6 Transmit Buffer 0 Byte 2 Transmit Buffer 0 Byte 2 Transmit Buffer 0 Byte 6 TX REQ 末 X Z EID<13:6> TX ERR X H X H TX TX ARB TX-TX ABT XT ABT XX ABT TX RB0 TX RB0 大 8 Bit 大 문 TX RB1 TX RB1 œ X F TX RTR X # 6 9 Transmit Buffer 0 Byte 5 Transmit Buffer 0 Byte 3 Transmit Buffer 0 Byte 3 Transmit Buffer 0 Byte 5 Transmit Buffer 0 Byte 3 Transmit Buffer 0 Byte 7 Transmit Buffer 0 Byte 7 Transmit Buffer 0 Byte 7 Transmit Buffer 0 Byte 1 CAN2 REGISTER MAP (CONTINUED) Ξ SID<10:6> EID<17:14> EID<17:14> EID<17:14> 4 15 ADR 40C 41A 41C 42C 40A 42A 42E 400 402 404 406 408 412 414 416 418 420 422 424 426 428 **TABLE 23-2:** File Name C2TX0CON C2TX2DLC C2TX2CON C2TX1CON C2TX0DLC C2TX1DLC C2TX1SID C2TX0SID C2TX2SID C2TX1EID C2TX0EID C2TX2EID C2TX1B3 C2TX2B2 C2TX2B3 C2TX2B4 C2TX1B2 C2TX1B4 C2TX0B2 C2TX0B3 C2TX0B4 C2TX0B1 C2TX2B1 C2TX1B1

| <b>TABLE</b> 23-2:  | CAN        | 2 REGI      | STER        | MAP (     | CAN2 REGISTER MAP (CONTIN | VUED)        |              |             |           |              |             |          |                         |                 |                                              |             |                 |       |

|---------------------|------------|-------------|-------------|-----------|---------------------------|--------------|--------------|-------------|-----------|--------------|-------------|----------|-------------------------|-----------------|----------------------------------------------|-------------|-----------------|-------|

| File Name           | ADR        |             |             |           |                           |              |              |             |           | Bit          |             |          |                         |                 |                                              |             |                 | RESET |

|                     |            | 15          | 14          | 13        | 12                        | Ħ            | 10           | 6           | 8         | 7            | 9           | 5        | 4                       | 3               | 2                                            | -           | 0               |       |

| C2RX1SID            | 430        | I           | I           | I         |                           |              | SID<10:6>    |             |           |              |             | SID<5:0> | 2:0>                    |                 |                                              | SRR         | RX<br>IDE       | XXXX  |

| C2RX1EID            | 432        | 1           | -           |           | 1                         |              | EID<         | EID<17:14>  |           |              |             |          | EID<13:6>               | 3:6>            |                                              |             |                 | XXXX  |

| C2RX1DLC            | 434        |             |             | EID       | EID<0:5>                  |              |              | RX<br>RTR   | RX<br>RB1 | -            | -           | Ι        | RX<br>RB0               |                 | DLC                                          | DLC[3:0]    |                 | XXXX  |

| C2RX1B1             | 436        |             |             | 1         | Receive Buffer 1 Byte 1   | ıffer 1 Byte | -            |             |           |              |             | Æ        | Receive Buffer 1 Byte 0 | er 1 Byte 0     |                                              |             |                 | XXXX  |

| C2RX1B2             | 438        |             |             | 1         | Receive Buffer 1 Byte 3   | iffer 1 Byte | 3            |             |           |              |             | Ŗ        | Receive Buffer 1 Byte 2 | er 1 Byte 2     |                                              |             |                 | XXXX  |

| C2RX1B3             | 43A        |             |             | 1         | Receive Buffer 1 Byte 5   | ıffer 1 Byte | 5            |             |           |              |             | Ŗ        | Receive Buffer 1 Byte 4 | er 1 Byte 4     |                                              |             |                 | XXXX  |

| C2RX1B4             | 43C        |             |             |           | Receive Buffer 1 Byte 7   | ıffer 1 Byte | 7            |             |           |              |             | ď        | Receive Buffer 1 Byte 6 | er 1 Byte 6     |                                              |             |                 | XXXX  |

| C2RX1CON            | 43E        | I           | I           | I         | _                         | ı            | -            | I           | I         | RX<br>FUL    | -           | I        | RX<br>ERR               | RX<br>RTR<br>R0 | _                                            | FILHIT[2:0] |                 | 0000  |

| C2RX1SID            | 440        | ı           | I           | -         |                           |              | SID<10:6>    | ٨           |           |              |             | SID<5:0> | >0:9                    |                 |                                              | SRR         | RX<br>IDE       | XXXX  |

| C2RX1EID            | 442        | 1           | 1           |           | 1                         |              | EID<         | EID<17:14>  |           |              |             |          | EID<13:6>               | 3:6>            |                                              |             |                 | XXXX  |

| C2RX1DLC            | 444        |             |             | EID       | EID<0:5>                  |              |              | RX<br>RTR   | RX<br>RB1 | -            | -           | I        | RX<br>RB0               |                 | DLC                                          | DLC[3:0]    |                 | XXXX  |

| C2RX0B1             | 446        |             |             | 1         | Receive Buffer 0 Byte 1   | ıffer 0 Byte | <del>-</del> |             |           |              |             | Ť        | Receive Buffer 0 Byte 0 | er 0 Byte 0     |                                              |             |                 | XXXX  |

| C2RX0B2             | 448        |             |             |           | Receive Buffer 0 Byte 3   | ıffer 0 Byte | က            |             |           |              |             | ď        | Receive Buffer 0 Byte 2 | 3r 0 Byte 2     |                                              |             |                 | XXXX  |

| C2RX0B3             | 44A        |             |             |           | Receive Buffer 0 Byte 5   | ıffer 0 Byte | 2            |             |           |              |             | ď        | Receive Buffer 0 Byte 4 | эr 0 Byte 4     |                                              |             |                 | XXXX  |

| C2RX0B4             | 44C        |             |             | -         | Receive Buffer 0 Byte 7   | ıffer 0 Byte | 7            |             |           |              |             | ă        | Receive Buffer 0 Byte 6 | er 0 Byte 6     |                                              |             |                 | XXXX  |

| C2RX0CON            | 44E        | I           | -           | I         | _                         | Ι            | -            | I           | I         | RX<br>FUL    | _           | I        | RX<br>ERR               | RX<br>RTR<br>R0 | RXB0<br>DBEN                                 | JTOFF       | FIL<br>HIT<br>0 | 0000  |

| C2CTRL              | 450        | CAN         | 1           | C<br>SIDL | ABAT                      | CAN          | -            | REQOP[2:0]  | 0]        | O            | OPMODE[2:0] | 0]       | 1                       | -               | ICODE[2:0]                                   | [           | 1               | 0480  |

| C2CFG1              | 452        | Ι           |             |           |                           | I            | I            |             | Ι         | ]wrs         | SJW[1:0]S   |          |                         | BRP[5:0]        | [5:0]                                        |             |                 | 0000  |

| C2CFG2              | 454        | I           | WAK<br>FIL  | I         | I                         | I            | σ I          | SEG2PH[2:0] | [0        | SEG2<br>PHTS | SAM         | S        | SEG1PH[2:0]             | _               | <u>.                                    </u> | PRSEG[2:0]  |                 | 0000  |

| C2INTF              | 456        | RXB0<br>OVR | RXB1<br>OVR | TXBO      | TXBP                      | RXBP         | TX<br>WARN   | RX<br>WARN  | E<br>WARN | IVB<br>F     | WAK<br>IF   | ERR<br>F | TXB2<br>IF              | TXB1            | TXB0<br>IF                                   | RXB1<br>IF  | RXB0<br>IF      | 0000  |

| C2INTE              | 458        | I           | 1           | T         | 1                         | 1            | 1            | I           | I         | N'R<br>E     | WAK<br>IE   | ERR      | TXB2<br>IE              | TXB1            | TXB0<br>IE                                   | RXB1        | RXB0<br>IE      | 0000  |

| C2EC                | 45A        |             |             |           | Transmit Err              | rror Counter | ər           |             |           |              |             | Ж        | Receive Error Counte    | r Counter       |                                              |             |                 | 0000  |

| Reserved            | 45C<br>4FE | I           | I           | I         | 1                         | 1            | 1            | I           | I         | I            | I           | I        | I                       | I               | I                                            | I           | I               | XXXX  |

| Legend: x = Unknown | w          |             |             |           |                           |              |              |             |           |              |             |          |                         |                 |                                              |             |                 |       |

# 45. Page 24-7, Section 24.3.4.1 General Code Segment Configuration Bit Group

On page 24-7, Section 24.3.4.1 General Code Segment Configuration Bit Group, add the following note to the end.

**Note:** If the code protection configuration fuse group (FGS<GCP:GWRP>) bits have been programmed, an erase of the entire code-protected device is only possible at voltages, VDD >= 4.5 volts.

# 46. Page 16-7, Section 16.2 DFLTCON Page 16-8, Section 16.3 Programmable Digital Noise Filters Page 16-14, Section 16.5.3.2 Index Pulse De-skew

The control bits used to control the QEI digital input filters may differ depending upon the device variant that is used. This affects the control bits found in the DFLTCON register. Please refer to the specific device data sheet to determine which DFLTCON control bits are implemented for the device you are using. Some devices have two sets of control bits to control the digital input filters. One set of control bits sets the digital filter characteristics for the INDX pin.

The second set of control bits sets the digital filter characteristics for the QEA and QEB pins. The DS70063B document correctly depicts the DFLTCON control register for these device variants.

Other device variants have one set of control bits that set the digital filter characteristics for the INDX, QEA and QEB pins. The DFLTCON register for these device variants is provided in Register 16-1 below. If the device variant has this DFLTCON register, then paragraph 5 of Section 16.3 "Programmable Digital Noise Filters" is not applicable. Also, Section 16.5.3.2. "Index Pulse De-skew" is not applicable.

Register 16-1: DFLTCON: Digital Filter Control Register

| Upper Half | <b>:</b> |     |     |     |       |       |       |

|------------|----------|-----|-----|-----|-------|-------|-------|

| U-0        | U-0      | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

| _          | _        | 1   | _   | _   | IMV<  | <1:0> | CEID  |

| bit 15     |          |     |     |     |       |       | bit 8 |

| Lower Half | :         |     |     |     |       |

|------------|-----------|-----|-----|-----|-------|

| R/W-0      | R/W-0     | U-0 | U-0 | U-0 | U-0   |

| QEOUT      | QECK<2:0> | _   | _   | _   | _     |

| bit 7      |           |     |     |     | bit 0 |

### bit 15-11 Unimplemented: Read as '0'

bit 10-9 **IMV<1:0>:** Index Match Value – These bits allow the user to specify the state of the QEA and QEB input pins during an Index pulse when the POSCNT register is to be reset.

In 4X Quadrature Count Mode:

IMV1= Required State of Phase B input signal for match on index pulse IMV0= Required State of Phase A input signal for match on index pulse

In 2X Quadrature Count Mode:

IMV1= Selects Phase input signal for Index state match (0 = Phase A, 1 = Phase B)

IMV0= Required State of the selected Phase input signal for match on index pulse

bit 8 **CEID:** Count Error Interrupt Disable

1 = Interrupts due to count errors are disabled

0 = Interrupts due to count errors are enabled

bit 7 **QEOUT:** QEA/QEB/INDX pin Digital Filter Output Enable

1 = Digital filter outputs enabled

0 = Digital filter outputs disabled (normal pin operation)

bit 6-4 QECK<2:0>: QEA/QEB/INDX Digital Filter Clock Divide Select Bits

111 = 1:256 Clock Divide

110 = 1:128 Clock Divide

101 = 1:64 Clock Divide

100 = 1:32 Clock Divide

011 = 1:16 Clock Divide

010 = 1:4 Clock Divide

001 = 1:2 Clock Divide

000 = 1:1 Clock Divide

bit 3-0 Unimplemented: Read as '0'

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

y = Value set from configuration bits on POR or BOR

### APPENDIX A: REVISION HISTORY

Revision A (10/2003)

Original version of the document.

Revision B (01/2004)

First revision of the document.

Revision C (02/2004)

Added clarification to QEI DFLTCON register.

Revision D (05/2004)

Additions made to Errata #21 and Errata #29. Added new Erratas #19, #24 and #25. New Errata #32 – updated document and Figure 17-21. Added new Figure 17-21a 65/2004)

Revision E (06/2004)

Additions made to Errata #30, Errata #32 and Errata #34. Errata #44 was updated. Added new Errata #33 and Errata #35.

| NOTES: |  |  |  |

|--------|--|--|--|

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, MXDEV, MXLAB, PICMASTER, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, dsPICDEM, dsPICDEM.net, dsPICWorks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2004, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002 ===

Microchip received ISO/TS-16949:2002 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona and Mountain View, California in October 2003. The Company's quality system processes and procedures are for its PICmicro® 8-bit MCUs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### WORLDWIDE SALES AND SERVICE