32-Bit

TC1736

32-Bit Single-Chip Microcontroller

Data Sheet V1.1 2009-08

## Microcontrollers

#### **Edition 2009-08**

Published by Infineon Technologies AG 81726 Munich, Germany © 2009 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

32-Bit

TC1736

32-Bit Single-Chip Microcontroller

Data Sheet V1.1 2009-08

# Microcontrollers

#### TC1736 Data Sheet

Revision History: V1.1, 2009-08

| Previous Vers | ion: V1.0                                                                                                     |

|---------------|---------------------------------------------------------------------------------------------------------------|

| Page          | Subjects (major changes since last revision)                                                                  |

| Page 5-95     | $I_{ m DD}$ for 40 MHz variant and the test condition is updated.                                             |

| Page 5-115    | The thermal resistance values are updated, the method used for the specified thermal resistances is included. |

| Page 5-116    | The package name is corrected.                                                                                |

| Previous Vers | ion: V0.2                                                                                                     |

| Page 2-25     | Text which describes the endurance of PFlash and DFlash is enhanced.                                          |

| Page 3-56     | Input spike-filter info is added to PORST.                                                                    |

| Page 3-56     | A footnote is added to $V_{DDMF}$ .                                                                           |

| Page 5-82     | The spike-filters parameters are included, $t_{\rm SF1}$ , $t_{\rm SF2}$ .                                    |

| Page 5-85     | The maximum limit for $I_{\rm OZ1}$ is updated.                                                               |

| Page 5-93     | The temperature sensor measurement time parameter is added.                                                   |

| Page 5-95     | $I_{ m DD}$ for 40 MHz variant is added.                                                                      |

| Page 5-101    | The condition for HWCFG is deleted from hold time from PORST rising edge.                                     |

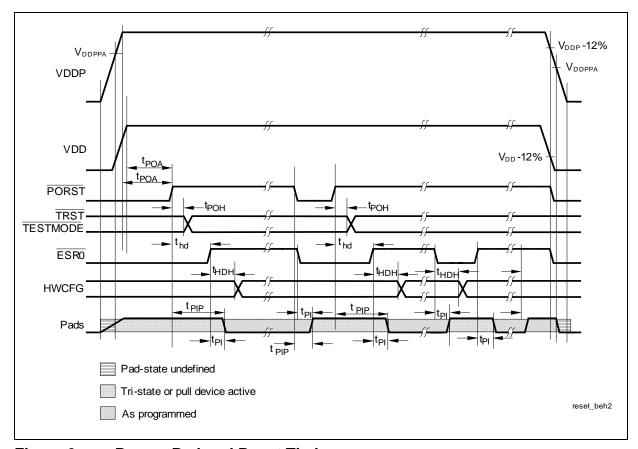

| Page 5-102    | The power, pad, reset timing figure is updated.                                                               |

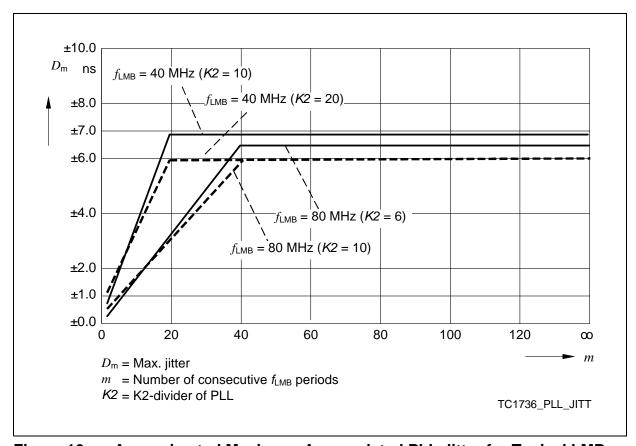

| Page 5-103    | The notes under the PLL sections are updated.                                                                 |

|               |                                                                                                               |

#### **Trademarks**

TriCore® is a trademark of Infineon Technologies AG.

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

Data Sheet V1.1, 2009-08

## **Table of Contents**

## **Table of Contents**

| 1       | Summary of Features                                | 4  |

|---------|----------------------------------------------------|----|

| 2       | Introduction                                       | 7  |

| 2.1     | About this Document                                | 7  |

| 2.1.1   | Related Documentations                             | 7  |

| 2.1.2   | Text Conventions                                   | 8  |

| 2.1.3   | Reserved, Undefined, and Unimplemented Terminology | 9  |

| 2.1.4   | Register Access Modes                              | 10 |

| 2.1.5   | Abbreviations and Acronyms                         | 11 |

| 2.2     | System Architecture of the TC1736                  |    |

| 2.2.1   | Block Diagram                                      | 14 |

| 2.2.2   | System Features of the TC1736 device               | 15 |

| 2.3     | High-Performance 32-Bit TriCore CPU                |    |

| 2.4     | On-Chip System Units                               |    |

| 2.4.1   | Flexible Interrupt System                          | 17 |

| 2.4.2   | Direct Memory Access Controller                    |    |

| 2.4.3   | System Timer                                       |    |

| 2.4.4   | System Control Unit                                |    |

| 2.4.4.1 | Clock Generation Unit                              | 21 |

| 2.4.4.2 | Features of the Watchdog Timer                     |    |

| 2.4.4.3 | Reset Operation                                    |    |

| 2.4.4.4 | External Interface                                 |    |

| 2.4.5   | General Purpose I/O Ports and Peripheral I/O Lines | 23 |

| 2.4.6   | Program Memory Unit (PMU)                          |    |

| 2.4.6.1 | Boot ROM                                           |    |

| 2.4.6.2 | Overlay RAM and Data Acquisition                   | 24 |

| 2.4.6.3 | Emulation Memory Interface                         |    |

| 2.4.6.4 | Tuning Protection                                  |    |

| 2.4.6.5 | Program and Data Flash                             | 25 |

| 2.4.7   | Data Access Overlay                                | 29 |

| 2.4.8   | TC1736 Development Support                         | 30 |

| 2.5     | On-Chip Peripheral Units                           |    |

| 2.5.1   | Asynchronous/Synchronous Serial Interfaces         | 32 |

| 2.5.2   | High-Speed Synchronous Serial Interfaces           | 34 |

| 2.5.3   | Micro Second Channel Interface                     | 36 |

| 2.5.4   | MultiCAN Controller                                | 38 |

| 2.5.5   | Micro Link Interface                               | 41 |

| 2.5.6   | General Purpose Timer Array (GPTAv5)               | 43 |

| 2.5.6.1 | Functionality of GPTA0                             | 44 |

| 2.5.7   | Analog-to-Digital Converter (ADC0, ADC1)           | 46 |

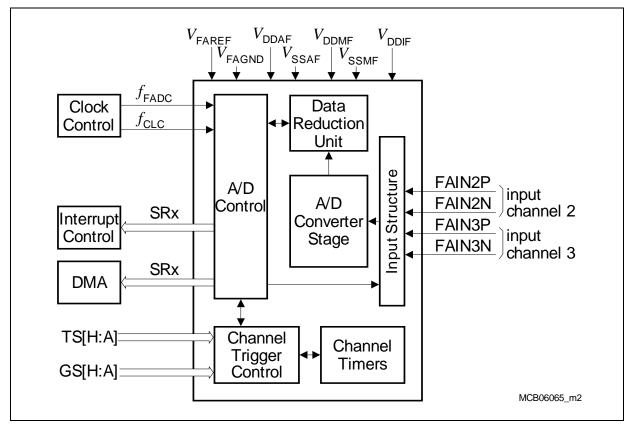

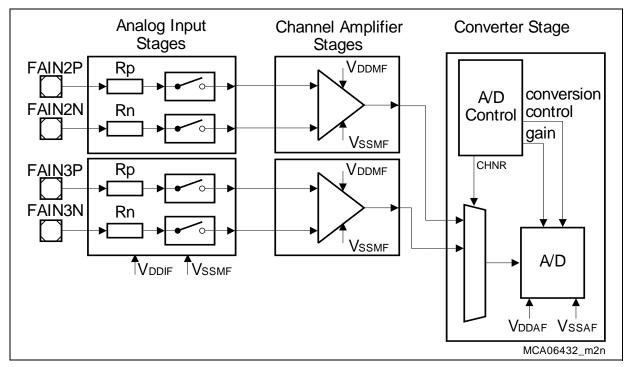

| 2.5.8   | Fast Analog to Digital Converter (FADC)            | 47 |

|  | Tabl | e of | Con | tents |

|--|------|------|-----|-------|

|--|------|------|-----|-------|

| 2.6<br>2.6.1<br>2.6.2<br>2.6.3<br>2.6.4<br>2.6.5<br>2.6.6 | On-Chip Debug Support (OCDS)51On-Chip Debug Support51Real Time Trace51Calibration Support52Tool Interfaces52Self-Test Support53FAR Support53                                                                 |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

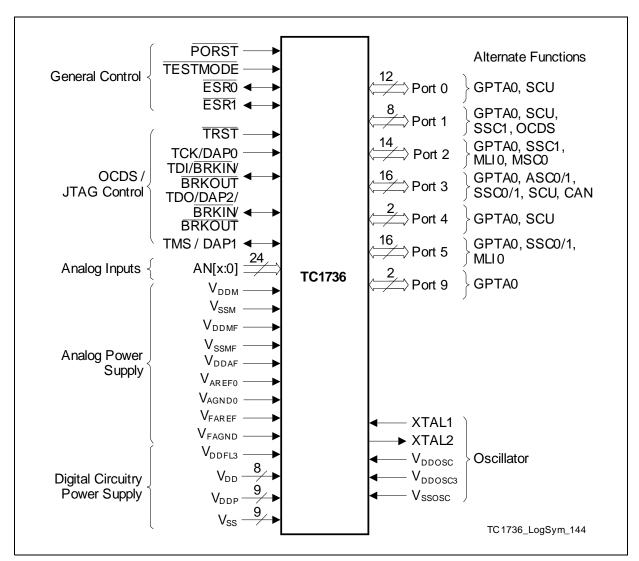

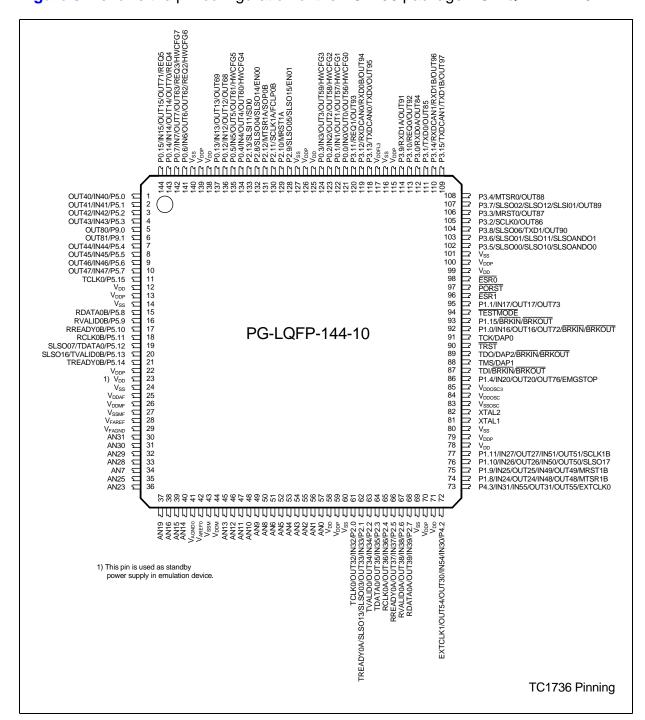

| 3<br>3.1<br>3.1.1<br>3.1.2<br>3.2<br>3.2.1                | Pinning       54         TC1736 Pinning       54         Logic Symbol       54         Pin Configuration       55         Pin Definitions and Functions       56         Reset Behavior of the Pins       73 |

| 4                                                         | Identification Registers                                                                                                                                                                                     |

| <b>5</b><br>5.1                                           | Electrical Parameters                                                                                                                                                                                        |

| 5.1.1<br>5.1.2                                            | General Parameters76Parameter Interpretation76Pad Driver and Pad Classes Summary77                                                                                                                           |

| 5.1.3<br>5.1.4                                            | Absolute Maximum Ratings                                                                                                                                                                                     |

| 5.2<br>5.2.1                                              | DC Parameters                                                                                                                                                                                                |

| 5.2.2                                                     | Analog to Digital Converters (ADC0/ADC1)                                                                                                                                                                     |

| 5.2.3<br>5.2.4                                            | Fast Analog to Digital Converter (FADC)                                                                                                                                                                      |

| 5.2.5<br>5.2.6                                            | Temperature Sensor                                                                                                                                                                                           |

| 5.3                                                       | AC Parameters 97                                                                                                                                                                                             |

| 5.3.1<br>5.3.2                                            | Testing Waveforms                                                                                                                                                                                            |

| 5.3.3                                                     | Power Sequencing                                                                                                                                                                                             |

| 5.3.4<br>5.3.5                                            | Power, Pad and Reset Timing                                                                                                                                                                                  |

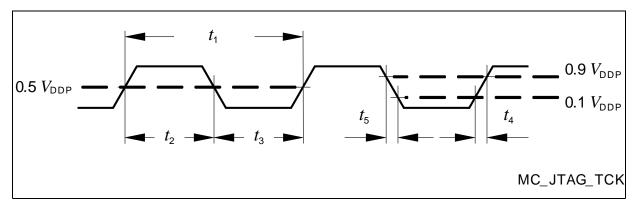

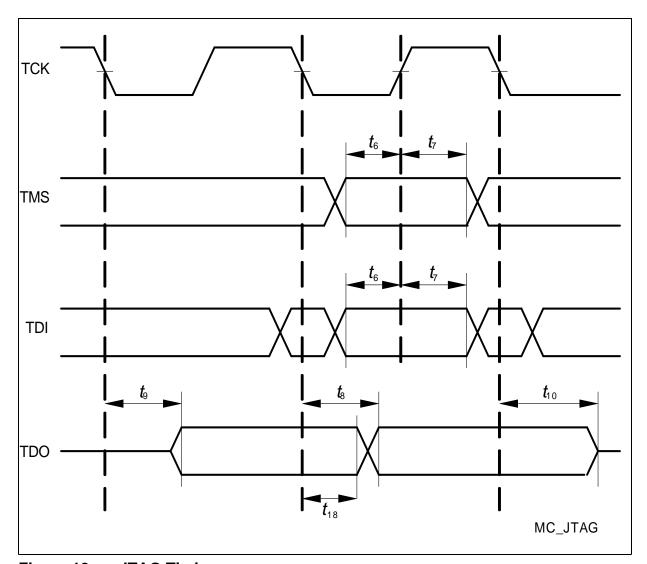

| 5.3.6                                                     | JTAG Interface Timing                                                                                                                                                                                        |

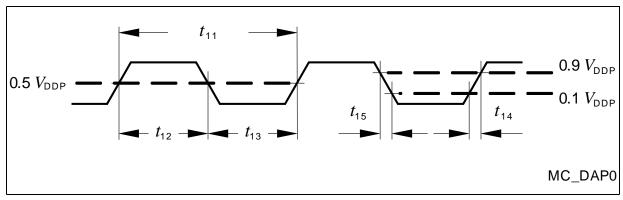

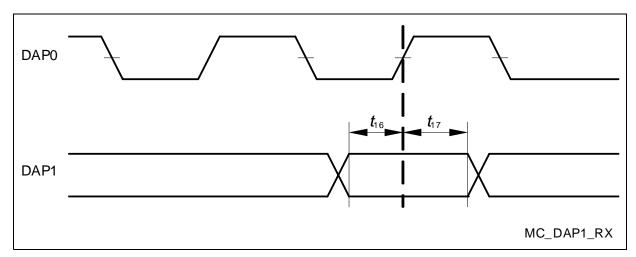

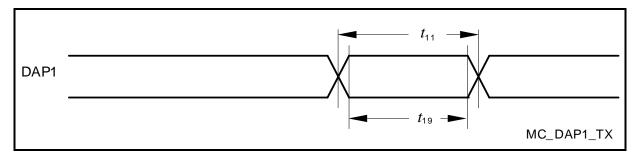

| 5.3.7                                                     | DAP Interface Timing                                                                                                                                                                                         |

| 5.3.8                                                     | Peripheral Timings                                                                                                                                                                                           |

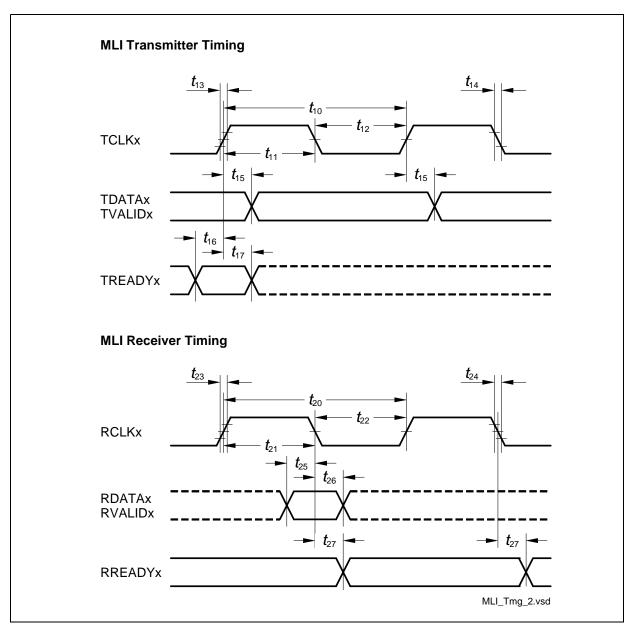

| 5.3.8.1<br>5.3.8.2                                        | Micro Link Interface (MLI) Timing                                                                                                                                                                            |

| 5.3.8.3                                                   | SSC Master / Slave Mode Timing                                                                                                                                                                               |

| 5.4                                                       | Package and Reliability                                                                                                                                                                                      |

| 5.4.1                                                     | Package Parameters                                                                                                                                                                                           |

|     |    |    | _   |     |     |

|-----|----|----|-----|-----|-----|

| Tah | l۵ | Ωf | റ്റ | nte | nte |

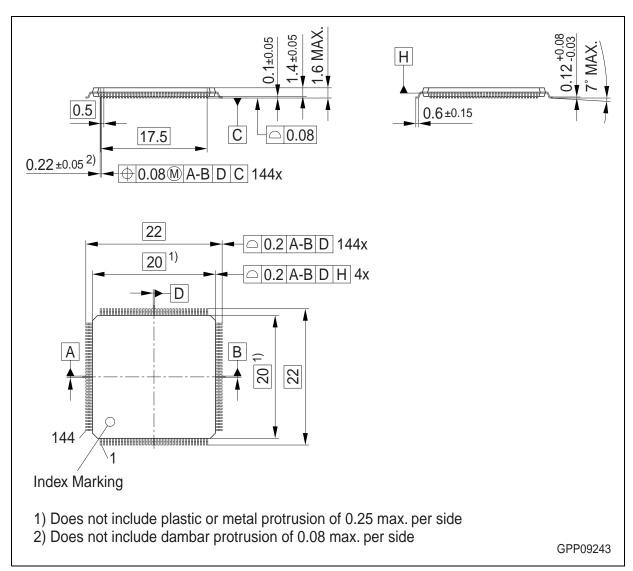

| 5.4.2 | Package Outline         | 116 |

|-------|-------------------------|-----|

| 5.4.3 | Flash Memory Parameters | 117 |

| 5.4.4 | Quality Declarations    | 118 |

## **Summary of Features**

## 1 Summary of Features

- High-performance 32-bit super-scalar TriCore V1.3.1 CPU with 4-stage pipeline

- Superior real-time performance

- Strong bit handling

- Fully integrated DSP capabilities

- Single precision Floating Point Unit (FPU)

- Up to 80 MHz operation at full temperature range

- Multiple on-chip memories

- Up to 36 Kbyte Data Memory (LDRAM)

- 8 Kbyte Code Scratchpad Memory (SPRAM)

- Up to 1 Mbyte Program Flash Memory (PFlash)

- 32 Kbyte Data Flash Memory (DFlash, represents 8Kbyte EEPROM)

- Instruction Cache: up to 8Kbyte (ICACHE, configurable)

- 4 Kbyte Overlay Memory (OVRAM)

- 16 Kbyte BootROM (BROM)

- 8-Channel DMA Controller

- Sophisticated interrupt system with 255 hardware priority arbitration levels serviced by CPU

- High performing on-chip bus structure

- 64-bit Local Memory Buses between CPU, Flash and Data Memory

- 32-bit System Peripheral Bus (SPB) for on-chip peripheral and functional units

- One bus bridges (LFI Bridge)

- Versatile On-chip Peripheral Units

- Two Asynchronous/Synchronous Serial Channels (ASC) with baud rate generator, parity, framing and overrun error detection

- Two High-Speed Synchronous Serial Channels (SSC) with programmable data length and shift direction

- One serial Micro Second Bus interface (MSC) for serial port expansion to external power devices

- One High-Speed Micro Link interface (MLI) for serial inter-processor communication

- One MultiCAN Module with 2CAN nodes and 64 free assignable message objects for high efficiency data handling via FIFO buffering and gateway data transfer

- One General Purpose Timer Array Modules (GPTA) providing a powerful set of digital signal filtering and timer functionality to realize autonomous and complex Input/Output management

- 24 analog input lines for ADC

- 2 independent kernels (ADC0, ADC1)

- Analog supply voltage range from 3.3 V to 5 V (single supply)

- Performance for 12 bit resolution ( $@f_{ADCI} = 10 \text{ MHz}$ )

- 2 different FADC input channels

- Extreme fast conversion, 21 cycles of  $f_{\rm FADC}$  clock (262.5 ns @  $f_{\rm FADC}$  = 80 MHz)

#### **Summary of Features**

- 10-bit A/D conversion (higher resolution can be achieved by averaging of consecutive conversions in digital data reduction filter)

- 70 digital general purpose I/O lines (GPIO), 4 input lines

- Digital I/O ports with 3.3 V capability

- On-chip debug support for OCDS Level 1 (CPU, DMA, On Chip Bus)

- Dedicated Emulation Device chip available (TC1736ED)

- multi-core debugging, real time tracing, and calibration

- four/five wire JTAG (IEEE 1149.1) or two wire DAP (Device Access Port) interface

- Power Management System

- Clock Generation Unit with PLL

- Core supply voltage of 1.5 V

- I/O voltage of 3.3 V

- Full automotive temperature range: -40° to +125°C

- Package variants:

- PG-LQFP-144-10

#### **Summary of Features**

## **Ordering Information**

The ordering code for Infineon microcontrollers provides an exact reference to the required product. This ordering code identifies:

- The derivative itself, i.e. its function set, the temperature range, and the supply voltage

- The package and the type of delivery.

For the available ordering codes for the TC1736 please refer to the "**Product Catalog Microcontrollers**", which summarizes all available microcontroller variants.

This document describes the derivatives of the device. The **Table 1** enumerates these derivatives and summarizes the differences.

Table 1 TC1736 Derivative Synopsis

| Derivative          | Ambient<br>Temperature Range                   | PFlash    | LDRAM    | CPU<br>frequency |

|---------------------|------------------------------------------------|-----------|----------|------------------|

| SAK-TC1736-128F80HL | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ | 1 Mbyte   | 36 Kbyte | 80 MHz           |

| SAK-TC1736-96F40HL  | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ | 768 Kbyte | 32 Kbyte | 40 MHz           |

## 2 Introduction

The TC1736 32-Bit Single-Chip Microcontroller is a cost-optimized version of the TC1767 32-Bit Single-Chip Microcontroller with less pin count and less functionalities. In comparison to the TC1767, the TC1736 provides:

- Less memories in general

- No PCP

- Reduced functionality of the GPTA with less I/Os

- Two CAN nodes only

- Less analog inputs

- Reduced CPU clock frequency

- No LVDS capability for MSC0 output lines

The TC1736 Emulation Device is implemented as a TC1767 emulation device in a QFP-144 package variant.

#### 2.1 About this Document

This document is designed to be read primarily by design engineers and software engineers who need a detailed description of the interactions of the TC1736 functional units, registers, instructions, and exceptions.

This TC1736 Data Sheet describes the features of the TC1736 with respect to the TriCore Architecture. Where the TC1736 directly implements TriCore architectural functions, this manual simply refers to those functions as features of the TC1736. In all cases where this manual describes a TC1736 feature without referring to the TriCore Architecture, this means that the TC1736 is a direct implementation of the TriCore Architecture.

Where the TC1736 implements a subset of TriCore architectural features, this manual describes the TC1736 implementation, and then describes how it differs from the TriCore Architecture. The differences between the TC1736 and the TriCore Architecture are documented in the section for each subject.

#### 2.1.1 Related Documentations

A complete description of the TriCore architecture is found in the document entitled "TriCore Architecture Manual". The architecture of the TC1736 is described separately this way because of the configurable nature of the TriCore specification: Different versions of the architecture may contain a different mix of systems components. The TriCore architecture, however, remains constant across all derivative designs in order to maintain compatibility.

This Data Sheets together with the "TriCore Architecture Manual" are required to understand the complete functionalities of the TC1736 microcontroller.

#### 2.1.2 Text Conventions

This document uses the following text conventions for named components of the TC1736:

- Functional units of the TC1736 are given in plain UPPER CASE. For example: "The SSC supports full-duplex and half-duplex synchronous communication".

- Pins using <u>negative</u> logic are indicated by an overline. For example: "The external reset pin, ESR0, has dual-functionality.".

- fields Bit and bits in registers are in general referenced as "Module Register name.Bit field" or "Module Register name.Bit". For example: "The Current CPU Priority Number bit field CPU\_ICR.CCPN is cleared". Most of the register names contain a module name prefix, separated by an underscore character " " from the actual register name (for example, "ASC0\_CON", where "ASC0" is the module name prefix, and "CON" is the kernel register name). In chapters describing the kernels of the peripheral modules, the registers are mainly referenced with their kernel register names. The peripheral module implementation sections mainly refer to the actual register names with module prefixes.

- Variables used to describe sets of processing units or registers appear in mixed upper and lower cases. For example, register name "MSGCFGn" refers to multiple "MSGCFG" registers with variable n. The boundary of the variables are always given where the register expression is first used (for example, "n = 0-31"), and may be repeated when necessary.

- The default radix is decimal. Hexadecimal constants are suffixed with a subscript letter "H", as in 100<sub>H</sub>. Binary constants are suffixed with a subscript letter "B", as in: 111<sub>B</sub>.

- When the extent of register fields, groups register bits, or groups of pins are

collectively named in the body of the document, they are represented as

"NAME[A:B]", which defines a range for the named group from B to A. Individual bits,

signals, or pins are given as "NAME[C]" where the range of the variable C is given in

the text. For example: CFG[2:0] and SRPN[0].

- Units are abbreviated as follows:

- MHz = Megahertz

- $\mu s = Microseconds$

- kBaud, kbit = 1000 characters/bits per second

- MBaud, Mbit = 1,000,000 characters/bits per second

- **Kbyte**, **KB** = 1024 bytes of memory

- Mbyte, MB = 1048576 bytes of memory

In general, the k prefix scales a unit by 1000 whereas the K prefix scales a unit by 1024. Hence, the Kbyte unit scales the expression preceding it by 1024. The kBaud unit scales the expression preceding it by 1000. The M prefix scales by 1,000,000 or 1048576, and  $\mu$  scales by .000001. For example, 1 Kbyte is 1024 bytes, 1 Mbyte is 1024  $\times$  1024 bytes, 1 kBaud/kbit are 1000 characters/bits

per second, 1 MBaud/Mbit are 1000000 characters/bits per second, and 1 MHz is 1,000,000 Hz.

- Data format quantities are defined as follows:

- Byte = 8-bit quantity

- Half-word = 16-bit quantity

- Word = 32-bit quantity

- Double-word = 64-bit quantity

## 2.1.3 Reserved, Undefined, and Unimplemented Terminology

In tables where register bit fields are defined, the following conventions are used to indicate undefined and unimplemented function. Furthermore, types of bits and bit fields are defined using the abbreviations as shown in **Table 2-1**.

Table 2-1 Bit Function Terminology

| Function of Bits           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Unimplemented,<br>Reserved | <ul> <li>Register bit fields named 0 indicate unimplemented functions with the following behavior.</li> <li>Reading these bit fields returns 0.</li> <li>These bit fields should be written with 0 if the bit field is defined as r or rh.</li> <li>These bit fields have to be written with 0 if the bit field is defined as rw.</li> <li>These bit fields are reserved. The detailed description of these bit fields can be found in the register descriptions.</li> </ul> |

| rw                         | The bit or bit field can be read and written.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| rwh                        | As rw, but bit or bit field can be also set or reset by hardware.                                                                                                                                                                                                                                                                                                                                                                                                            |

| r                          | The bit or bit field can only be read (read-only).                                                                                                                                                                                                                                                                                                                                                                                                                           |

| w                          | The bit or bit field can only be written (write-only). A read to this register will always give a default value back.                                                                                                                                                                                                                                                                                                                                                        |

| rh                         | This bit or bit field can be modified by hardware (read-hardware, typical example: status flags). A read of this bit or bit field give the actual status of this bit or bit field back. Writing to this bit or bit field has no effect to the setting of this bit or bit field.                                                                                                                                                                                              |

**Table 2-1 Bit Function Terminology** (cont'd)

| Function of Bits | Description                                                                                                                                                                                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S                | Bits with this attribute are "sticky" in one direction. If their reset value is once overwritten by software, they can be switched again into their reset state only by a reset operation. Software cannot switch this type of bit into its reset state by writing the register. This attribute can be combined to "rws" or "rwhs". |

| f                | Bits with this attribute are readable only when they are accessed<br>by an instruction fetch. Normal data read operations will return<br>other values.                                                                                                                                                                              |

## 2.1.4 Register Access Modes

Read and write access to registers and memory locations are sometimes restricted. In memory and register access tables, the terms as defined in **Table 2-2** are used.

Table 2-2 Access Terms

| Symbol | Description                                                                                                                                                                                                                        |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U      | Access Mode: Access permitted in User Mode 0 or 1.                                                                                                                                                                                 |

|        | Reset Value: Value or bit is not changed by a reset operation.                                                                                                                                                                     |

| SV     | Access permitted in Supervisor Mode.                                                                                                                                                                                               |

| R      | Read-only register.                                                                                                                                                                                                                |

| 32     | Only 32-bit word accesses are permitted to this register/address range.                                                                                                                                                            |

| E      | Endinit-protected register/address.                                                                                                                                                                                                |

| PW     | Password-protected register/address.                                                                                                                                                                                               |

| NC     | No change, indicated register is not changed.                                                                                                                                                                                      |

| BE     | Indicates that an access to this address range generates a Bus Error.                                                                                                                                                              |

| nBE    | Indicates that no Bus Error is generated when accessing this address range, even though it is either an access to an undefined address or the access does not follow the given rules.                                              |

| nE     | Indicates that no Error is generated when accessing this address or address range, even though the access is to an undefined address or address range. True for CPU accesses (MTCR/MFCR) to undefined addresses in the CSFR range. |

## 2.1.5 Abbreviations and Acronyms

The following acronyms and terms are used in this document:

ADC Analog-to-Digital Converter

AGPR Address General Purpose Register

ALU Arithmetic and Logic Unit

ASC Asynchronous/Synchronous Serial Controller

BCU Bus Control Unit

BROM Boot ROM & Test ROM

CAN Controller Area Network

CISC Complex Instruction Set Computing

CPS CPU Slave Interface

CPU Central Processing Unit

CSA Context Save Area

CSFR Core Special Function Register

DAP Device Access Port

DAS Device Access Server

DFLASH Data Flash Memory

DGPR Data General Purpose Register

DMA Direct Memory Access

DMI Data Memory Interface

ERU External Request Unit

EMI Electro-Magnetic Interference

FADC Fast Analog-to-Digital Converter

FAM Flash Array Module

FCS Flash Command State Machine

FIM Flash Interface and Control Module

FPI Flexible Peripheral Interconnect (Bus)

FPU Floating Point Unit

GPIO General Purpose Input/Output

GPR General Purpose Register

GPTA General Purpose Timer Array

ICACHE Instruction Cache

I/O Input / Output

JTAG Joint Test Action Group = IEEE1149.1

LBCU Local Memory Bus Control Unit

LDRAM Local Data RAM

LFI Local Memory-to-FPI Bus Interface

LMB Local Memory Bus

LTC Local Timer Cell

MLI Micro Link Interface

MMU Memory Management Unit

MSB Most Significant Bit

MSC Micro Second Channel

NC Non-Connected

NMI Non-Maskable Interrupt

OCDS On-Chip Debug Support

OVRAM Overlay Memory

PMU Program Memory Unit

PLL Phase Locked Loop

PFLASH Program Flash Memory

PMI Program Memory Interface

PMU Program Memory Unit

RAM Random Access Memory

RISC Reduced Instruction Set Computing SBCU System Peripheral Bus Control Unit

SCU System Control Unit

SFR Special Function Register

SPB System Peripheral Bus

SPRAM Scratch-Pad RAM

SRAM Static Data Memory

SRN Service Request Node

SSC Synchronous Serial Controller

STM System Timer

WDT Watchdog Timer

## 2.2 System Architecture of the TC1736

The TC1736 combines three powerful technologies within one silicon die, achieving new levels of power, speed, and economy for embedded applications:

- Reduced Instruction Set Computing (RISC) processor architecture

- Digital Signal Processing (DSP) operations and addressing modes

- On-chip memories and peripherals

DSP operations and addressing modes provide the computational power necessary to efficiently analyze complex real-world signals. The RISC load/store architecture provides high computational bandwidth with low system cost. On-chip memory and peripherals are designed to support even the most demanding high-bandwidth real-time embedded control-systems tasks.

## Additional High-level features of the TC1736 include:

- Program Memory Unit instruction memory and instruction cache

- Serial communication interfaces flexible synchronous and asynchronous modes

- DMA Controller DMA operations and interrupt servicing

- General-purpose timers

- High-performance on-chip buses

- On-chip debugging and emulation facilities

- Flexible interconnections to external components

- Flexible power-management

#### **System Features**

- Maximum CPU clock frequency: 80 MHz

- Maximum System Peripheral Bus frequency: 80 MHz

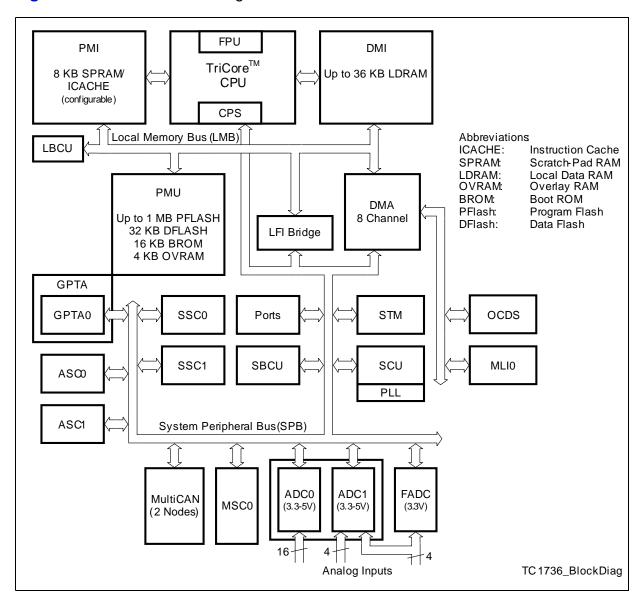

The TC1736 is a high-performance microcontroller with TriCore CPU, program and data memories, buses, bus arbitration, an interrupt controller, a DMA controller and several on-chip peripherals. The TC1736 is designed to meet the needs of the most demanding embedded control systems applications where the competing issues of price/performance, real-time responsiveness, computational power, data bandwidth, and power consumption are key design elements.

The TC1736 offers several versatile on-chip peripheral units such as serial controllers, timer units, and Analog-to-Digital converters. Within the TC1736, all these peripheral units are connected to the TriCore CPU/system via the System Peripheral Bus (SPB) and the Local Memory Bus (LMB). Several I/O lines on the TC1736 ports are reserved for these peripheral units to communicate with the external world.

## 2.2.1 Block Diagram

Figure 2-1 shows the block diagram of the TC1736.

Figure 2-1 TC1736 Block Diagram

## 2.2.2 System Features of the TC1736 device

The TC1736 has the following features:

## **Packages**

• PG-LQFP-144-10 package, 0.5 mm pitch

## **Clock Frequencies**

- Maximum CPU clock frequency: 80 MHz

- Maximum SPB clock frequency: 80 MHz

## 2.3 High-Performance 32-Bit TriCore CPU

## TriCore (TC1.3.1) Architectural Highlights

- Unified RISC MCU/DSP

- 32-bit architecture with 4 Gbytes unified data, program, and input/output address space

- Fast automatic context-switching

- Multiply-accumulate unit

- Floating point unit

- Saturating integer arithmetic

- High-performance on-chip peripheral bus (FPI Bus)

- Register based design with multiple variable register banks

- Bit handling

- Packed data operations

- Zero overhead loop

- Precise exceptions

- Flexible power management

## **High-Efficiency TriCore Instruction Set**

- 16/32-bit instructions for reduced code size

- Data types include: Boolean, array of bits, character, signed and unsigned integer, integer with saturation, signed fraction, double-word integers, and IEEE-754 singleprecision floating point

- Data formats include: Bit, 8-bit byte, 16-bit half-word, 32-bit word, and 64-bit doubleword data formats

- Powerful instruction set

- Flexible and efficient addressing mode for high code density

#### **Integrated CPU related On-Chip Memories**

- 8 KB instruction memory

- configurable as SPRAM and ICACHE in 4 KB granularity

- Up to 36 KB data memory (LDRAM)

- On-chip SRAMs with parity error detection

## 2.4 On-Chip System Units

The TC1736 32-Bit Single-Chip Microcontroller offers several versatile on-chip system peripheral units such as DMA controller, embedded Flash module, interrupt system and ports.

## 2.4.1 Flexible Interrupt System

The TC1736 includes a programmable interrupt system with the following features:

#### **Features**

- Fast interrupt response

- Hardware arbitration

- Programmable service request nodes (SRNs)

- Flexible interrupt-prioritizing scheme with 255 interrupt priority levels per SRN to choose from

- Each SRN is mapped to the CPU interrupt system

## 2.4.2 Direct Memory Access Controller

The TC1736 includes a fast and flexible DMA controller with 8 independent DMA channels (one DMA engine).

#### **Features**

- independent DMA channels

- Up to 16 selectable request inputs per DMA channel

- 2-level programmable priority of DMA channels within the DMA Sub-Block

- Software and hardware DMA request

- Hardware requests by selected on-chip peripherals and external inputs

- 3-level programmable priority of the DMA Sub-Block at the on-chip bus interfaces

- Buffer capability for move actions on the buses (at least 1 move per bus is buffered)

- Individually programmable operation modes for each DMA channel

- Single Mode: stops and disables DMA channel after a predefined number of DMA transfers

- Continuous Mode: DMA channel remains enabled after a predefined number of DMA transfers; DMA transaction can be repeated

- Programmable address modification

- Two shadow register modes (with or without automatic re-set and direct write access).

- Full 32-bit addressing capability of each DMA channel

- 4 Gbyte address range

- Data block move supports > 32 Kbyte per DMA transaction

- Circular buffer addressing mode with flexible circular buffer sizes

- Programmable data width of DMA transfer/transaction: 8-bit, 16-bit, or 32-bit

- Register set for each DMA channel

- Source and destination address register

- Channel control and status register

- Transfer count register

- Flexible interrupt generation (the service request node logic for the MLI channel is also implemented in the DMA module)

- DMA module is working on FPI frequency, LMB interface on LMB frequency.

- Dependant on the target/destination address, Read/write requests from the Move Engine are directed to the FPI, LMB, MLI or to the the Cerberus.

## 2.4.3 System Timer

The TC1736's STM is designed for global system timing applications requiring both high precision and long range.

#### **Features**

- Free-running 56-bit counter

- All 56 bits can be read synchronously

- Different 32-bit portions of the 56-bit counter can be read synchronously

- Flexible interrupt generation based on compare match with partial STM content

- Driven by maximum 80 MHz (=  $f_{SYS}$ , default after reset =  $f_{SYS}$ /2)

- Counting starts automatically after a reset operation

- STM registers are reset by an application reset if bit ARSTDIS.STMDIS is cleared. If bit ARSTDIS.STMDIS is set, the STM registers are not reset.<sup>1)</sup>.

- STM can be halted in debug/suspend mode

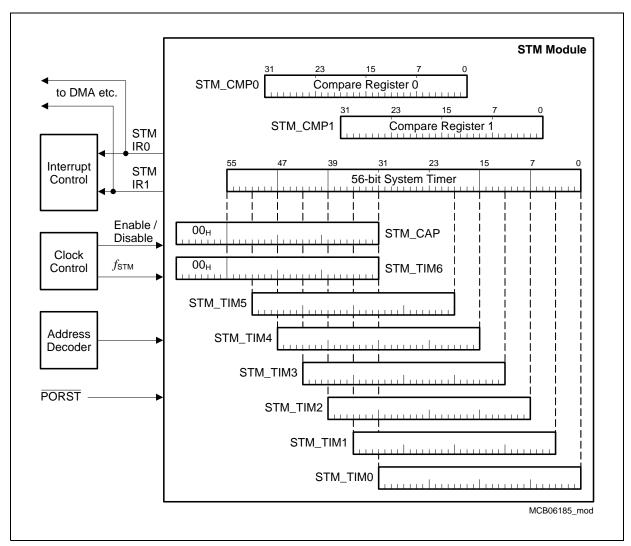

Special STM register semantics provide synchronous views of the entire 56-bit counter, or 32-bit subsets at different levels of resolution.

The maximum clock period is  $2^{56} \times f_{\text{STM}}$ . At  $f_{\text{STM}}$  = 80 MHz, for example, the STM counts 28.56 years before overflowing. Thus, it is capable of continuously timing the entire expected product life time of a system without overflowing.

The STM can be optionally disabled for power-saving purposes, or suspended for debugging purposes via its clock control register. In suspend mode of the TC1736 (initiated by writing an appropriate value to STM\_CLC register), the STM clock is stopped but all registers are still readable.

Due to the 56-bit width of the STM, it is not possible to read its entire content with one instruction. It needs to be read with two load instructions. Since the timer would continue to count between the two load operations, there is a chance that the two values read are not consistent (due to possible overflow from the low part of the timer to the high part between the two read operations). To enable a synchronous and consistent reading of the STM content, a capture register (STM\_CAP) is implemented. It latches the content of the high part of the STM each time when one of the registers STM\_TIM0 to STM\_TIM5 is read. Thus, STM\_CAP holds the upper value of the timer at exactly the same time when the lower part is read. The second read operation would then read the content of the STM\_CAP to get the complete timer value.

The STM can also be read in sections from seven registers, STM\_TIM0 through STM\_TIM6, that select increasingly higher-order 32-bit ranges of the STM. These can be viewed as individual 32-bit timers, each with a different resolution and timing range.

The content of the 56-bit System Timer can be compared against the content of two compare values stored in the STM\_CMP0 and STM\_CMP1 registers. Service requests

<sup>1) &</sup>quot;STM registers" means all registers except STM\_CLC, STM\_SRC0, and STM\_SRC1.

can be generated on a compare match of the STM with the STM\_CMP0 or STM\_CMP1 registers.

**Figure 2-2** provides an overview on the STM module. It shows the options for reading parts of STM content.

Figure 2-2 General Block Diagram of the STM Module Registers

## 2.4.4 System Control Unit

The following SCU introduction gives an overview about the TC1736 System Control Unit (SCU).

#### 2.4.4.1 Clock Generation Unit

The Clock Generation Unit (CGU) allows a very flexible clock generation for the TC1736. During user program execution the frequency can be programmed for an optimal ratio between performance and power consumption.

## 2.4.4.2 Features of the Watchdog Timer

The main features of the WDT are summarized here.

- 16-bit Watchdog counter

- Selectable input frequency:  $f_{\text{FPI}}/256 \text{ or } f_{\text{FPI}}/16384$

- 16-bit user-definable reload value for normal Watchdog operation, fixed reload value for Time-Out and Prewarning Modes

- Incorporation of the ENDINIT bit and monitoring of its modifications

- Sophisticated Password Access mechanism with fixed and user-definable password fields

- Access Error Detection: Invalid password (during first access) or invalid guard bits (during second access) trigger the Watchdog reset generation

- Overflow Error Detection: An overflow of the counter triggers the Watchdog reset generation

- Watchdog function can be disabled; access protection and ENDINIT monitor function remain enabled

- Double Reset Detection: If a Watchdog induced reset occurs twice, a severe system malfunction is assumed and the TC1736 is held in reset until a system / class 0 reset occurs.

## 2.4.4.3 Reset Operation

The following reset request triggers are available:

- 1 External power-on hardware reset request trigger; PORST, (cold reset)

- 2 External System Request reset triggers; ESR0 and ESR1 (warm reset)

- Watchdog Timer (WDT) reset request trigger, (warm reset)

- Software reset (SW), (warm reset)

- Debug (OCDS) reset request trigger, (warm reset)

- JTAG reset (special reset)

There are two basic types of reset request triggers:

- Trigger sources that do not depend on a clock, such as the PORST. This trigger force

the device into an asynchronous reset assertion independently of any clock. The

activation of an asynchronous reset is asynchronous to the system clock, whereas

its de-assertion is synchronized.

- <u>Trigger</u> sources that need a clock in order to be asserted, such as the input signals ESR0 and ESR1, the WDT trigger, the parity trigger, or the SW trigger.

#### 2.4.4.4 External Interface

The SCU provides interface pads for system purpose. Various functions are covered by these pins. Due to the different tasks some of the pads can not be shared with other functions but most of them can be shared with other functions. The following functions are covered by the SCU controlled pads:

- Reset request triggers

- Reset indication

- Trap request triggers

- Interrupt request triggers

- Non SCU module triggers

The first three points are covered by the ESR pads and the last two points by the ERU pads.

## 2.4.5 General Purpose I/O Ports and Peripheral I/O Lines

The TC1736 includes a flexible Ports structure with the following features:

#### **Features**

- 70 digital General-Purpose Input/Output (GPIO) port lines

- Input/output functionality individually programmable for each port line

- Programmable input characteristics (pull-up, pull-down, no pull device)

- Programmable output driver strength for EMI minimization (weak, medium, strong)

- Programmable output characteristics (push-pull, open drain)

- Programmable alternate output functions

- Output lines of each port can be updated port-wise or set/reset/toggled bit-wise

## 2.4.6 Program Memory Unit (PMU)

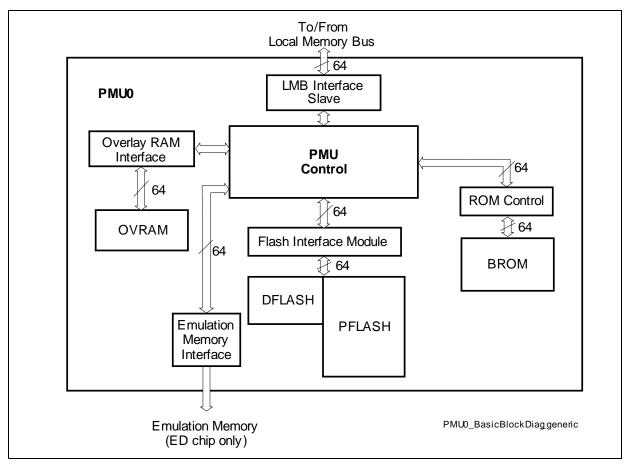

The devices of the AudoF family contain at least one Program Memory Unit. This is named "PMU0". Some devices contain additional PMUs which are named "PMU1", ...

In the TC1736, the PMU0 contains the following submodules:

- The Flash command and fetch control interface for Program Flash and Data Flash.

- The Overlay RAM interface with Online Data Acquisition (OLDA) support.

- The Boot ROM interface.

- The Emulation Memory interface.

- The Local Memory Bus LMB slave interface.

Following memories are controlled by and belong to the PMU0:

- 1 Mbyte of Program Flash memory (PFlash)

- 32 Kbyte of Data Flash memory (DFlash, represents 8 Kbyte EEPROM)

- 16 Kbyte of Boot ROM (BROM)

- 4 Kbyte Overlay RAM (OVRAM)

The following figure shows the block diagram of the PMU0:

Figure 2-3 PMU0 Basic Block Diagram

#### 2.4.6.1 Boot ROM

The internal 16 Kbyte Boot ROM (BROM) is divided into two parts, used for:

- firmware (Boot ROM), and

- factory test routines (Test ROM).

The different sections of the firmware in Boot ROM provide startup and boot operations after reset. The TestROM is reserved for special routines, which are used for testing, stressing and qualification of the component.

## 2.4.6.2 Overlay RAM and Data Acquisition

The overlay memory OVRAM is provided in the PMU especially for redirection of data accesses to program memory to the OVRAM by using the data overlay function. The data overlay functionality itself is controlled in the DMI module.

For online data acquisition (OLDA) of application or calibration data a virtual 32 KB memory range is provided which can be accessed without error reporting. Accesses to this OLDA range can also be redirected to an overlay memory.

## 2.4.6.3 Emulation Memory Interface

In TC1736 Emulation Device, an Emulation Memory (EMEM) is provided, which can fully be used for calibration via program memory or OLDA overlay. The Emulation Memory interface shown in **Figure 2-3** is a 64-bit wide memory interface that controls the CPU-accesses to the Emulation Memory in the TC1736 Emulation Device. In the TC1736 production device, the EMEM interface is always disabled.

## 2.4.6.4 Tuning Protection

Tuning protection is required by the user to absolutely protect control data (e.g. for engine control), serial number and user software, stored in the Flash, from being manipulated, and to safely detect changed or disturbed data. For the internal Flash, these protection requirements are excellently fulfilled in the TC1736 with

- Flash read and write protection with user-specific protection levels, and with

- dedicated HW and firmware, supporting the internal Flash read protection, and with

- the Alternate Boot Mode.

Special tuning protection support is provided for external Flash, which must also be protected.

## 2.4.6.5 Program and Data Flash

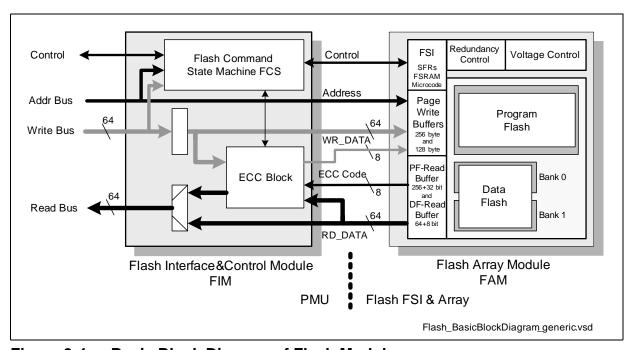

The embedded Flash modules of PMU0 includes 1 Mbyte of Flash memory for code or constant data (called Program Flash) and additionally 32 Kbyte of Flash memory used for emulation of EEPROM data (called Data Flash). The Program Flash is realized as one independent Flash bank, whereas the Data Flash is built of two Flash banks, allowing the following combinations of concurrent Flash operations:

- Read code or data from Program Flash, while one bank of Data Flash is busy with a program or erase operation.

- Read data from one bank of Data Flash, while the other bank of Data Flash is busy with a program or erase operation.

- Program one bank of Data Flash while erasing the other bank of Data Flash, read from Program Flash.

Both, the Program Flash and the Data Flash, provide error correction of single-bit errors within a 64-bit read double-word, resulting in an extremely low failure rate. Read accesses to Program Flash are executed in 256-bit width, to Data Flash in 64-bit width (both plus ECC). Single-cycle burst transfers of up to 4 double-words and sequential prefetching with control of prefetch hit are supported for Program Flash.

The minimum programming width is the page, including 256 bytes in Program Flash and 128 bytes in Data Flash. Concurrent programming and erasing in Data Flash is performed using an automatic erase suspend and resume function.

A basic block diagram of the Flash Module is shown in the following figure.

Figure 2-4 Basic Block Diagram of Flash Module

All Flash operations are controlled simply by transferring command sequences to the Flash which are based on JEDEC standard. This user interface of the embedded Flash is very comfortable, because all operations are controlled with high level commands, such as "Erase Sector". State transitions, such as termination of command execution, or errors are reported to the user by maskable interrupts. Command sequences are normally written to Flash by the CPU, but may also be issued by the DMA controller (or OCDS).

The Flash also features an advanced read/write protection architecture, including a read protection for the whole Flash array (optionally without Data Flash) and separate write protection for all sectors (only Program Flash). Write protected sectors can be made reprogrammable (enabled with passwords), or they can be locked for ever (ROM function). Each sector can be assigned to up to three different users for write protection. The different users are organized hierarchically.

## **Program Flash Features and Functions**

- 1 Mbyte on-chip Program Flash in PMU0.

- Any use for instruction code or constant data.

- 256 bit read interface (burst transfer operation).

- Dynamic correction of single-bit errors during read access.

- Transfer rate in burst mode: One 64-bit double-word per clock cycle.

- Sector architecture:

- Eight 16 Kbyte, one 128 Kbyte and three 256 Kbyte sectors.

- Each sector separately erasable.

- Each sector lockable for protection against erase and program (write protection).

- One additional configuration sector (not accessible to the user).

- Optional read protection for whole Flash, with sophisticated read access supervision.

Combined with whole Flash write protection thus supporting protection against Trojan horse programs.

- Sector specific write protection with support of re-programmability or locked forever.

- Comfortable password checking for temporary disable of write or read protection.

- User controlled configuration blocks (UCB) in configuration sector for keywords and for sector-specific lock bits (one block for every user; up to three users).

- Pad supply voltage (V<sub>DDP</sub>) also used for program and erase (no VPP pin).

- Efficient 256 byte page program operation.

- All Flash operations controlled by CPU per command sequences (unlock sequences) for protection against unintended operation.

- End-of-busy as well as error reporting with interrupt and bus error trap.

- Write state machine for automatic program and erase, including verification of operation quality.

- Support of margin check.

- Delivery in erased state (read all zeros).

- Global and sector status information.

- Overlay support with SRAM for calibration applications.

- Configurable wait state selection for different CPU frequencies.

- Endurance = 1000; minimum 1000 program/erase cycles per physical sector; reduced endurance of 100 per 16 KB sector.

- Operating lifetime (incl. Retention): 20 years with endurance=1000.

- For further operating conditions see data sheet section "Flash Memory Parameters".

#### **Data Flash Features and Functions**

- 32 Kbyte on-chip Flash, configured in two independent Flash banks of equal size.

- 64 bit read interface.

- Erase/program one bank while data read access from the other bank.

- Programming one bank while erasing the other bank using an automatic suspend/resume function.

- Dynamic correction of single-bit errors during read access.

- Sector architecture:

- Two sectors of equal size.

- Each sector separately erasable.

- 128 byte pages to be written in one step.

- Operational control per command sequences (unlock sequences, same as those of Program Flash) for protection against unintended operation.

- End-of-busy as well as error reporting with interrupt and bus error trap.

- Write state machine for automatic program and erase.

- Margin check for detection of problematic Flash bits.

- Endurance = 30000 (can be device dependent); i.e. 30000 program/erase cycles per sector are allowed, with a retention of min. 5 years.

- Dedicated DFlash status information.

- Other characteristics: Same as Program Flash.

## 2.4.7 Data Access Overlay

The data overlay functionality provides the capability to redirect data accesses by the TriCore to program memory (internal Program Flash or external memory) to the Overlay SRAM in the PMU, or to the Emulation Memory in Emulation Device ED. This functionality makes it possible, for example, to modify the application's test and calibration parameters (which are typically stored in the program memory) during run time of a program. Note that read and write data accesses from/to program memory are redirected.

Attention: As the address translation is implemented in the DMI, it is only effective for data accesses by the TriCore. Instruction fetches by the TriCore or accesses by any other master (including the debug interface) are not affected!

## **Summary of Features and Functions**

- 16 overlay ranges ("blocks") configurable for Program Flash and external memory

- Support of 4 Kbyte embedded Overlay SRAM (OVRAM) in PMU

- Support of up to 256 Kbyte overlay/calibration memory in Emulation Device (EMEM)

- Support of Online Data Acquisition into range of up to 32 KB and of its overlay

- Support of different overlay memory selections for every enabled overlay block

- Sizes of overlay blocks selectable from 16 byte to 2 Kbyte for redirection to OVRAM

- Sizes of overlay blocks selectable from 1 Kbyte to 128 Kbyte for redirection to EMEM

- All configured overlay ranges can be enabled with only one register write access

## 2.4.8 TC1736 Development Support

Overview about the TC1736 development environment:

## **Complete Development Support**

A variety of software and hardware development tools for the 32-bit microcontroller TC1736 are available from experienced international tool suppliers. The development environment for the Infineon 32-bit microcontroller includes the following tools:

- Embedded Development Environment for TriCore Products

- The TC1736 On-chip Debug Support (OCDS) provides a JTAG port for communication between external hardware and the system

- The System Timer (STM) with high-precision, long-range timing capabilities

- The TC1736 includes a power management system, a watchdog timer as well as reset logic

## 2.5 On-Chip Peripheral Units

The TC1736 micro controller offers several versatile on-chip peripheral units such as serial controllers, timer units, and Analog-to-Digital converters. Several I/O lines on the TC1736 ports are reserved for these peripheral units to communicate with the external world.

## **On-Chip Peripheral Units**

- Two Asynchronous/Synchronous Serial Channels (ASC0, ASC1) with baud rate generator, parity, framing and overrun error detection

- Two Synchronous Serial Channels (SSC0, SSC1) with programmable data length and shift direction

- One Micro Second Bus Interface (MSC0) for serial communication

- One CAN Module with two CAN nodes (MultiCAN) for high-efficiency data handling via FIFO buffering and gateway data transfer

- One Micro Link Serial Bus Interfaces (MLI0) for serial multiprocessor communication

- One General Purpose Timer Array (GPTA0) with a powerful set of digital signal filtering and timer functionality to accomplish autonomous and complex Input/Output management

- Two Analog-to-Digital Converter Units (ADC0, ADC1) with 8-bit, 10-bit, or 12-bit resolution.

- One fast Analog-to-Digital Converter Unit (FADC)

## 2.5.1 Asynchronous/Synchronous Serial Interfaces

The TC1736 includes two Asynchronous/Synchronous Serial Interfaces, ASC0 and ASC1. Both ASC modules have the same functionality.

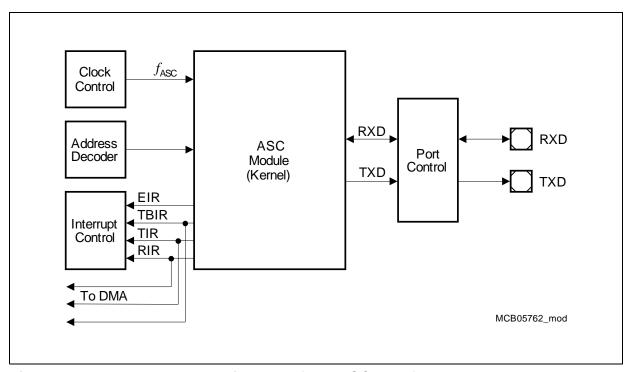

Figure 2-5 shows a global view of the Asynchronous/Synchronous Serial Interface (ASC).

Figure 2-5 General Block Diagram of the ASC Interface

The ASC provides serial communication between the TC1736 and other microcontrollers, microprocessors, or external peripherals.

The ASC supports full-duplex asynchronous communication and half-duplex synchronous communication. In Synchronous Mode, data is transmitted or received synchronous to a shift clock that is generated by the ASC internally. In Asynchronous Mode, 8-bit or 9-bit data transfer, parity generation, and the number of stop bits can be selected. Parity, framing, and overrun error detection are provided to increase the reliability of data transfers. Transmission and reception of data is double-buffered. For multiprocessor communication, a mechanism is included to distinguish address bytes from data bytes. Testing is supported by a loop-back option. A 13-bit baud rate generator provides the ASC with a separate serial clock signal, which can be accurately adjusted by a prescaler implemented as fractional divider.

#### **Features**

- Full-duplex asynchronous operating modes

- 8-bit or 9-bit data frames, LSB first

- Parity-bit generation/checking

- One or two stop bits

- Baud rate from 5.0 Mbit/s to 1.19 bit/s (@ 80 MHz module clock)

- Multiprocessor mode for automatic address/data byte detection

- Loop-back capability

- Half-duplex 8-bit synchronous operating mode

- Baud rate from 10.0 Mbit/s to 813.8 bit/s (@ 80 MHz module clock)

- Double-buffered transmitter/receiver

- Interrupt generation

- On a transmit buffer empty condition

- On a transmit last bit of a frame condition

- On a receive buffer full condition

- On an error condition (frame, parity, overrun error)

- Implementation features

- Connections to DMA Controller

- Connections of receiver input to GPTA (LTC) for baud rate detection and LIN break signal measuring

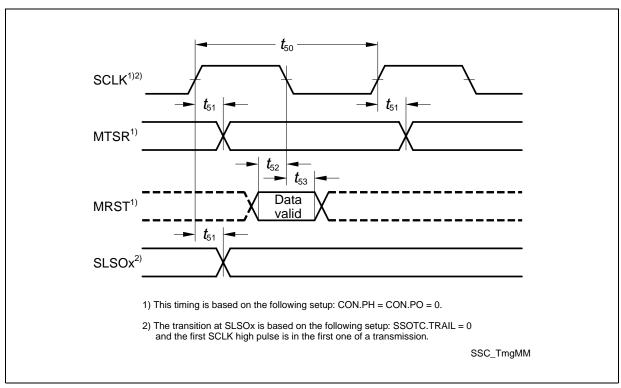

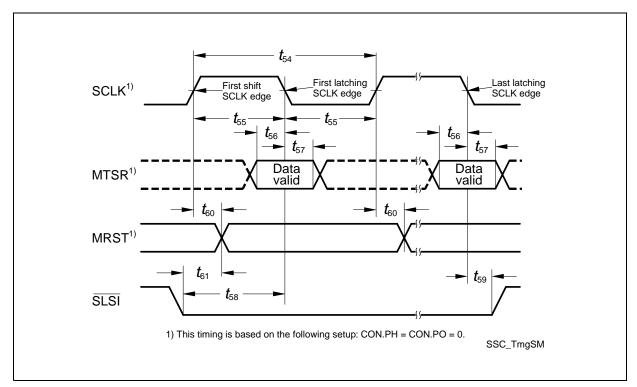

## 2.5.2 High-Speed Synchronous Serial Interfaces

The TC1736 includes two High-Speed Synchronous Serial Interfaces, SSC0 and SSC1. Both SSC modules have the same functionality.

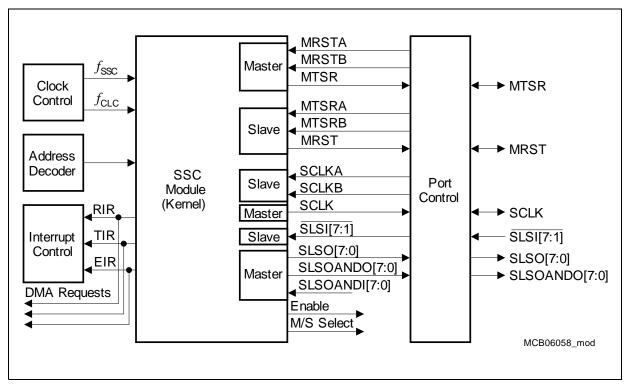

Figure 2-6 shows a global view of the Synchronous Serial interface (SSC).

Figure 2-6 General Block Diagram of the SSC Interface

The SSC supports full-duplex and half-duplex serial synchronous communication up to 40 Mbit/s (@ 80 MHz module clock, Master Mode). The serial clock signal can be generated by the SSC itself (Master Mode) or can be received from an external master (Slave Mode). Data width, shift direction, clock polarity and phase are programmable. This allows communication with SPI-compatible devices. Transmission and reception of data are double-buffered. A shift clock generator provides the SSC with a separate serial clock signal. One slave select input is available for slave mode operation. Eight programmable slave select outputs (chip selects) are supported in Master Mode.

#### **Features**

- Master and Slave Mode operation

- Full-duplex or half-duplex operation

- Automatic pad control possible

- Flexible data format

- Programmable number of data bits: 2 to 16 bits

- Programmable shift direction: LSB or MSB shift first

- Programmable clock polarity: Idle low or idle high state for the shift clock

- Programmable clock/data phase: Data shift with leading or trailing edge of the shift clock

- Baud rate generation

- Master Mode: 40.0 Mbit/s to 610.36 bit/s (@ 80 MHz module clock)

- Slave Mode: 20 Mbit/s to 610.36 bit/s (@ 80 MHz module clock)

- Interrupt generation

- On a transmitter empty condition

- On a receiver full condition

- On an error condition (receive, phase, baud rate, transmit error)

- Flexible SSC pin configuration

- Seven slave select inputs SLSI[7:1] in Slave Mode

- Eight programmable slave select outputs SLSO in Master Mode

- Automatic SLSO generation with programmable timing

- Programmable active level and enable control

- Combinable with SLSO output signals from other SSC modules

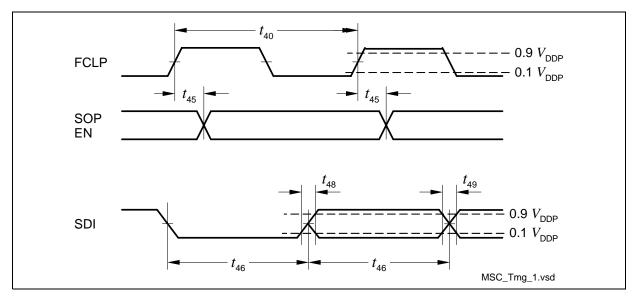

### 2.5.3 Micro Second Channel Interface

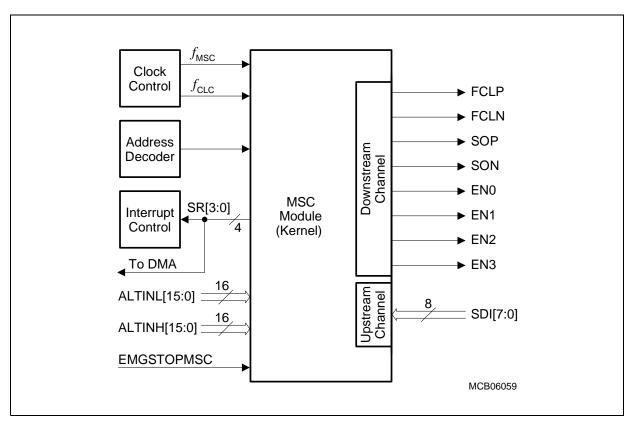

The Micro Second Channel (MSC) interface provides serial communication links typically used to connect power switches or other peripheral devices. The serial communication link includes a fast synchronous downstream channel and a slow asynchronous upstream channel. **Figure 2-7** shows a global view of the interface signals of the MSC interface.

Figure 2-7 General Block Diagram of the MSC Interface

The downstream and upstream channels of the MSC module communicate with the external world via nine I/O lines. Eight output lines are required for the serial communication of the downstream channel (clock, data, and enable signals). One out of eight input lines SDI[7:0] is used as serial data input signal for the upstream channel. The source of the serial data to be transmitted by the downstream channel can be MSC register contents or data that is provided on the ALTINL/ALTINH input lines. These input lines are typically connected with other on-chip peripheral units (for example with a timer unit such as the GPTA). An emergency stop input signal makes it possible to set bits of the serial data stream to dedicated values in an emergency case.

Clock control, address decoding, and interrupt service request control are managed outside the MSC module kernel. Service request outputs are able to trigger an interrupt or a DMA request.

#### **Features**

- Fast synchronous serial interface to connect power switches in particular, or other peripheral devices via serial buses

- High-speed synchronous serial transmission on downstream channel

- Serial output clock frequency:  $f_{FCL} = f_{MSC}/2$  ( $f_{MSCmax} = 80$  MHz)

- Fractional clock divider for precise frequency control of serial clock  $f_{

m MSC}$

- Command, data, and passive frame types

- Start of serial frame: Software-controlled, timer-controlled, or free-running

- Programmable upstream data frame length (16 or 12 bits)

- Transmission with or without SEL bit

- Flexible chip select generation indicates status during serial frame transmission

- Emergency stop without CPU intervention

- Low-speed asynchronous serial reception on upstream channel

- Baud rate:  $f_{MSC}$  divided by 4, 8, 16, 32, 64, 128, or 256 ( $f_{MSCmax}$  = 80 MHz)

- Standard asynchronous serial frames

- Parity error checker

- 8-to-1 input multiplexer for SDI lines

- Built-in spike filter on SDI lines

### 2.5.4 MultiCAN Controller

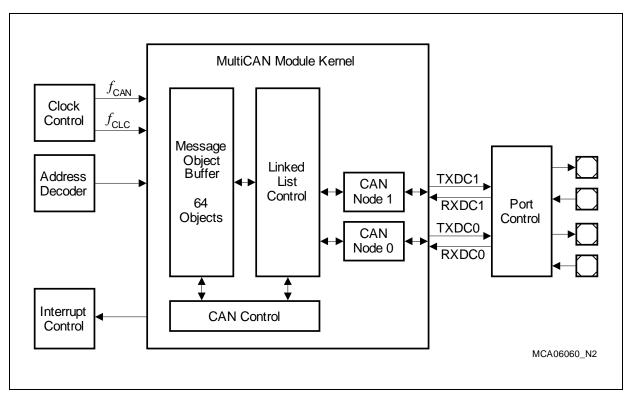

The MultiCAN module provides two independent CAN nodes, representing two serial communication interfaces. The number of available message objects 64.

Figure 2-8 Overview of the MultiCAN Module

The MultiCAN module contains two independently operating CAN nodes with Full-CAN functionality that are able to exchange Data and Remote Frames via a gateway function. Transmission and reception of CAN frames is handled in accordance to CAN specification V2.0 B (active). Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

All two CAN nodes share a common set of message objects. Each message object can be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects can be combined to build gateways between the CAN nodes or to set up a FIFO buffer.

The message objects are organized in double-chained linked lists, where each CAN node has its own list of message objects. A CAN node stores frames only into message objects that are allocated to the message object list of the CAN node, and it transmits only messages belonging to this message object list. A powerful, command-driven list controller performs all message object list operations.

The bit timings for the CAN nodes are derived from the module timer clock ( $f_{CAN}$ ) and are programmable up to a data rate of 1 Mbit/s. External bus transceivers are connected to a CAN node via a pair of receive and transmit pins.

#### **Features**

- Compliant with ISO 11898

- CAN functionality according to CAN specification V2.0 B active

- Dedicated control registers for each CAN node

- Data transfer rates up to 1 Mbit/s

- Flexible and powerful message transfer control and error handling capabilities

- Advanced CAN bus bit timing analysis and baud rate detection for each CAN node via a frame counter

- Full-CAN functionality: A set of 64 message objects can be individually

- Allocated (assigned) to any CAN node

- Configured as transmit or receive object

- Setup to handle frames with 11-bit or 29-bit identifier

- Identified by a timestamp via a frame counter

- Configured to remote monitoring mode

- Advanced Acceptance Filtering

- Each message object provides an individual acceptance mask to filter incoming frames.

- A message object can be configured to accept standard or extended frames or to accept both standard and extended frames.

- Message objects can be grouped into four priority classes for transmission and reception.

- The selection of the message to be transmitted first can be based on frame identifier, IDE bit and RTR bit according to CAN arbitration rules, or on its order in the list.

- Advanced message object functionality

- Message objects can be combined to build FIFO message buffers of arbitrary size, limited only by the total number of message objects.

- Message objects can be linked to form a gateway that automatically transfers frames between 2 different CAN buses. A single gateway can link any two CAN nodes. An arbitrary number of gateways can be defined.

- Advanced data management

- The message objects are organized in double-chained lists.

- List reorganizations can be performed at any time, even during full operation of the CAN nodes.

- A powerful, command-driven list controller manages the organization of the list structure and ensures consistency of the list.

- Message FIFOs are based on the list structure and can easily be scaled in size during CAN operation.

- Static allocation commands offer compatibility with MultiCAN applications that are not list-based.

- Advanced interrupt handling

- Up to 16 interrupt output lines are available. Interrupt requests can be routed individually to one of the 16 interrupt output lines.

- Message post-processing notifications can be combined flexibly into a dedicated register field of 256 notification bits.

### 2.5.5 Micro Link Interface

This TC1736 contains one Micro Link Interface, MLIO.

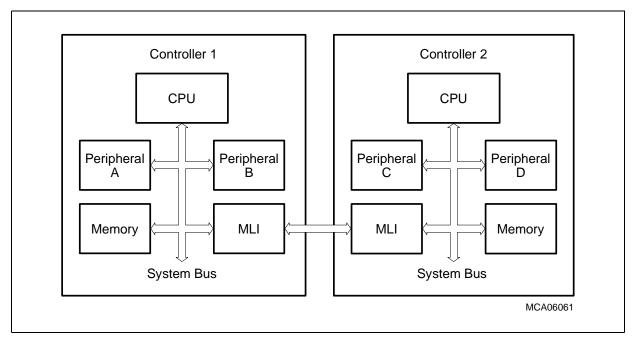

The Micro Link Interface (MLI) is a fast synchronous serial interface to exchange data between microcontrollers or other devices, such as stand-alone peripheral components. Figure 2-9 shows how two microcontrollers are typically connected together via their MLI interfaces.

Figure 2-9 Typical Micro Link Interface Connection

#### **Features**

- Synchronous serial communication between an MLI transmitter and an MLI receiver

- Different system clock speeds supported in MLI transmitter and MLI receiver due to full handshake protocol (4 lines between a transmitter and a receiver)

- Fully transparent read/write access supported (= remote programming)

- Complete address range of target device available

- Specific frame protocol to transfer commands, addresses and data

- Error detection by parity bit

- 32-bit, 16-bit, or 8-bit data transfers supported

- Programmable baud rates

- MLI transmitter baud rate: max.  $f_{\rm MLI}/2$  (= 40 Mbit/s @ 80 MHz module clock)

- MLI receiver baud rate: max.  $f_{\text{MLI}}$

- Address range protection scheme to block unauthorized accesses

- Multiple receiving devices supported

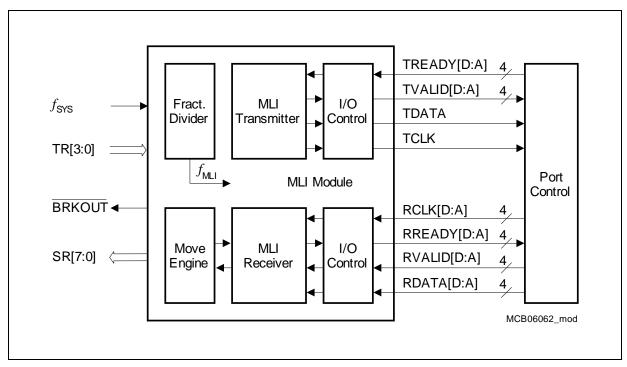

Figure 2-10 shows a general block diagram of the MLI module.

Figure 2-10 General Block Diagram of the MLI Modules

The MLI transmitter and MLI receiver communicate with other MLI receivers and MLI transmitters via a four-line serial connection each. Several I/O lines of these connections are available outside the MLI module kernel as a four-line output or input vector with index numbering A, B, C and D. The MLI module internal I/O control blocks define which signal of a vector is actually taken into account and also allow polarity inversions (to adapt to different physical interconnection means).

## 2.5.6 General Purpose Timer Array (GPTAv5)

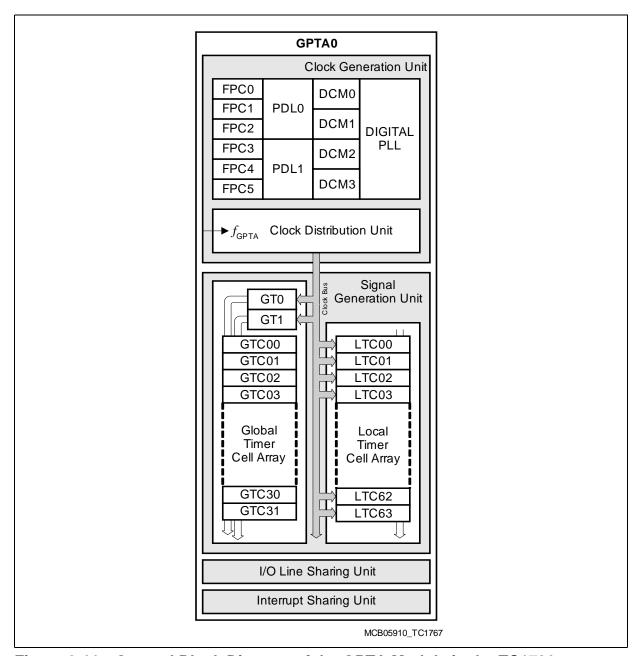

The TC1736 contains the General Purpose Timer Array (GPTA0). **Figure 2-11** shows a global view of the GPTA module.

The GPTA provides a set of timer, compare, and capture functionalities that can be flexibly combined to form signal measurement and signal generation units. They are optimized for tasks typical of engine, gearbox, and electrical motor control applications, but can also be used to generate simple and complex signal waveforms required for other industrial applications.

Figure 2-11 General Block Diagram of the GPTA Module in the TC1736

## 2.5.6.1 Functionality of GPTA0

The General Purpose Timer Array (GPTA0) provides a set of hardware modules required for high-speed digital signal processing:

- Filter and Prescaler Cells (FPC) support input noise filtering and prescaler operation.

- Phase Discrimination Logic units (PDL) decode the direction information output by a rotation tracking system.

- Duty Cycle Measurement Cells (DCM) provide pulse-width measurement capabilities.

- A Digital Phase Locked Loop unit (PLL) generates a programmable number of GPTA module clock ticks during an input signal's period.

- Global Timer units (GT) driven by various clock sources are implemented to operate as a time base for the associated Global Timer Cells.

- Global Timer Cells (GTC) can be programmed to capture the contents of a Global Timer on an external or internal event. A GTC may also be used to control an external port pin depending on the result of an internal compare operation. GTCs can be logically concatenated to provide a common external port pin with a complex signal waveform.

- Local Timer Cells (LTC) operating in Timer, Capture, or Compare Mode may also be logically tied together to drive a common external port pin with a complex signal waveform. LTCs – enabled in Timer Mode or Capture Mode – can be clocked or triggered by various external or internal events.

- On-chip Trigger and Gating Signals (OTGS) can be configured to provide trigger or gating signals to integrated peripherals.

Input lines can be shared by an LTC and a GTC to trigger their programmed operation simultaneously.

The following list summarizes the specific features of the GPTA units.

#### **Clock Generation Unit**

- Filter and Prescaler Cell (FPC)

- Six independent units

- Three basic operating modes:

Prescaler, Delayed Debounce Filter, Immediate Debounce Filter

- Selectable input sources:

- Port lines, GPTA module clock, FPC output of preceding FPC cell

- Selectable input clocks:

- GPTA module clock, prescaled GPTA module clock, DCM clock, compensated or uncompensated PLL clock.

- $-f_{GPTA}/2$  maximum input signal frequency in Filter Modes

- Phase Discriminator Logic (PDL)

- Two independent units

- Two operating modes (2- and 3- sensor signals)

- $-f_{\rm GPTA}/4$  maximum input signal frequency in 2-sensor Mode,  $f_{\rm GPTA}/6$  maximum input signal frequency in 3-sensor Mode

- Duty Cycle Measurement (DCM)

- Four independent units

- 0 100% margin and time-out handling

- $-f_{GPTA}$  maximum resolution

- $-f_{GPTA}/2$  maximum input signal frequency

- Digital Phase Locked Loop (PLL)

- One unit

- Arbitrary multiplication factor between 1 and 65535

- $-f_{GPTA}$  maximum resolution

- $-f_{GPTA}/2$  maximum input signal frequency

- Clock Distribution Unit (CDU)

- One unit

- Provides nine clock output signals:  $f_{\text{GPTA}}$ , divided  $f_{\text{GPTA}}$  clocks, FPC1/FPC4 outputs, DCM clock, LTC prescaler clock

### **Signal Generation Unit**

- Global Timers (GT)

- Two independent units

- Two operating modes (Free-Running Timer and Reload Timer)

- 24-bit data width

- $-f_{GPTA}$  maximum resolution

- $-f_{GPTA}/2$  maximum input signal frequency

- Global Timer Cell (GTC)

- 32 units related to the Global Timers

- Two operating modes (Capture, Compare and Capture after Compare)

- 24-bit data width

- $-f_{GPTA}$  maximum resolution

- $-f_{GPTA}/2$  maximum input signal frequency

- Local Timer Cell (LTC)

- 64 independent units

- Three basic operating modes (Timer, Capture and Compare) for 63 units

- Special compare modes for one unit

- 16-bit data width

- $-f_{GPTA}$  maximum resolution

- $-f_{GPTA}/2$  maximum input signal frequency

### Interrupt Sharing Unit

111 interrupt sources, generating up to 38 service requests

### **On-chip Trigger Unit**

16 on-chip trigger signals

### I/O Sharing Unit

Interconnecting inputs and outputs from internal clocks, FPC, GTC, LTC, ports, and MSC interface

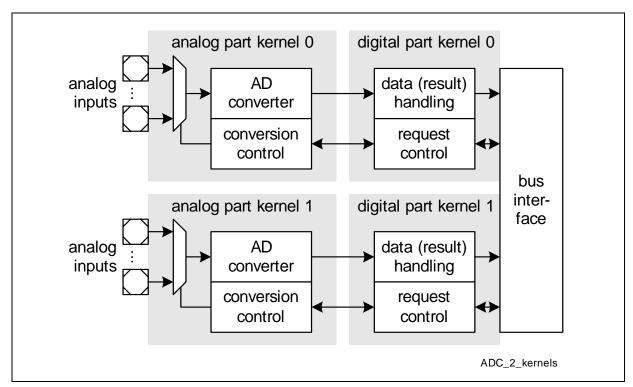

## 2.5.7 Analog-to-Digital Converter (ADC0, ADC1)

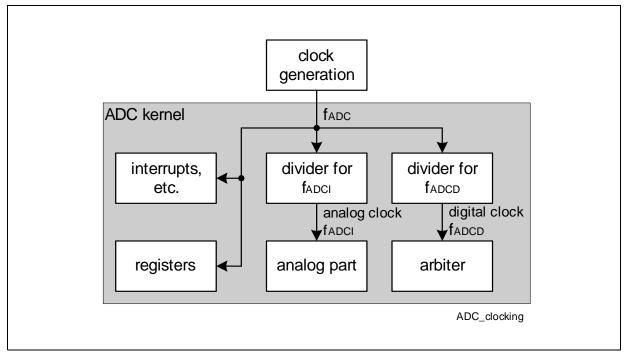

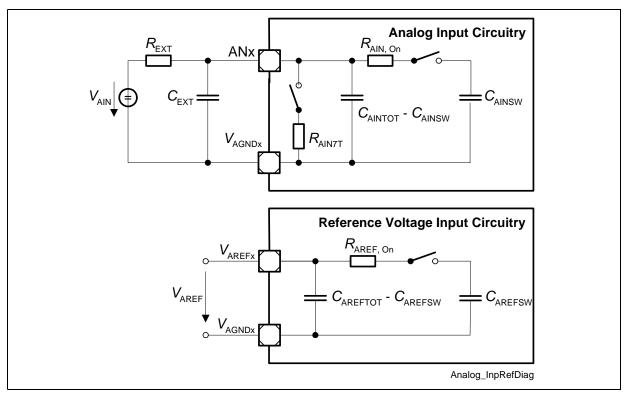

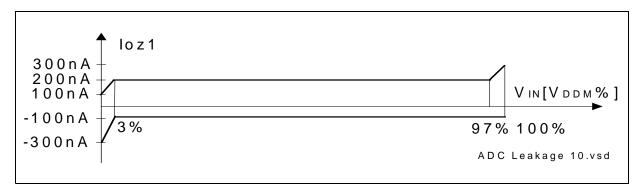

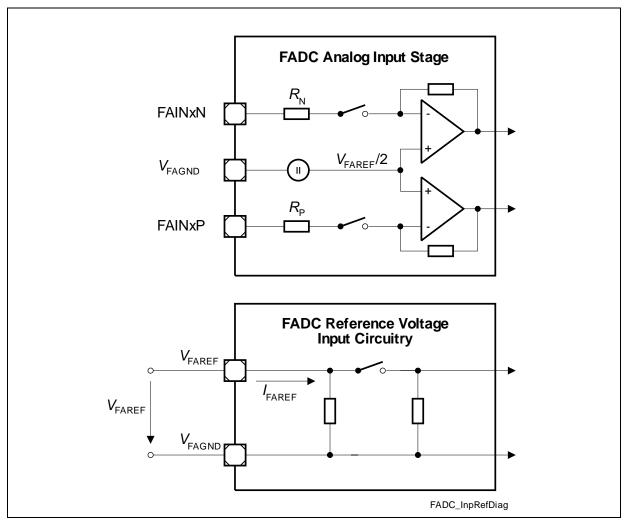

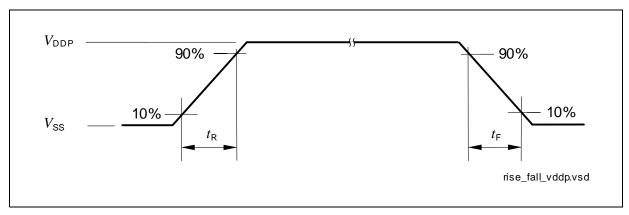

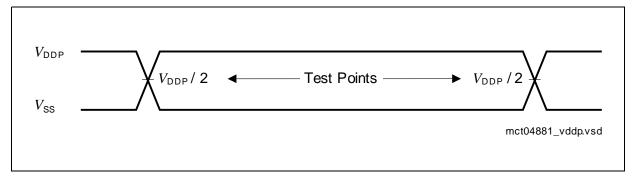

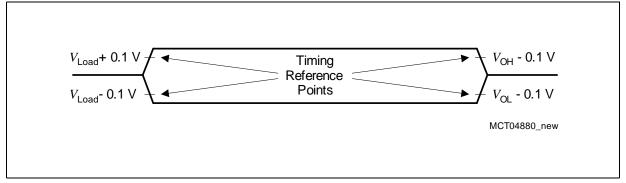

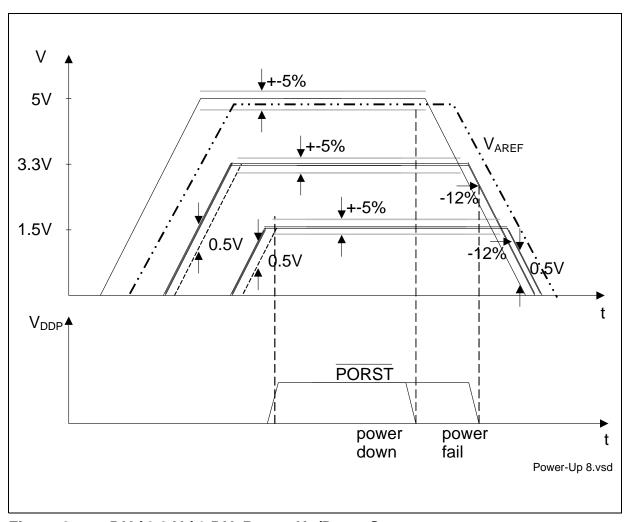

The analog to digital converter module (ADC) allows the conversion of analog input values into discrete digital values based on the successive approximation method.