#### **General Description**

The MAXQ3108 is a low-power microcontroller that features two high-performance MAXQ20 cores: a dedicated core (DSPCore) for intensive data processing and a user core (UserCore) for supervisory functions. The two cores can operate at different clock speeds, allowing lower system power consumption for even processing intensive applications. The UserCore can be configured to run at the lowest clock rate possible for monitoring the peripherals for communication activities, while the DSPCore runs at the highest speed. Each core has access to an independent math accelerator (a multiply/accumulate unit). The UserCore supports SPI™, 12C, two UART channels with one channel supporting IR carrier modulation, a trimmable real-time clock (RTC), battery-backed RTC registers, and data memory. The DSPCore is fully user programmable and configurable. With the standard 32,768Hz crystal, the DSPCore operates at 10.027MHz, while the UserCore runs at 5.014MHz.

#### **Applications**

**Electricity Meters**

**Industrial Control**

Battery-Powered and Portable Devices

**Smart Transmitters**

Medical Instrumentation

#### **Features**

- ♦ High-Performance, Low-Power, Dual 16-Bit RISC Cores

- ♦ Approaches 1MIPS per MHz

- ♦ System Clock

10.027MHz (DSPCore) 5.014MHz (UserCore)

- ♦ 33 Instructions

- ♦ Approximately 100ns Execution Time at 10.027MHz

- **♦** Three Independent Data Pointers Accelerate Data Movement with Automatic Increment/Decrement

- ♦ 16-Bit Instruction Word, 16-Bit Data Bus

- ♦ 16 x 16-Bit General-Purpose Working Registers for Each Core

- **♦ 16-Level Hardware Stack for Each Core**

- ♦ Hardware Support for Software Stack

- **♦** Memory Features

UserCore

64KB Flash Program Memory

16B Battery-Backed (VBAT) Data SRAM

4KB Utility ROM

2KB Data SRAM; 10KB Total Data SRAM (If

DSPCore Inactive)

DSPCore

8KB User-Loadable SRAM Code Memory

1KB Data SRAM

#### **♦** Peripherals

FLL (10MHz Output with 32kHz Input)

SPI Master, I<sup>2</sup>C Master

Two UART Channels (One Supports IR Carrier Modulation)

Math Accelerator for Each Core

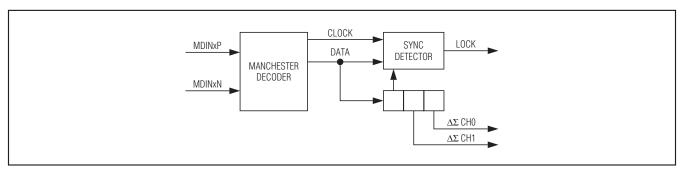

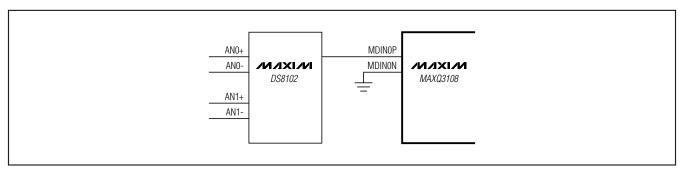

Three Manchester Decoder and Cubic Sinc Filter Channels for Interfacing to DS8102 Delta-Sigma

Two 16-Bit Programmable Timer/Counters RTC with Alarms and Digital Trim, Dedicated

Battery-Backup Pin (VBAT)

Two Programmable Pulse Generators Independent Watchdog Timer for Each Core External Interrupts

JTAG Interface

#### **♦ Operating Modes**

Stop Mode: 0.1µA typ

Active Current at 10MHz and VDD = 2.0V: 1.0mA typ

#### **Ordering Information**

| PART          | TEMP RANGE     | PIN-PACKAGE |

|---------------|----------------|-------------|

| MAXQ3108-FFN+ | -40°C to +85°C | 28 TSSOP    |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

Pin Configuration appears at end of data sheet.

SPI is a trademark of Motorola, Inc.

MAXQ is a registered trademark of Maxim Integrated Products, Inc.

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, go to: www.maxim-ic.com/errata.

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

| TABLE OF CONTENTS                          |    |

|--------------------------------------------|----|

| Absolute Maximum Ratings                   | 4  |

| Recommended DC Operating Conditions        | 4  |

| Block Diagram                              | 6  |

| Pin Description                            | 7  |

| Detailed Description                       | 8  |

| Microprocessor                             | 8  |

| Memory                                     | 9  |

| DSP Program RAM                            | 10 |

| Registers                                  | 10 |

| System Registers                           | 10 |

| Peripheral Registers—UserCore              | 10 |

| Peripheral Registers—DSPCore               | 15 |

| Special Function Register Bit Descriptions | 17 |

| Peripherals                                | 50 |

| Pins                                       | 50 |

| Clock                                      | 51 |

| 32,768Hz Crystal Oscillator                | 52 |

| Frequency-Locked Loop (FLL)                | 52 |

| Power Conservation                         | 52 |

| Power-Management Mode                      | 53 |

| Switchback                                 | 53 |

| Stop Mode                                  | 54 |

| Idle Mode                                  | 54 |

| Reset                                      | 54 |

| Power-On Reset/Brownout Reset Generation   | 54 |

| Watchdog Timer Reset                       | 55 |

| External Reset                             | 55 |

| Reset Input Pin Disable                    | 55 |

| Peripheral Devices                         | 55 |

| GPIO Ports                                 | 55 |

| UARTs                                      | 55 |

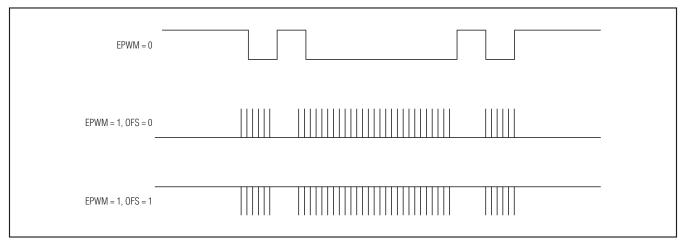

| Infrared Support                           | 56 |

| SPI                                        | 56 |

| I <sup>2</sup> C Interface                 | 56 |

| ADC Inputs                                 | 58 |

| ADC Registers                              | 59 |

| TABLE OF CONTENTS (continued)                                            |  |

|--------------------------------------------------------------------------|--|

| Dual-Core Interfaces                                                     |  |

| DSP Code Memory                                                          |  |

| Intercore Communications                                                 |  |

| Timer 2                                                                  |  |

| Timer B                                                                  |  |

| Timer B Use-Case Scenarios                                               |  |

| Multiply-Accumulate Unit                                                 |  |

| Real-Time Clock                                                          |  |

| Programmable Pulse Generators                                            |  |

| In-Application Flash Programming                                         |  |

| Development and Technical Support                                        |  |

| Additional Documentation                                                 |  |

| Pin Configuration                                                        |  |

| Package Information                                                      |  |

| LIST OF FIGURES                                                          |  |

| Figure 1. Memory Map                                                     |  |

| Figure 2. IR Option on UART 0                                            |  |

| Figure 3. ADC Bit Stream Decoder                                         |  |

| Figure 4. Connecting the MAXQ3108 to a DS8102 Dual Delta-Sigma Modulator |  |

|                                                                          |  |

| LIST OF TABLES                                                           |  |

| Table 1. UserCore Peripheral Registers                                   |  |

| Table 2. UserCore Peripheral Register Default Values                     |  |

| Table 3. DSPCore Peripheral Registers                                    |  |

| Table 4. DSPCore Peripheral Register Default Values                      |  |

| Table 5. Multipurpose Pin Description                                    |  |

| Table 6. MAXQ3108 Clock Divisors                                         |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on Any Pin                                                       | Storage Temperature Range65°C to +150°C     |

|--------------------------------------------------------------------------------|---------------------------------------------|

| except V <sub>DD</sub> with Respect to V <sub>SS</sub> 0.3V to V <sub>DD</sub> | Soldering TemperatureRefer to the IPC/JEDEC |

| Voltage Range on V <sub>DD</sub> with Respect to V <sub>SS</sub> 0.3V to +3.6V | J-STD-020 Specification.                    |

| Operating Temperature Range40°C to +85°C                                       |                                             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED DC OPERATING CONDITIONS

$(V_{DD} = V_{RST} \text{ to } 3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C.}) \text{ (Notes 1, 2)}$

| PARAMETER                                                                                       | SYMBOL                | CONDITIONS                                                               | MIN                    | TYP | MAX                  | UNITS |

|-------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------|------------------------|-----|----------------------|-------|

| Supply Voltage                                                                                  | $V_{DD}$              |                                                                          | V <sub>RST</sub>       |     | 3.6                  | V     |

| Power-Fail Reset Voltage                                                                        | V <sub>RST</sub>      | Monitors V <sub>DD</sub>                                                 | 1.875                  |     | 1.975                | V     |

| 1.8V Internal Regulator                                                                         | V <sub>REG18</sub>    |                                                                          | 1.71                   | 1.8 | 1.89                 | V     |

| 1.8V Power-Fail Reset Voltage                                                                   | VREGRST               | Monitors REGOUT                                                          | 1.62                   |     | 1.71                 | V     |

| Battery Supply Voltage                                                                          | V <sub>BAT</sub>      |                                                                          | 1.8                    |     | 3.6                  | V     |

| Battery Current (Note 3)                                                                        | I <sub>BAT1</sub>     | $V_{DD} = 0$ , $V_{BAT} = 3.6V$ , $32kHz$ oscillator and RTC enabled     |                        | 0.8 |                      | μA    |

| Battery Guirent (Note 3)                                                                        | IBALI                 | $V_{DD} = 0$ , $V_{BAT} = 2V$ , $32kHz$ oscillator and RTC enabled       |                        | 0.6 |                      | μΑ    |

| Active Current with 32.768kHz                                                                   | IDD_FLL1              | /1 mode, V <sub>DD</sub> = 2.0V                                          |                        | 1.3 | 2.2                  |       |

| Crystal Connected to CX1, CX2;                                                                  | IDD_FLL2              | /1 mode, V <sub>DD</sub> = 3.6V                                          |                        | 1.5 | 2.5                  | ^     |

| FLL Selected (10MHz Output);<br>ENDSP = 0; All Decimators and                                   | IDD_FLL9              | PMM2 (32kHz), V <sub>DD</sub> = 2.0V                                     |                        | 0.5 | 0.8                  | mA    |

| Sinc Filters Off (Note 4)                                                                       | IDD_FLL10             | PMM2 (32kHz), V <sub>DD</sub> = 3.6V                                     |                        | 0.6 | 1.0                  |       |

| Active Current with 32.768kHz<br>Crystal Connected to CX1, CX2;<br>FLL Selected (10MHz Output); | I <sub>DD_FLL14</sub> | V <sub>DD</sub> = 2.0V                                                   |                        | 1.0 | 1.7                  |       |

| UserCore = /256 PMM; DSPCore<br>= /1; ENDSP = 1; Manchester<br>Decoders On; Decimators On       | IDD_FLL15             | V <sub>DD</sub> = 3.6V                                                   |                        | 1.8 | 3.0                  | mA    |

| Cton Mada Current (Note 5)                                                                      | ISTOP_1               | BOD = 1, REGEN = 0, SVMSTOP = 0, RTC off (lowest current stop mode)      |                        | 0.1 | 2.4                  |       |

| Stop-Mode Current (Note 5)                                                                      | I <sub>STOP_2</sub>   | BOD = 0, REGEN = 0, SVMSTOP = 0, RTC off (adds brownout-reset detection) |                        | 30  | 125                  | μΑ    |

| Input Low (CX1)                                                                                 | V <sub>IL1</sub>      |                                                                          | V <sub>SS</sub>        | 0.2 | 20 x V <sub>DD</sub> | V     |

| Input Low (All Other Pins)                                                                      | V <sub>IL2</sub>      |                                                                          | V <sub>SS</sub>        | 0.3 | 30 x V <sub>DD</sub> | V     |

| Input High (CX1)                                                                                | V <sub>IH1</sub>      |                                                                          | 0.75 x V <sub>DE</sub> | )   | $V_{DD}$             | V     |

| Input High (All Other Pins)                                                                     | V <sub>IH2</sub>      |                                                                          | 0.70 x V <sub>DE</sub> | )   | $V_{DD}$             | V     |

| Input Hysteresis (Schmitt)                                                                      | VIHYS                 |                                                                          | 0.18                   |     |                      | V     |

| Output Low (All Port Pins)                                                                      | V <sub>OL</sub>       | I <sub>OL</sub> = 4mA (Note 6)                                           | V <sub>SS</sub>        |     | 0.4                  | V     |

| Output High (All Port Pins)                                                                     | VoH                   | I <sub>OH</sub> = -4mA (Note 6)                                          | V <sub>DD</sub> - 0.4  |     |                      | V     |

4 \_\_\_\_\_\_*MAXIM*

#### RECOMMENDED DC OPERATING CONDITIONS (continued)

$(V_{DD} = V_{RST} \text{ to } 3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C.}) \text{ (Notes 1, 2)}$

| PARAMETER                                      | SYMBOL           | CONDITIONS                                       | MIN  | TYP    | MAX  | UNITS  |

|------------------------------------------------|------------------|--------------------------------------------------|------|--------|------|--------|

| Input/Output Pin Capacitance                   | CIO              | Guaranteed by design                             |      |        | 15   | pF     |

| Input Low Current All Pins                     | I <sub>I</sub> L | V <sub>IN</sub> = 0.4V                           |      |        | -30  | μΑ     |

| Input-Leakage Current                          | IL               | Internal pullup disabled                         | -100 |        | +100 | nA     |

| Input Pullup Resistor (All Inputs)             | R <sub>PU</sub>  |                                                  |      | 60     |      | kΩ     |

| CLOCK SOURCE                                   |                  |                                                  |      |        |      |        |

| FLL Output Frequency                           | fFLL             | CX1 = 32.768kHz                                  | 9.5  | 10.0   | 10.5 | MHz    |

| FLL Output Accuracy                            | $\Delta f_{FLL}$ | CX1 = 32.768kHz                                  |      | 1.5    | ±5   | %      |

| FLASH MEMORY                                   |                  |                                                  |      |        |      |        |

| System Clock During Flash<br>Programming/Erase |                  |                                                  | 2    |        |      | MHz    |

| Flash Erase Time                               |                  | Mass erase                                       | 22.8 | 24     | 25.2 |        |

| Flash Erase Time<br>                           |                  | Page erase                                       | 22.8 | 24     | 25.2 | ms     |

| Flash Programming Time Per<br>Word             |                  | (Note 7)                                         | 59.5 |        | 66.5 | μs     |

| Write/Erase Cycles                             |                  |                                                  |      | 1000   |      | Cycles |

| Data Retention                                 |                  | T <sub>A</sub> = +25°C                           | 100  |        |      | Years  |

| SUPPLY VOLTAGE MONITOR                         |                  |                                                  |      |        |      |        |

| Set Point                                      | SVTR             |                                                  | 2.0  |        | 3.5  | V      |

| Increment Resolution                           |                  |                                                  |      | 0.1    |      | V      |

| Default Set Point                              |                  |                                                  |      | 2.7    |      | V      |

| Current Consumption                            | IsvM             |                                                  |      |        | 10   | μΑ     |

| Start Time                                     | tsvmst           |                                                  |      |        | 200  | μs     |

| Setup Time (Change Set Point)                  | tsvm_su1         | Changing from one set point to another set point |      |        | 2    | μs     |

| Setup Time (Stop Mode Exit)                    | tsvm_su2         | Exit from stop mode                              |      |        | 8    | μs     |

| REAL-TIME CLOCK                                |                  |                                                  |      |        |      |        |

| RTC Input Frequency                            | f32KIN           | 32kHz watch crystal                              |      | 32,768 |      | Hz     |

| RTC Operating Current                          | Into             | V <sub>DD</sub> = 2.0V                           |      | 0.6    |      |        |

| NTO Operating Current                          | IRTC             | V <sub>DD</sub> = 3.6V                           | _    | 0.8    |      | μA     |

- Note 1: Results based on simulation data. Characterization data will be available at a later date. All voltages are referenced to ground. Specifications to  $T_A = -40$ °C are guaranteed by design and are not production tested.

- **Note 2:** Typical values are not guaranteed. These values are measured at room temperature,  $V_{DD} = 3.3V$ .

- Note 3: This current is from V<sub>BAT</sub> only if (V<sub>DD</sub> < V<sub>BAT</sub> and V<sub>DD</sub> < V<sub>RST</sub>) or (STOP = 1, REGEN = 0, BOD = 1). Otherwise, this current is from V<sub>DD</sub>.

- **Note 4:** Measured on the V<sub>DD</sub> pin and the device not in reset. All inputs are connected to V<sub>SS</sub> or V<sub>DD</sub>. Outputs do not source/sink any current. Timer enabled, RTC enabled, part executing JUMP \$ from flash.

- Note 5: If the RTC is on for parameters ISTOP\_2, ISTOP\_3, and ISTOP\_4, a current equal to IBAT1 is added to IDD.

- Note 6: The maximum total current, I<sub>OH(MAX)</sub> and I<sub>OL(MAX)</sub>, for all outputs combined should not exceed 35mA to satisfy the maximum specified voltage drop.

- Note 7: The timing listed above is clocked by 63 cycles of the internal 1MHz ±5% clock. There will be ROM code overhead, which is a function of system clock. For data sheet purposes, a better way is to specify the limits that include ROM code execution with specified system clock speed.

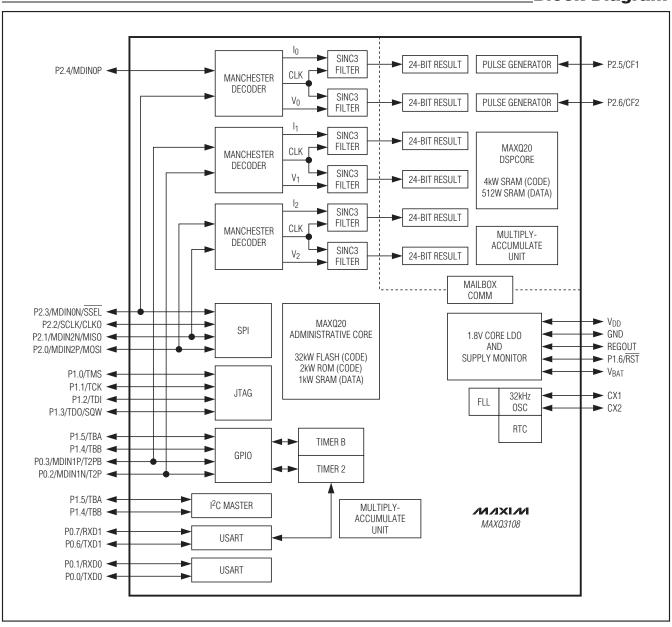

#### **Block Diagram**

### Pin Description

| PIN                        | NAME             |                                                                                                                                                                                    | FUNC                                                                                                                                                                                                                   | TION                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|----------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                            |                  | I                                                                                                                                                                                  | POWER PINS                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 21                         | V <sub>DD</sub>  | Supply Voltage. Must be capacitor.                                                                                                                                                 | e bypassed with a 4.7μF α                                                                                                                                                                                              | capacitor with ESR $< 5\Omega$ and a 0.1 $\mu$ F ceramic                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 17                         | GND              | Ground                                                                                                                                                                             |                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 20                         | REGOUT           | Regulator Output. 1.8V c capacitor.                                                                                                                                                | output. Must be connected                                                                                                                                                                                              | I to a 1 $\mu$ F low-ESR (< 1 $\Omega$ ) external ceramic chip                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 19                         | V <sub>BAT</sub> | Battery Input for Backin                                                                                                                                                           | g Up the RTC                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                            |                  |                                                                                                                                                                                    | CLOCK PINS                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 15, 16                     | CX1, CX2         |                                                                                                                                                                                    |                                                                                                                                                                                                                        | Iz crystal to be connected in order to supply the e included in the circuitry.                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                            |                  | •                                                                                                                                                                                  | I/O PINS                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                            |                  | master and serial UARTs<br>reset condition of the pir<br>register must be program                                                                                                  | s 0 and 1. All pins suppor<br>ns is weakly pulled up (in                                                                                                                                                               | nd as a special function interface to the I <sup>2</sup> C t external interrupt functionality. The default put). To drive output, either the port direction the alternate function module must be le to the UserCore only.                                                                                                                                                                              |  |  |  |  |

|                            |                  | PIN                                                                                                                                                                                | PORT                                                                                                                                                                                                                   | ALTERNATE FUNCTION                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                            |                  | 2                                                                                                                                                                                  | P0.0                                                                                                                                                                                                                   | TXD0/INT0                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 2–7, 23, 22                | P0.0-P0.7        | 3                                                                                                                                                                                  | P0.1                                                                                                                                                                                                                   | RXD0/INT1                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                            |                  | 4                                                                                                                                                                                  | P0.2                                                                                                                                                                                                                   | MDIN1N/T2P/INT2                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                            |                  | 5                                                                                                                                                                                  | P0.3                                                                                                                                                                                                                   | MDIN1P/T2PB/INT3                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                            |                  | 6                                                                                                                                                                                  | P0.4                                                                                                                                                                                                                   | SDA/INT4                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                            |                  | 7                                                                                                                                                                                  | P0.5                                                                                                                                                                                                                   | SCL/INT5                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                            |                  | 23                                                                                                                                                                                 | P0.6                                                                                                                                                                                                                   | TXD1/INT6                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                            |                  | 22                                                                                                                                                                                 | P0.7                                                                                                                                                                                                                   | RXD1/INT7                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 10, 11, 12,<br>13, 14, 18, | P1.0-P1.6        | compatible test access from timer B. All pins su P1.0–P1.3 is the JTAG for disabled by user code. The Active-Low Reset (RST) an internal pullup resists not required for power-up. | port (TAP), the RTC squar pport external interrupt fur unctions. To use the 4-bit This port is accessible to The RST pin recognizes or to allow for a combination, as this function is provincial that this pin not be | If as a special function interface to the JTAG e-wave output, and as the input/output to and actionality. The default reset condition of pins port as standard GPIO, the TAP must be the UserCore only.  External active-low reset inputs and employs on of wired-OR external reset sources. An RC is ded internally. The RST pin function is enabled held low externally after a power-on reset or the |  |  |  |  |

| 24                         |                  | PIN                                                                                                                                                                                | PORT                                                                                                                                                                                                                   | ALTERNATE FUNCTION                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                            |                  | 10                                                                                                                                                                                 | P1.0                                                                                                                                                                                                                   | TMS/INT8                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                            |                  | 11                                                                                                                                                                                 | P1.1                                                                                                                                                                                                                   | TCK/INT9                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                            |                  | 12                                                                                                                                                                                 | P1.2                                                                                                                                                                                                                   | TDI/INT10                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                            |                  | 13                                                                                                                                                                                 | P1.3                                                                                                                                                                                                                   | TDO/SQW/INT11                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                            |                  | 14                                                                                                                                                                                 | P1.4                                                                                                                                                                                                                   | ТВВ                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                            |                  | 18                                                                                                                                                                                 | P1.5                                                                                                                                                                                                                   | ТВА                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                            |                  | 24                                                                                                                                                                                 | P1.6                                                                                                                                                                                                                   | RST                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

#### **Pin Description (continued)**

| PIN                     | NAME      |                                                                                    | FUNC                                                                                                                | TION                                                                                                                                                                                                                                                        |        |      |             |  |    |      |             |           |

|-------------------------|-----------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-------------|--|----|------|-------------|-----------|

|                         |           | generator outputs, clock<br>the pins is weakly pulled<br>and default to strong hig | output, and the Manches<br>d up (input), with exceptio<br>h. To drive output, either t<br>alternate function module | d as a special function interface to the CF pulse<br>ster ENDEC or SPI. The default reset condition of<br>on of P2.5 and P2.6, which are always outputs<br>the port direction register must be programmed<br>must be configured to drive the pins. P2.5 and |        |      |             |  |    |      |             |           |

|                         |           | PIN                                                                                | PORT                                                                                                                | ALTERNATE FUNCTION                                                                                                                                                                                                                                          |        |      |             |  |    |      |             |           |

| 1, 28, 27, 26, 25, 8, 9 | P2.0-P2.6 | 1                                                                                  | P2.0                                                                                                                | MDIN2P/MOSI                                                                                                                                                                                                                                                 |        |      |             |  |    |      |             |           |

| 20, 0, 0                |           |                                                                                    |                                                                                                                     |                                                                                                                                                                                                                                                             | 28     | P2.1 | MDIN2N/MISO |  |    |      |             |           |

|                         |           |                                                                                    |                                                                                                                     |                                                                                                                                                                                                                                                             | -      |      | -           |  |    | 27   | P2.2        | SCLK/CLKO |

|                         |           |                                                                                    |                                                                                                                     |                                                                                                                                                                                                                                                             |        |      |             |  | 26 | P2.3 | MDINON/SSEL |           |

|                         |           | 25 I                                                                               |                                                                                                                     | P2.4                                                                                                                                                                                                                                                        | MDIN0P |      |             |  |    |      |             |           |

|                         |           | 8                                                                                  | P2.5                                                                                                                | CF1                                                                                                                                                                                                                                                         |        |      |             |  |    |      |             |           |

|                         |           | 9                                                                                  | P2.6                                                                                                                | CF2                                                                                                                                                                                                                                                         |        |      |             |  |    |      |             |           |

#### Detailed Description

The MAXQ3108 microcontroller is an integrated, low-cost solution to simplify the design of electricity metering and industrial control products. Standard features include two highly optimized, single-cycle, MAXQ 16-bit RISC microcontroller cores; 64KB of flash memory, 11KB RAM, and independent hardware stacks; general-purpose registers; and data pointers for each core. Application-specific peripherals include hardware SPI and I<sup>2</sup>C masters, real-time clock, programmable pulse generators, dual UARTs (one of which that supports IR carrier frequency modulation), and math accelerators.

At the heart of the MAXQ3108 are two MAXQ20 16-bit RISC microcontrollers. The dual-core approach allows one core (DSPCore) to be entirely dedicated to collection and processing of AFE samples for the metering function, while the second core handles any communication and user-specific administrative functions. The MAXQ3108 DSPCore operates at 10.027MHz with the default crystal and almost all instructions execute in a single clock cycle (100ns), while the UserCore runs at half that frequency (5.014MHz).

The dual-core strategy promotes flexibility by allowing the update of metering routines and parameters separately in DSPCore code and data memory. Furthermore, an independent DSPCore solely responsible for accurate metering introduces a measure of safety and reliability since all administrative/communication functions and interruptions are handled by the UserCore. Both cores feature standard MAXQ power-saving system

clock-divide modes and independently implement low-power stop (UserCore) and idle (DSPCore) modes. The DSPCore implements an idle mode that allows CPU execution to be halted while awaiting an ADC sample. The UserCore implements an ultra-low-power stop mode that automatically disables the DSPCore and results in a quiescent current consumption of less than 1.5 $\mu$ A. The combination of high performance and corespecific low-power mode implementation provides increased power efficiency and capability over competitive microcontrollers.

#### \_Microprocessor

The MAXQ20 is a low-power implementation of the new 16-bit MAXQ family of RISC cores. The core supports the Harvard memory architecture with separate 16-bit program and data address buses, but also provides pseudo-Von Neumann support through utility ROM functions. A fixed 16-bit instruction is standard, but data can be arranged in 8 or 16 bits. The MAXQ20 core is implemented as a nonpipelined processor with single clock-cycle instruction execution. The data path is implemented around register modules, and each register module contributes specific functions to the core. The accumulator module consists of sixteen 16-bit registers and is tightly coupled to the arithmetic logic unit (ALU). Program flow is supported by a dedicated 16-level-deep hardware stack.

Execution of instructions is triggered by data transfer between functional register modules, or between a functional register module and memory. Since data

movement involves only source and destination modules, circuit switching activities are limited to active modules only. For power-conscious applications, this approach localizes power dissipation and minimizes switching noise. The modular architecture also provides maximum flexibility and reusability, which are important for a microprocessor used in embedded applications.

The MAXQ instruction set is designed to be highly orthogonal. All arithmetical and logical operations can use any register along with the accumulator. Data movement is supported from any register to any other register. Memory is accessed through specific data pointer registers with auto increment/decrement support.

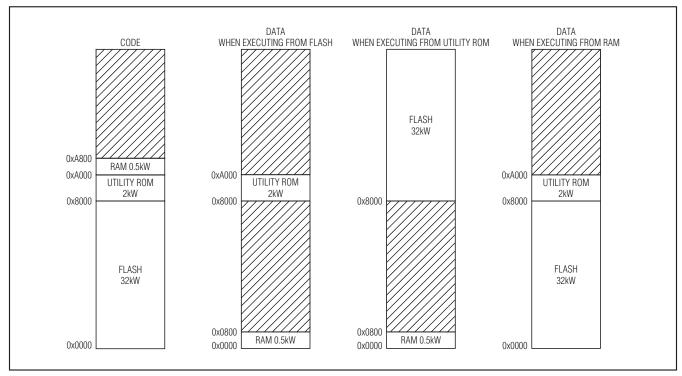

#### Memory

The MAXQ3108 supports a pseudo-Von Neumann memory structure that can merge program and data into a linear memory map. This is accomplished by mapping the data memory into the program space or mapping the program memory segment into the data space. Memory access is under the control of the memory management unit (MMU). During flash programming, the MMU maps the flash memory into data space, and the built-in firmware provides necessary controls to the

embedded flash memory for all read/erase/write operations when the ROM loader is invoked. Additionally, when the DSPCore is disabled, all its code SRAM (8KB) is mapped into the data SRAM space of the UserCore. This allows streamlined reconfiguration of the DSP code memory or a larger data SRAM for applications not employing DSPCore operation.

The MAXQ3108 incorporates the following:

- 4KB utility ROM

- 64KB program flash

- 2KB SRAM data memory

- 8KB program SRAM (DSPCore)

- 1KB SRAM data memory (DSPCore)

The MMU operates automatically and maps data memory as a function of the contents of the instruction pointer; that is, the execution location controls the structure of the data memory map. The only constraint is that no memory region is available as data when code is being fetched from that region. For example, when executing from flash, flash cannot be read as data. But changing the execution location to the utility ROM through a subroutine call allows the flash memory to be read as data.

Figure 1. Memory Map

#### **DSP Program RAM**

A 4K Word (8KB) section of memory is available to the DSPCore as code memory. When the DSPCore is disabled (as it is immediately following a reset event) that block of memory appears in the UserCore data memory map at location 0x1000. Thus, a typical startup sequence to operate both cores might include:

- 1) Low-level initialization of the UserCore.

- Copy DSP code from program flash to DSPCore code RAM at 0x1000.

- 3) Enable DSPCore.

- 4) Poll mailbox registers to verify that DSPCore is correctly running.

For more information, see the *Dual-Core Interfaces* section.

#### Registers

The MAXQ family of microcontrollers uses a bank of registers to access memory and peripherals and to perform basic CPU activities. These registers are organized into as many as 16 register modules, each of which can have as many as 32 registers, giving a system maximum of 512 registers. The registers are divided into two sections: system registers (modules 7 to 15) and peripheral registers (modules 0 to 5).

Since the MAXQ3108 contains two MAXQ core processors, each has a set of system registers and a set of peripheral registers.

#### **System Registers**

The MAXQ3108 UserCore implements the standard set of system registers as described in the *MAXQ Family User's Guide*. The exceptions are listed below:

In the IMR register, bit IM5 is not implemented since there is no module 5 implemented in the MAXQ3108.

- In the SC register, bits CDA1 and UPM are not implemented since the size of the memory in the device does not require their implementation.

- In the IIR register, bit II5 is not implemented since there is no module 5 implemented in the MAXQ3108.

- In the CKCN register, bits XT/RC, RGSL, and RGMD are not implemented. Instead, bits 5 and 6 are FLLMD and FLLSL, respectively. These bits support the frequency-locked loop (FLL) that forms a core part of the MAXQ3108 clocking scheme. More information is given in the *Clock* section.

The MAXQ3108 DSPCore system register complement is identical to that found in the UserCore, with these exceptions:

- In the IMR register, only IMO is implemented.

- The system control (SC) register is not implemented.

- In the IIR register, only the II0 bit is implemented.

- The WDCN register is not implemented because there is no watchdog timer in the DSPCore. Watchdog functionality can be implemented in the UserCore by determining if the DSPCore is responding to messages.

- In the CKCN register, the STOP, RGSL, and SWB bits are not implemented because the corresponding functions do not exist in the DSPCore. The FLLMD and FLLSL bits are not implemented because a common clock block is shared with the UserCore, and the control bits here would be redundant.

#### Peripheral Registers—UserCore

The MAXQ3108 UserCore exposes its peripheral complement in five modules numbered 0 to 4. Table 1 describes the functions associated with the peripheral registers, and Table 2 shows the default values of these registers.

**Table 1. UserCore Peripheral Registers**

| REGISTER | MOD: |    |                           |                      |    |    |    |    | В       | IT       |      |        |        |         |       |     |   |

|----------|------|----|---------------------------|----------------------|----|----|----|----|---------|----------|------|--------|--------|---------|-------|-----|---|

| REGISTER | REG  | 15 | 14                        | 13                   | 12 | 11 | 10 | 9  | 8       | 7        | 6    | 5      | 4      | 3       | 2     | 1   | 0 |

| AD0      | 0:0  |    |                           |                      |    |    |    | AD | C0 Outp | ut Regi: | ster |        |        |         |       |     |   |

| AD1      | 0:1  |    |                           | ADC1 Output Register |    |    |    |    |         |          |      |        |        |         |       |     |   |

| AD2      | 0:2  |    |                           | ADC2 Output Register |    |    |    |    |         |          |      |        |        |         |       |     |   |

| AD3      | 0:3  |    |                           |                      |    |    |    | AD | C3 Outp | ut Regi: | ster |        |        |         |       |     |   |

| AD4      | 0:4  |    |                           |                      |    |    |    | AD | C4 Outp | ut Regi  | ster |        |        |         |       |     |   |

| AD5      | 0:5  |    |                           |                      |    |    |    | AD | C5 Outp | ut Regi: | ster |        |        |         |       |     |   |

| SRSP0    | 0:6  |    |                           |                      |    |    |    |    |         |          |      | RSPSDV | REQE   |         | RS    | PST |   |

| SRSP1    | 0:7  |    | Slave Response Register 1 |                      |    |    |    |    |         |          |      |        |        |         |       |     |   |

| AD0LSB   | 0:8  |    |                           |                      |    |    |    |    |         |          |      | ADC    | Output | Registe | r LSB | ·   |   |

10 \_\_\_\_\_\_\_/V|X|/V

Table 1. UserCore Peripheral Registers (continued)

|          | MOD: |        |       |        |        |       |       |                 | В        | IT        |         |           |            |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |          |  |  |

|----------|------|--------|-------|--------|--------|-------|-------|-----------------|----------|-----------|---------|-----------|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|--|--|

| REGISTER | REG  | 15     | 14    | 13     | 12     | 11    | 10    | 9               | 8        | 7         | 6       | 5         | 4          | 3        | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1        | 0        |  |  |

| AD1LSB   | 0:9  |        |       |        |        |       |       |                 |          |           |         | ADC       | 1 Output   | Registe  | er LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |          |  |  |

| AD2LSB   | 0:10 |        |       |        |        |       |       |                 |          |           |         | ADC       | 2 Output   | Registe  | er LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |          |  |  |

| AD3LSB   | 0:11 |        |       |        |        |       |       |                 |          |           |         | ADC       | 3 Output   | Registe  | er LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |          |  |  |

| AD4LSB   | 0:12 |        |       |        |        |       |       |                 |          |           |         | ADC       | 4 Output   | Registe  | er LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |          |  |  |