#### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics atta abooks, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU ROHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

32

# SH7712

# Hardware Manual

Renesas 32-Bit RISC Microcomputer SuperHTM RISC engine Family / SH7700 Series

SH7712 HD6417712

Renesas Electronics

Rev.1.00 2005.12

Rev. 1.00 Dec. 27, 2005 Page ii of xlii

#### Keep safety first in your circuit designs!

Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any thirdparty's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

#### **General Precautions on Handling of Product**

- 1. Treatment of NC Pins

- Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level. Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a passthrough current flows internally, and a malfunction may occur.

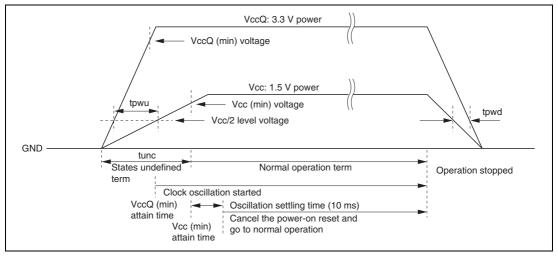

- 3. Processing before Initialization

- Note: When power is first supplied, the product's state is undefined. The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

- 4. Prohibition of Access to Undefined or Reserved Addresses

- Note: Access to undefined or reserved addresses is prohibited. The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

# Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5. Overview

- 6. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. List of Registers

- 8. Electrical Characteristics

- 9. Appendix

10. Main Revisions and Additions in this Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier versions. This does not include all of the revised contents. For details, see the actual locations in this manual.

11. Index

Rev. 1.00 Dec. 27, 2005 Page vi of xlii

# Preface

The SH7712 RISC (Reduced Instruction Set Computer) microcomputer includes a Renesas Technology original RISC CPU as its core, and the peripheral functions required to configure a system.

- Target Users: This manual was written for users who will be using this LSI in the design of application systems. Users of this manual are expected to understand the fundamentals of electrical circuits, logical circuits, and microcomputers.

- Objective: This manual was written to explain the hardware functions and electrical characteristics of this LSI to the above users. Refer to the SH-3/SH-3E/SH3-DSP Programming Manual for a detailed description of the instruction set.

Notes on reading this manual:

• Product names

The following products are covered in this manual.

#### **Product Classifications and Abbreviations**

| Basic Classification | Product Code |

|----------------------|--------------|

| SH7712               | HD6417712    |

• In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized into parts on the CPU, system control functions, peripheral functions and electrical characteristics.

• In order to understand the details of the CPU's functions

Read the SH-3/SH-3E/SH3-DSP Programming Manual.

| Rules:          | Register name:   | The following notation is used for cases when the same or a similar function, e.g. serial communication interface, is implemented on more than one channel:<br>XXX_N (XXX is the register name and N is the channel number) |

|-----------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Bit order:       | The MSB (most significant bit) is on the left and the LSB (least significant bit) is on the right.                                                                                                                          |

|                 | Number notation: | Binary is B'xxxx, hexadecimal is H'xxxx, decimal is xxxx.                                                                                                                                                                   |

|                 | Signal notation: | An overbar is added to a low-active signal: $\overline{xxxx}$                                                                                                                                                               |

| Related Manuals |                  | ions of all related manuals are available from our web site.<br>you have the latest versions of all documents you require.<br>hesas.com/                                                                                    |

| SH7712 manual   | s:               |                                                                                                                                                                                                                             |

| Document Title                        | Document No. |

|---------------------------------------|--------------|

| SH7712 Hardware Manual                | This manual  |

| SH-3/SH-3E/SH3-DSP Programming Manual | ADE-602-096B |

User's manuals for development tools:

| Document Title                                                                                                              | Document No.    |

|-----------------------------------------------------------------------------------------------------------------------------|-----------------|

| SuperH <sup>™</sup> RISC engine C/C++ Compiler,Assembler,Optimizing Linkage<br>Editor Compiler Package V.9.00 User's Manual | REJ10B0152-0101 |

| SuperH <sup>™</sup> RISC engine High-performance Embedded Workshop 3 Users<br>Manual                                        | REJ10B0025-0200 |

| SuperH RISC engine High-Performance Embedded Workshop 3 Tutorial                                                            | REJ10B0023-0200 |

Application note:

| Document Title                                             | Document No.    |  |  |

|------------------------------------------------------------|-----------------|--|--|

| SuperH RISC engine C/C++ Compiler Package Application Note | REJ05B0463-0100 |  |  |

#### Abbreviations

| ACIA  | Asynchronous communication interface adapter |

|-------|----------------------------------------------|

| AUD   | Advanced user debugger                       |

| BSC   | Bus state controller                         |

| CPG   | Clock pulse generator                        |

| DMA   | Direct memory access                         |

| DMAC  | Direct memory access controller              |

| etu   | Elementary time unit                         |

| FIFO  | First-in first-out                           |

| H-UDI | User debugging interface                     |

| INTC  | Interrupt controller                         |

| JTAG  | Joint test action group                      |

| LSB   | Least significant bit                        |

| MMU   | Memory management unit                       |

| MSB   | Most significant bit                         |

| PFC   | Pin function controller                      |

| RISC  | Reduced instruction set computer             |

| RTC   | Realtime clock                               |

| SCIF  | Serial communication interface with FIFO     |

| SIOF  | Serial I/O with FIFO                         |

| TLB   | Translation lookaside buffer                 |

| TMU   | Timer unit                                   |

| UART  | Universal asynchronous receiver/transmitter  |

| UBC   | User break controller                        |

| WDT   | Watchdog timer                               |

|       |                                              |

# Contents

| 1.1 Features                                 |    |

|----------------------------------------------|----|

| 1.1 1 Catures                                | 1  |

| 1.2 Block Diagram                            | 7  |

| 1.3 Pin Description                          |    |

| 1.3.1 Pin Assignment                         |    |

| 1.3.2 Pin Functions                          |    |

| Section 2 CPU                                | 27 |

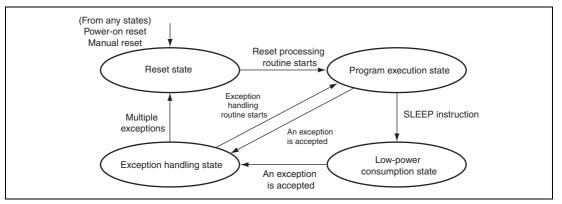

| 2.1 Processing States and Processing Modes   |    |

| 2.1.1 Processing States                      |    |

| 2.1.2 Processing Modes                       |    |

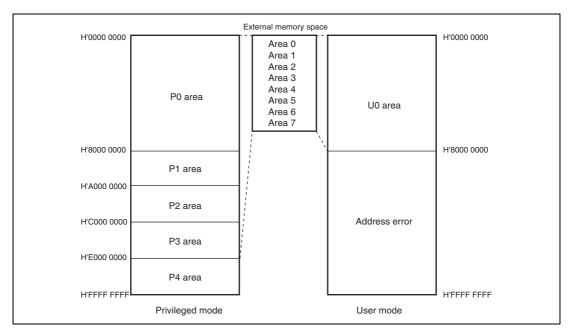

| 2.2 Memory Map                               |    |

| 2.2.1 Logical Address Space                  |    |

| 2.2.2 External Memory Space                  |    |

| 2.3 Register Descriptions                    |    |

| 2.3.1 General Registers                      |    |

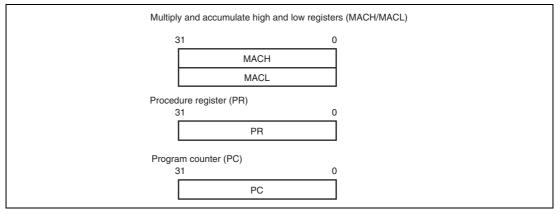

| 2.3.2 System Registers                       |    |

| 2.3.3 Program Counter                        |    |

| 2.3.4 Control Registers                      |    |

| 2.4 Data Formats                             |    |

| 2.4.1 Register Data Format                   |    |

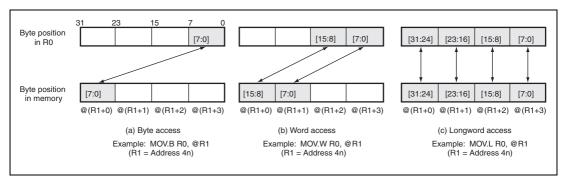

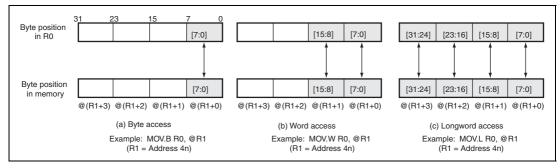

| 2.4.2 Memory Data Formats                    |    |

| 2.5 Features of CPU Core Instructions        |    |

| 2.5.1 Instruction Execution Method           | 44 |

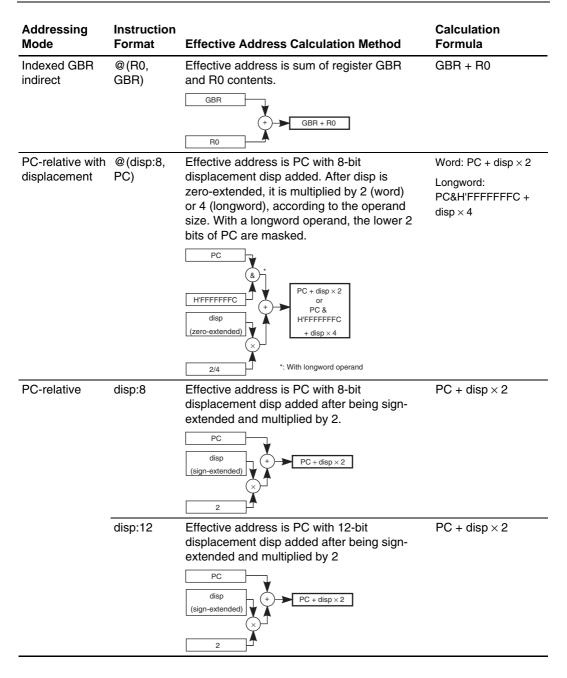

| 2.5.2 CPU Instruction Addressing Modes       |    |

| 2.5.3 CPU Instruction Formats                |    |

| 2.6 Instruction Set                          |    |

| 2.6.1 CPU Instruction Set Based on Functions |    |

| 2.6.2 Operation Code Map                     | 66 |

| Section 3 DSP Operating Unit                 | 71 |

| 3.1 DSP Extended Functions                   |    |

| 3.2 DSP Mode Resources                       |    |

| 3.2.1 Processing Modes                       |    |

| 3.2.2 DSP Mode Memory Map                    |    |

| 3.2.3 CPU Register Sets                      |    |

|       | 3.2.4  | DSP Registers                                                  | 77    |

|-------|--------|----------------------------------------------------------------|-------|

| 3.3   | CPU E  | xtended Instructions                                           |       |

|       | 3.3.1  | Repeat Control Instructions                                    |       |

|       | 3.3.2  | Extended Repeat Control Instructions                           |       |

| 3.4   | DSP Da | ata Transfer Instructions                                      |       |

|       | 3.4.1  | General Registers                                              |       |

|       | 3.4.2  | DSP Data Addressing                                            |       |

|       | 3.4.3  | Modulo Addressing                                              |       |

|       | 3.4.4  | Memory Data Formats                                            |       |

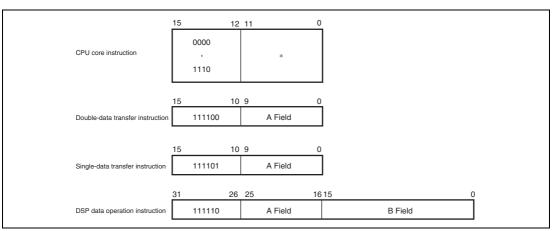

|       | 3.4.5  | Instruction Formats of Double and Single Transfer Instructions |       |

| 3.5   | DSP Da | ata Operation Instructions                                     |       |

|       | 3.5.1  | DSP Registers                                                  |       |

|       | 3.5.2  | DSP Operation Instruction Set                                  |       |

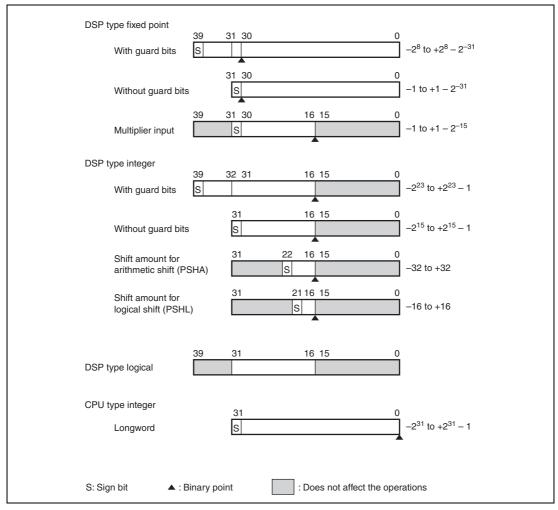

|       | 3.5.3  | DSP-Type Data Formats                                          |       |

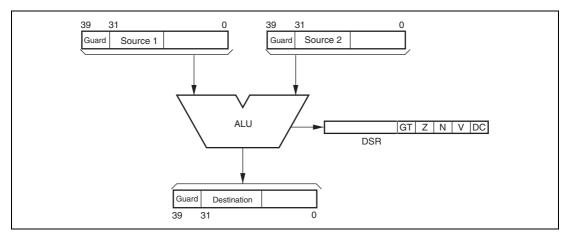

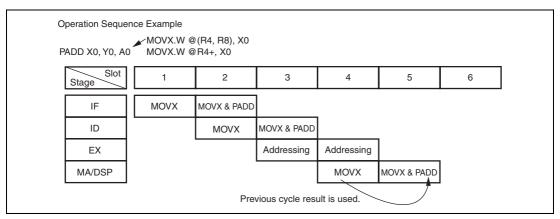

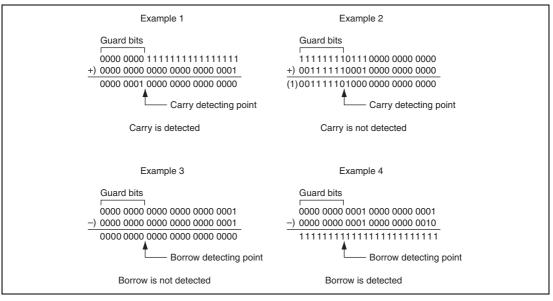

|       | 3.5.4  | ALU Fixed-Point Operations                                     |       |

|       | 3.5.5  | ALU Integer Operations                                         |       |

|       | 3.5.6  | ALU Logical Operations                                         |       |

|       | 3.5.7  | Fixed-Point Multiply Operation                                 |       |

|       | 3.5.8  | Shift Operations                                               |       |

|       | 3.5.9  | Most Significant Bit Detection Operation                       |       |

|       | 3.5.10 | Rounding Operation                                             |       |

|       | 3.5.11 | Overflow Protection                                            |       |

|       | 3.5.12 | Local Data Move Instruction                                    |       |

|       | 3.5.13 | Operand Conflict                                               |       |

| 3.6   | DSP E  | stended Function Instruction Set                               |       |

|       | 3.6.1  | CPU Extended Instructions                                      |       |

|       | 3.6.2  | Double-Data Transfer Instructions                              |       |

|       | 3.6.3  | Single-Data Transfer Instructions                              |       |

|       | 3.6.4  | DSP Operation Instructions                                     |       |

|       | 3.6.5  | Operation Code Map in DSP Mode                                 |       |

| a     | 4 1    |                                                                | 1.5.5 |

| Secti |        | Exception Handling                                             |       |

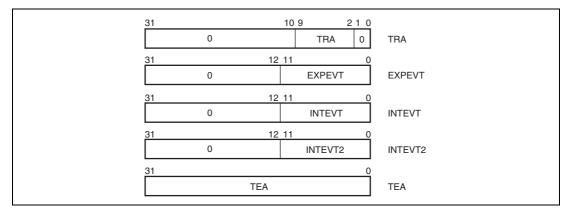

| 4.1   | -      | r Descriptions                                                 |       |

|       | 4.1.1  | TRAPA Exception Register (TRA)                                 |       |

|       | 4.1.2  | Exception Event Register (EXPEVT)                              |       |

|       | 4.1.3  | Interrupt Event Register (INTEVT)                              |       |

|       | 4.1.4  | Interrupt Event Register 2 (INTEVT2)                           |       |

|       | 4.1.5  | Exception Address Register (TEA)                               |       |

| 4.2   | -      | ion Handling Function                                          |       |

|       | 4.2.1  | Exception Handling Flow                                        |       |

|      | 4.2.2 | Exception Vector Addresses                                           |  |

|------|-------|----------------------------------------------------------------------|--|

|      | 4.2.3 | Exception Codes                                                      |  |

|      | 4.2.4 | Exception Request and BL Bit (Multiple Exception Prevention)         |  |

|      | 4.2.5 | Exception Source Acceptance Timing and Priority                      |  |

| 4.3  | Indiv | idual Exception Operations                                           |  |

|      | 4.3.1 | Resets                                                               |  |

|      | 4.3.2 | General Exceptions                                                   |  |

|      | 4.3.3 | General Exceptions (MMU Exceptions)                                  |  |

| 4.4  | Excep | ption Processing while DSP Extension Function is Valid               |  |

|      | 4.4.1 | Illegal Instruction Exception and Slot Illegal Instruction Exception |  |

|      | 4.4.2 | CPU Address Error                                                    |  |

|      | 4.4.3 | Exception in Repeat Control Period                                   |  |

| 4.5  | Usage | e Notes                                                              |  |

|      |       |                                                                      |  |

| Sect | ion 5 | Memory Management Unit (MMU)                                         |  |

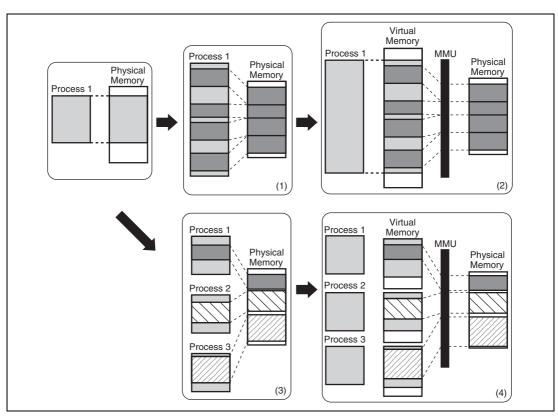

| 5.1  | Role  | of MMU                                                               |  |

|      | 5.1.1 | MMU of This LSI                                                      |  |

| 5.2  | Regis | ter Descriptions                                                     |  |

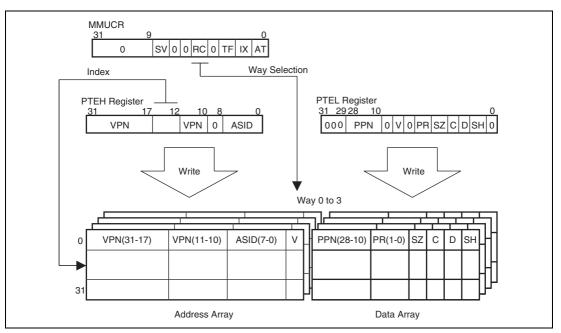

|      | 5.2.1 | Page Table Entry Register High (PTEH)                                |  |

|      | 5.2.2 | Page Table Entry Register Low (PTEL)                                 |  |

|      | 5.2.3 | Translation Table Base Register (TTB)                                |  |

|      | 5.2.4 | MMU Control Register (MMUCR)                                         |  |

| 5.3  | TLB   | Functions                                                            |  |

|      | 5.3.1 | Configuration of the TLB                                             |  |

|      | 5.3.2 | TLB Indexing                                                         |  |

|      | 5.3.3 | TLB Address Comparison                                               |  |

|      | 5.3.4 | Page Management Information                                          |  |

| 5.4  | MMU   | J Functions                                                          |  |

|      | 5.4.1 | MMU Hardware Management                                              |  |

|      | 5.4.2 | MMU Software Management                                              |  |

|      | 5.4.3 | MMU Instruction (LDTLB)                                              |  |

|      | 5.4.4 | Avoiding Synonym Problems                                            |  |

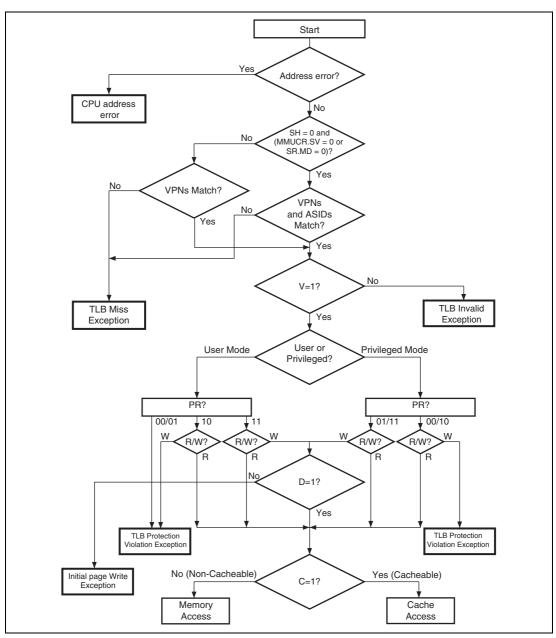

| 5.5  | MMU   | J Exceptions                                                         |  |

|      | 5.5.1 | TLB Miss Exception                                                   |  |

|      | 5.5.2 | TLB Protection Violation Exception                                   |  |

|      | 5.5.3 | TLB Invalid Exception                                                |  |

|      | 5.5.4 | Initial Page Write Exception                                         |  |

|      | 5.5.5 | MMU Exception in Repeat Loop                                         |  |

| 5.6  | Mem   | ory-Mapped TLB                                                       |  |

|      | 5.6.1 | Address Array                                                        |  |

|       | 5.6.2  | Data Array                             |

|-------|--------|----------------------------------------|

|       | 5.6.3  | Usage Examples                         |

| 5.7   | Usage  | 213 Note                               |

|       |        |                                        |

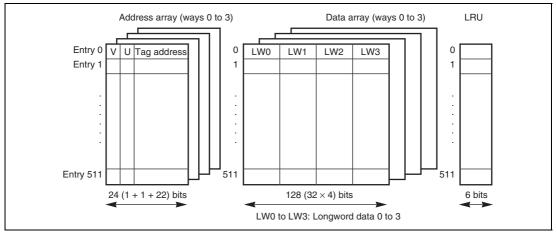

| Secti | on 6   | Cache                                  |

| 6.1   | Featur | res                                    |

|       | 6.1.1  | Cache Structure                        |

| 6.2   | Regist | ter Descriptions                       |

|       | 6.2.1  | Cache Control Register 1 (CCR1)        |

|       | 6.2.2  | Cache Control Register 2 (CCR2)        |

|       | 6.2.3  | Cache Control Register 3 (CCR3)        |

| 6.3   | Opera  | tion                                   |

|       | 6.3.1  | Searching the Cache                    |

|       | 6.3.2  | Read Access                            |

|       | 6.3.3  | Prefetch Operation                     |

|       | 6.3.4  | Write Access                           |

|       | 6.3.5  | Write-Back Buffer                      |

|       | 6.3.6  | Coherency of Cache and External Memory |

| 6.4   | Memo   | pry-Mapped Cache                       |

|       | 6.4.1  | Address Array                          |

|       | 6.4.2  | Data Array                             |

|       | 6.4.3  | Usage Examples                         |

|       |        |                                        |

| Secti | on 7   | X/Y Memory                             |

| 7.1   | Featur | res                                    |

| 7.2   | Opera  | tion                                   |

|       | 7.2.1  | Access from CPU                        |

|       | 7.2.2  | Access from DSP                        |

|       | 7.2.3  | Access from DMAC and E-DMAC            |

| 7.3   | Usage  | 233 Notes                              |

|       | 7.3.1  | Page Conflict                          |

|       | 7.3.2  | Bus Conflict                           |

|       | 7.3.3  | MMU and Cache Settings                 |

|       | 7.3.4  | Sleep Mode                             |

|       | 7.3.5  | Address Error                          |

|       |        |                                        |

| Secti | on 8   | Interrupt Controller (INTC)            |

| 8.1   |        | res                                    |

|       | 8.1.1  | Block Diagram                          |

| 8.2   | Input/ | Output Pins                            |

|       |        |                                        |

| 8.3  | Interru | pt Sources                                         | 237 |

|------|---------|----------------------------------------------------|-----|

|      | 8.3.1   | NMI Interrupt                                      | 237 |

|      | 8.3.2   | IRQ Interrupts                                     | 238 |

|      | 8.3.3   | IRL Interrupts                                     | 238 |

|      | 8.3.4   | On-Chip Peripheral Module Interrupts               | 239 |

|      | 8.3.5   | Interrupt Exception Handling and Priority          | 240 |

| 8.4  | Registe | er Descriptions                                    | 246 |

|      | 8.4.1   | Interrupt Priority Registers A to I (IPRA to IPRI) | 246 |

|      | 8.4.2   | Interrupt Control Register 0 (ICR0)                | 248 |

|      | 8.4.3   | Interrupt Control Register 1 (ICR1)                | 249 |

|      | 8.4.4   | Interrupt Request Register 0 (IRR0)                | 251 |

|      | 8.4.5   | Interrupt Request Register 1 (IRR1)                | 251 |

|      | 8.4.6   | Interrupt Request Register 2 (IRR2)                | 253 |

|      | 8.4.7   | Interrupt Request Register 3 (IRR3)                | 254 |

|      | 8.4.8   | Interrupt Request Register 4 (IRR4)                | 255 |

|      | 8.4.9   | Interrupt Request Register 5 (IRR5)                | 256 |

|      | 8.4.10  | Interrupt Request Register 7 (IRR7)                | 257 |

|      | 8.4.11  | Interrupt Request Register 8 (IRR8)                | 258 |

| 8.5  | Operati | ion                                                | 260 |

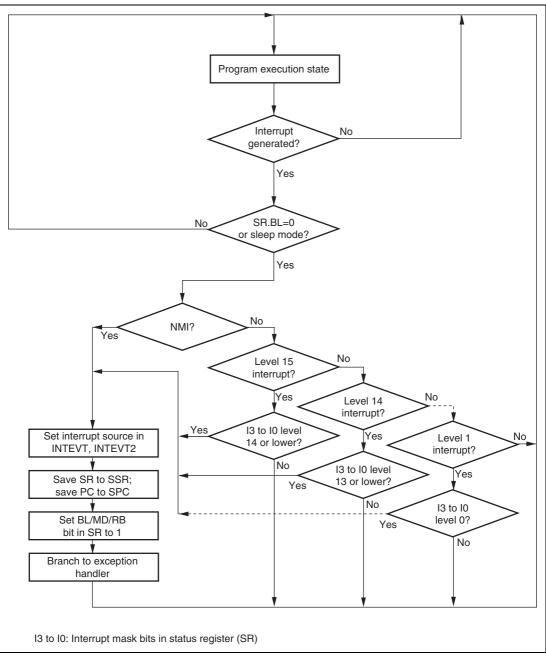

|      | 8.5.1   | Interrupt Sequence                                 | 260 |

|      | 8.5.2   | Multiple Interrupts                                | 262 |

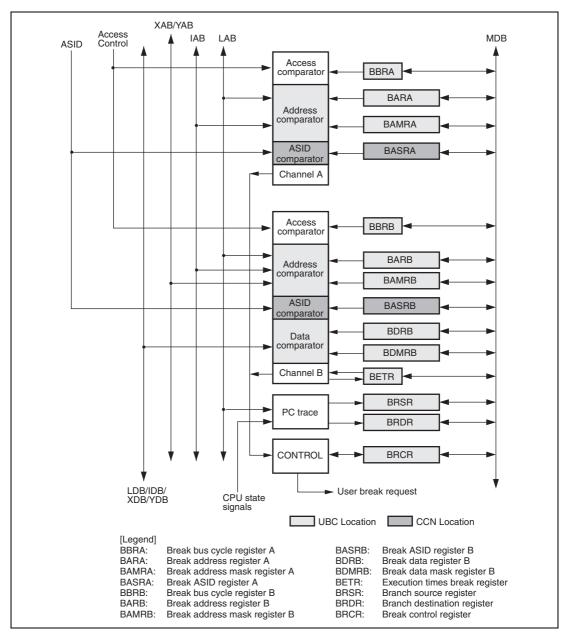

| Soot | on 9    | User Break Controller                              | 263 |

|      |         |                                                    |     |

| 9.1  |         | es                                                 |     |

| 9.2  | U       | er Descriptions                                    |     |

|      | 9.2.1   | Break Address Register A (BARA)                    |     |

|      | 9.2.2   | Break Address Mask Register A (BAMRA)              |     |

|      | 9.2.3   | Break Bus Cycle Register A (BBRA)                  |     |

|      | 9.2.4   | Break Address Register B (BARB)                    |     |

|      | 9.2.5   | Break Address Mask Register B (BAMRB)              |     |

|      | 9.2.6   | Break Data Register B (BDRB)                       |     |

|      | 9.2.7   | Break Data Mask Register B (BDMRB)                 |     |

|      | 9.2.8   | Break Bus Cycle Register B (BBRB)                  |     |

|      | 9.2.9   | Break Control Register (BRCR)                      |     |

|      | 9.2.10  | 8 ( )                                              |     |

|      | 9.2.11  | Branch Source Register (BRSR)                      |     |

|      |         | Branch Destination Register (BRDR)                 |     |

|      |         | Break ASID Register A (BASRA)                      |     |

|      |         | Break ASID Register B (BASRB)                      |     |

| 9.3  | 0       | ion                                                | 201 |

|       | 9.3.1     | Flow of the User Break Operation    | 281 |

|-------|-----------|-------------------------------------|-----|

|       | 9.3.2     | Break on Instruction Fetch Cycle    | 283 |

|       | 9.3.3     | Break on Data Access Cycle          | 283 |

|       | 9.3.4     | Break on X/Y-Memory Bus Cycle       | 285 |

|       | 9.3.5     | Sequential Break                    | 285 |

|       | 9.3.6     | Value of Saved Program Counter      | 286 |

|       | 9.3.7     | PC Trace                            | 287 |

|       | 9.3.8     | Usage Examples                      | 287 |

| 9.4   | Usage I   | Notes                               | 292 |

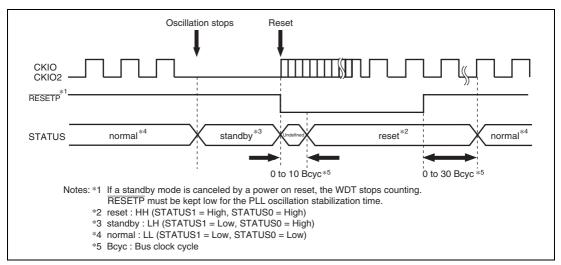

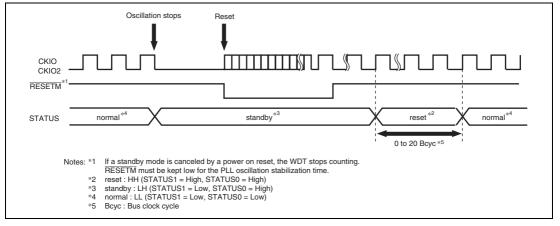

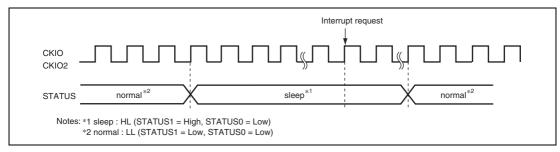

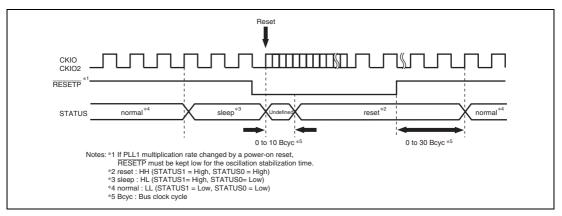

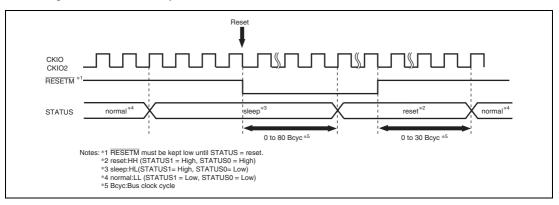

| Secti | on 10     | Power-Down Modes                    | 295 |

| 10.1  | Overvie   | ew                                  | 295 |

|       | 10.1.1    | Power-Down Modes                    | 295 |

|       | 10.1.2    | Reset                               | 296 |

|       | 10.1.3    | Input/Output Pins                   | 298 |

| 10.2  |           | r Descriptions                      |     |

|       | 10.2.1    | Standby Control Register (STBCR)    | 298 |

|       | 10.2.2    |                                     |     |

|       | 10.2.3    | Standby Control Register 3 (STBCR3) | 301 |

| 10.3  | Operation |                                     |     |

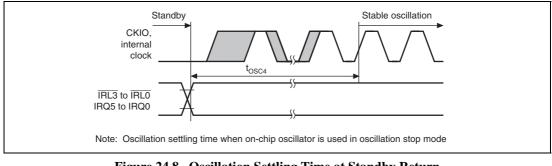

|       | 10.3.1    | Sleep Mode                          | 302 |

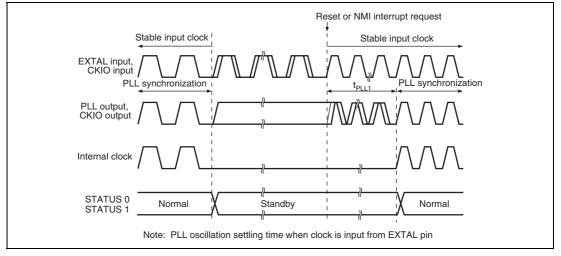

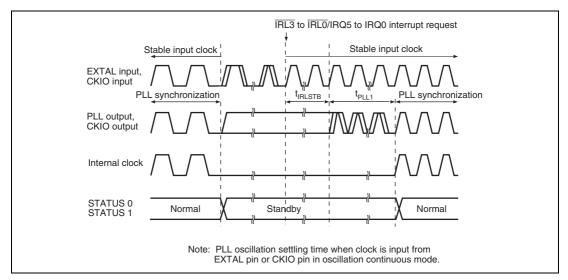

|       | 10.3.2    | Software Standby Mode               | 303 |

|       | 10.3.3    | Module Standby Function             | 305 |

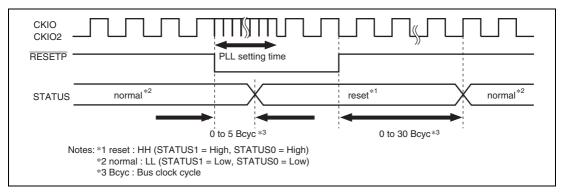

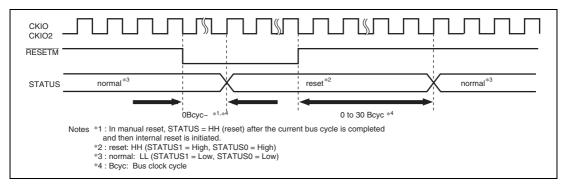

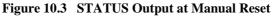

|       | 10.3.4    | STATUS Pin Change Timings           | 306 |

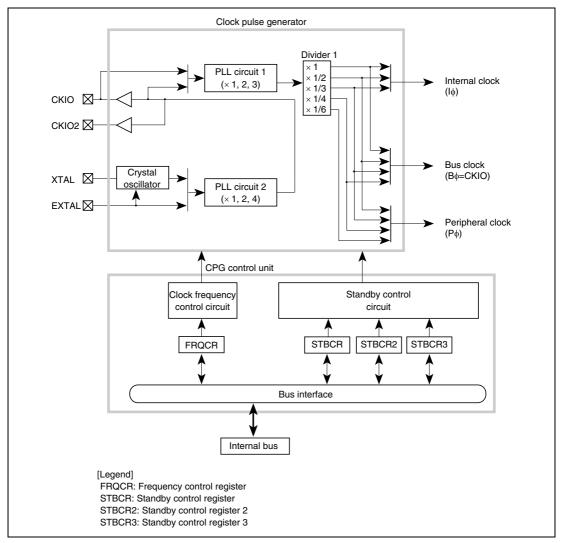

| Secti | on 11     | On-Chip Oscillation Circuits        | 311 |

| 11.1  | Overvi    | 2<br>EW                             |     |

|       | 11.1.1    | Features                            | 311 |

| 11.2  | Overvie   | ew of CPG                           | 313 |

|       | 11.2.1    | CPG Block Diagram                   | 313 |

|       |           | Input/Output Pins                   |     |

| 11.3  |           | Deperating Modes                    |     |

| 11.4  | Registe   | r Description                       | 320 |

|       | 11.4.1    | Frequency Control Register (FRQCR)  | 320 |

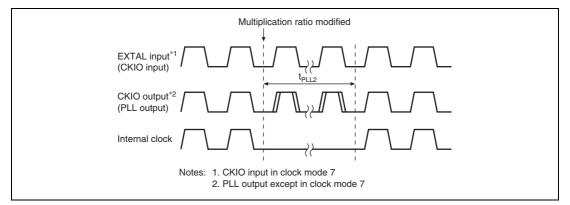

| 11.5  |           | ng Frequency                        |     |

|       | 11.5.1    | Changing Multiplication Rate        | 322 |

|       |           | Changing Division Ratio             |     |

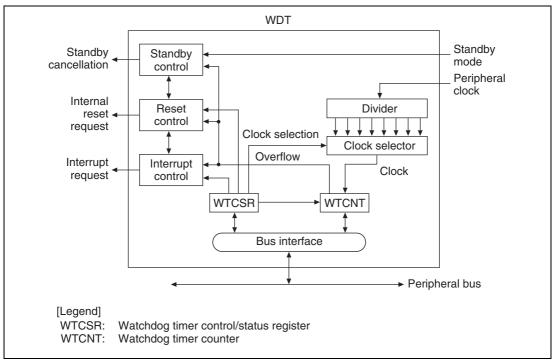

| 11.6  |           | ew of WDT                           |     |

|       | 11.6.1    | Block Diagram of WDT                | 323 |

| 11.7  | Registe   | r Descriptions of WDT               | 324 |

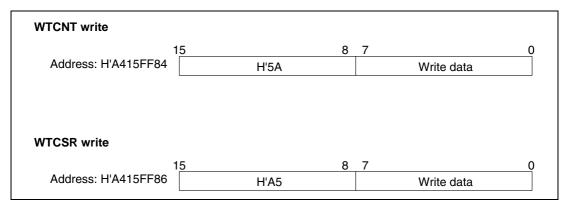

|       | 11.7.1  | Watchdog Timer Counter (WTCNT)                                            | . 324 |

|-------|---------|---------------------------------------------------------------------------|-------|

|       | 11.7.2  | Watchdog Timer Control/Status Register (WTCSR)                            | . 324 |

|       | 11.7.3  | Notes on Register Access                                                  | . 326 |

| 11.8  | Using V | NDT                                                                       | . 327 |

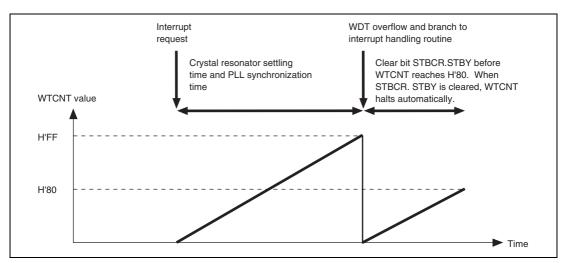

|       | 11.8.1  | Canceling Standbys                                                        | . 327 |

|       | 11.8.2  | Changing Frequency                                                        | . 328 |

|       | 11.8.3  | Using Watchdog Timer Mode                                                 | . 328 |

|       | 11.8.4  | Using Interval Timer Mode                                                 | . 328 |

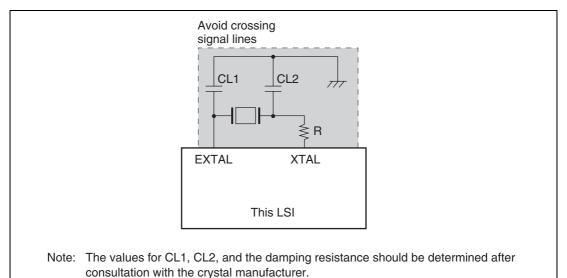

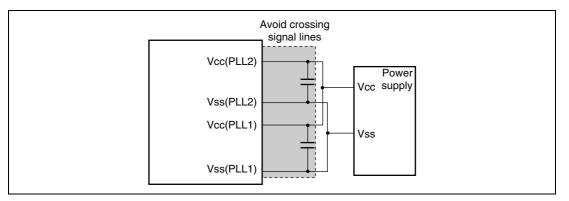

| 11.9  | Notes o | n Board Design                                                            | . 329 |

|       |         |                                                                           |       |

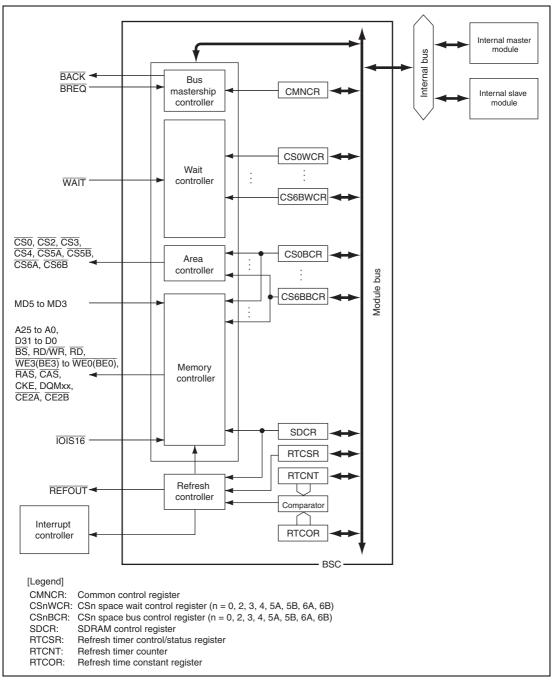

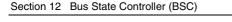

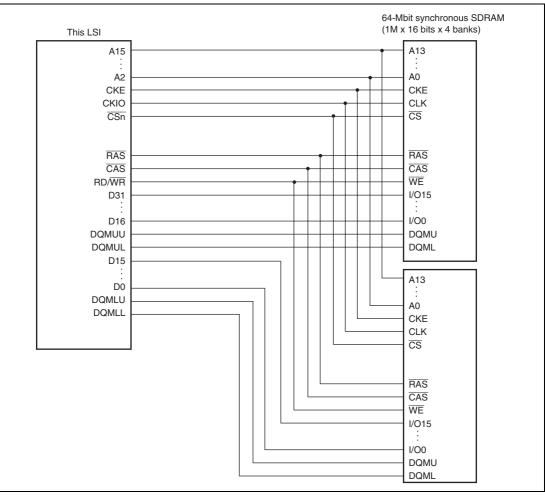

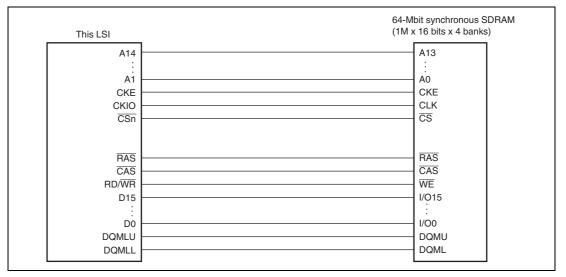

| Secti | on 12   | Bus State Controller (BSC)                                                | 331   |

| 12.1  |         | S                                                                         |       |

| 12.2  | Input/O | Output Pins                                                               | . 334 |

| 12.3  |         | verview                                                                   |       |

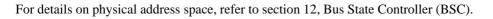

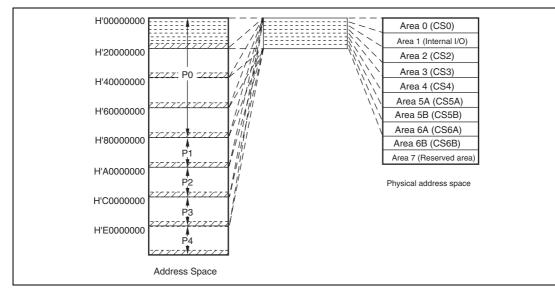

|       |         | Area Division                                                             |       |

|       | 12.3.2  | Shadow Area                                                               | . 336 |

|       | 12.3.3  | Address Map                                                               | . 338 |

|       | 12.3.4  | Area 0 Memory Type and Memory Bus Width                                   | . 340 |

|       | 12.3.5  | Data Alignment                                                            | . 340 |

| 12.4  | Registe | r Descriptions                                                            | . 341 |

|       | 12.4.1  | Common Control Register (CMNCR)                                           | . 342 |

|       | 12.4.2  | CSn Space Bus Control Register (CSnBCR) (n = 0, 2, 3, 4, 5A, 5B, 6A, 6B)  | . 345 |

|       | 12.4.3  | CSn Space Wait Control Register (CSnWCR) (n = 0, 2, 3, 4, 5A, 5B, 6A, 6B) | . 351 |

|       | 12.4.4  | SDRAM Control Register (SDCR)                                             | . 378 |

|       | 12.4.5  | Refresh Timer Control/Status Register (RTCSR)                             | . 381 |

|       | 12.4.6  | Refresh Timer Counter (RTCNT)                                             | . 382 |

|       | 12.4.7  | Refresh Time Constant Register (RTCOR)                                    | . 383 |

| 12.5  | Operati | on                                                                        | . 384 |

|       | 12.5.1  | Endian/Access Size and Data Alignment                                     | . 384 |

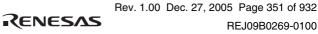

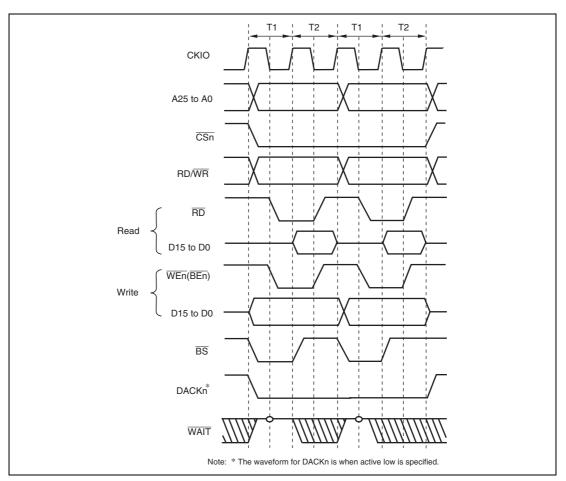

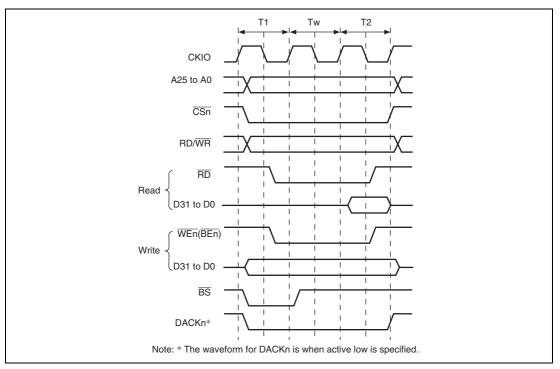

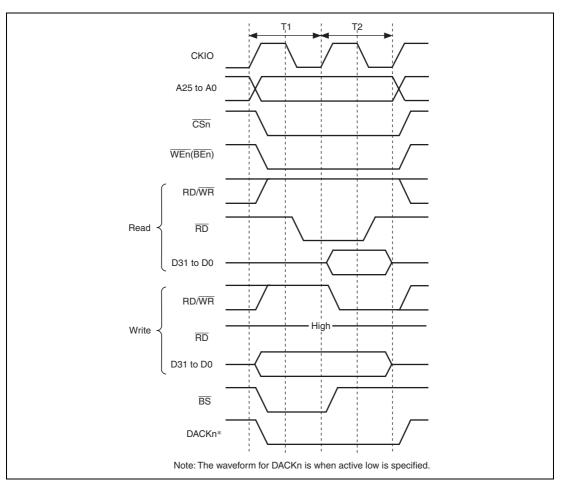

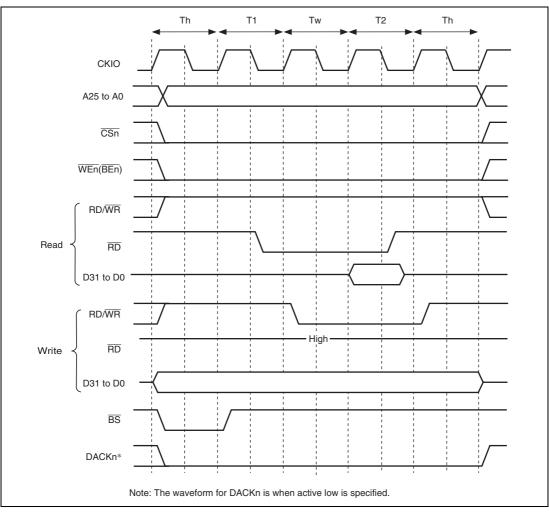

|       | 12.5.2  | Normal Space Interface                                                    | . 390 |

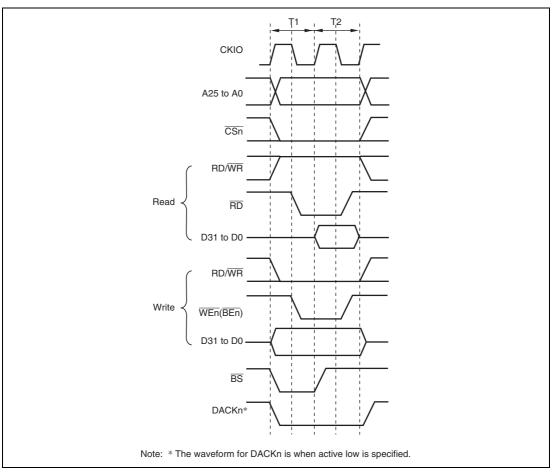

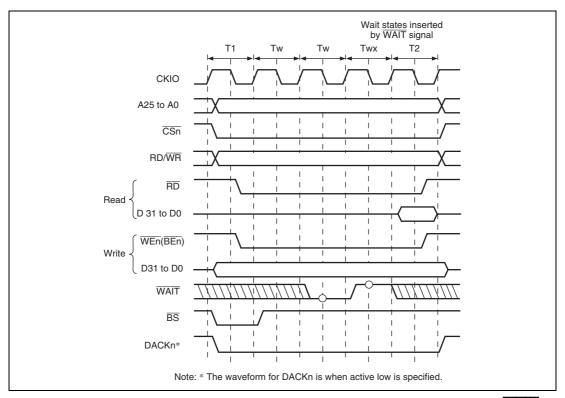

|       | 12.5.3  | Access Wait Control                                                       | . 396 |

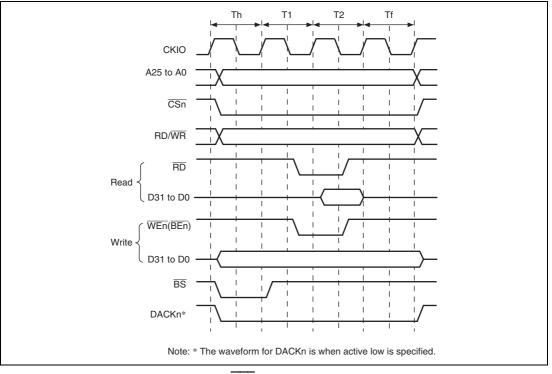

|       | 12.5.4  | CSn Assert Period Expansion                                               | . 398 |

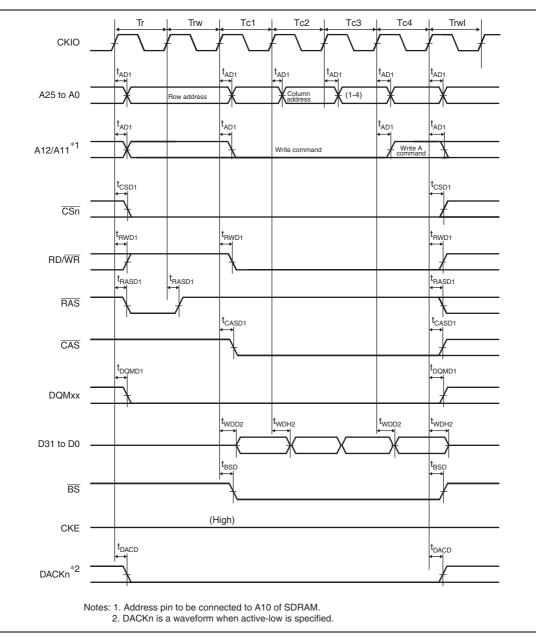

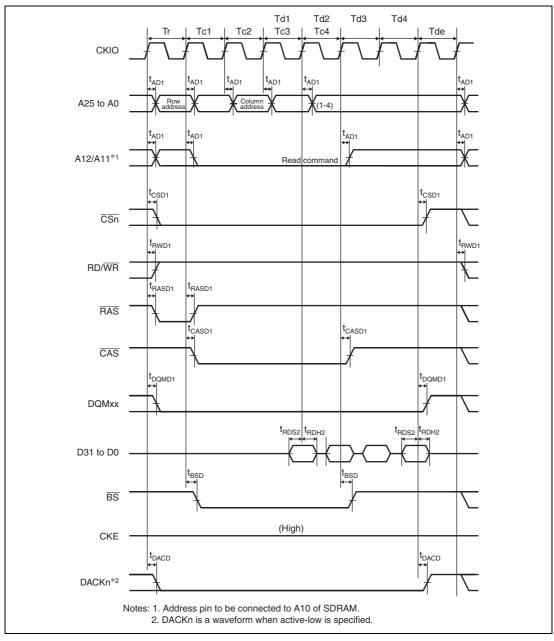

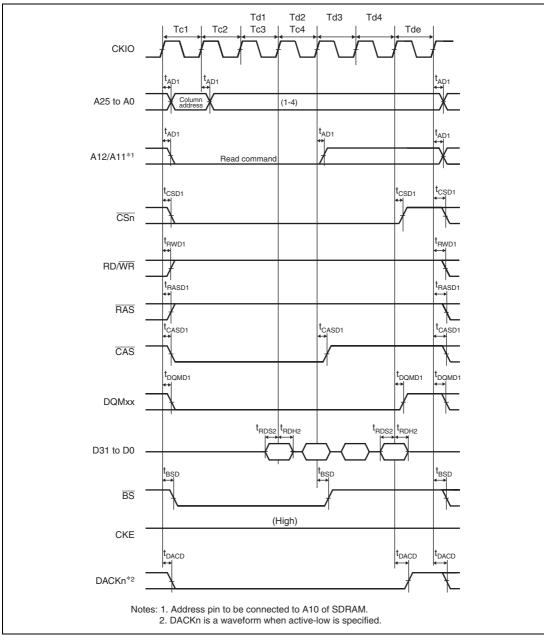

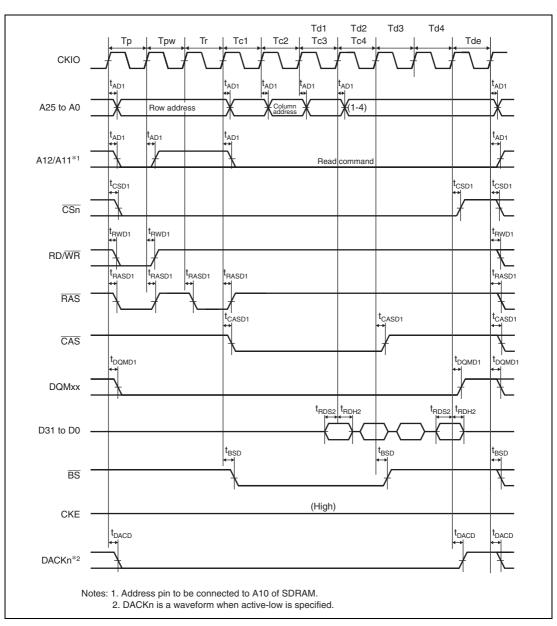

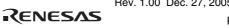

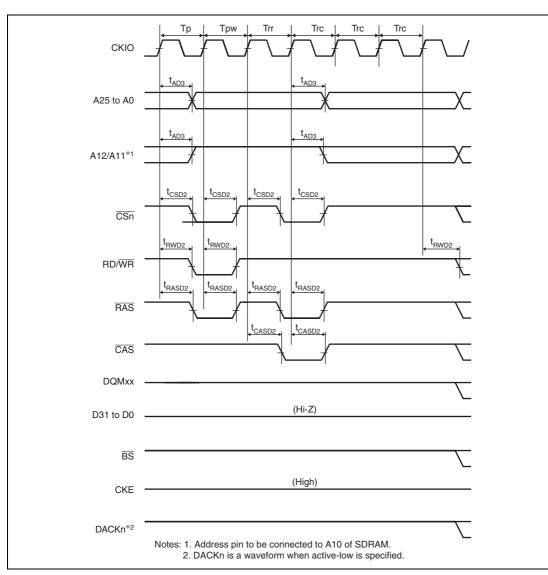

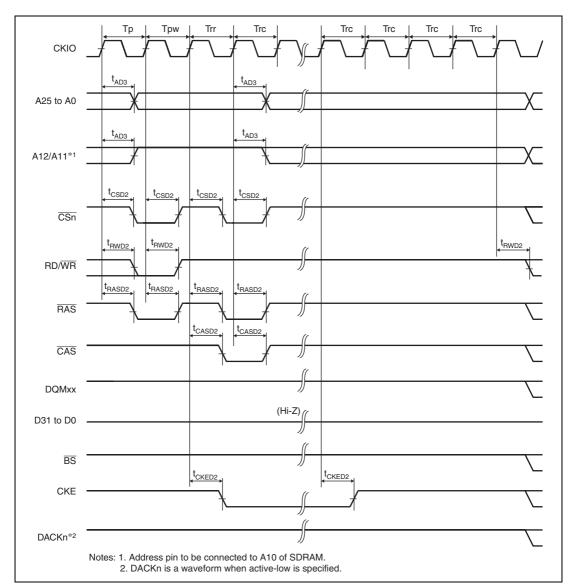

|       | 12.5.5  | SDRAM Interface                                                           | . 399 |

|       | 12.5.6  | Burst ROM (Clock Asynchronous) Interface                                  | . 440 |

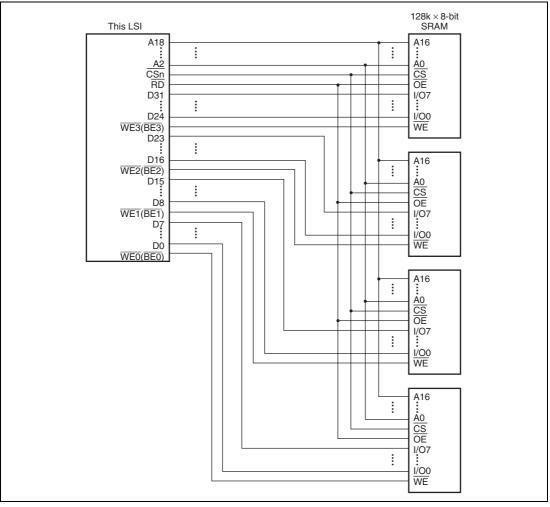

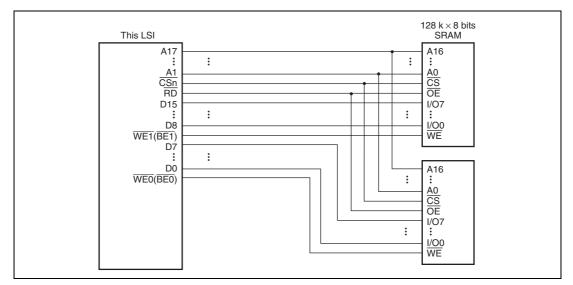

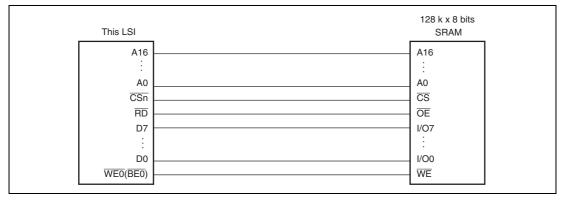

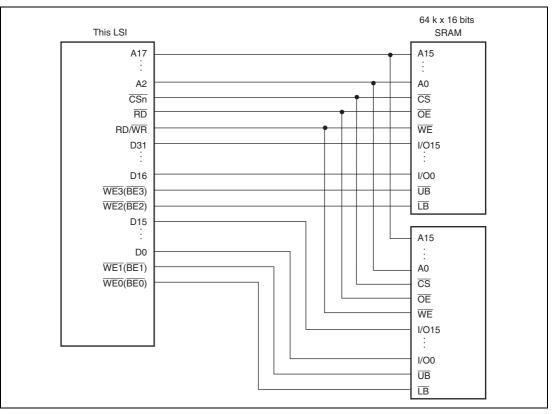

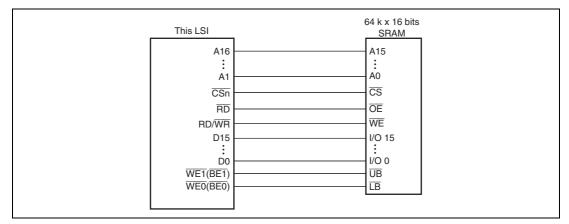

|       | 12.5.7  | Byte-Selection SRAM Interface                                             | . 442 |

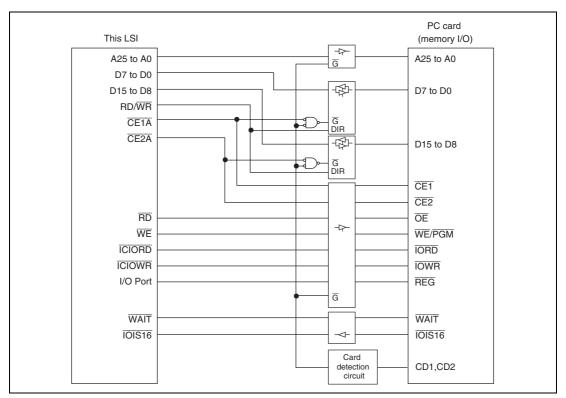

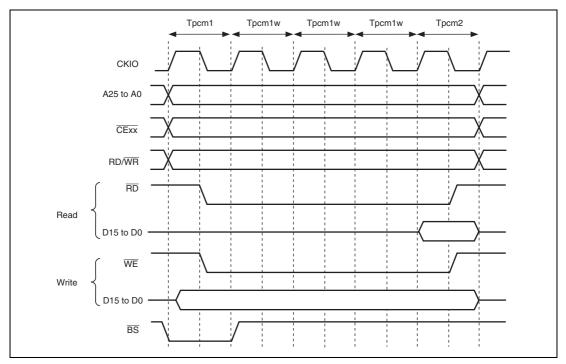

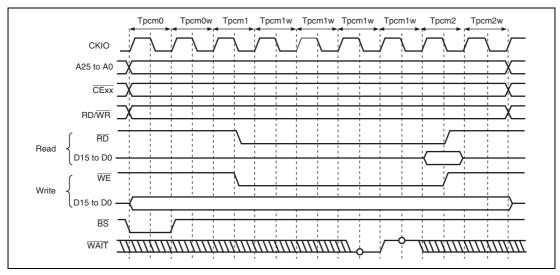

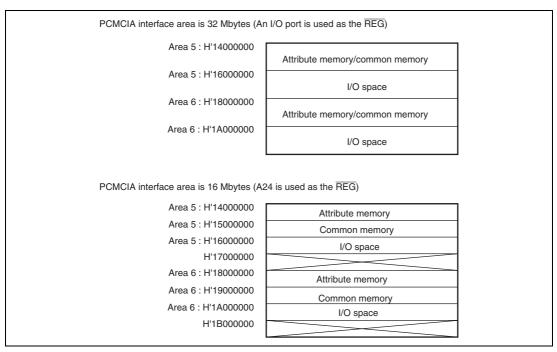

|       | 12.5.8  | PCMCIA Interface                                                          | . 447 |

|       | 12.5.9  | Burst ROM (Clock Synchronous) Interface                                   | . 453 |

|       |         | Wait between Access Cycles                                                |       |

|       | 12.5.11 | Bus Arbitration                                                           | . 454 |

|       | 12.5.12 | Others                                                                    | . 456 |

| Sect | ion 13   | Direct Memory Access Controller (DMAC)                    |      |

|------|----------|-----------------------------------------------------------|------|

| 13.1 |          | 28                                                        |      |

| 13.2 | Input/C  | Dutput Pins                                               |      |

| 13.3 | Registe  | er Descriptions                                           |      |

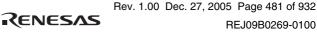

|      | 13.3.1   | DMA Source Address Register (SAR)                         |      |

|      | 13.3.2   | DMA Destination Address Register (DAR)                    |      |

|      | 13.3.3   | DMA Transfer Count Register (DMATCR)                      |      |

|      | 13.3.4   | DMA Channel Control Register (CHCR)                       |      |

|      | 13.3.5   | DMA Operation Register (DMAOR)                            |      |

|      | 13.3.6   | DMA Extension Resource Selector 0 to 2 (DMARS0 to DMARS2) |      |

| 13.4 | Operat   | ion                                                       |      |

|      | 13.4.1   | DMA Transfer Flow                                         |      |

|      | 13.4.2   | DMA Transfer Requests                                     |      |

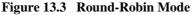

|      | 13.4.3   | Channel Priority                                          |      |

|      | 13.4.4   | DMA Transfer Types                                        |      |

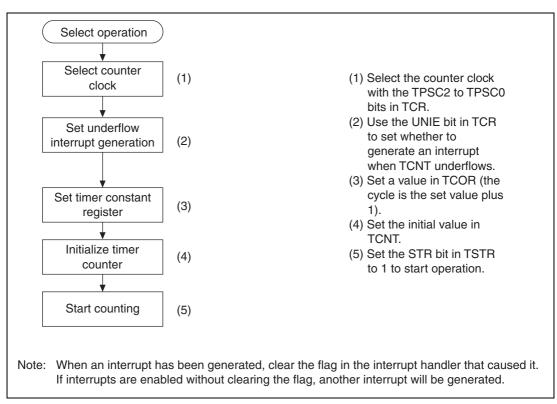

|      | 13.4.5   | Number of Bus Cycle States and DREQ Pin Sampling Timing   |      |

| 13.5 | Usage    | Note                                                      |      |

| ~    |          |                                                           | 40.7 |

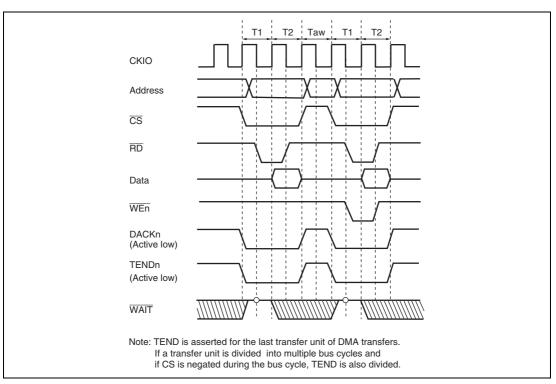

|      |          | Timer Unit (TMU)                                          |      |

| 14.1 |          | 28                                                        |      |

|      |          | Block Diagram                                             |      |

| 14.2 | -        | er Descriptions                                           |      |

|      |          | Timer Start Register (TSTR)                               |      |

|      |          | Timer Control Registers (TCR)                             |      |

|      |          | Timer Constant Registers (TCOR)                           |      |

|      |          | Timer Counters (TCNT)                                     |      |

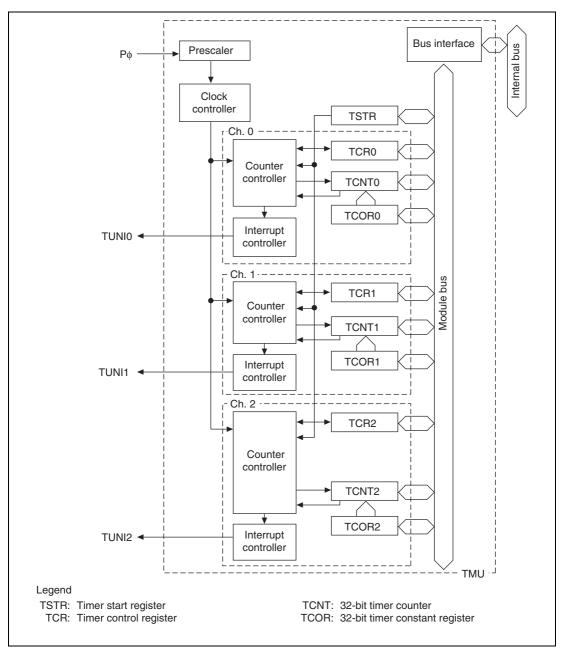

| 14.3 |          | Dperation                                                 |      |

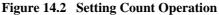

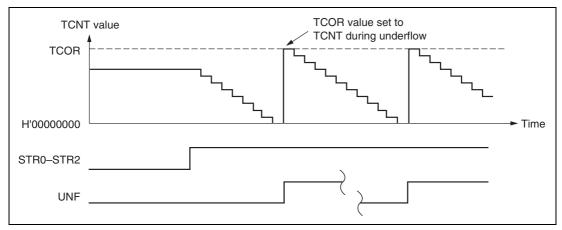

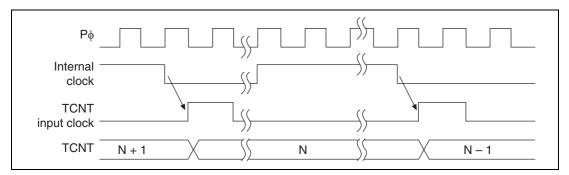

|      |          | Counter Operation                                         |      |

| 14.4 | Interru  | pts                                                       |      |

|      | 14.4.1   | 8 8                                                       |      |

|      | 14.4.2   | 8 8                                                       |      |

|      | 14.4.3   | Interrupt Sources and Priorities                          | 504  |

| 14.5 | -        | Notes                                                     |      |

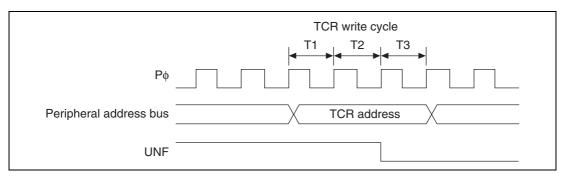

|      |          | Writing to Registers                                      |      |

|      | 14.5.2   | Reading Registers                                         | 504  |

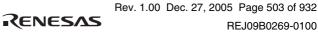

| Sect | ion 15   | Realtime Clock (RTC)                                      | 505  |

| 15.1 |          | - Ксанпис Сюск (КТС)                                      |      |

| 15.2 |          | Dutput Pins                                               |      |

| 15.3 | -        | er Descriptions                                           |      |

| 10.0 | 1.051010 |                                                           |      |

|      | 15.3.1  | 64-Hz Counter (R64CNT)                            | 508 |

|------|---------|---------------------------------------------------|-----|

|      | 15.3.2  | Second Counter (RSECCNT)                          | 508 |

|      | 15.3.3  | Minute Counter (RMINCNT)                          | 509 |

|      | 15.3.4  | Hour Counter (RHRCNT)                             | 509 |

|      | 15.3.5  | Day of Week Counter (RWKCNT)                      |     |

|      |         | Date Counter (RDAYCNT)                            |     |

|      | 15.3.7  | Month Counter (RMONCNT)                           |     |

|      | 15.3.8  | Year Counter (RYRCNT)                             |     |

|      | 15.3.9  | Second Alarm Register (RSECAR)                    |     |

|      | 15.3.10 | ) Minute Alarm Register (RMINAR)                  |     |

|      | 15.3.11 | Hour Alarm Register (RHRAR)                       | 515 |

|      | 15.3.12 | 2 Day of Week Alarm Register (RWKAR)              | 516 |

|      | 15.3.13 | B Date Alarm Register (RDAYAR)                    |     |

|      | 15.3.14 | Month Alarm Register (RMONAR)                     | 518 |

|      |         | 5 Year Alarm Register (RYRAR)                     |     |

|      | 15.3.16 | 5 RTC Control Register 1 (RCR1)                   |     |

|      | 15.3.17 | 7 RTC Control Register 2 (RCR2)                   |     |

|      |         | B RTC Control Register 3 (RCR3)                   |     |

| 15.4 | -       | ion                                               |     |

|      | 15.4.1  | Initial Settings of Registers after Power-On      | 525 |

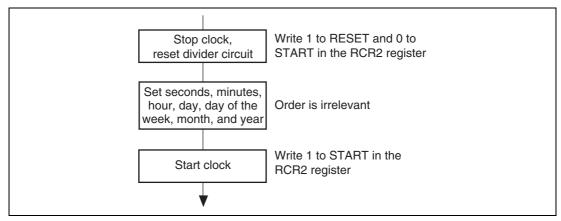

|      | 15.4.2  | Setting Time                                      |     |

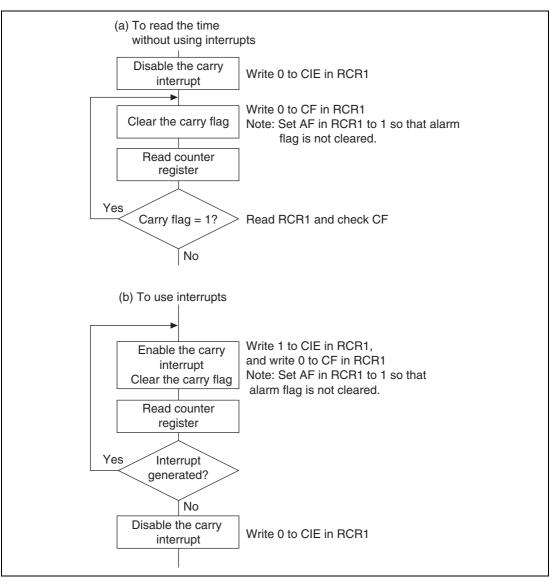

|      | 15.4.3  | Reading Time                                      |     |

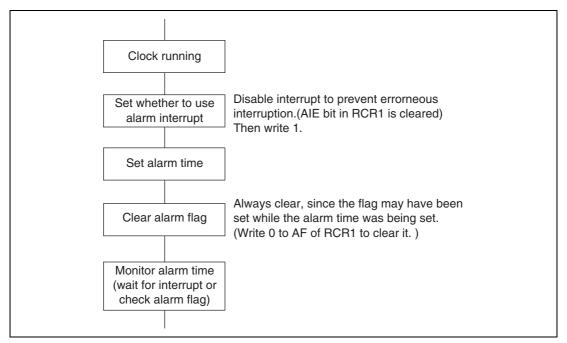

|      |         | Alarm Function                                    |     |

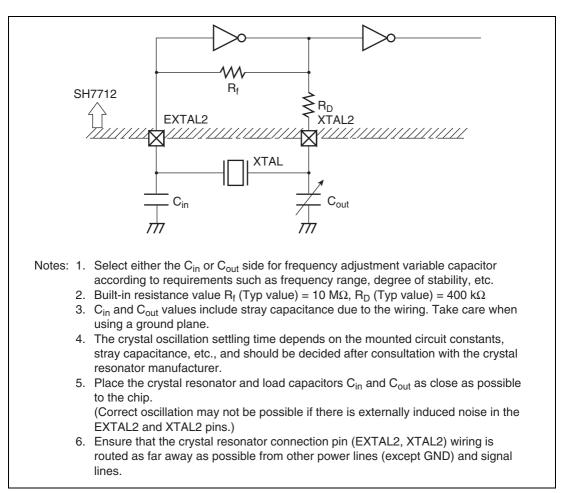

|      | 15.4.5  | Crystal Oscillator Circuit                        |     |

| 15.5 | U       | Notes                                             |     |

|      | 15.5.1  | Register Writing during RTC Count                 |     |

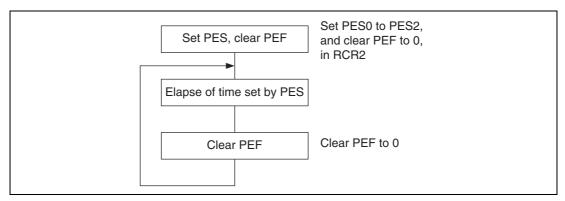

|      |         | Use of Realtime Clock (RTC) Periodic Interrupts   |     |

|      |         | Transition to Standby Mode after Setting Register |     |

|      | 15.5.4  | Usage Note about RTC Power Supply                 | 530 |

|      |         |                                                   |     |

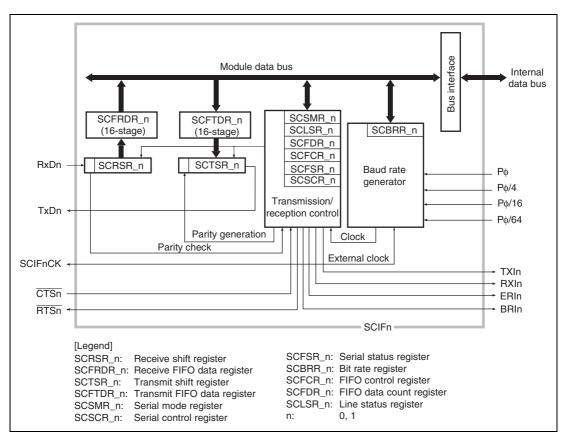

|      |         | Serial Communication Interface with FIFO (SCIF)   |     |

| 16.1 |         | 28                                                |     |

| 16.2 |         | Dutput Pins                                       |     |

| 16.3 | -       | er Descriptions                                   |     |

|      |         | Receive Shift Register (SCRSR)                    |     |

|      |         | Receive FIFO Data Register (SCFRDR)               |     |

|      |         | Transmit Shift Register (SCTSR)                   |     |

|      |         | Transmit FIFO Data Register (SCFTDR)              |     |

|      |         | Serial Mode Register (SCSMR)                      |     |

|      | 16.3.6  | Serial Control Register (SCSCR)                   | 541 |

|       | 16.3.7  | Serial Status Register (SCFSR)                |     |

|-------|---------|-----------------------------------------------|-----|

|       | 16.3.8  | Bit Rate Register (SCBRR)                     | 553 |

|       | 16.3.9  | FIFO Control Register (SCFCR)                 | 554 |

|       | 16.3.10 | FIFO Data Count Register (SCFDR)              | 556 |

|       | 16.3.11 | Line Status Register (SCLSR)                  | 558 |

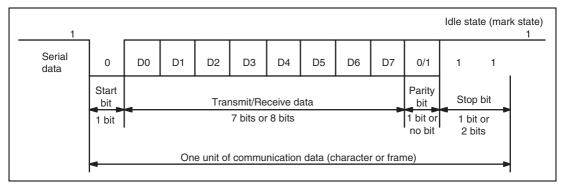

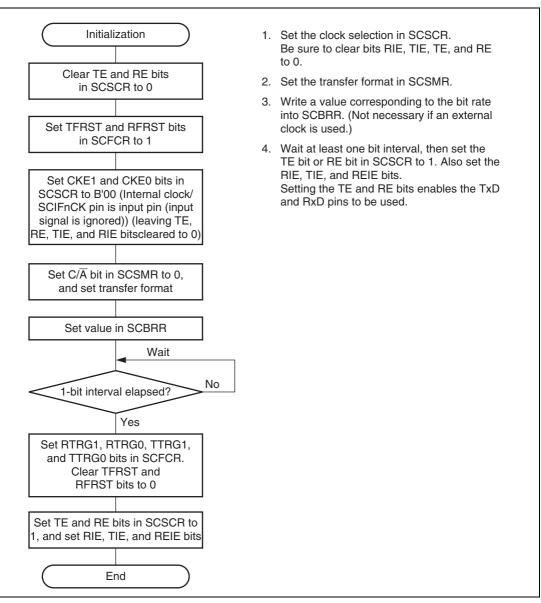

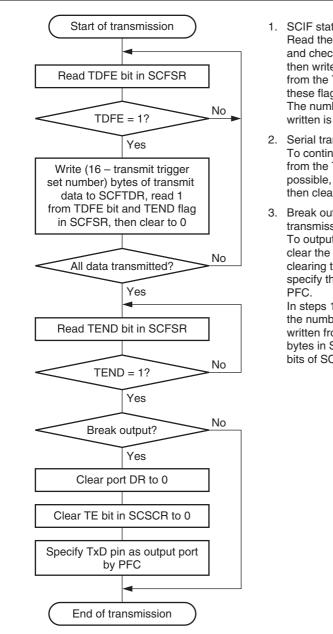

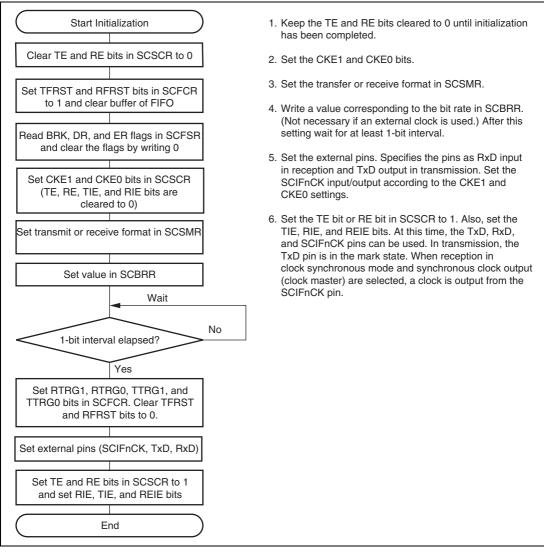

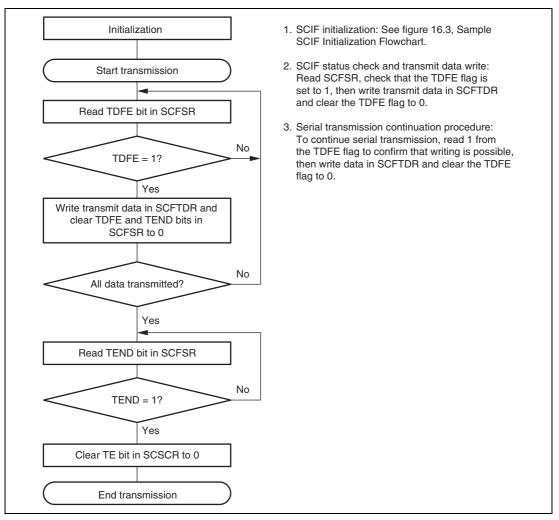

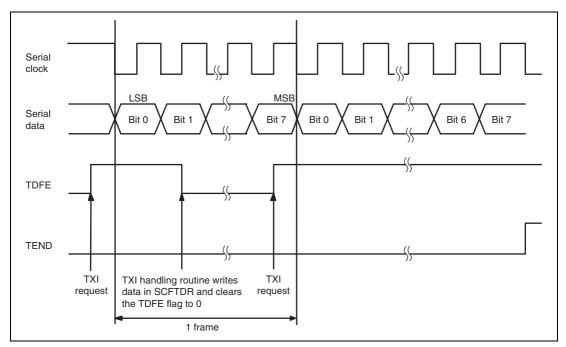

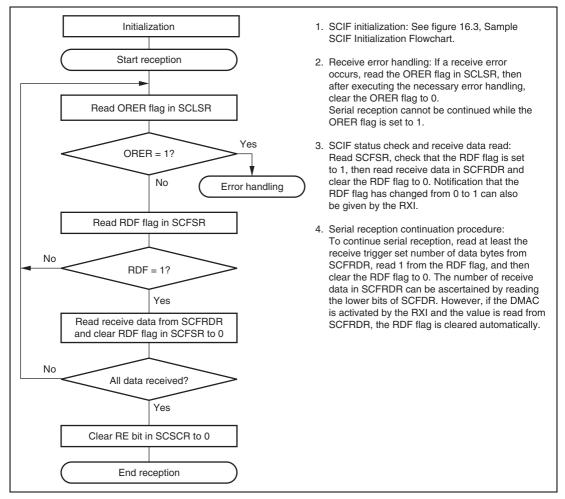

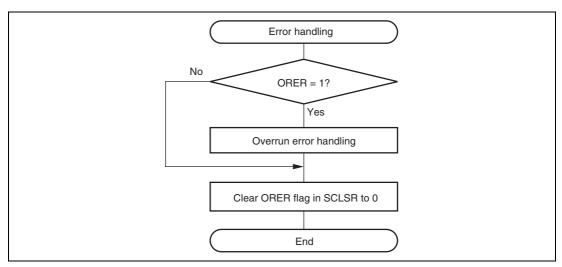

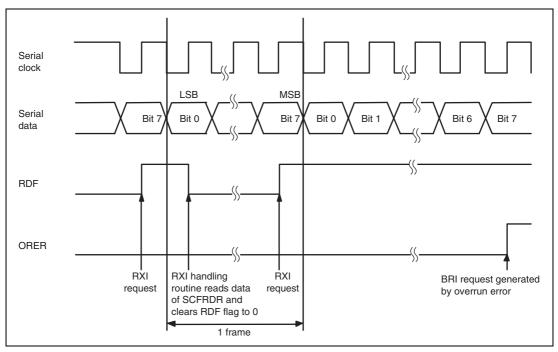

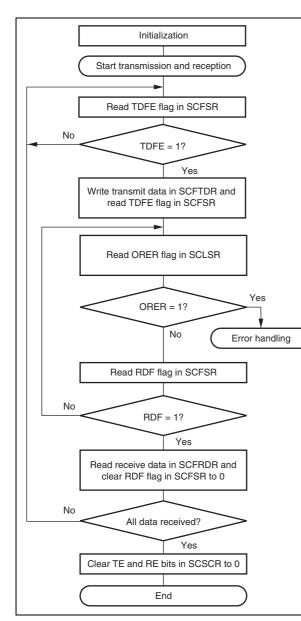

| 16.4  | Operati | on                                            | 559 |

|       | 16.4.1  | Overview                                      | 559 |

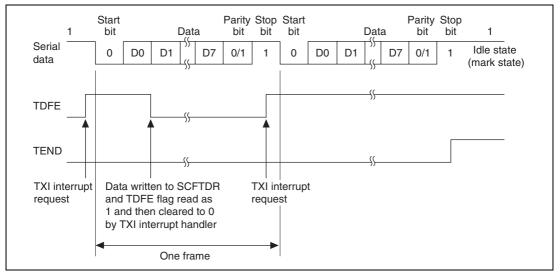

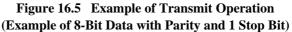

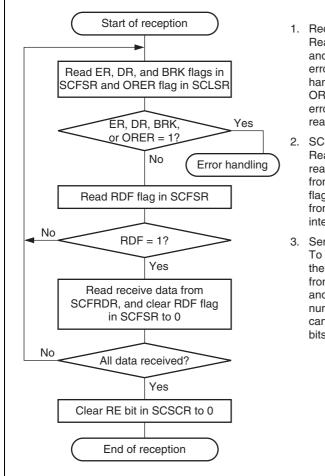

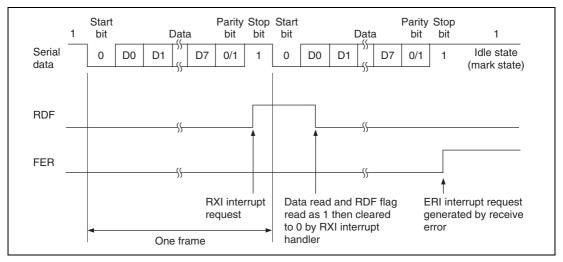

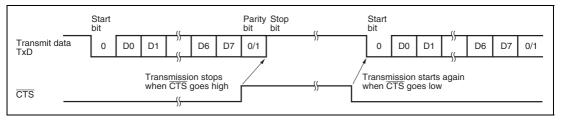

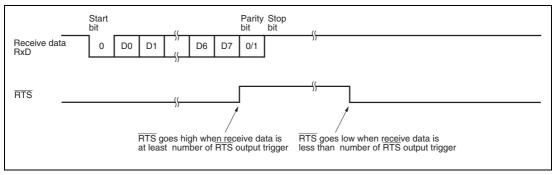

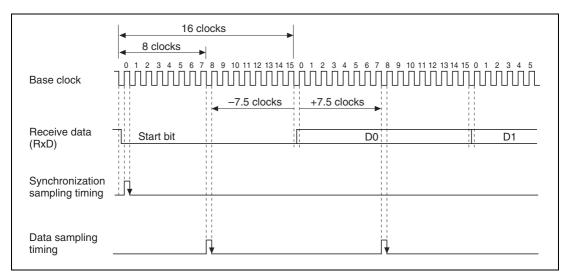

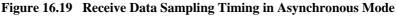

|       | 16.4.2  | Serial Operation in Asynchronous Mode         | 561 |

|       | 16.4.3  | Serial Operation in Clock Synchronous Mode    | 572 |

| 16.5  | SCIF Ir | nterrupt Sources and DMAC                     | 582 |

| 16.6  | Usage 1 | Notes                                         |     |

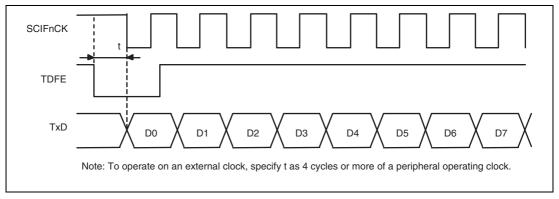

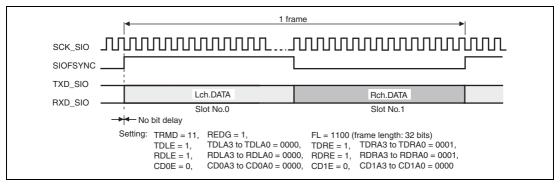

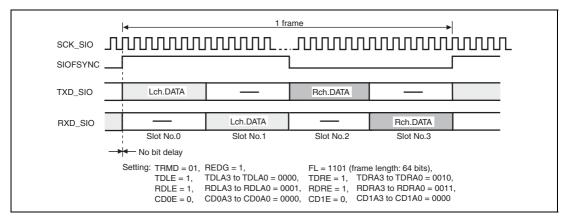

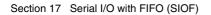

| Secti | on 17   | Serial I/O with FIFO (SIOF)                   | 587 |

| 17.1  |         | ·S                                            |     |

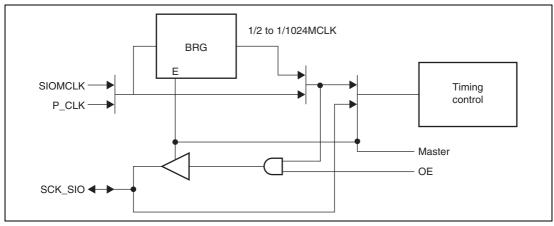

|       |         | Block Diagram                                 |     |

| 17.2  |         | Dutput Pins                                   |     |

| 17.3  | -       | r Descriptions                                |     |

|       | -       | SIOF Mode Register (SIMDR)                    |     |

|       | 17.3.2  |                                               |     |

|       | 17.3.3  |                                               |     |

|       | 17.3.4  |                                               |     |

|       | 17.3.5  |                                               |     |

|       |         | SIOF Control Register (SICTR)                 |     |

|       | 17.3.7  |                                               |     |

|       | 17.3.8  |                                               |     |

|       | 17.3.9  | -                                             |     |

|       | 17.3.10 | Serial Transmit Data Register (SITDR)         |     |

|       |         | Serial Receive Data Register (SIRDR)          |     |

|       |         | Serial Transmit Control Data Register (SITCR) |     |

|       |         | Serial Receive Control Data Register (SIRCR)  |     |

| 17.4  |         | on                                            |     |

|       | 17.4.1  |                                               |     |

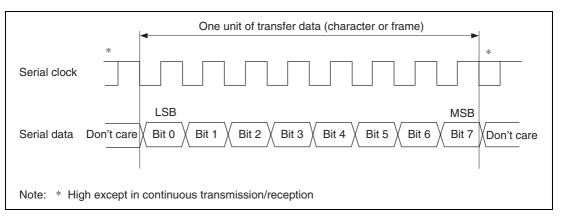

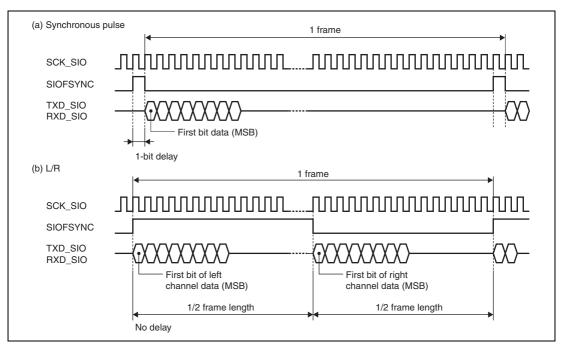

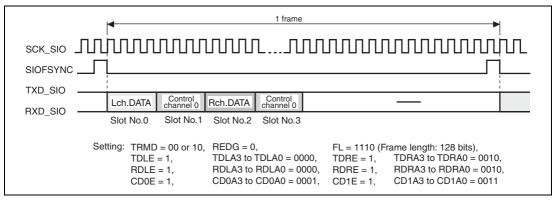

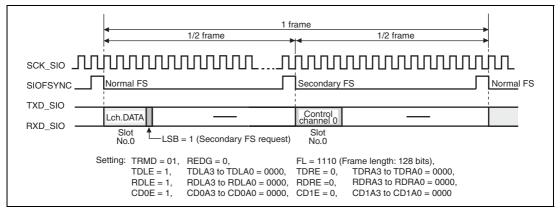

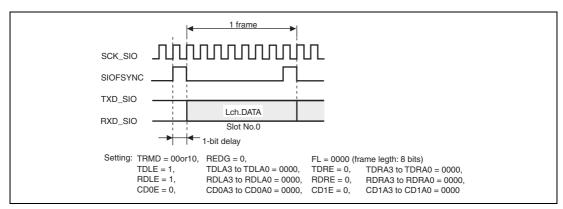

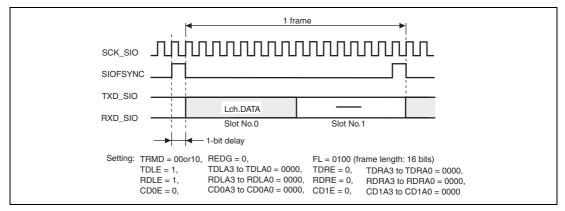

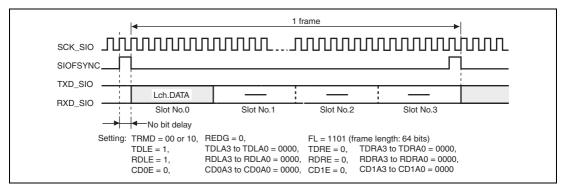

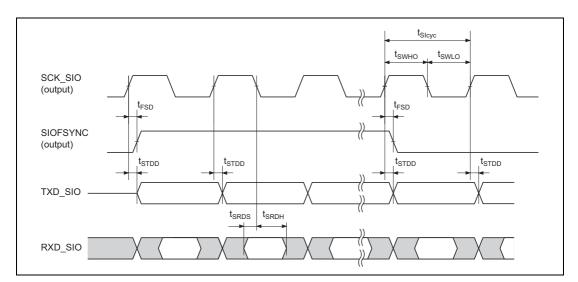

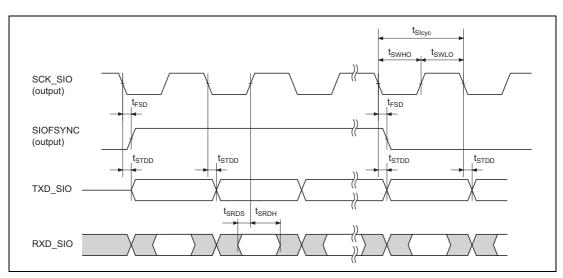

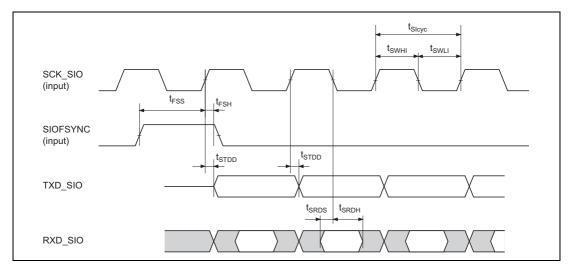

|       | 17.4.2  | Serial Timing                                 | 614 |

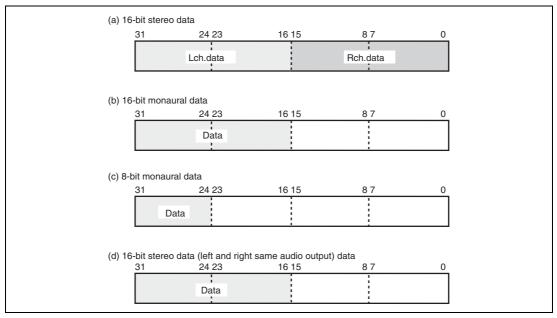

|       |         | Transfer Data Format                          |     |

|       |         | Register Allocation of Transfer Data          |     |

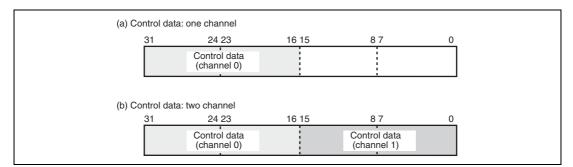

|       | 17.4.5  | Control Data Interface                        |     |

|       |         | FIFO                                          |     |

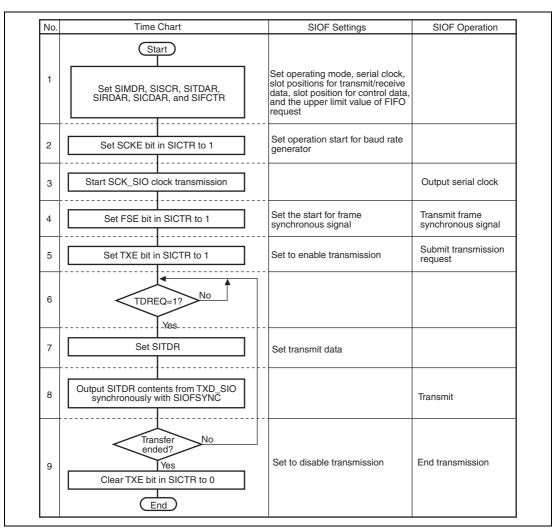

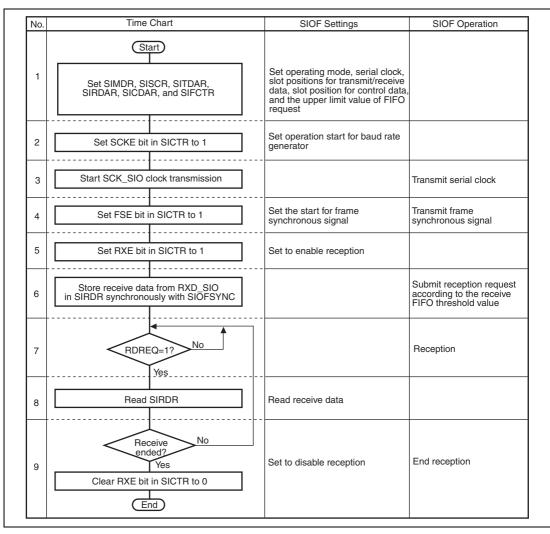

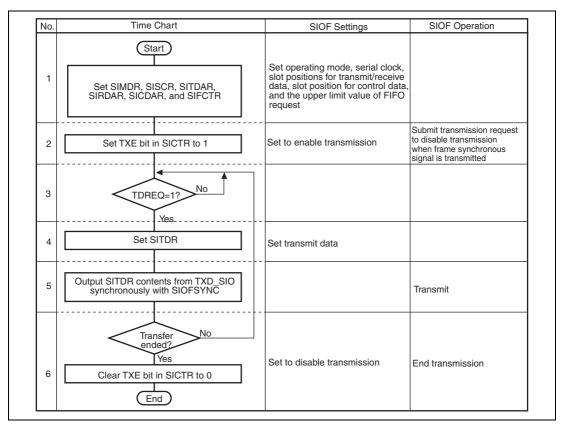

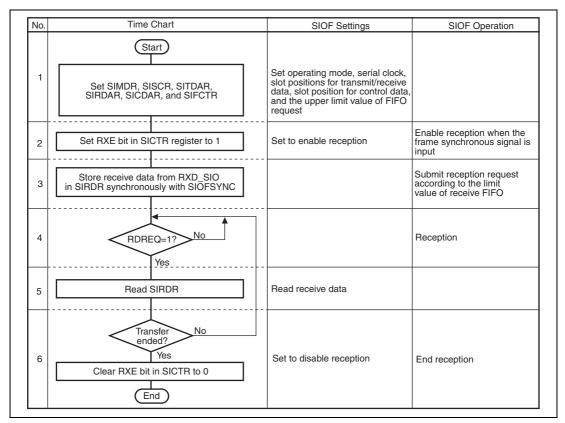

|       | 17.4.7  | Transmission and Reception Procedures         |     |

|       | 17.4.8  | Interrupts                                    |     |

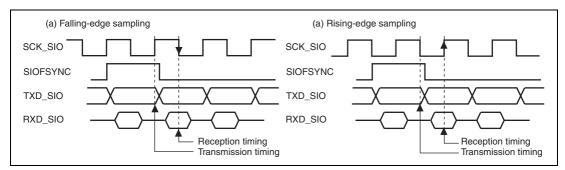

|       |         | Transmission and Reception Timing             |     |

|       |         | · · · · · · · · · · · · · · · · · · ·         |     |

| 17.5  | Usage 1 | Notes                                                               | 635 |

|-------|---------|---------------------------------------------------------------------|-----|

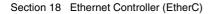

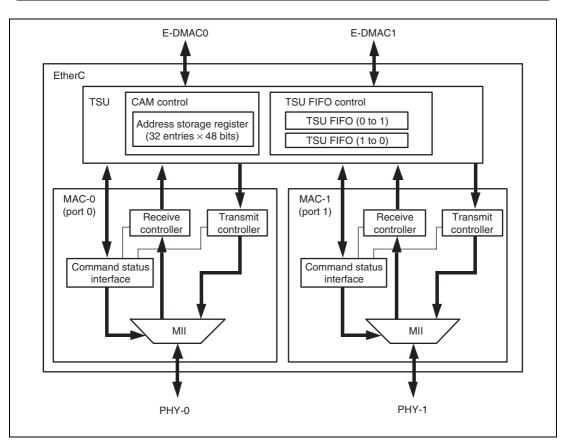

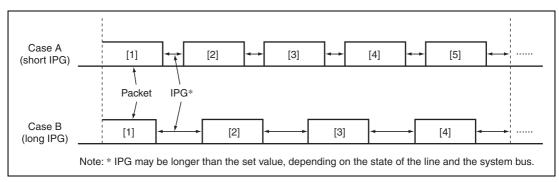

| Secti | ion 18  | Ethernet Controller (EtherC)                                        | 637 |

| 18.1  |         | 55                                                                  |     |

| 18.2  |         | Output Pins                                                         |     |

| 18.3  | Registe | r Descriptions                                                      | 641 |

|       | 18.3.1  | Software Reset Register (ARSTR)                                     | 644 |

|       |         | EtherC Mode Register (ECMR)                                         |     |

|       | 18.3.3  | EtherC Status Register (ECSR)                                       | 648 |

|       | 18.3.4  | EtherC Interrupt Permission Register (ECSIPR)                       | 649 |

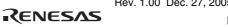

|       | 18.3.5  | PHY Interface Register (PIR)                                        | 650 |

|       | 18.3.6  | MAC Address High Register (MAHR)                                    | 651 |

|       | 18.3.7  | MAC Address Low Register (MALR)                                     | 651 |

|       | 18.3.8  | Receive Frame Length Register (RFLR)                                | 652 |

|       | 18.3.9  | PHY Status Register (PSR)                                           | 653 |

|       | 18.3.10 | Transmit Retry Over Counter Register (TROCR)                        | 653 |

|       | 18.3.11 | Delayed Collision Detect Counter Register (CDCR)                    | 654 |

|       | 18.3.12 | Lost Carrier Counter Register (LCCR)                                | 654 |

|       | 18.3.13 | Carrier Not Detect Counter Register (CNDCR)                         | 654 |

|       | 18.3.14 | CRC Error Frame Receive Counter Register (CEFCR)                    | 655 |

|       | 18.3.15 | Frame Receive Error Counter Register (FRECR)                        | 655 |

|       | 18.3.16 | o Too-Short Frame Receive Counter Register (TSFRCR)                 | 655 |

|       | 18.3.17 | Too-Long Frame Receive Counter Register (TLFRCR)                    | 656 |

|       | 18.3.18 | Residual-Bit Frame Receive Counter Register (RFCR)                  | 656 |

|       | 18.3.19 | Multicast Address Frame Receive Counter Register (MAFCR)            | 657 |

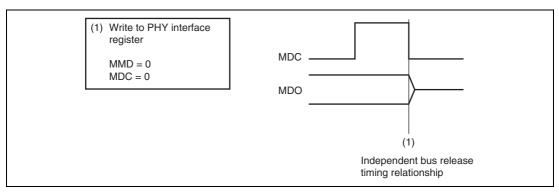

|       | 18.3.20 | PIPG Register (IPGR)                                                | 657 |

|       |         | TSU Counter Reset Register (TSU_CTRST)                              |     |

|       |         | Relay Enable Register (Port 0 to 1) (TSU_FWEN0)                     |     |

|       |         | Relay Enable Register (Port 1 to 0) (TSU_FWEN1)                     |     |

|       | 18.3.24 | Relay FIFO Size Select Register (TSU_FCM)                           | 660 |

|       | 18.3.25 | Relay FIFO Overflow Alert Set Register (Port 0) (TSU_BSYSL0)        | 661 |

|       | 18.3.26 | Relay FIFO Overflow Alert Set Register (Port 1) (TSU_BSYSL1)        | 662 |

|       | 18.3.27 | Transmit/Relay Priority Control Mode Register (Port 0) (TSU_PRISL0) | 663 |

|       | 18.3.28 | Transmit/Relay Priority Control Mode Register (Port 1) (TSU_PRISL1) | 664 |

|       | 18.3.29 | Receive/Relay Function Set Register (Port 0 to 1) (TSU_FWSL0)       | 666 |

|       | 18.3.30 | Receive/Relay Function Set Register (Port 1 to 0) (TSU_FWSL1)       | 667 |

|       | 18.3.31 | Relay Function Set Register (Common) (TSU_FWSLC)                    | 669 |

|       | 18.3.32 | 2 Qtag Addition/Deletion Set Register (Port 0 to 1) (TSU_QTAGM0)    | 671 |

|       | 18.3.33 | Qtag Addition/Deletion Set Register (Port 1 to 0) (TSU_QTAGM1)      | 672 |

|       | 18.3.34 | Relay Status Register (TSU_FWSR)                                    | 673 |

|      | 18.3.35 Relay Status Interrupt Mask Register (TSU_FWINMK)                                     | 675  |

|------|-----------------------------------------------------------------------------------------------|------|

|      | 18.3.36 Added Qtag Value Set Register (Port 0 to 1) (TSU_ADQT0)                               |      |

|      | 18.3.37 Added Qtag Value Set Register (Port 1 to 0) (TSU_ADQT1)                               | 680  |

|      | 18.3.38 CAM Entry Table Busy Register (TSU_ADSBSY)                                            | 681  |

|      | 18.3.39 CAM Entry Table Enable Register (TSU_TEN)                                             | 682  |

|      | 18.3.40 CAM Entry Table POST1 Register (TSU_POST1)                                            | 686  |

|      | 18.3.41 CAM Entry Table POST2 Register (TSU_POST2)                                            | 689  |

|      | 18.3.42 CAM Entry Table POST3 Register (TSU_POST3)                                            | 692  |

|      | 18.3.43 CAM Entry Table POST4 Register (TSU_POST4)                                            | 695  |

|      | 18.3.44 CAM Entry Table 0 to 31 H Registers (TSU_ADRH0 to TSU_ADRH31)                         | 698  |

|      | 18.3.45 CAM Entry Table 0 to 31 L Registers (TSU_ADRL0 to TSU_ADRL31)                         | 699  |

|      | 18.3.46 Transmit Frame Counter Register (Port 0) (Normal Transmission Only)                   |      |

|      | (TXNLCR0)                                                                                     | 699  |

|      | 18.3.47 Transmit Frame Counter Register (Port 0) (Normal and Error Transmission)<br>(TXALCR0) | 700  |

|      | 18.3.48 Receive Frame Counter Register (Port 0) (Normal Reception Only)                       | / 00 |

|      | (RXNLCR0)                                                                                     |      |

|      | 18.3.49 Receive Frame Counter Register (Port 0) (Normal and Error Reception)                  |      |

|      | (RXALCR0)                                                                                     | 701  |

|      | 18.3.50 Relay Frame Counter Register (Port 1 to 0) (Normal Relay Only)                        |      |

|      | (FWNLCR0)                                                                                     | 701  |

|      | 18.3.51 Relay Frame Counter Register (Port 1 to 0) (Normal and Error Relay)                   |      |

|      | (FWALCR0)                                                                                     | 702  |

|      | 18.3.52 Transmit Frame Counter Register (Port 1) (Normal Transmission Only)                   |      |

|      | (TXNLCR1)                                                                                     | 702  |

|      | 18.3.53 Transmit Frame Counter Register (Port 1) (Normal and Error Transmission)              |      |

|      | (TXALCR1)                                                                                     | 703  |

|      | 18.3.54 Receive Frame Counter Register (Port 1) (Normal Reception Only)                       |      |

|      | (RXNLCR1)                                                                                     | 703  |

|      | 18.3.55 Receive Frame Counter Register (Port 1) (Normal and Error Reception)                  |      |

|      | (RXALCR1)                                                                                     | 704  |

|      | 18.3.56 Relay Frame Counter Register (Port 0 to 1) (Normal Relay Only)                        |      |

|      | (FWNLCR1)                                                                                     | 704  |

|      | 18.3.57 Relay Frame Counter Register (Port 0 to 1) (Normal and Error Relay)                   |      |

|      | (FWALCR1)                                                                                     |      |

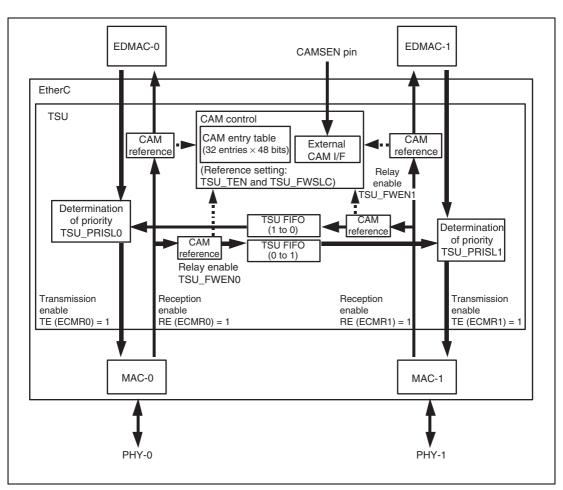

| 18.4 | Operation                                                                                     |      |

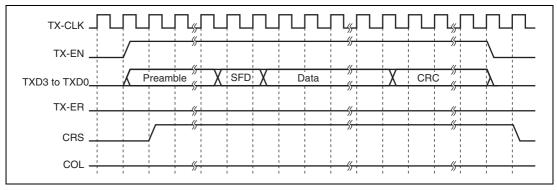

|      | 18.4.1 Transmission                                                                           |      |

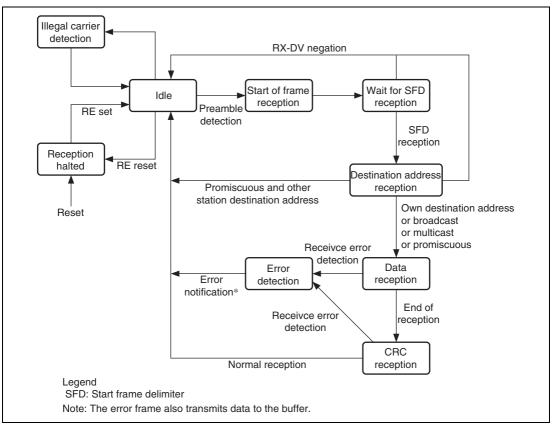

|      | 18.4.2 Reception                                                                              |      |

|      | 18.4.3 Relay                                                                                  |      |

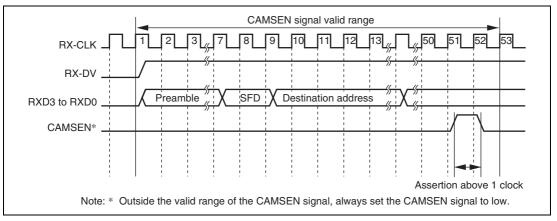

|      | 18.4.4 CAM Function                                                                           | 711  |

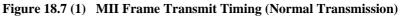

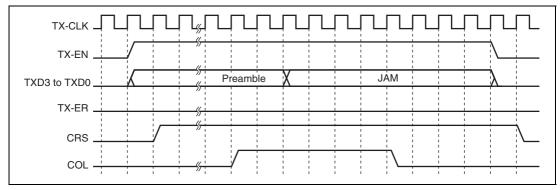

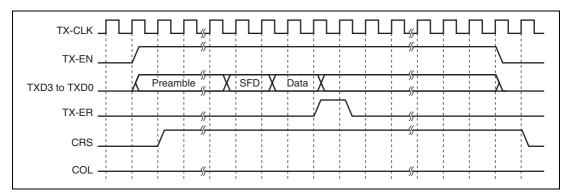

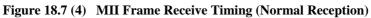

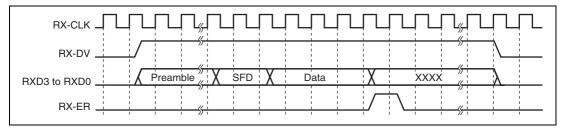

|       | 18.4.5  | MII Frame Timing                                            |     |

|-------|---------|-------------------------------------------------------------|-----|

|       | 18.4.6  | Accessing MII Registers                                     |     |

|       |         | Magic Packet Detection                                      |     |

|       |         | Operation by IPG Setting                                    |     |

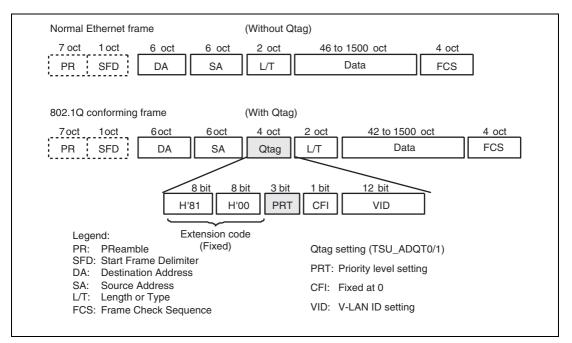

|       |         | Direction for IEEE802.1Q Qtag                               |     |

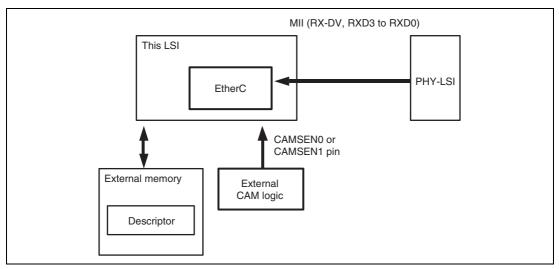

| 18.5  |         | ction to LSI                                                |     |

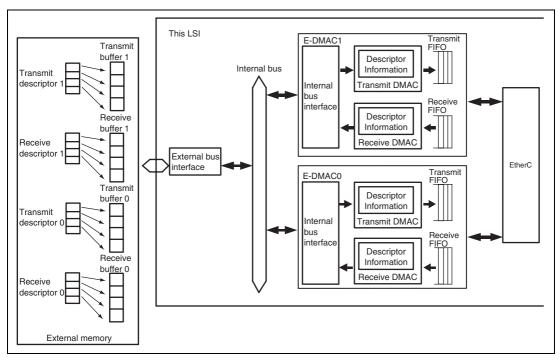

| Secti | ion 19  | Ethernet Controller Direct Memory Access Controller         |     |

|       |         | (E-DMAC)                                                    | 727 |

| 19.1  | Feature | 28                                                          |     |

| 19.2  | Registe | er Descriptions                                             |     |

|       | 19.2.1  | E-DMAC Mode Register (EDMR)                                 |     |

|       | 19.2.2  | E-DMAC Transmit Request Register (EDTRR)                    |     |

|       | 19.2.3  | E-DMAC Receive Request Register (EDRRR)                     |     |

|       | 19.2.4  | Transmit Descriptor List Address Register (TDLAR)           |     |

|       |         | Receive Descriptor List Address Register (RDLAR)            |     |

|       | 19.2.6  | EtherC/E-DMAC Status Register (EESR)                        |     |

|       | 19.2.7  | EtherC/E-DMAC Status Interrupt Permission Register (EESIPR) |     |

|       | 19.2.8  | Transmit/Receive Status Copy Enable Register (TRSCER)       |     |

|       | 19.2.9  | Receive Missed-Frame Counter Register (RMFCR)               |     |

|       | 19.2.10 | ) Transmit FIFO Threshold Register (TFTR)                   |     |

|       | 19.2.11 | FIFO Depth Register (FDR)                                   |     |

|       | 19.2.12 | Receiving Method Control Register (RMCR)                    |     |

|       | 19.2.13 | B E-DMAC Operation Control Register (EDOCR)                 |     |

|       | 19.2.14 | Receive Buffer Write Address Register (RBWAR)               |     |

|       | 19.2.15 | 6 Receive Descriptor Fetch Address Register (RDFAR)         |     |

|       | 19.2.16 | 5 Transmit Buffer Read Address Register (TBRAR)             |     |

|       | 19.2.17 | 7 Transmit Descriptor Fetch Address Register (TDFAR)        |     |

|       | 19.2.18 | 3 Overflow Alert FIFO Threshold Register (FCFTR)            |     |

|       | 19.2.19 | P Transmit Interrupt Register (TRIMD)                       |     |

| 19.3  | Operati | on                                                          |     |

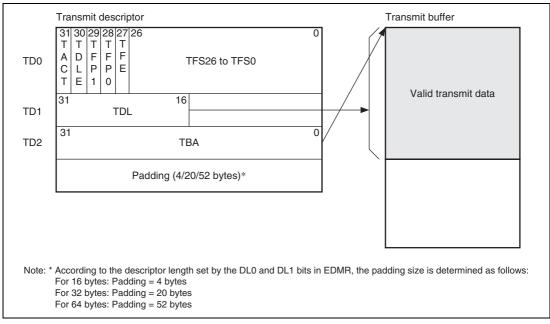

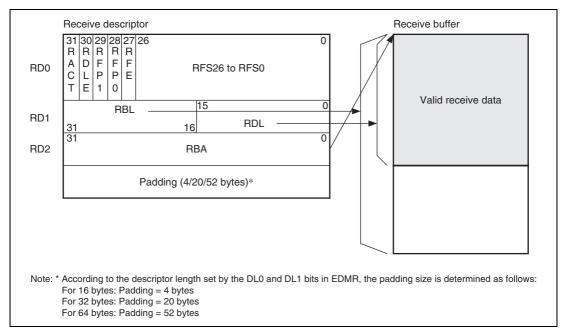

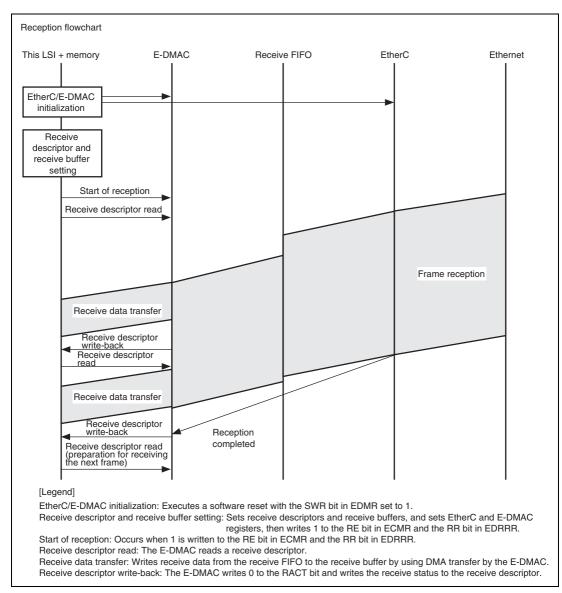

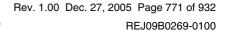

|       | 19.3.1  | Descriptors and Descriptor List                             |     |

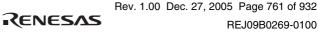

|       | 19.3.2  | Transmission                                                |     |

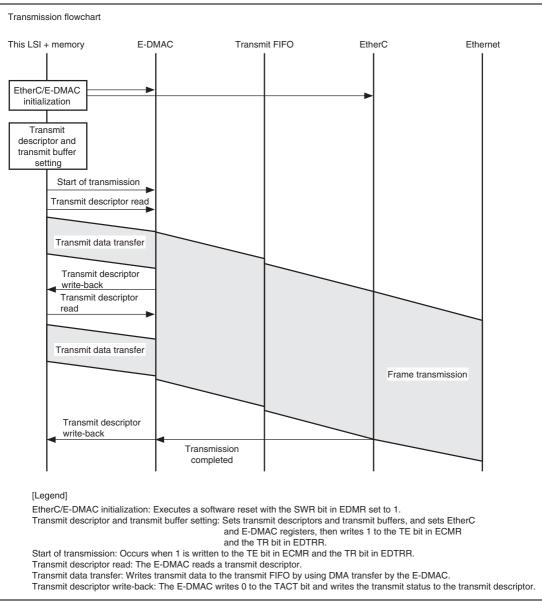

|       | 19.3.3  | Reception                                                   |     |

|       | 19.3.4  | Transmit/Receive Processing of Multi-Buffer Frame           |     |

|       |         | (Single-Frame/ Multi-Descriptor)                            |     |

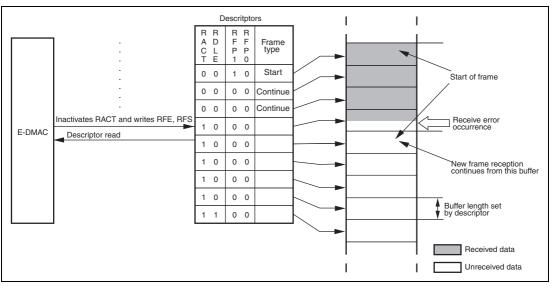

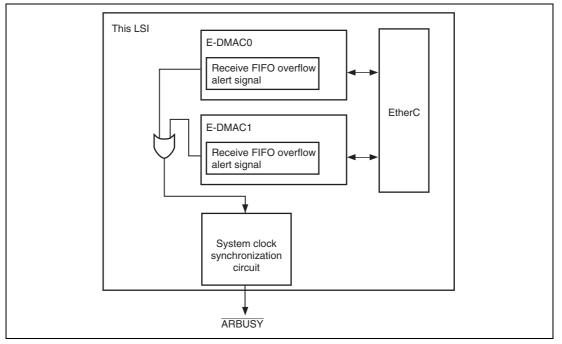

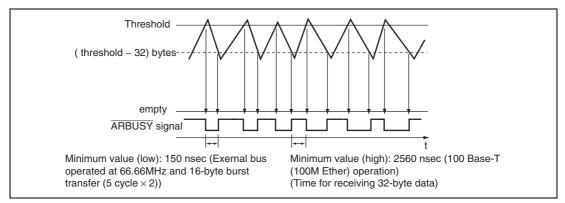

|       | 19.3.5  | Receive FIFO Overflow Alert Signal (ARBUSY)                 |     |

| 19.4  | Usage 1 | Notes                                                       |     |

|       | 19.4.1  | Using of EDTRR and EDRRR                                    |     |

|       | 19.4.2  | Endian Support in E-DMAC                                    |     |

| Secti | on 20   | Pin Function Controller (PFC)                                     | 779 |

|-------|---------|-------------------------------------------------------------------|-----|

| 20.1  | Overvie | ew                                                                |     |

| 20.2  | Registe | r Configuration                                                   |     |

| 20.3  | Registe | r Descriptions                                                    |     |

|       | 20.3.1  | Port A Control Register (PACR)                                    |     |

|       |         | Port B Control Register (PBCR)                                    |     |

|       |         | Port C Control Register (PCCR)                                    |     |

|       | 20.3.4  | Ethernet Controller Pin Control Register (PETCR)                  | 784 |

| Secti | on 21   | I/O Ports                                                         | 787 |

| 21.1  |         | ew                                                                |     |

| 21.2  |         | r Descriptions                                                    |     |

|       |         | Port A Data Register (PADR)                                       |     |

|       |         | Port B Data Register (PBDR)                                       |     |

|       |         | Port C Data Register (PCDR)                                       |     |

|       |         |                                                                   |     |

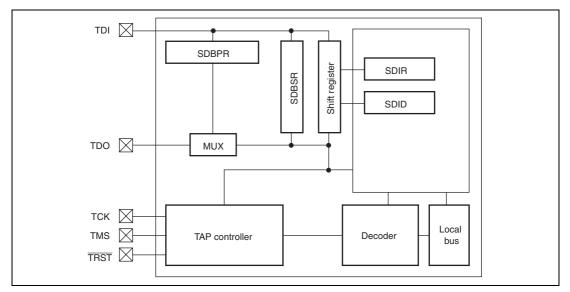

| Secti |         | User Debugging Interface (H-UDI)                                  |     |

| 22.1  | Feature | S                                                                 |     |

| 22.2  | Input/C | Output Pins                                                       |     |

| 22.3  | Registe | r Descriptions                                                    |     |

|       | 22.3.1  | Bypass Register (SDBPR)                                           |     |

|       | 22.3.2  | Instruction Register (SDIR)                                       |     |

|       |         | Boundary Scan Register (SDBSR)                                    |     |

|       | 22.3.4  | ID Register (SDID)                                                | 801 |

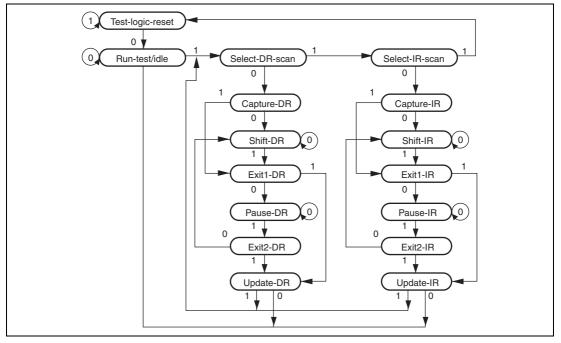

| 22.4  | Operati | on                                                                |     |

|       | 22.4.1  | TAP Controller                                                    |     |

|       | 22.4.2  | Reset Configuration                                               | 803 |

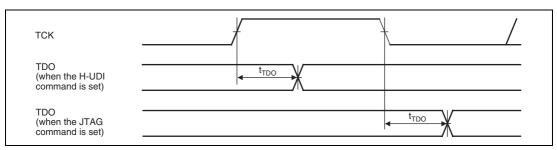

|       | 22.4.3  | TDO Output Timing                                                 | 803 |

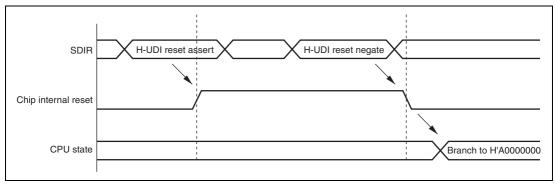

|       | 22.4.4  | H-UDI Reset                                                       | 804 |

|       | 22.4.5  | H-UDI Interrupt                                                   | 804 |

| 22.5  | Bounda  | ry Scan                                                           | 805 |

|       | 22.5.1  | Supported Instructions                                            | 805 |

|       | 22.5.2  | Points for Attention                                              | 806 |

| 22.6  | Usage l | Notes                                                             |     |

| 22.7  | -       | red User Debugger (AUD)                                           |     |

| Secti | on 23   | List of Registers                                                 |     |

| 23.1  |         | er Addresses (by functional module, in order of the corresponding |     |

|       | 0       | numbers)                                                          |     |

| 23.2  |         | r Bits                                                            |     |

|       | -       |                                                                   |     |

| 23.3  | Registe | er States in Each Operating Mode          |  |

|-------|---------|-------------------------------------------|--|

| Secti | ion 24  | Electrical Characteristics                |  |

| 24.1  |         | te Maximum Ratings                        |  |

| 24.2  |         | aracteristics                             |  |

| 24.3  | AC Ch   | aracteristics                             |  |

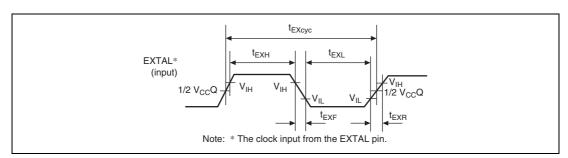

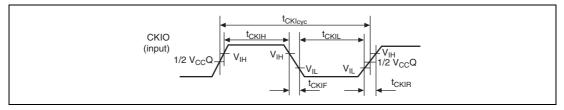

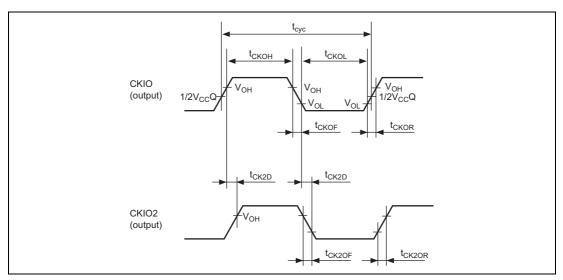

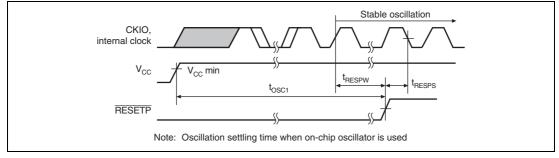

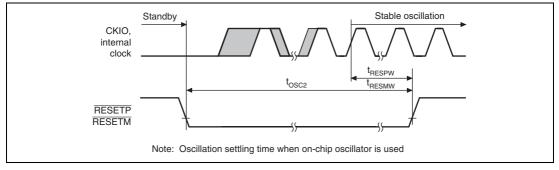

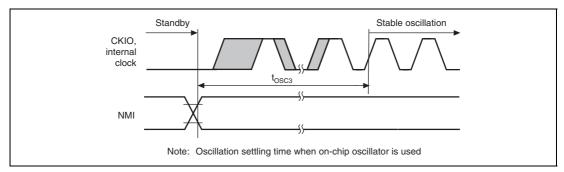

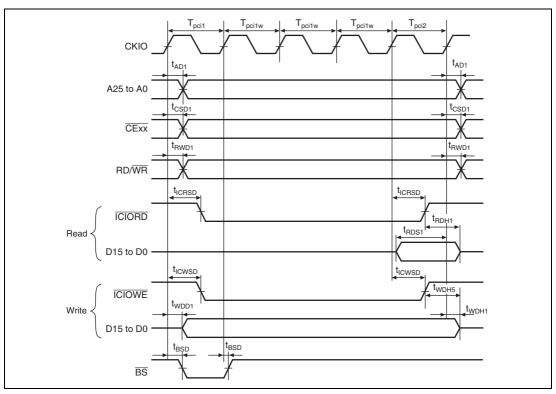

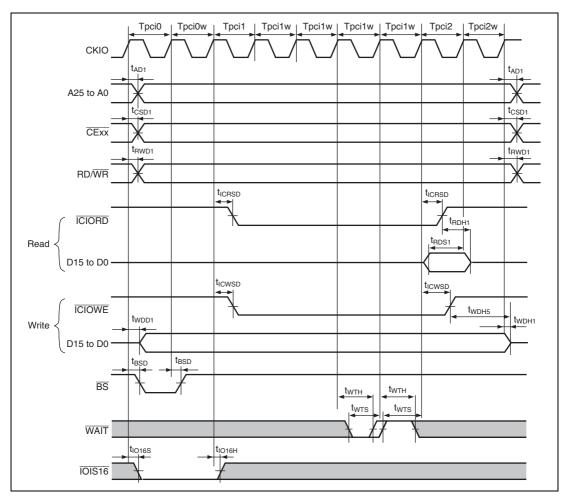

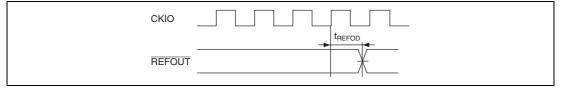

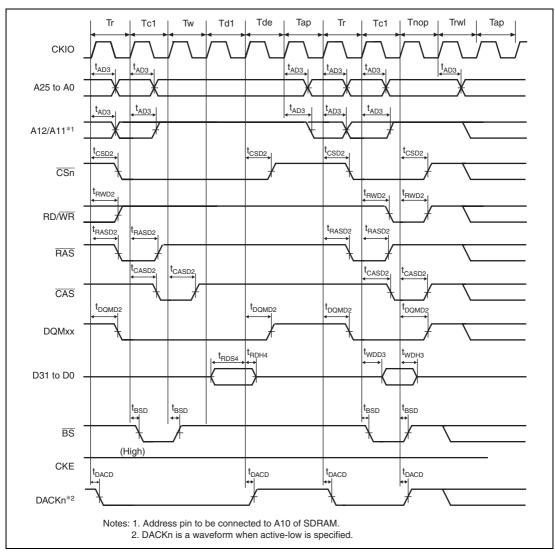

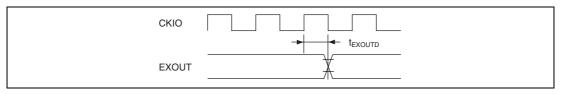

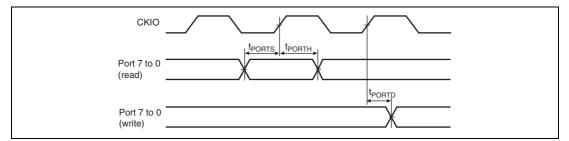

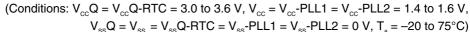

|       | 24.3.1  | Clock Timing                              |  |

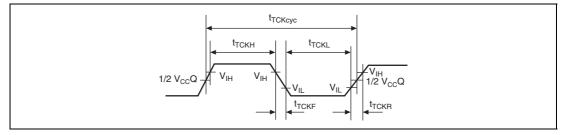

|       | 24.3.2  | Control Signal Timing                     |  |

|       | 24.3.3  | AC Bus Timing                             |  |

|       | 24.3.4  | Basic Timing                              |  |

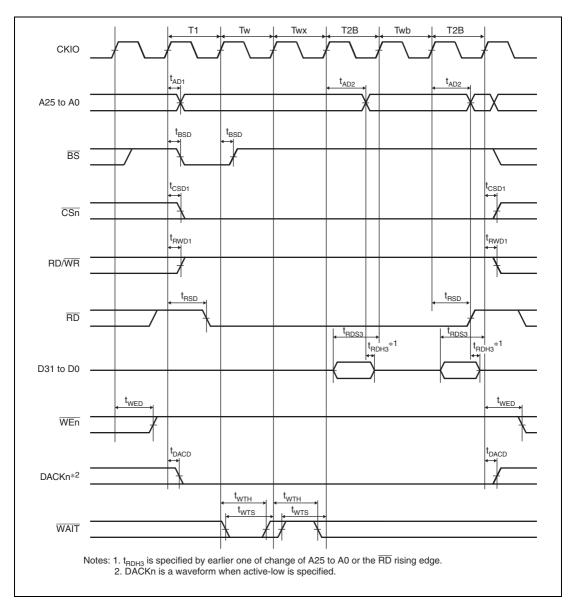

|       | 24.3.5  | Burst ROM Timing                          |  |

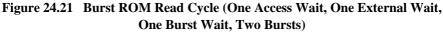

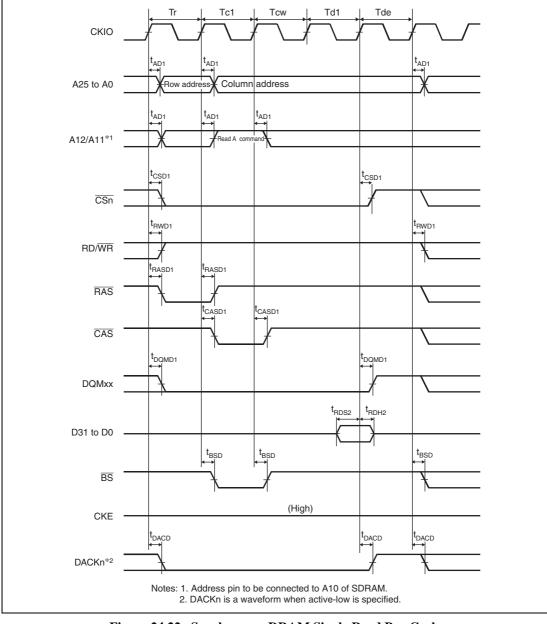

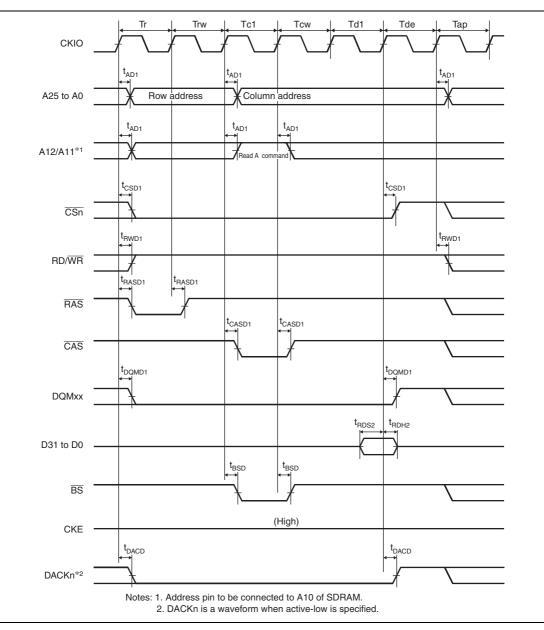

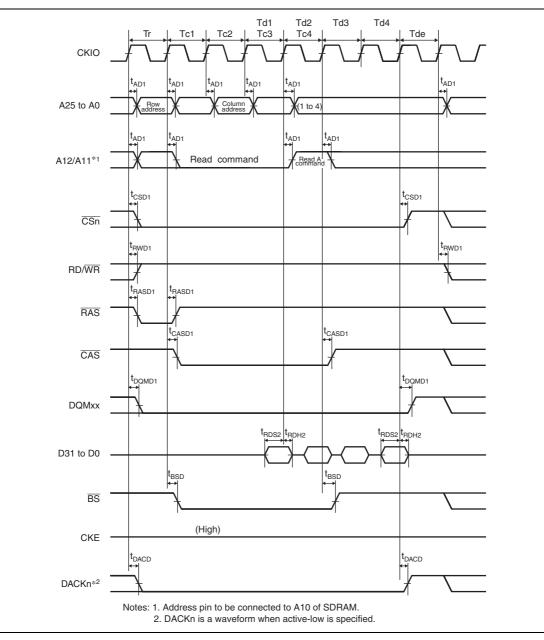

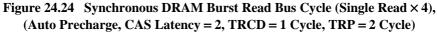

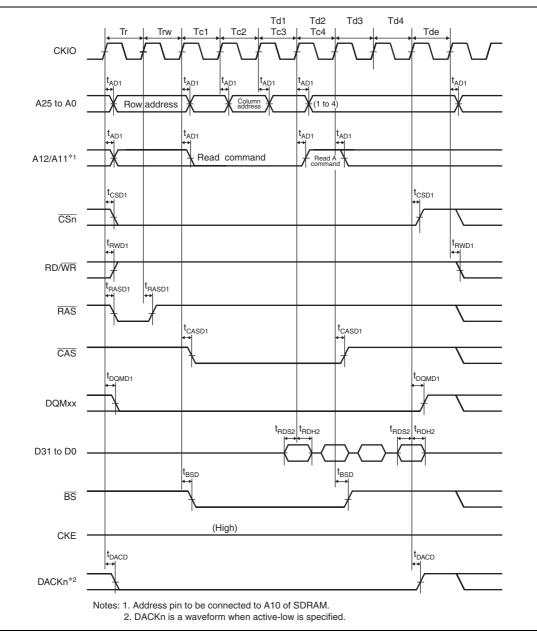

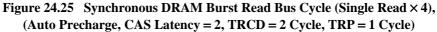

|       | 24.3.6  | Synchronous DRAM Timing                   |  |

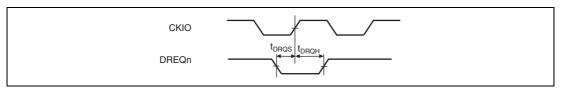

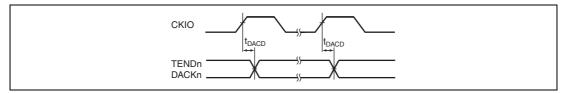

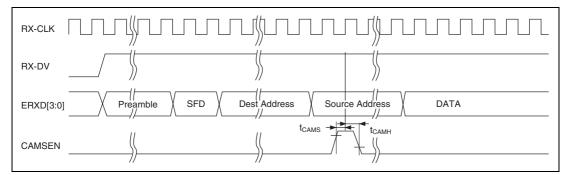

|       | 24.3.7  | DMAC Signal Timing                        |  |

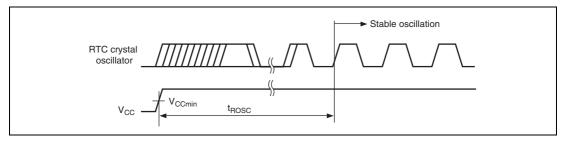

|       | 24.3.8  | RTC Signal Timing                         |  |

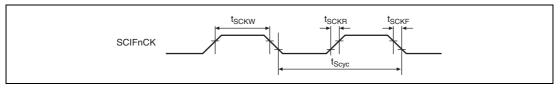

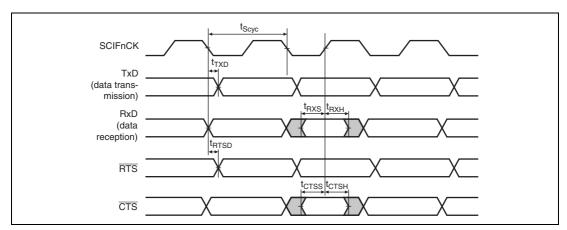

|       | 24.3.9  | SCIF Module Signal Timing                 |  |

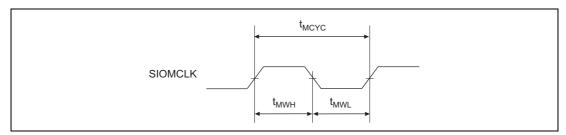

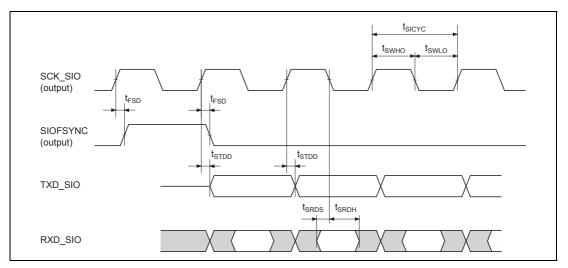

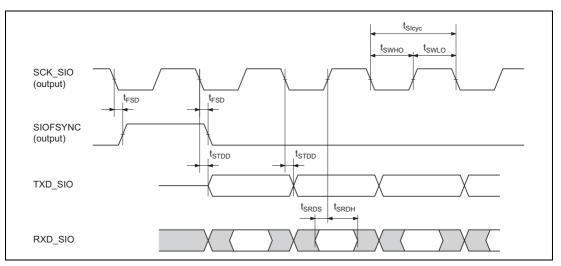

|       | 24.3.10 | ) SIOF Module Signal Timing               |  |

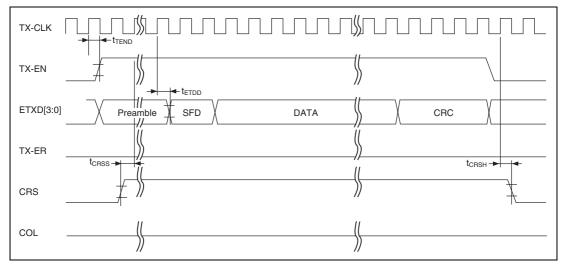

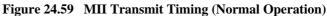

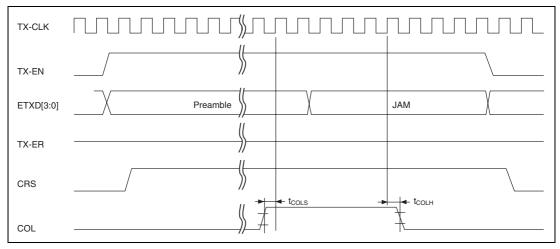

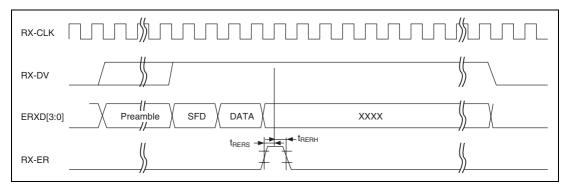

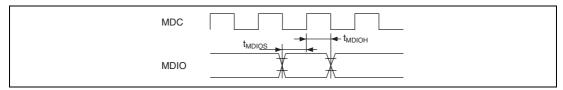

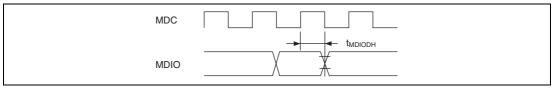

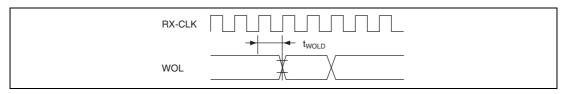

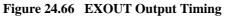

|       | 24.3.11 | Ethernet Controller Timing                |  |

|       | 24.3.12 | Port Input/Output Timing                  |  |

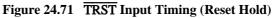

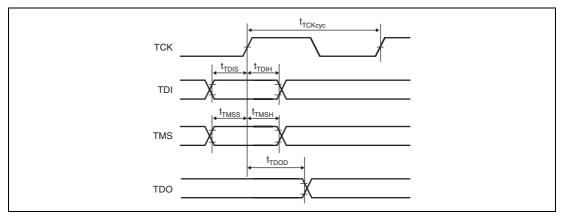

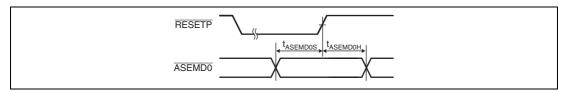

|       | 24.3.13 | H-UDI Related Pin Timing                  |  |

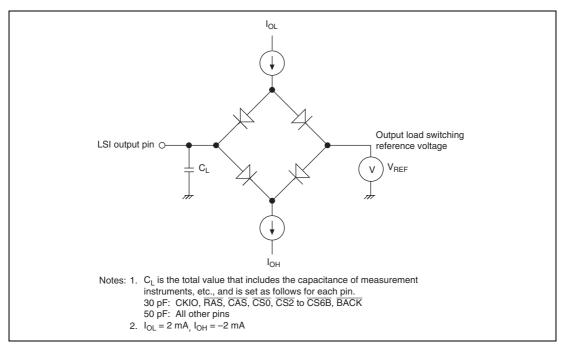

|       | 24.3.14 | AC Characteristics Measurement Conditions |  |

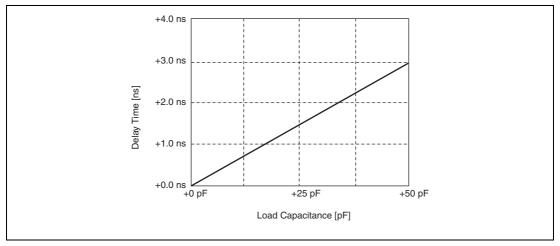

| 24.4  | Delay   | Fime Variation Due to Load Capacitance    |  |

| App   | endix   |                                           |  |

| Α.    | Pin Sta | tes and States of Unused Pins             |  |

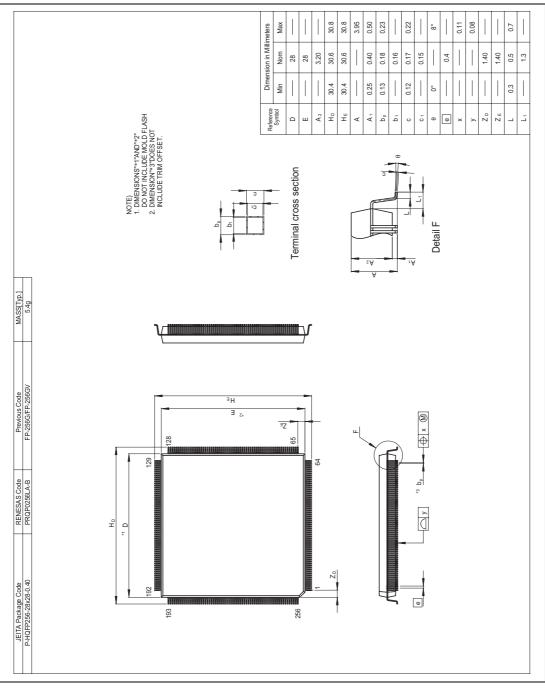

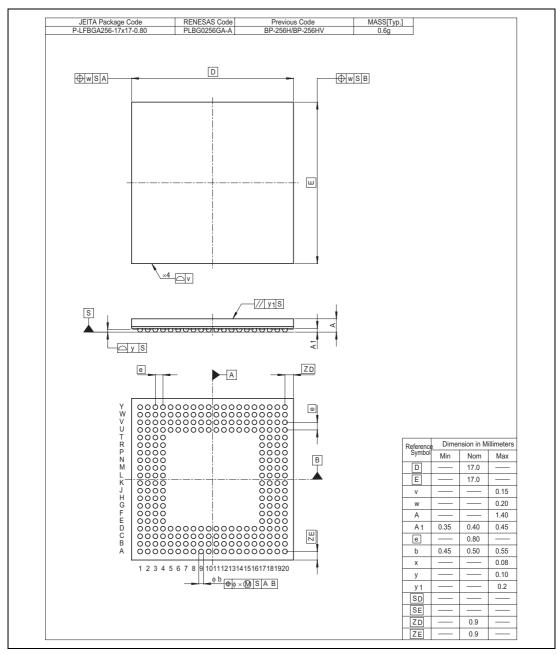

| В.    | Packag  | e Dimensions                              |  |

| Inde  | X       |                                           |  |

# Figures

| Section 1   | Overview                                                          |     |

|-------------|-------------------------------------------------------------------|-----|

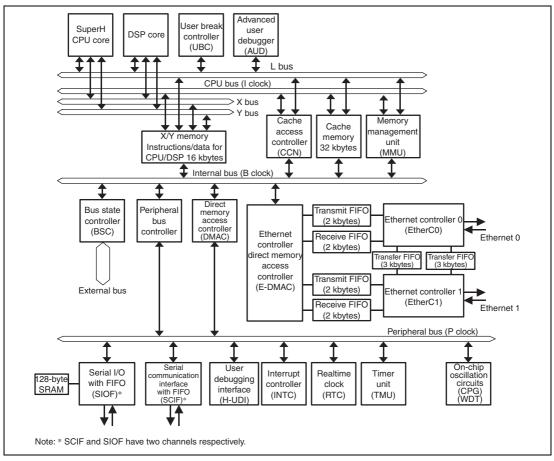

| Figure 1.1  | Block Diagram                                                     | 7   |

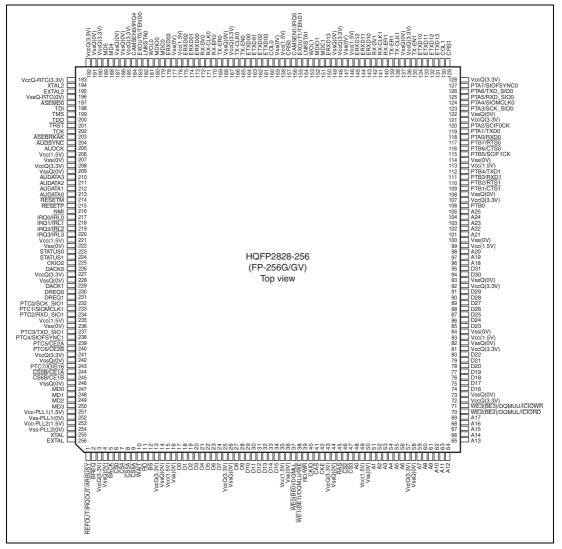

| Figure 1.2  | Pin Assignment (HQFP2828-256(FP-256G/GV))                         |     |

| Figure 1.3  | Pin Assignment (P-LFBGA1717-256(BP-256H/HV))                      | 9   |

| Section 2   |                                                                   |     |

| -           | Processing State Transitions                                      |     |

| -           | Logical Address to External Memory Space Mapping                  |     |

| -           | Register Configuration in Each Processing Mode                    |     |

| -           | General Registers                                                 |     |

| Figure 2.5  | System Registers and Program Counter                              |     |

| -           | Control Register Configuration                                    |     |

| -           | Data Format on Memory (Big Endian Mode)                           |     |

| Figure 2.8  | Data Format on Memory (Little Endian Mode)                        | 43  |

| Section 3   | DSP Operating Unit                                                |     |

| Figure 3.1  | DSP Instruction Format                                            | 72  |

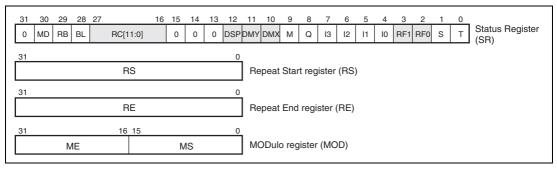

| Figure 3.2  | CPU Registers in DSP Mode                                         | 74  |

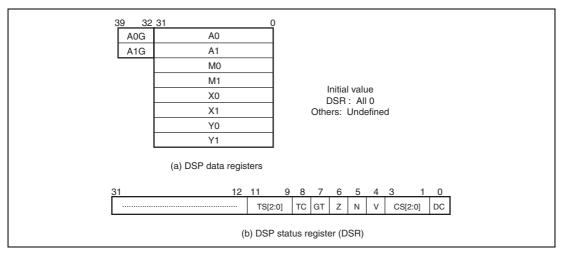

| Figure 3.3  | DSP Register Configuration                                        | 77  |

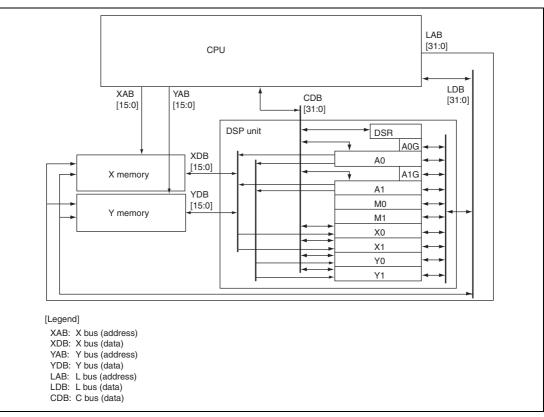

| Figure 3.4  | DSP Registers and Bus Connections                                 | 94  |

| Figure 3.5  | General Registers (DSP Mode)                                      | 97  |

| Figure 3.6  | Sample Parallel Instruction Program                               |     |

| Figure 3.7  | Examples of Conditional Operations and Data Transfer Instructions | 115 |

| Figure 3.8  | Data Formats                                                      | 117 |

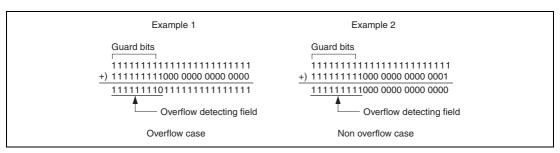

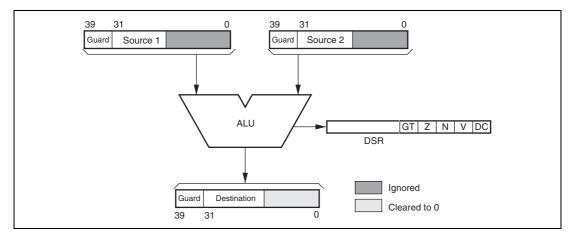

| Figure 3.9  | ALU Fixed-Point Arithmetic Operation Flow                         |     |

| Figure 3.10 | Operation Sequence Example                                        |     |

| Figure 3.11 | DC Bit Generation Examples in Carry or Borrow Mode                |     |

| Figure 3.12 | DC Bit Generation Examples in Negative Value Mode                 |     |

| Figure 3.13 | DC Bit Generation Examples in Overflow Mode                       |     |

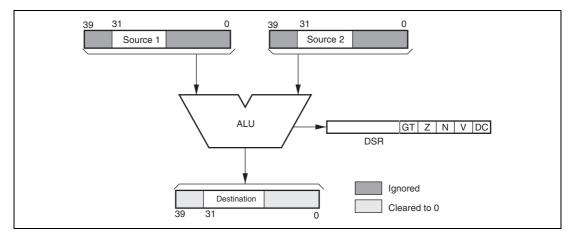

| Figure 3.14 | ALU Integer Arithmetic Operation Flow                             |     |

| Figure 3.15 | ALU Logical Operation Flow                                        |     |

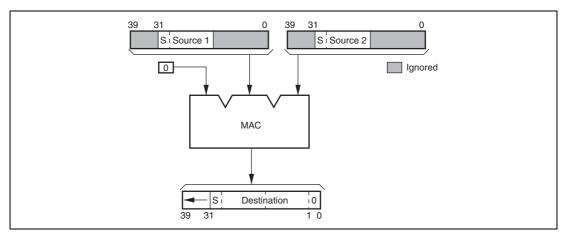

| Figure 3.16 | Fixed-Point Multiply Operation Flow                               |     |

| Figure 3.17 | Arithmetic Shift Operation Flow                                   |     |

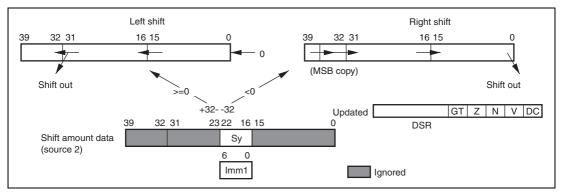

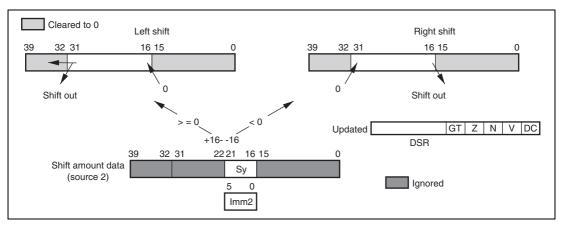

| Figure 3.18 | Logical Shift Operation Flow                                      |     |

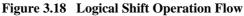

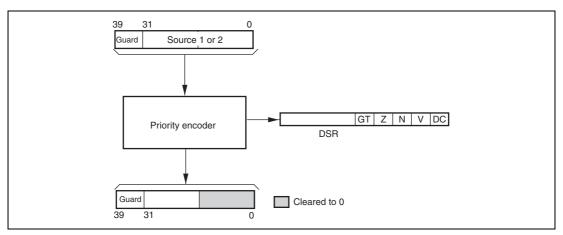

| Figure 3.19 | PDMSB Operation Flow                                              |     |

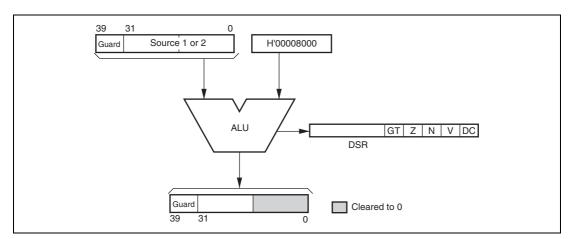

| Figure 3.20 | Rounding Operation Flow                                           |     |

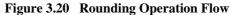

| Figure 3.21 | Definition of Rounding Operation                                  |     |

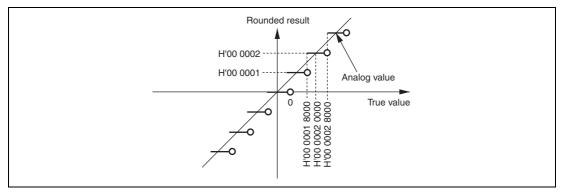

| Figure 3.22 | Local Data Move Instruction Flow                                  |     |

| Section 4 Exception Handling                                         |                 |

|----------------------------------------------------------------------|-----------------|

| Figure 4.1 Register Bit Configuration                                |                 |

| Section 5 Memory Management Unit (MMU)                               |                 |

| Figure 5.1 MMU Functions                                             |                 |

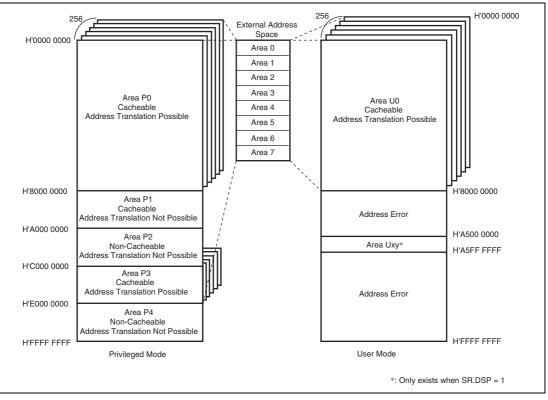

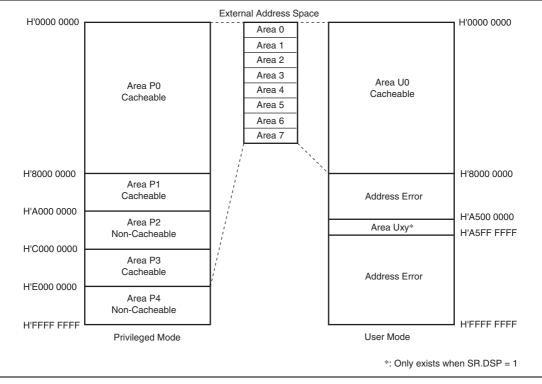

| Figure 5.2 Virtual Address Space (MMUCR.AT = 1)                      |                 |

| Figure 5.3 Virtual Address Space (MMUCR.AT = 0)                      |                 |

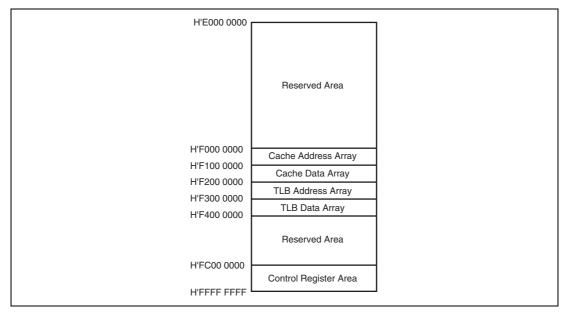

| Figure 5.4 P4 Area                                                   |                 |

| Figure 5.5 External Memory Space                                     |                 |

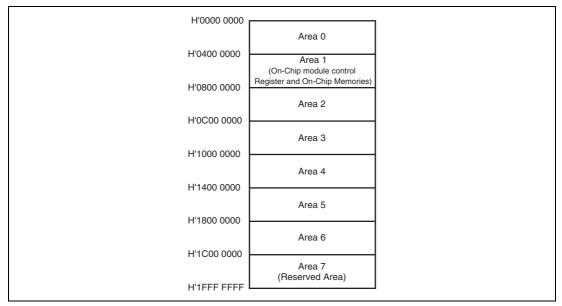

| Figure 5.6 Overall Configuration of the TLB                          |                 |

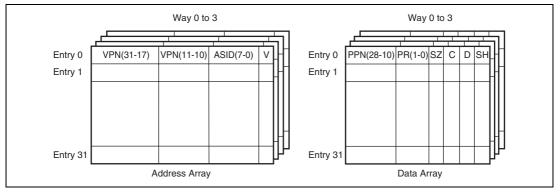

| Figure 5.7 Virtual Address and TLB Structure                         |                 |

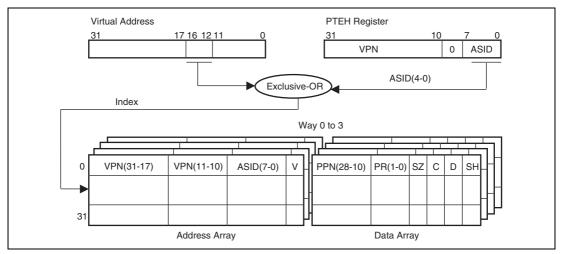

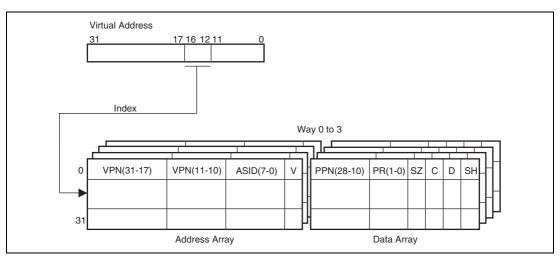

| Figure 5.8 TLB Indexing (IX = 1)                                     |                 |

| Figure 5.9 TLB Indexing (IX = 0)                                     |                 |

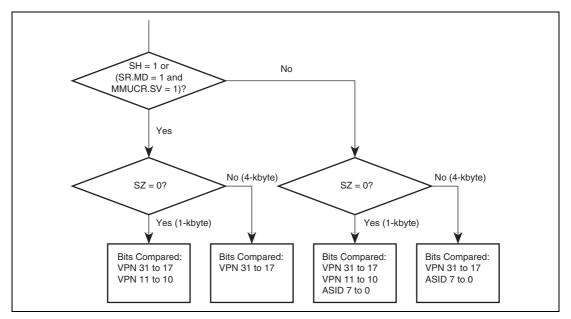

| Figure 5.10 Objects of Address Comparison                            |                 |

| Figure 5.11 Operation of LDTLB Instruction                           |                 |

| Figure 5.12 Synonym Problem (32-kbyte Cache)                         |                 |

| Figure 5.13 MMU Exception Generation Flowchart                       |                 |

| Figure 5.14 Specifying Address and Data for Memory-Mapped TLB Access | s212            |

| Section 6 Cache                                                      |                 |

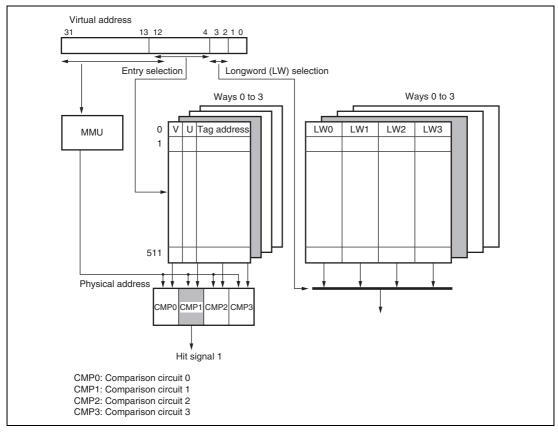

| Figure 6.1 Cache Structure                                           |                 |

| Figure 6.2 Cache Search Scheme                                       |                 |

| Figure 6.3 Write-Back Buffer Configuration                           |                 |

| Figure 6.4 Specifying Address and Data for Memory-Mapped Cache Acces | 38              |

| (16 kbytes mode)                                                     |                 |

| Figure 6.5 Specifying Address and Data for Memory-Mapped Cache Acces | 38              |

| (32 kbytes mode)                                                     |                 |

| Section 8 Interrupt Controller (INTC)                                |                 |

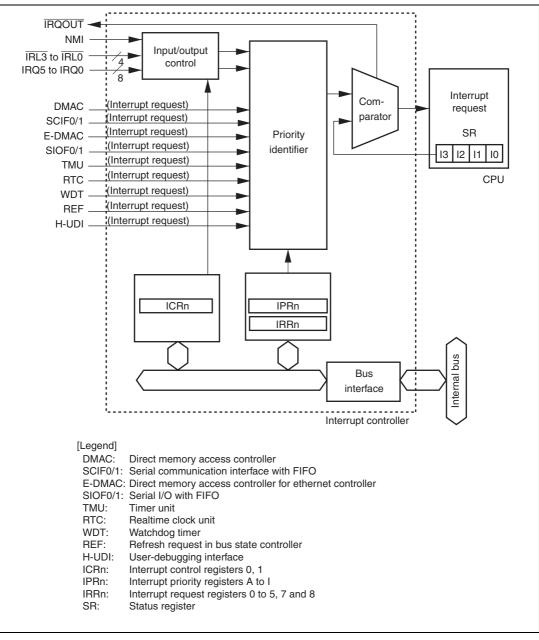

| Figure 8.1 Block Diagram of INTC                                     |                 |

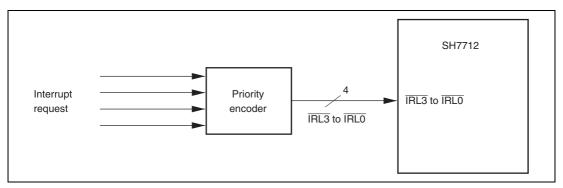

| Figure 8.2 Example of IRL Interrupt Connection                       |                 |