### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# M16C/63 Group

# HARDWARE MANUAL RENESAS MCU M16C FAMILY / M16C/60 SERIES

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

Renesas Electronics www.renesas.com

Rev.1.00 2009.09

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

You should not use the products or the technology described in this document for the purpose of military

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below: (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

#### General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

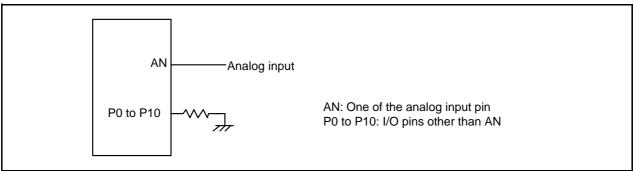

1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

- The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

- 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

- In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

- The reserved addresses are provided for the possible future expansion of functions. Do

not access these addresses; the correct operation of LSI is not guaranteed if they are

accessed.

- 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

- 5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.

# How to Use This Manual

#### 1. Purpose and Target Readers

This manual is designed to provide the user with an understanding of the hardware functions and electrical characteristics of the MCU. It is intended for users designing application systems incorporating the MCU. A basic knowledge of electric circuits, logical circuits, and MCUs is necessary in order to use this manual. The manual comprises an overview of the product; descriptions of the CPU, system control functions, peripheral functions, and electrical characteristics; and usage notes.

Particular attention should be paid to the precautionary notes when using the manual. These notes occur within the body of the text, at the end of each section, and in the Usage Notes section.

The revision history summarizes the locations of revisions and additions. It does not list all revisions. Refer to the text of the manual for details.

The following documents apply to the M16C/63 Group. Make sure to refer to the latest versions of these documents. The newest versions of the documents listed may be obtained from the Renesas Technology Website.

| Document Type    | Description                                         | Document Title       | Document No.  |

|------------------|-----------------------------------------------------|----------------------|---------------|

| Datasheet        | Hardware overview and electrical characteristics    | M16C/63 Group        | REJ03B0271    |

|                  |                                                     | Datasheet            |               |

| Hardware manual  | Hardware specifications (pin assignments,           | M16C/63 Group        | This hardware |

|                  | memory maps, peripheral function                    | Hardware Manual      | manual        |

|                  | specifications, electrical characteristics, timing  |                      |               |

|                  | charts) and operation description                   |                      |               |

|                  | Note: Refer to the application notes for details on |                      |               |

|                  | using peripheral functions.                         |                      |               |

| Software manual  | Descriptions of CPU instruction set                 | M16C/60,             | REJ09B0137    |

|                  |                                                     | M16C/20,             |               |

|                  |                                                     | M16C/Tiny Series     |               |

|                  |                                                     | Software Manual      |               |

| Application note | Information on using peripheral functions and       | Available from the I | Renesas       |

|                  | application examples                                | Technology website   | Э.            |

|                  | Sample programs                                     |                      |               |

|                  | Information on writing programs in assembly         |                      |               |

|                  | language and C                                      |                      |               |

| Renesas          | Product specifications, updates on documents,       |                      |               |

| technical update | etc.                                                |                      |               |

#### 2. Notation of Numbers and Symbols

The notation conventions for register names, bit names, numbers, and symbols used in this manual are described below.

(1) Registers, bits, and pins Registers, bits, and pins are indicated by symbols. Each symbol has a register/bit/pin identifier after the symbol. Example: PM03 bit in the PM0 register P3\_5 pin, VCC pin

(2) Numbers A binary number has the suffix "b" except for a 1-bit value. A hexadecimal number has the suffix "h". A decimal number has no suffix. Example: Binary notation: 11b Hexadecimal notation: EFA0h Decimal notation: 1234

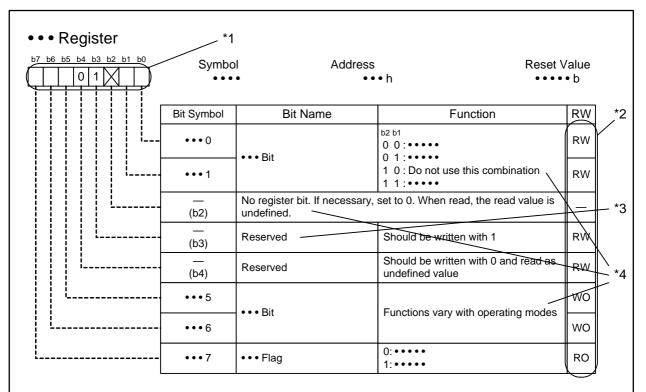

#### 3. Register Notation

The symbols and terms used in register diagrams are described below.

\*1

Blank box: Set this bit to 0 or 1 according to the function.

0: Set this bit to 0.

1: Set this bit to 1.

X: Nothing is assigned to this bit.

\*2

RW: Read and write

RO: Read only

WO: Write only (the read value is undefined)

-: Not applicable

\*3

• Reserved bit: This bit field is reserved. Set this bit to a specified value. For RW bits, the written value is read unless otherwise noted.

\*4

• No register bit(s): No register bit(s) is/are assigned to this field. If necessary, set to 0 for possible future implementation.

• Do not use this combination: Proper operation is not guaranteed when this value is set.

• Functions vary with operating modes: Functions vary with peripheral operating modes. Refer to register illustrations of the respective mode.

#### 4. List of Abbreviations and Acronyms

| Abbreviation | Full Form                                    |

|--------------|----------------------------------------------|

| ACIA         | Asynchronous Communication Interface Adapter |

| bps          | bits per second                              |

| CRC          | Cyclic Redundancy Check                      |

| DMA          | Direct Memory Access                         |

| DMAC         | Direct Memory Access Controller              |

| GSM          | Global System for Mobile Communications      |

| Hi-Z         | High Impedance                               |

| IEBus        | Inter Equipment bus                          |

| I/O          | Input/Output                                 |

| IrDA         | Infrared Data Association                    |

| LSB          | Least Significant Bit                        |

| MSB          | Most Significant Bit                         |

| NC           | Non-Connect                                  |

| PLL          | Phase Locked Loop                            |

| PWM          | Pulse Width Modulation                       |

| SFR          | Special Function Registers                   |

| SIM          | Subscriber Identity Module                   |

| UART         | Universal Asynchronous Receiver/Transmitter  |

| VCO          | Voltage Controlled Oscillator                |

All trademarks and registered trademarks are the property of their respective owners.

IEBus is a registered trademark of NEC Electronics Corporation. HDMI and High-Definition Multimedia Interface are registered trademarks of HDMI Licensing, LLC.

## Table of Contents

| SF | R Page | e Reference                                                | B-1 |

|----|--------|------------------------------------------------------------|-----|

| 1. | Ove    | erview                                                     | 1   |

|    | 1.1    | Features                                                   | 1   |

|    | 1.1.   | .1 Applications                                            | 1   |

|    | 1.2    | Specifications                                             | 2   |

|    | 1.3    | Product List                                               | 6   |

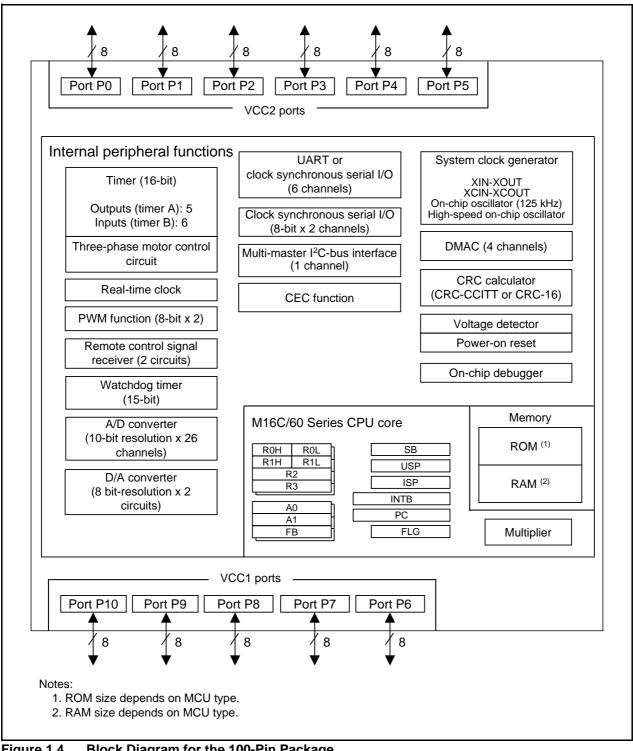

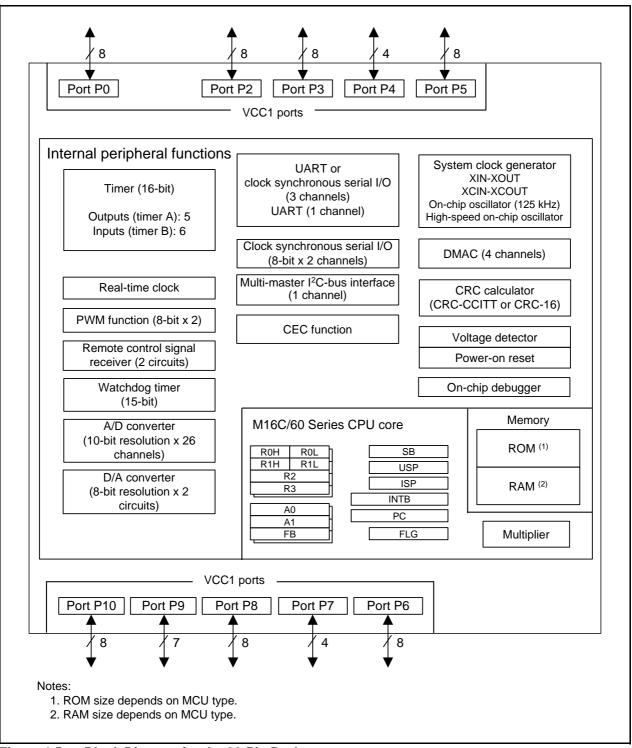

|    | 1.4    | Block Diagram                                              | 8   |

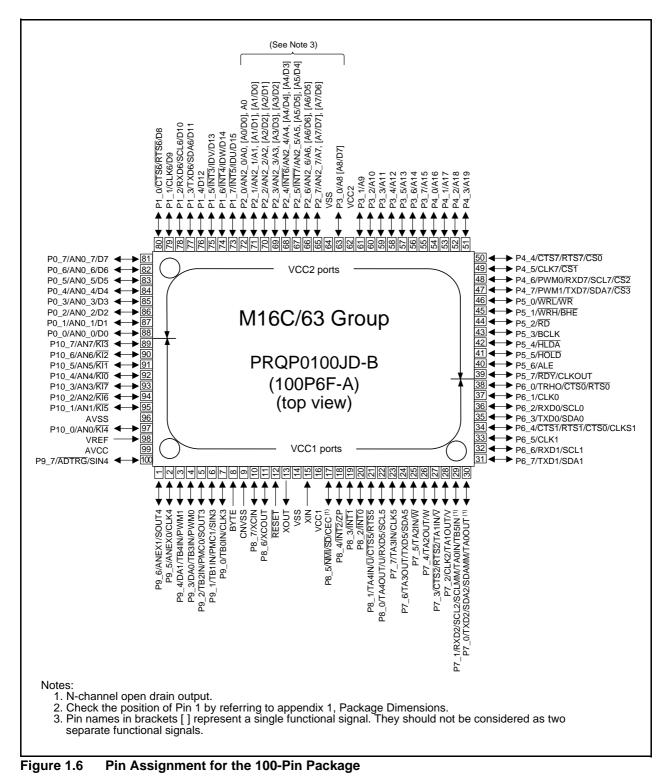

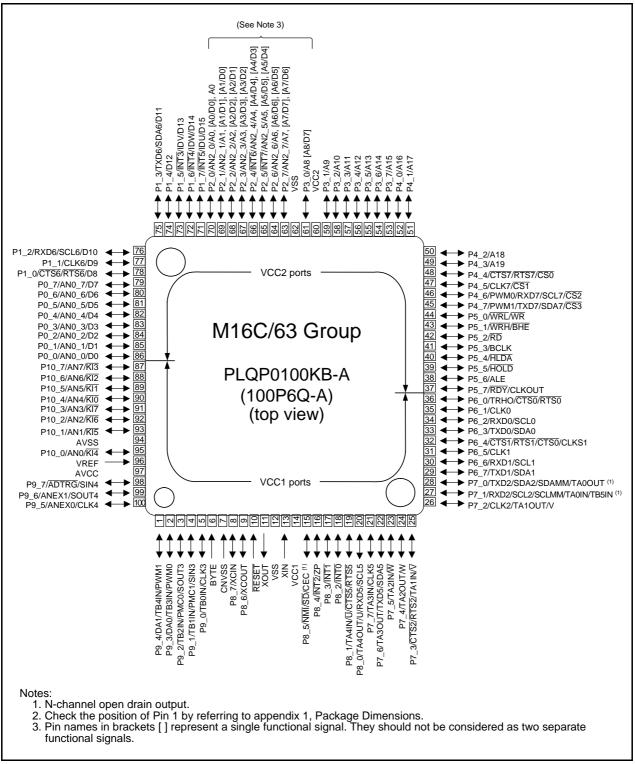

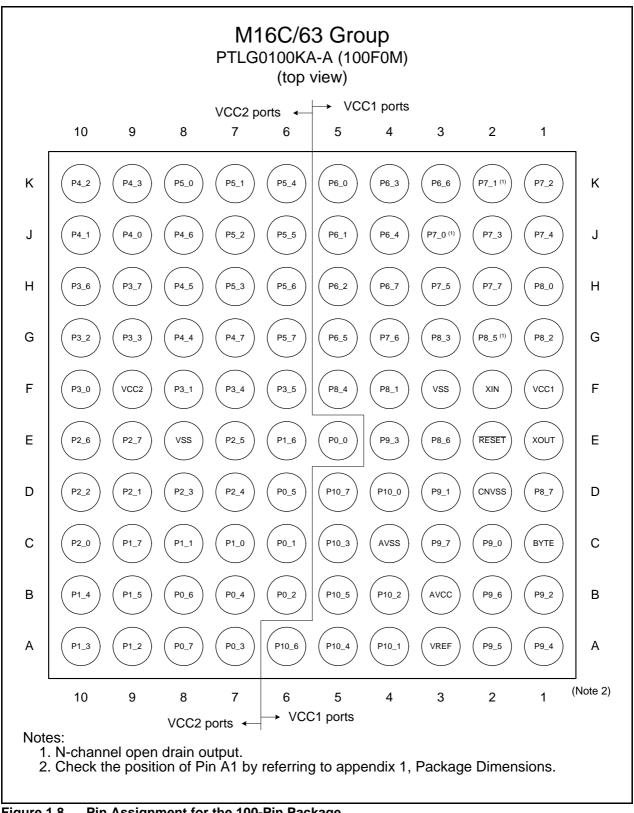

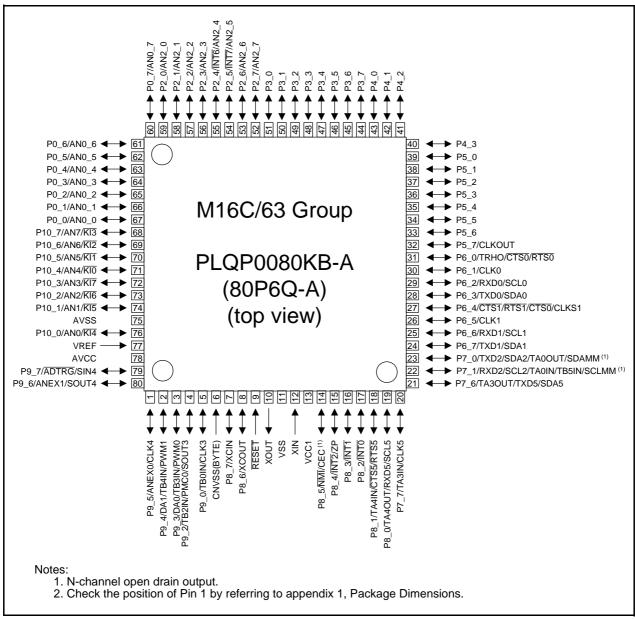

|    | 1.5    | Pin Assignments                                            | 10  |

|    | 1.6    | Pin Functions                                              | 18  |

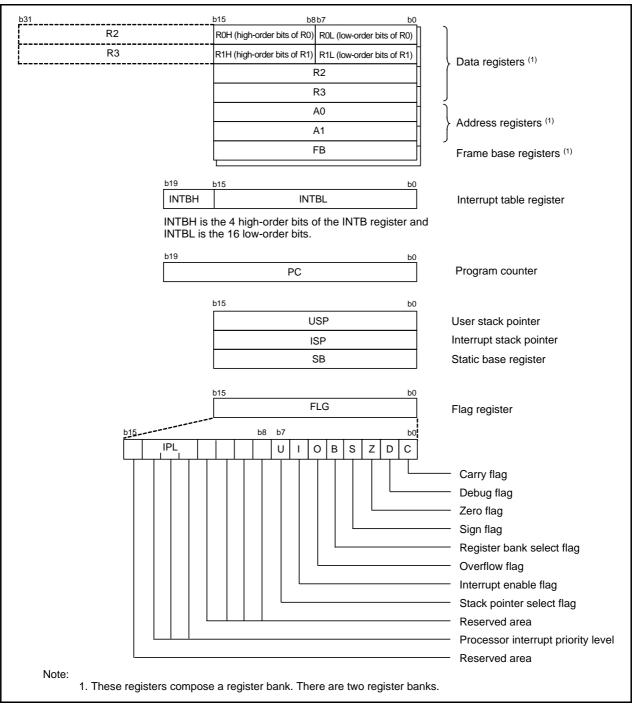

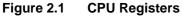

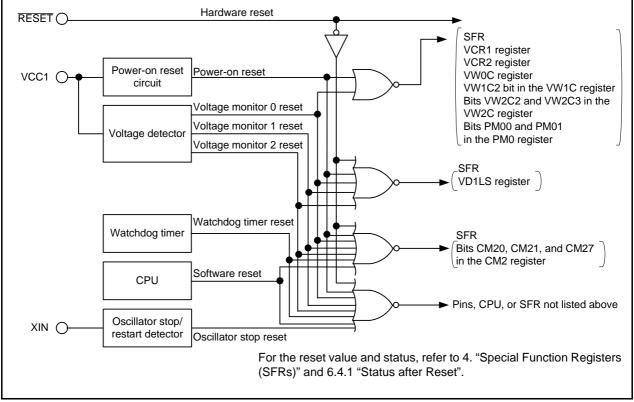

| 2. | Cen    | ntral Processing Unit (CPU)                                |     |

|    | 2.1    | Data Registers (R0, R1, R2, and R3)                        |     |

|    | 2.2    | Address Registers (A0 and A1)                              |     |

|    | 2.3    | Frame Base Register (FB)                                   | 24  |

|    | 2.4    | Interrupt Table Register (INTB)                            | 24  |

|    | 2.5    | Program Counter (PC)                                       | 24  |

|    | 2.6    | User Stack Pointer (USP) and Interrupt Stack Pointer (ISP) | 24  |

|    | 2.7    | Static Base Register (SB)                                  | 24  |

|    | 2.8    | Flag Register (FLG)                                        | 24  |

|    | 2.8.   | .1 Carry Flag (C Flag)                                     | 24  |

|    | 2.8.2  | .2 Debug Flag (D Flag)                                     | 24  |

|    | 2.8.3  | .3 Zero Flag (Z Flag)                                      | 24  |

|    | 2.8.4  | .4 Sign Flag (S Flag)                                      | 24  |

|    | 2.8.   | .5 Register Bank Select Flag (B Flag)                      | 24  |

|    | 2.8.   | .6 Overflow Flag (O Flag)                                  | 24  |

|    | 2.8.   | .7 Interrupt Enable Flag (I Flag)                          | 24  |

|    | 2.8.   | .8 Stack Pointer Select Flag (U Flag)                      | 25  |

|    | 2.8.9  | .9 Processor Interrupt Priority Level (IPL)                | 25  |

|    | 2.8.   | .10 Reserved Areas                                         | 25  |

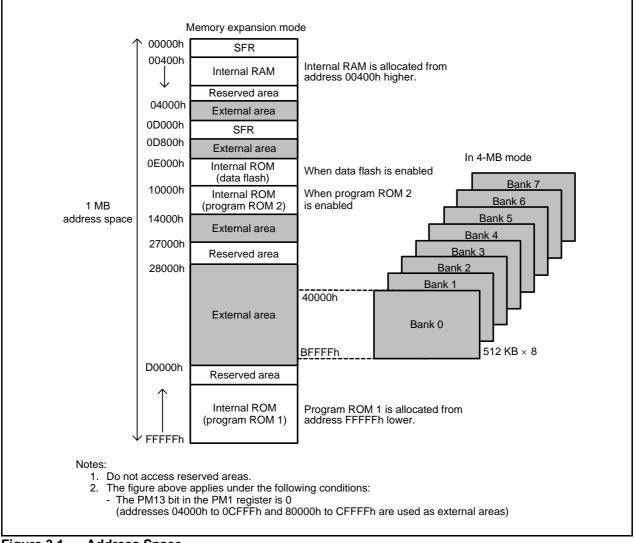

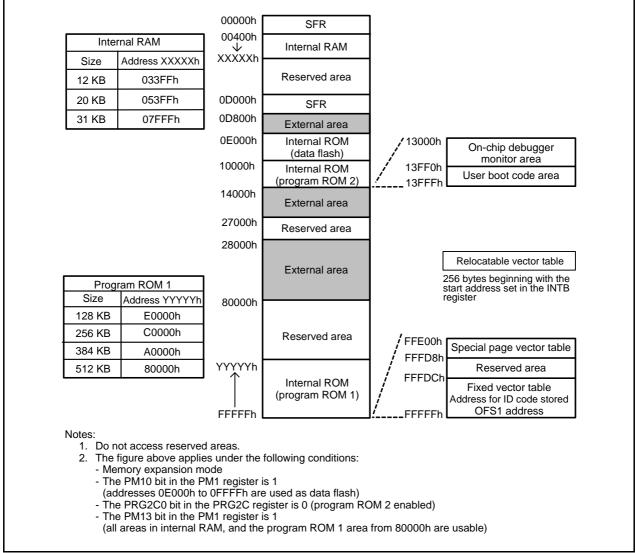

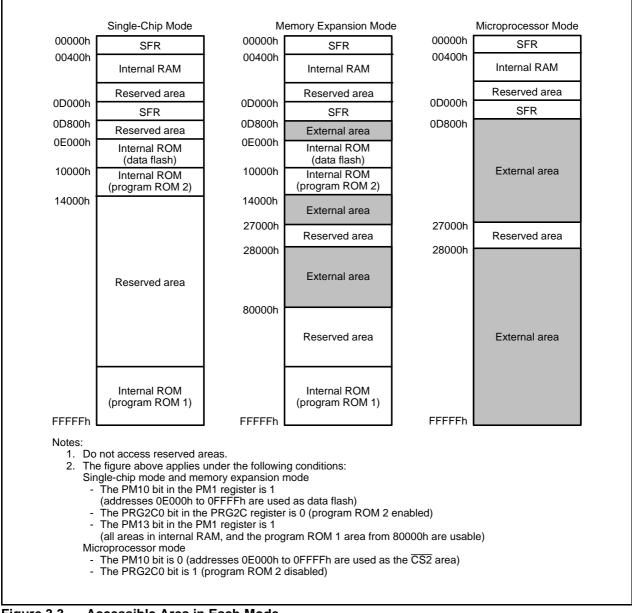

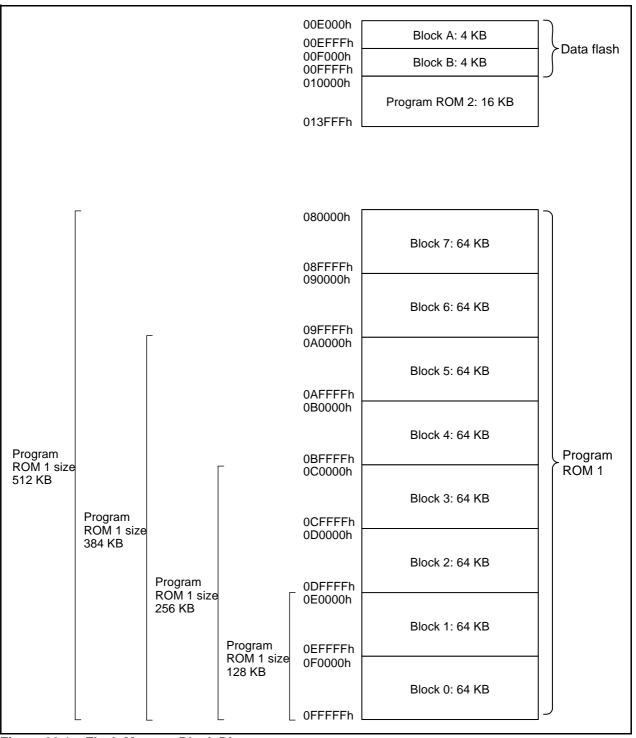

| 3. | Add    | dress Space                                                | 26  |

|    | 3.1    | Address Space                                              |     |

|    | 3.2    | Memory Map                                                 | 27  |

|    | 3.3    | Accessible Area in Each Mode                               |     |

| 4. | Spe  | cial  | Function Registers (SFRs)                               | 29 |

|----|------|-------|---------------------------------------------------------|----|

|    | 4.1  | SFF   | २ड                                                      | 29 |

|    | 4.2  | Not   | es on SFRs                                              | 45 |

|    | 4.2. | 1     | Register Settings                                       | 45 |

| 5. | Prot | tecti | on                                                      |    |

|    | 5.1  | Intro | oduction                                                |    |

|    | 5.2  | Reg   | gister                                                  |    |

|    | 5.2. | 1     | Protect Register (PRCR)                                 | 46 |

|    | 5.3  | Not   | es on Protection                                        | 48 |

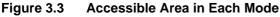

| 6. | Res  | ets   |                                                         |    |

|    | 6.1  | Intro | oduction                                                |    |

|    | 6.2  | Reg   | gisters                                                 | 50 |

|    | 6.2. | 1     | Processor Mode Register 0 (PM0)                         | 51 |

|    | 6.2. | 2     | Reset Source Determine Register (RSTFR)                 | 52 |

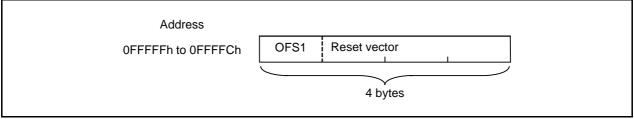

|    | 6.3  | Opt   | ional Function Select Area                              | 53 |

|    | 6.3. | 1     | Optional Function Select Address 1 (OFS1)               | 53 |

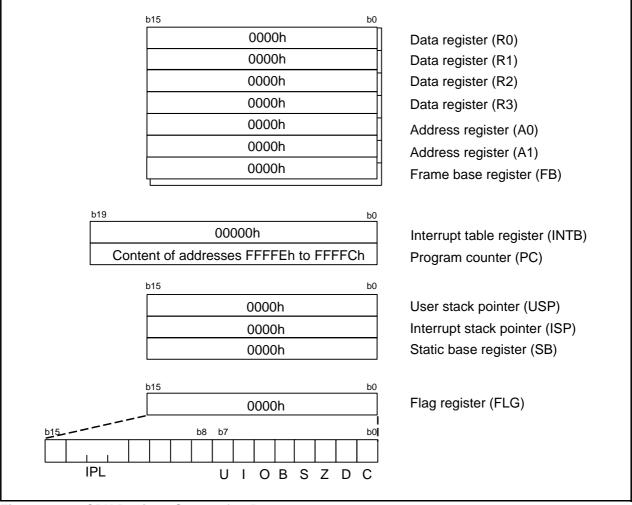

|    | 6.4  | Ope   | erations                                                | 55 |

|    | 6.4. | 1     | Status after Reset                                      | 55 |

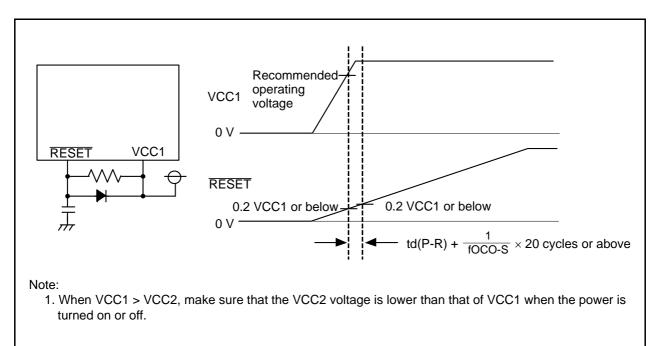

|    | 6.4. | 2     | Hardware Reset                                          | 58 |

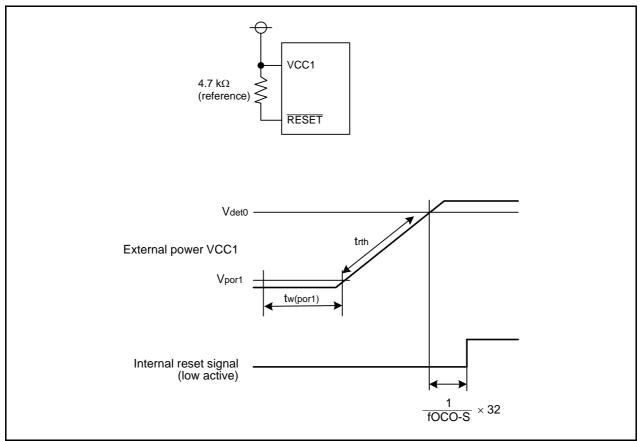

|    | 6.4. | 3     | Power-On Reset Function                                 | 59 |

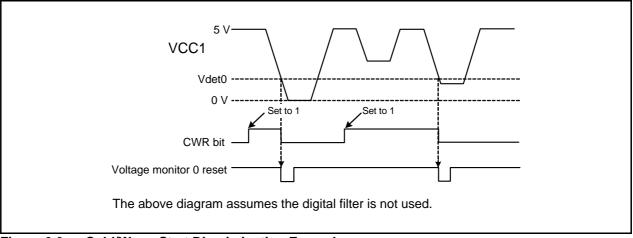

|    | 6.4. | 4     | Voltage Monitor 0 Reset                                 | 60 |

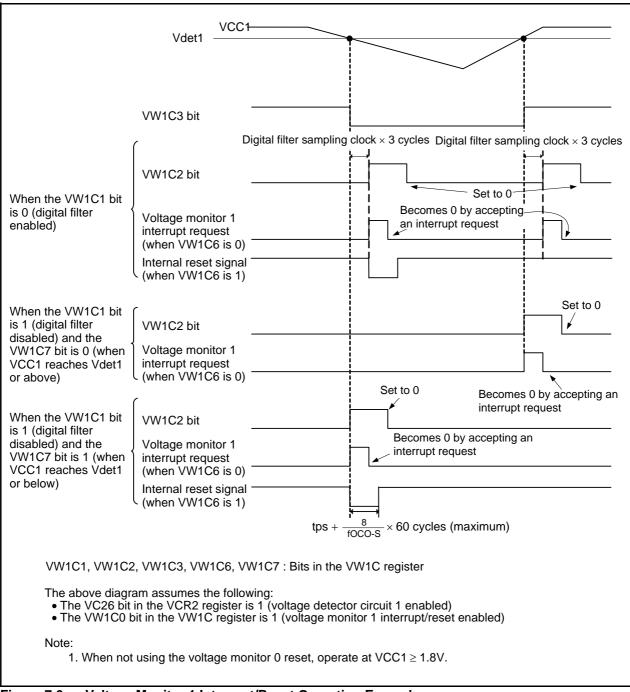

|    | 6.4. | 5     | Voltage Monitor 1 Reset                                 | 60 |

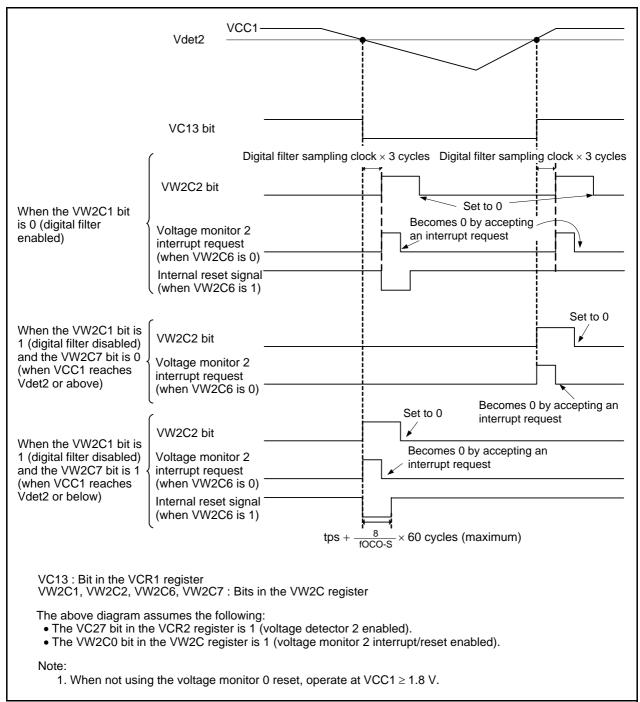

|    | 6.4. | 6     | Voltage Monitor 2 Reset                                 | 60 |

|    | 6.4. | 7     | Oscillator Stop Detect Reset                            | 61 |

|    | 6.4. | 8     | Watchdog Timer Reset                                    | 61 |

|    | 6.4. | 9     | Software Reset                                          | 61 |

|    | 6.4. | 10    | Cold/Warm Start Discrimination                          | 62 |

|    | 6.5  | Not   | es on Resets                                            |    |

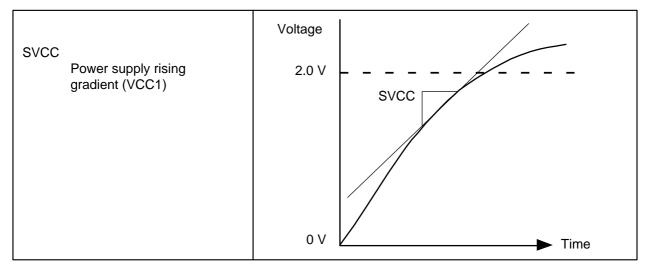

|    | 6.5. | 1     | Power Supply Rising Gradient                            |    |

|    | 6.5. | 2     | Power-On Reset                                          |    |

|    | 6.5. | 3     | OSDR Bit (Oscillation Stop Detect Reset Detection Flag) | 63 |

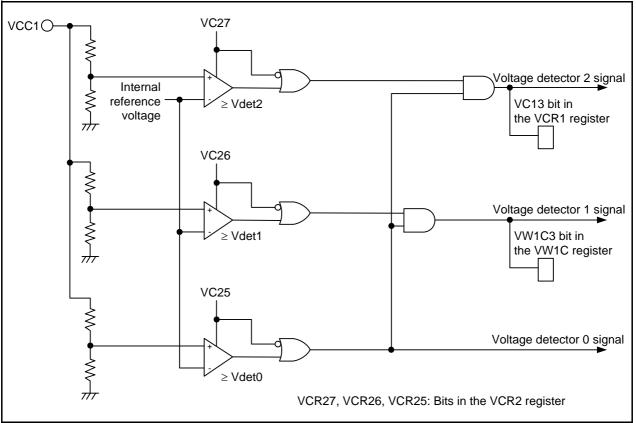

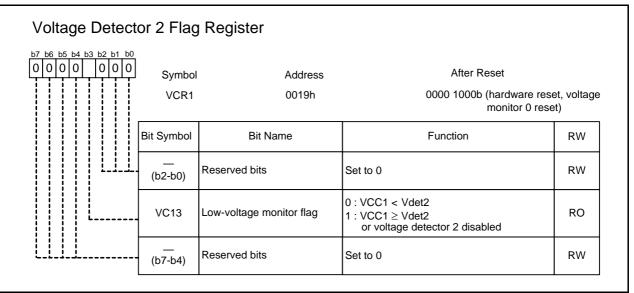

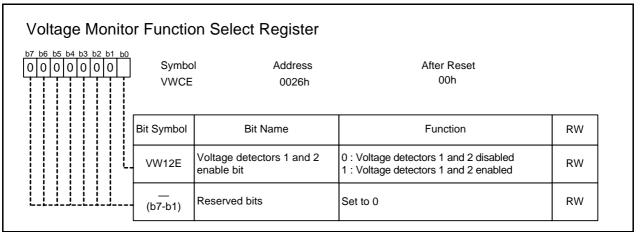

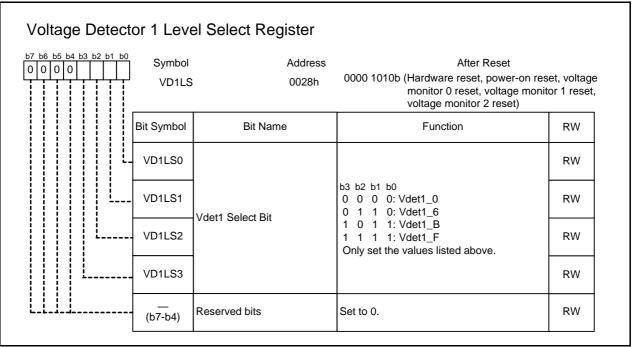

| 7. | Volt | age   | Detector                                                | 64 |

|    | 7.1  | Intro | oduction                                                | 64 |

|    | 7.2 R  | egisters                                            |     |

|----|--------|-----------------------------------------------------|-----|

|    | 7.2.1  | Voltage Detector 2 Flag Register (VCR1)             | 67  |

|    | 7.2.2  | Voltage Detector Operation Enable Register (VCR2)   |     |

|    | 7.2.3  | Voltage Monitor Function Select Register (VWCE)     | 69  |

|    | 7.2.4  | Voltage Detector 1 Level Select Register (VD1LS)    | 70  |

|    | 7.2.5  | Voltage Monitor 0 Control Register (VW0C)           | 71  |

|    | 7.2.6  | Voltage Monitor 1 Control Register (VW1C)           | 72  |

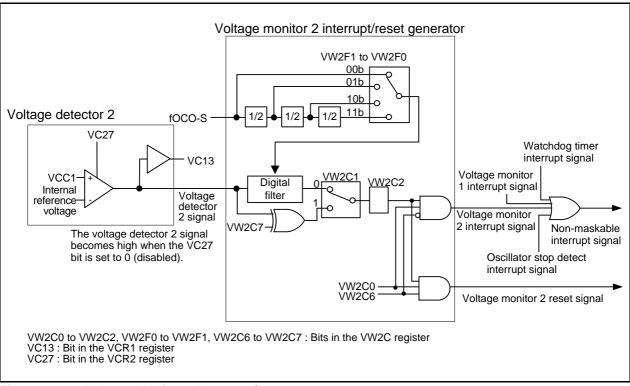

|    | 7.2.7  | Voltage Monitor 2 Control Register (VW2C)           | 74  |

|    | 7.3 O  | ptional Function Select Area                        | 76  |

|    | 7.3.1  | Optional Function Select Address 1 (OFS1)           | 76  |

|    | 7.4 O  | perations                                           | 77  |

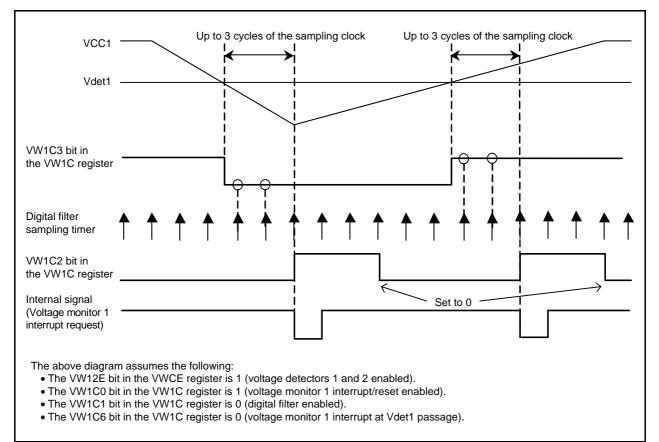

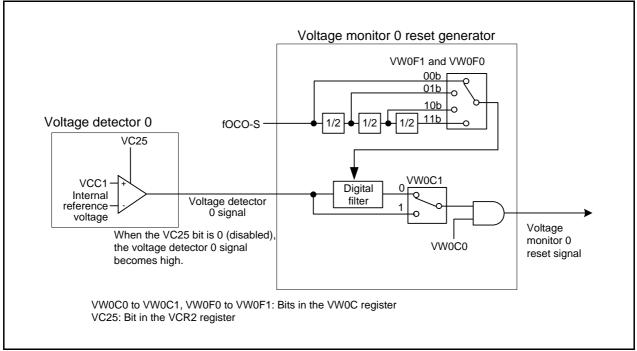

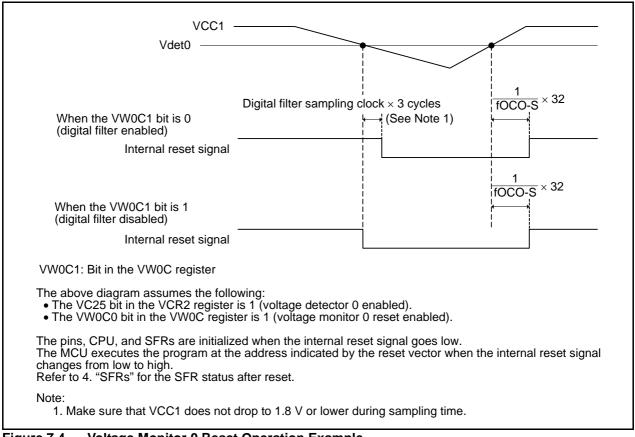

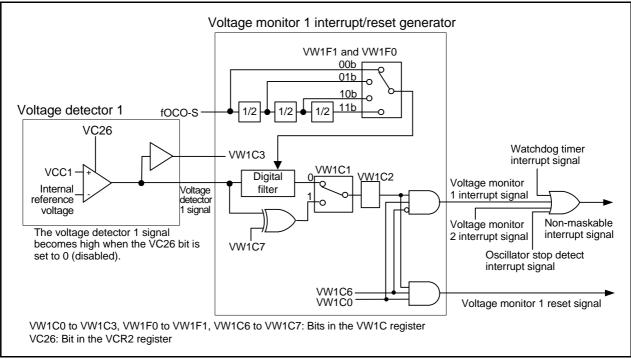

|    | 7.4.1  | Digital Filter                                      | 77  |

|    | 7.4.2  | Voltage Detector 0                                  | 78  |

|    | 7.4.3  | Voltage Detector 1                                  | 80  |

|    | 7.4.4  | Voltage Detector 2                                  |     |

|    | 7.5 Ir | iterrupts                                           |     |

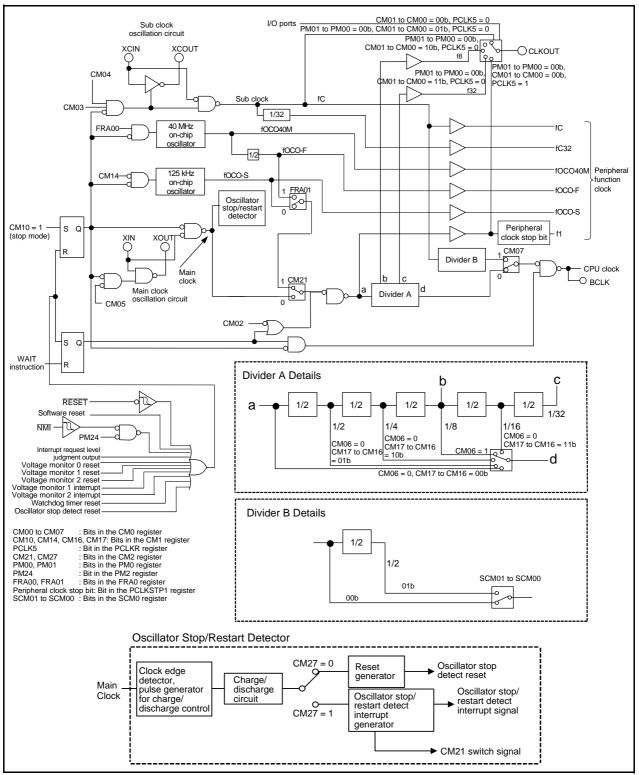

| 8. | Clock  | Generator                                           |     |

|    | 8.1 Ir | troduction                                          |     |

|    | 8.2 R  | egisters                                            |     |

|    | 8.2.1  | Processor Mode Register 0 (PM0)                     |     |

|    | 8.2.2  | System Clock Control Register 0 (CM0)               | 91  |

|    | 8.2.3  | System Clock Control Register 1 (CM1)               |     |

|    | 8.2.4  | Oscillation Stop Detection Register (CM2)           |     |

|    | 8.2.5  | Peripheral Clock Select Register (PCLKR)            |     |

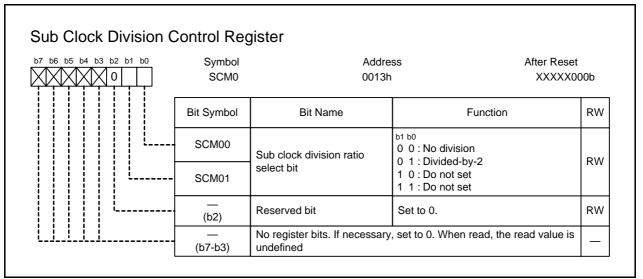

|    | 8.2.6  | Sub Clock Division Control Register (SCM0)          |     |

|    | 8.2.7  | Peripheral Clock Stop Register (PCLKSTP1)           |     |

|    | 8.2.8  | Processor Mode Register 2 (PM2)                     |     |

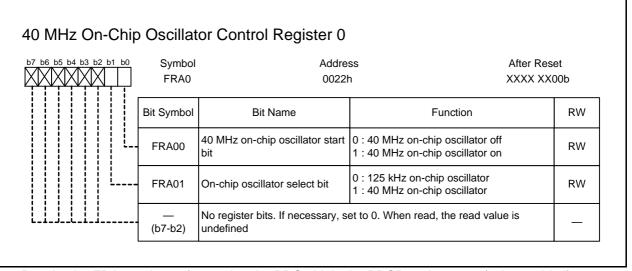

|    | 8.2.9  | 40 MHz On-Chip Oscillator Control Register 0 (FRA0) | 100 |

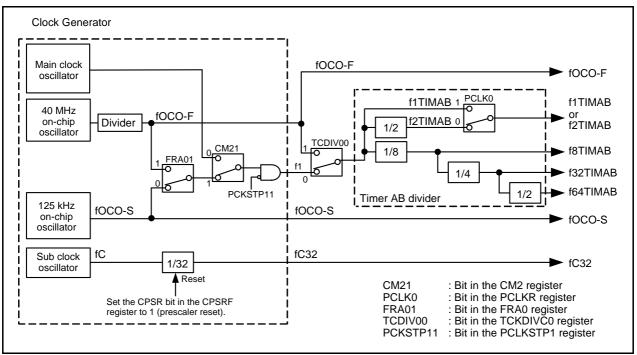

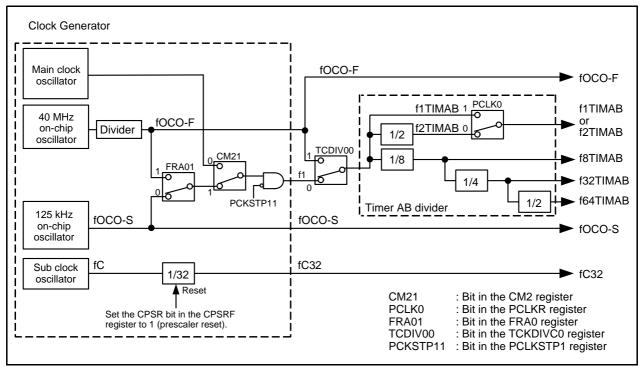

|    | 8.3 C  | locks Generated by Clock Generators                 | 101 |

|    | 8.3.1  | Main Clock                                          | 101 |

|    | 8.3.2  | fOCO40M                                             |     |

|    | 8.3.3  | fOCO-F                                              |     |

|    | 8.3.4  | 125 kHz On-Chip Oscillator Clock (fOCO-S)           |     |

|    | 8.3.5  | Sub Clock (fC)                                      | 103 |

|       | 8.4   | CP    | U Clock and Peripheral Function Clocks                                  | . 104 |

|-------|-------|-------|-------------------------------------------------------------------------|-------|

| 8.4.1 |       | 1     | CPU Clock and BCLK                                                      | . 104 |

|       | 8.4.2 |       | Peripheral Function Clocks (f1, fOCO40M, fOCO-F, fOCO-S, fC32, fC)      | . 104 |

|       | 8.5   | Clo   | ck Output Function                                                      | . 106 |

|       | 8.6   | Sys   | stem Clock Protection Function                                          | . 106 |

|       | 8.7   | Osc   | cillator Stop/Restart Detect Function                                   | . 107 |

|       | 8.7.  | 1     | Operation When CM27 Bit is 0 (Oscillator Stop Detect Reset)             | . 107 |

|       | 8.7.  | 2     | Operation When CM27 Bit is 1 (Oscillator Stop/Restart Detect Interrupt) | 108   |

|       | 8.7.  | 3     | Using the Oscillator Stop/Restart Detect Function                       | . 109 |

|       | 8.8   | Inte  | errupt                                                                  | . 109 |

|       | 8.9   | Not   | es on Clock Generator                                                   | . 110 |

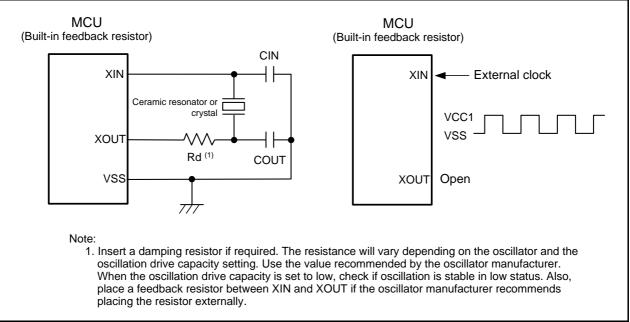

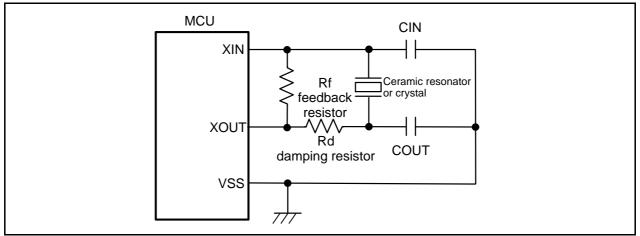

|       | 8.9.  | 1     | Oscillation Circuit Using an Oscillator                                 | . 110 |

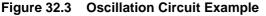

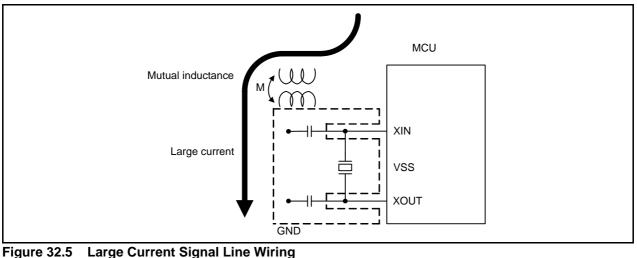

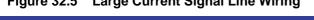

|       | 8.9.  | 2     | Noise Countermeasure                                                    | 111   |

|       | 8.9.  | 3     | CPU Clock                                                               | . 112 |

|       | 8.9.  | 4     | Oscillation Stop/Restart Detect Function                                | . 112 |

| 9.    | Pov   | ver ( | Control                                                                 | 113   |

|       | 9.1   | Intr  | oduction                                                                | . 113 |

|       | 9.2   | Red   | gisters                                                                 | . 113 |

|       | 9.2.  | 1     | Flash Memory Control Register 0 (FMR0)                                  | . 114 |

|       | 9.2.  | 2     | Flash Memory Control Register 2 (FMR2)                                  |       |

|       | 9.3   | Clo   | ck                                                                      |       |

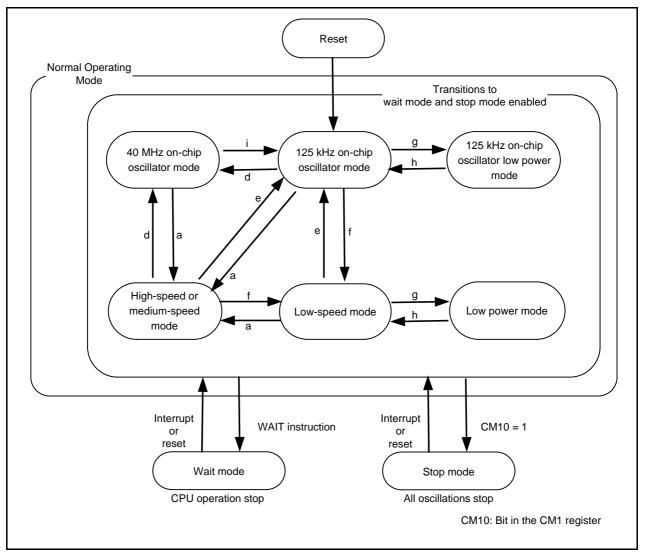

|       | 9.3.  | 1     | Normal Operating Mode                                                   | . 116 |

|       | 9.3.  | 2     | Clock Mode Transition Procedure                                         | . 120 |

|       | 9.3.  | 3     | Wait Mode                                                               | . 122 |

|       | 9.3.  | 4     | Stop Mode                                                               | . 125 |

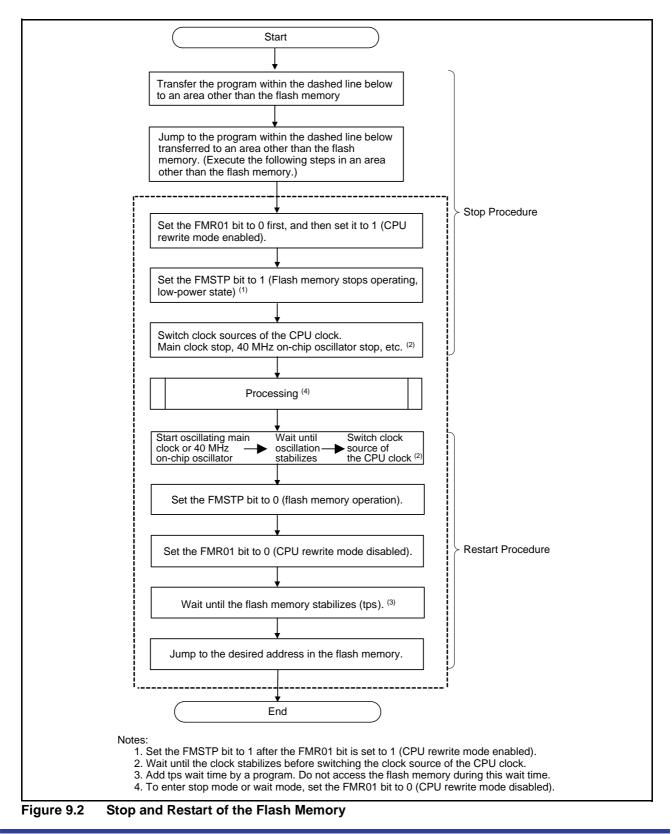

|       | 9.4   | Pov   | wer Control in Flash Memory                                             | . 127 |

|       | 9.4.  | 1     | Stopping Flash Memory                                                   | . 127 |

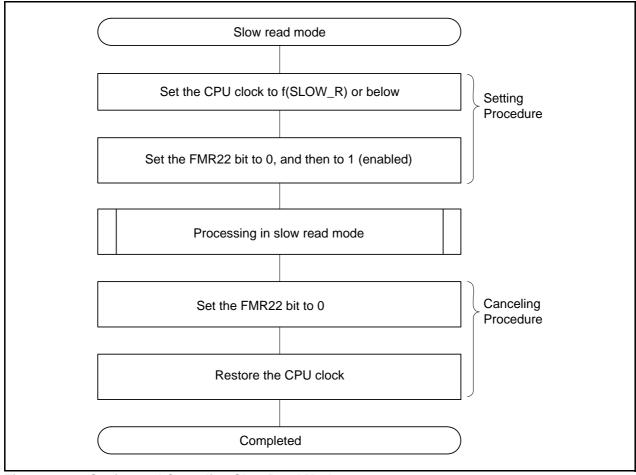

|       | 9.4.  | 2     | Reading Flash Memory                                                    | . 128 |

|       | 9.5   | Red   | ducing Power Consumption                                                | . 130 |

|       | 9.5.  | 1     | Ports                                                                   | . 130 |

|       | 9.5.  | 2     | A/D Converter                                                           | . 130 |

|       | 9.5.  | 3     | D/A Converter                                                           | . 130 |

|       | 9.5.  | 4     | Stopping Peripheral Functions                                           | . 130 |

|       | 9.5.  | 5     | Switching the Oscillation-Driving Capacity                              | . 130 |

| 9.6 No     | tes on Power Control                                                |

|------------|---------------------------------------------------------------------|

| 9.6.1      | CPU Clock                                                           |

| 9.6.2      | Wait Mode131                                                        |

| 9.6.3      | Stop Mode                                                           |

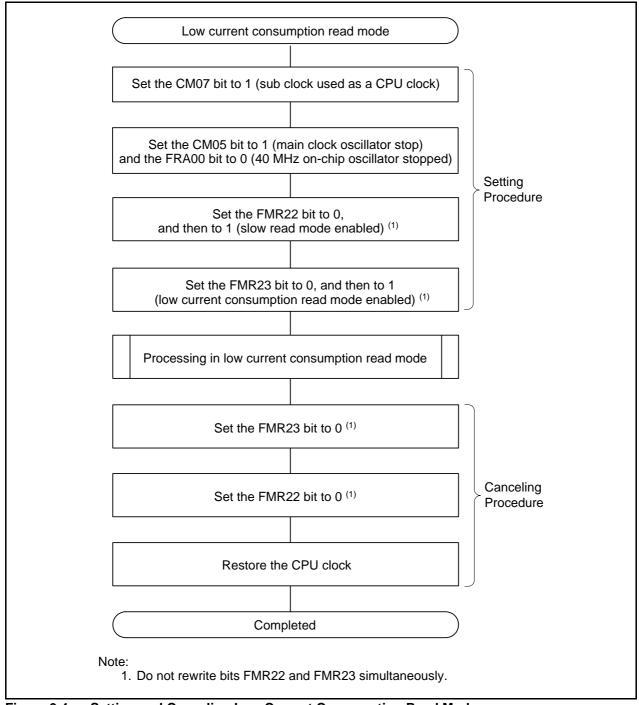

| 9.6.4      | Low Current Consumption Read Mode132                                |

| 10. Proces | sor Mode                                                            |

| 10.1 Inti  | oduction                                                            |

| 10.2 Re    | gisters                                                             |

| 10.2.1     | Processor Mode Register 0 (PM0)134                                  |

| 10.2.2     | Processor Mode Register 1 (PM1)135                                  |

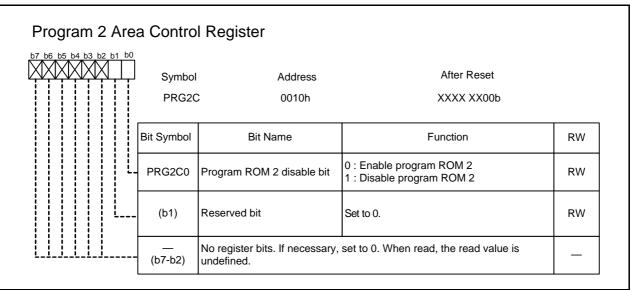

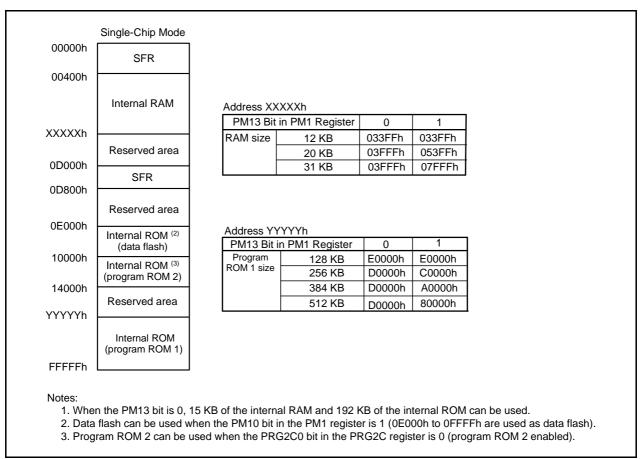

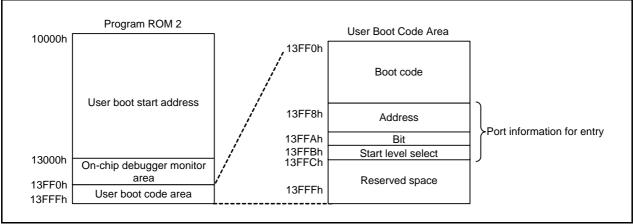

| 10.2.3     | Program 2 Area Control Register (PRG2C)137                          |

| 10.3 Op    | erations                                                            |

| 10.3.1     | Processor Mode Settings                                             |

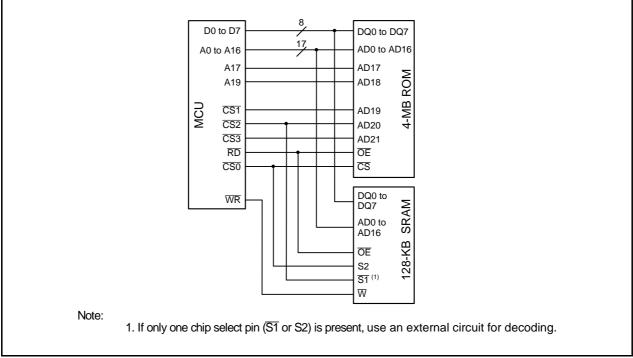

| 11. Bus    |                                                                     |

|            | oduction                                                            |

|            | gisters                                                             |

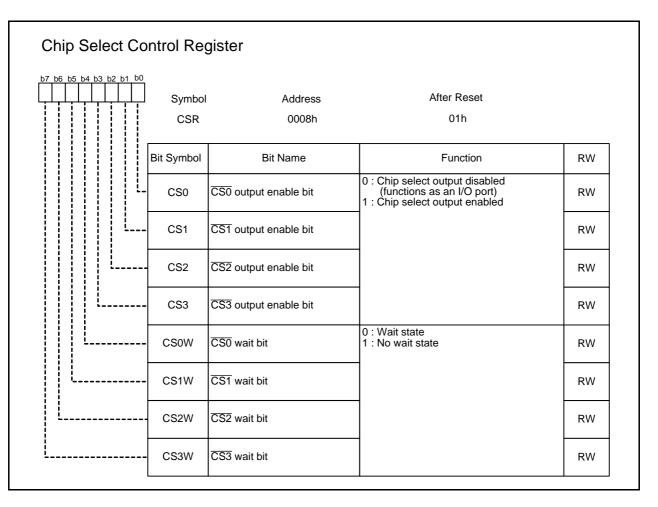

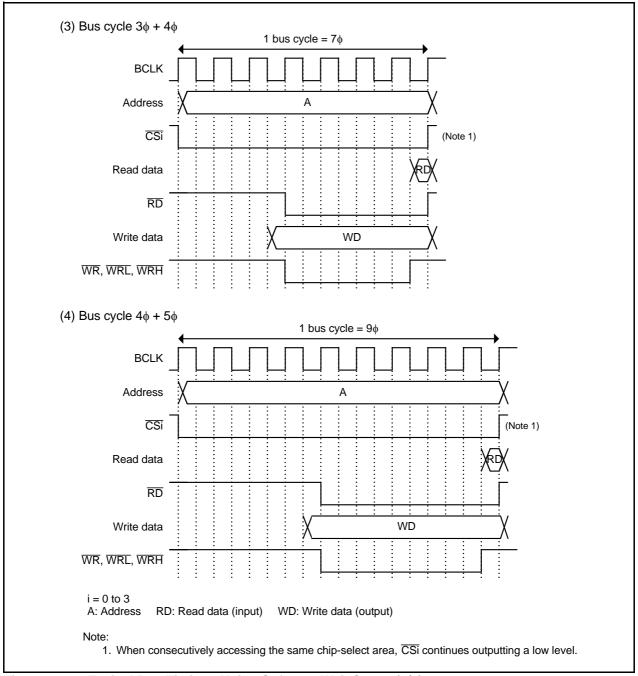

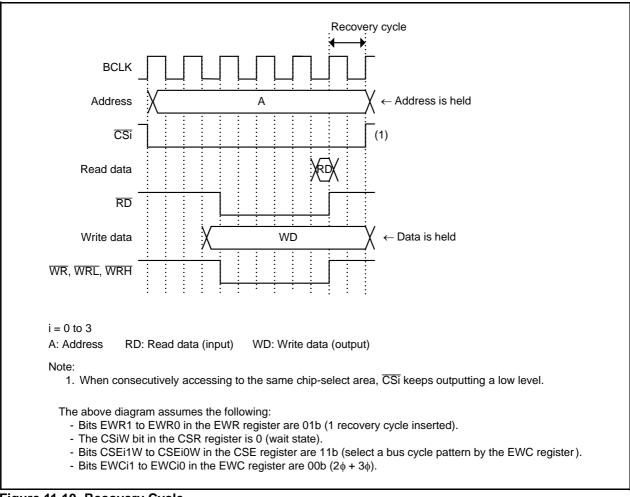

| 11.2.1     | Chip Select Control Register (CSR)                                  |

| 11.2.2     | Chip Select Expansion Control Register (CSE)                        |

| 11.2.3     | External Area Wait Control Expansion Register (EWC)                 |

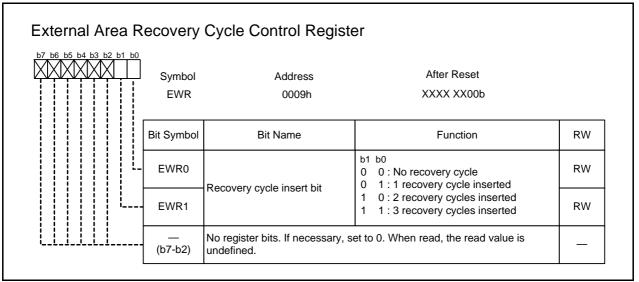

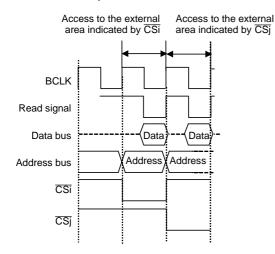

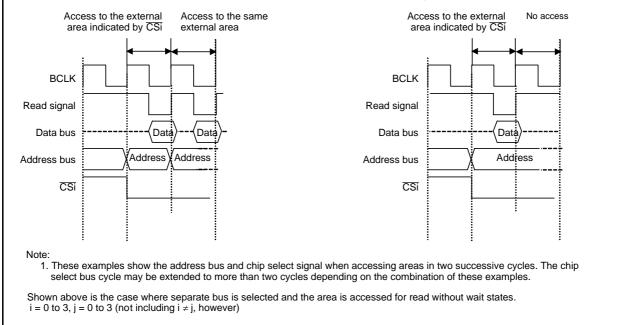

| 11.2.4     | External Area Recovery Cycle Control Register (EWR)                 |

|            | erations                                                            |

| •          | Common Specifications between the Internal Bus and External Bus 145 |

| 11.3.2     | Internal Bus                                                        |

| 11.3.3     | External Bus147                                                     |

| 11.3.4     | External Bus Mode147                                                |

| 11.3.5     | External Bus Control                                                |

| 11.4 No    | tes on Bus                                                          |

| 11.4.1     | Reading Data Flash                                                  |

| 11.4.2     | External Bus                                                        |

| 11.4.3     | External Access Immediately after Writing to the SFRs               |

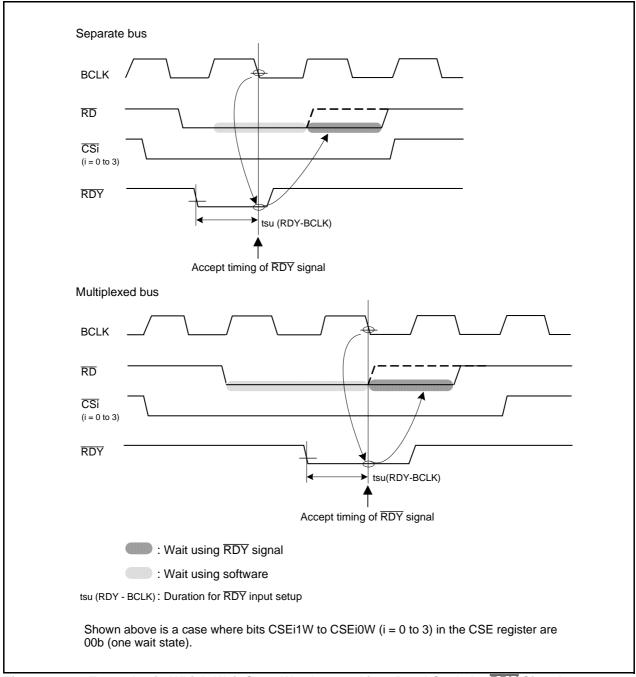

| 11.4.4     | Wait and RDY                                                        |

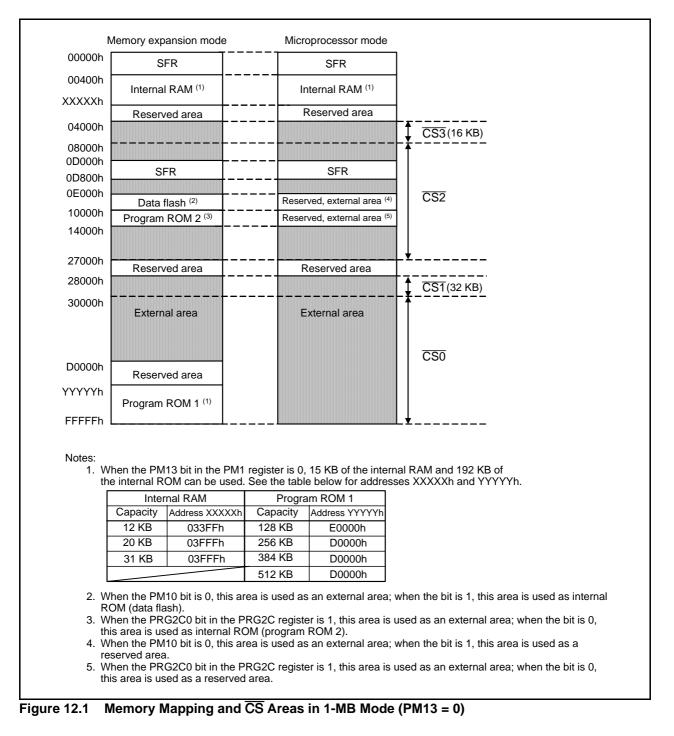

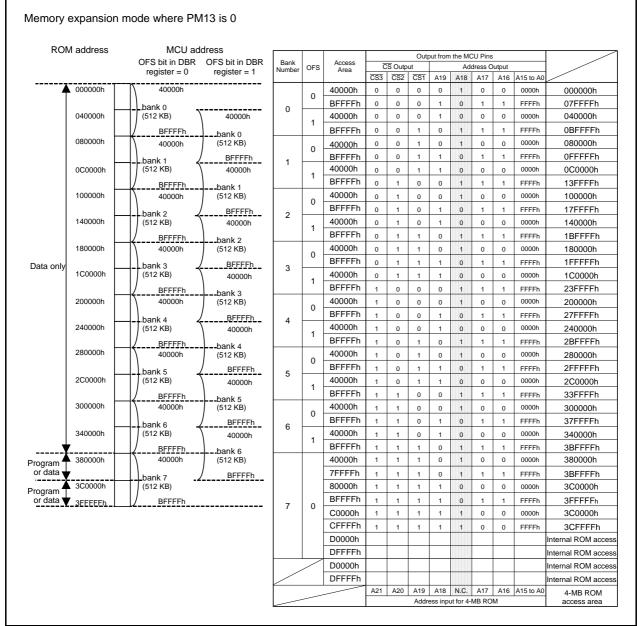

| 12. Memor  | y Space Expansion Function                                          |

|            | oduction                                                            |

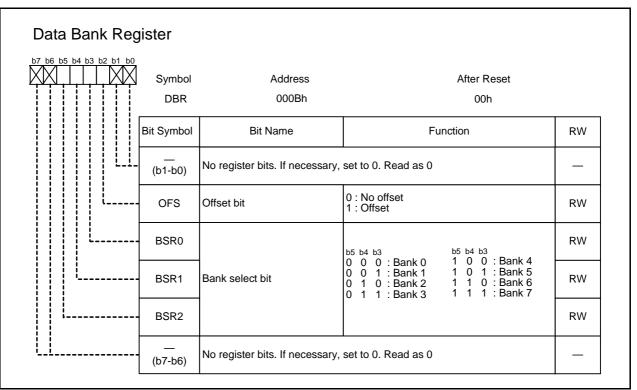

| 12.2     | Re   | gisters                                                                                                                                                                                                                                                                                               |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12.2     | 2.1  | Data Bank Register (DBR)163                                                                                                                                                                                                                                                                           |

| 12.3     | Ope  | erations164                                                                                                                                                                                                                                                                                           |

| 12.3     | 3.1  | 1-MB Mode                                                                                                                                                                                                                                                                                             |

| 12.3     | 3.2  | 4-MB Mode                                                                                                                                                                                                                                                                                             |

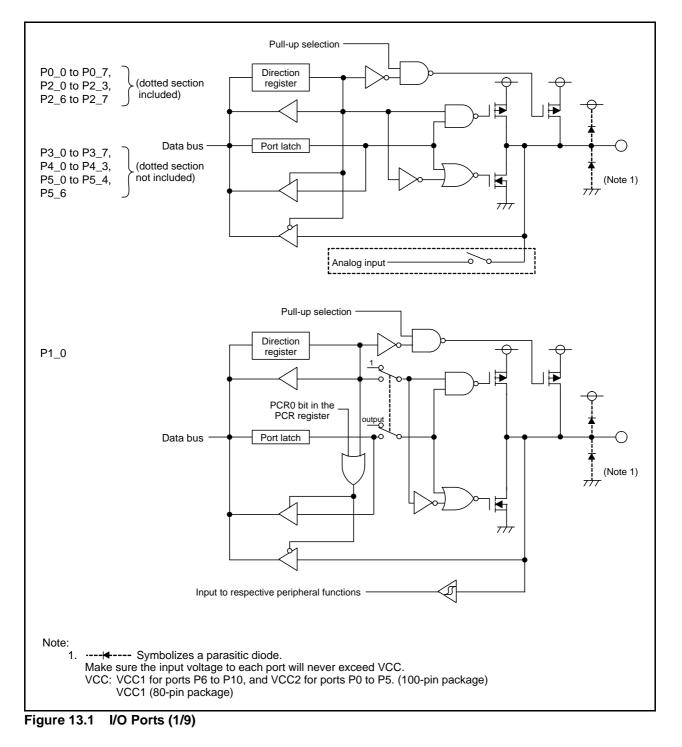

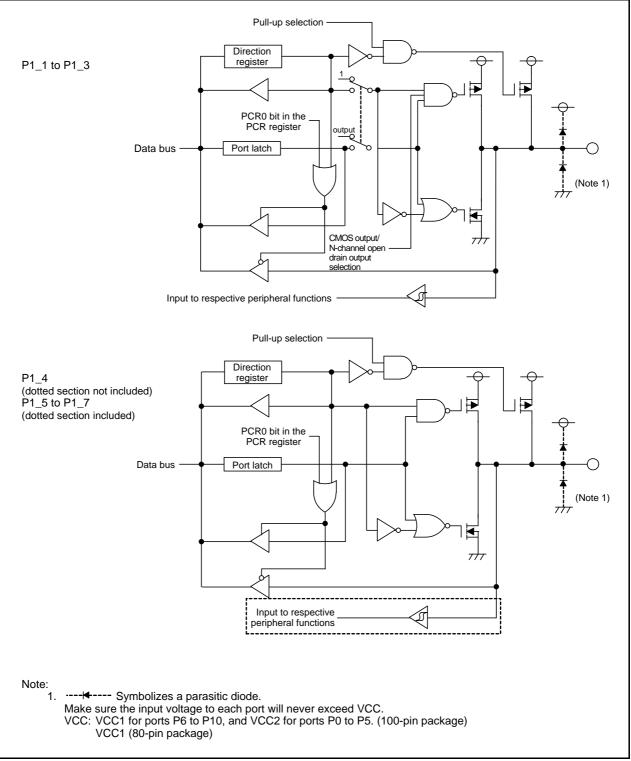

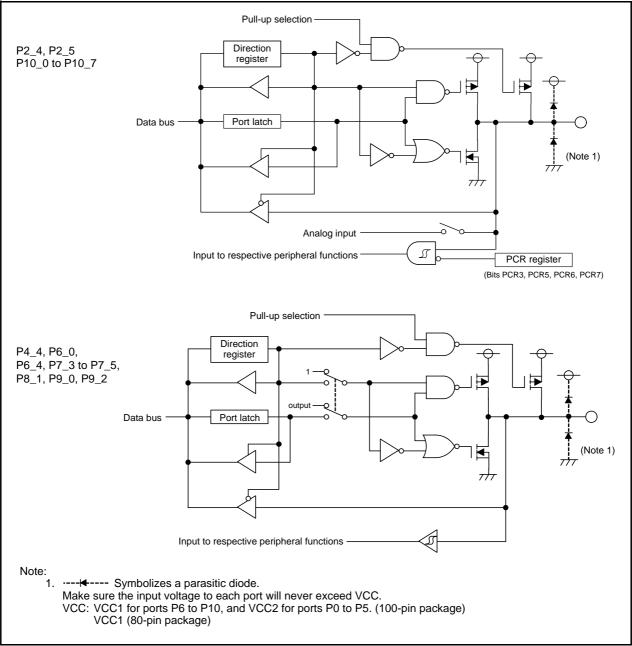

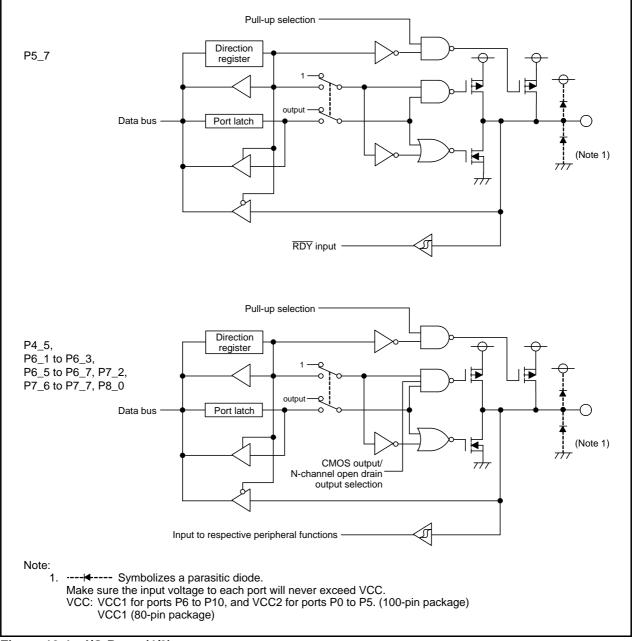

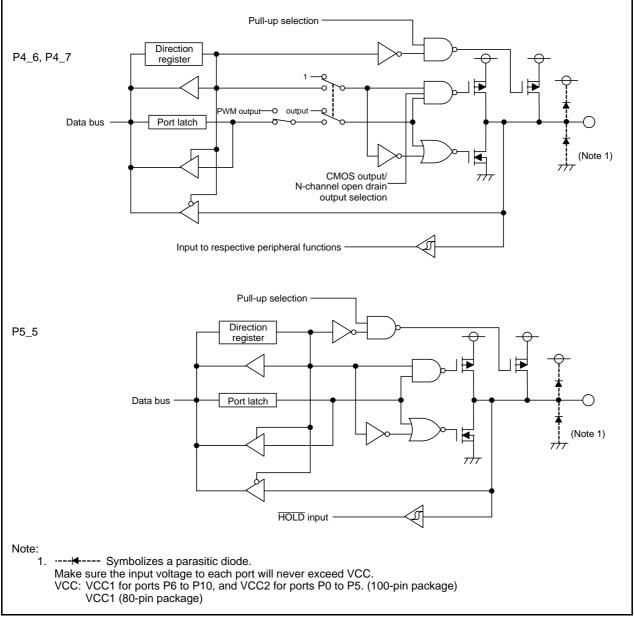

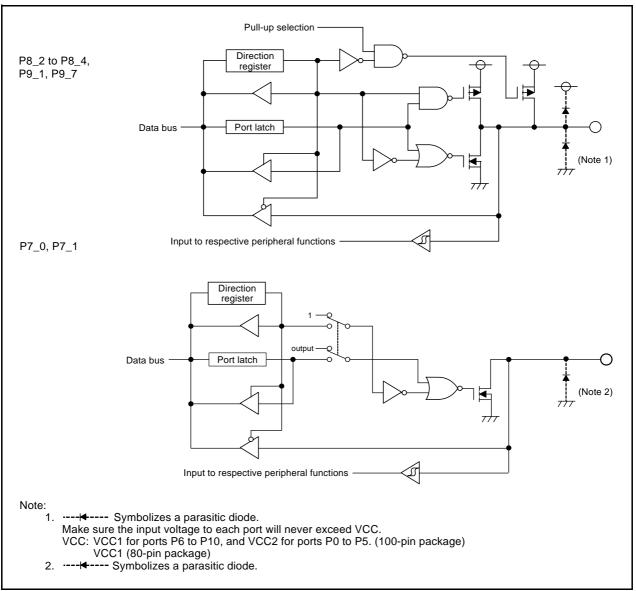

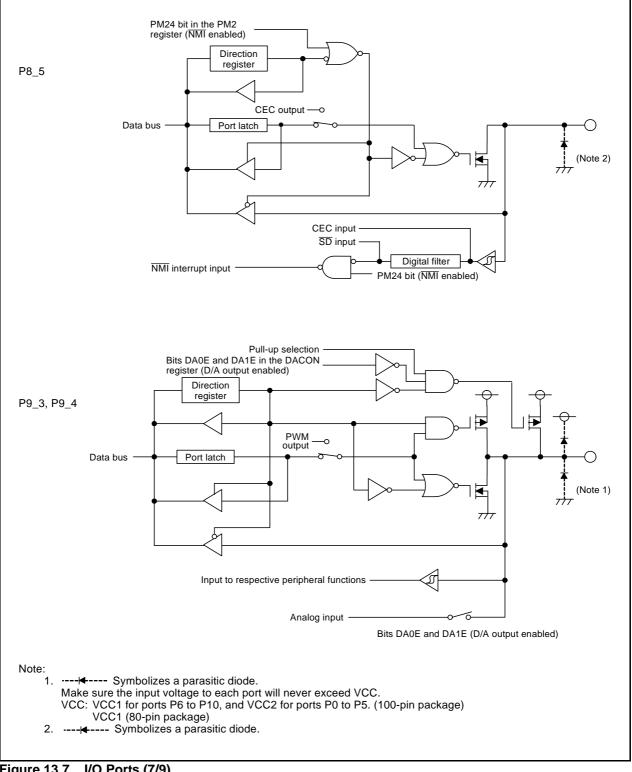

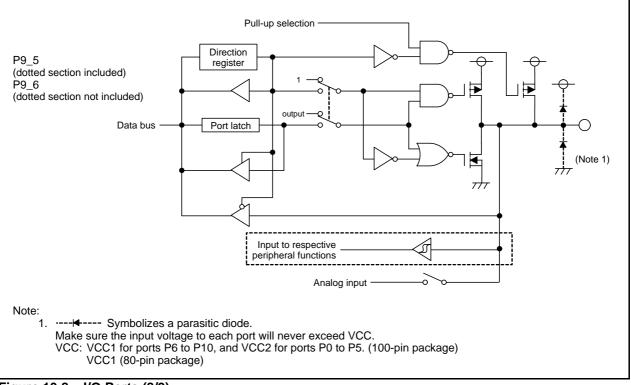

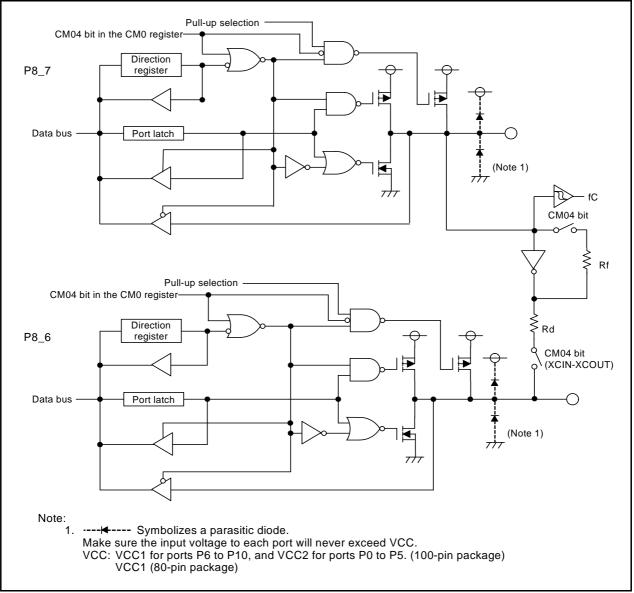

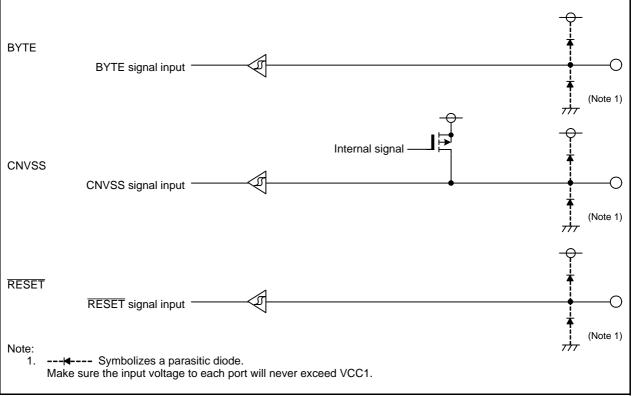

| 13. Pro  | grar | nmable I/O Ports173                                                                                                                                                                                                                                                                                   |

| 13.1     | Intr | oduction173                                                                                                                                                                                                                                                                                           |

| 13.2     | I/O  | Ports and Pins                                                                                                                                                                                                                                                                                        |

| 13.3     | Re   | gisters                                                                                                                                                                                                                                                                                               |

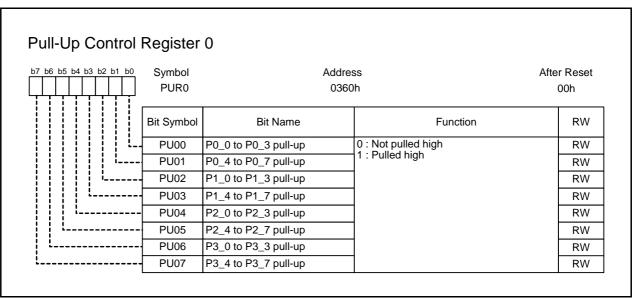

| 13.3     | 3.1  | Pull-Up Control Register 0 (PUR0)                                                                                                                                                                                                                                                                     |

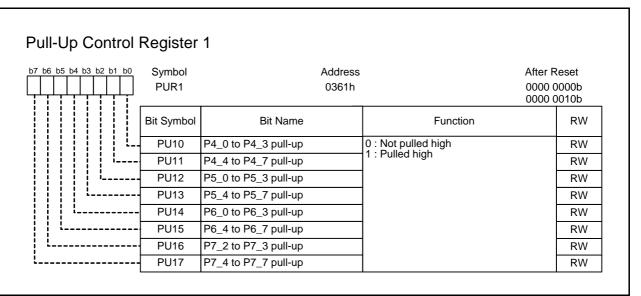

| 13.3     | 3.2  | Pull-Up Control Register 1 (PUR1)                                                                                                                                                                                                                                                                     |

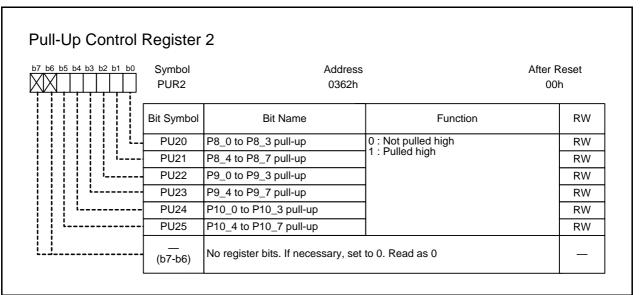

| 13.3     | 3.3  | Pull-Up Control Register 2 (PUR2)                                                                                                                                                                                                                                                                     |

| 13.3     | 3.4  | Port Control Register (PCR)                                                                                                                                                                                                                                                                           |

| 13.3     | 3.5  | Port Pi Register (Pi) (i = 0 to 10)                                                                                                                                                                                                                                                                   |

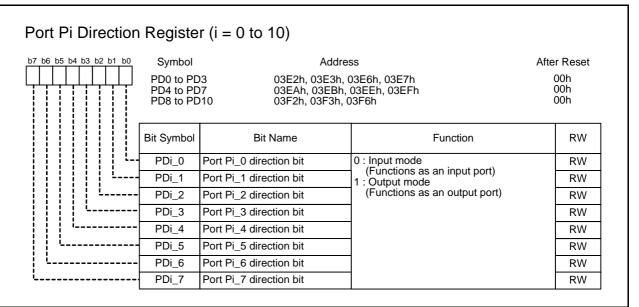

| 13.3     | 3.6  | Port Pi Direction Register (PDi) (i = 0 to 10)190                                                                                                                                                                                                                                                     |

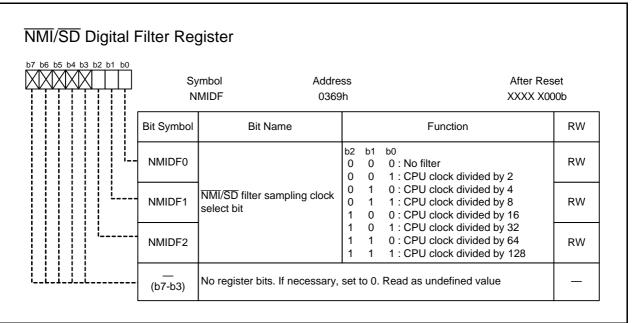

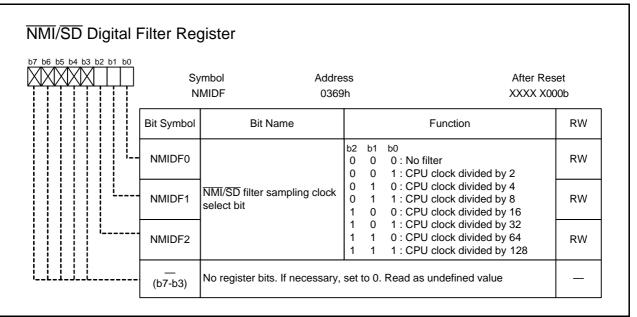

| 13.3     | 3.7  | NMI/SD Digital Filter Register (NMIDF)                                                                                                                                                                                                                                                                |

| 13.4     | Per  | ipheral Function I/O192                                                                                                                                                                                                                                                                               |

| 13.4     | 4.1  | Peripheral Function I/O and Port Direction Bits                                                                                                                                                                                                                                                       |

| 13.4     | 4.2  | Priority Level of Peripheral Function I/O192                                                                                                                                                                                                                                                          |

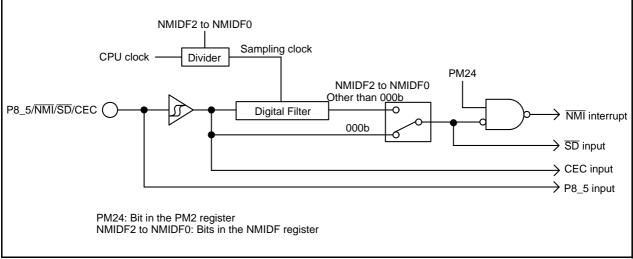

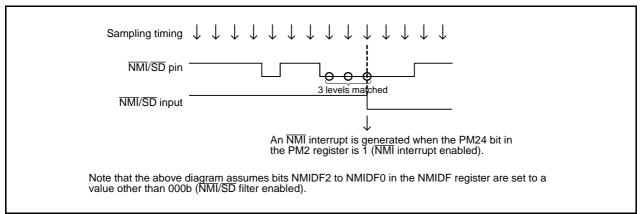

| 13.4     | 4.3  | NMI/SD Digital Filter                                                                                                                                                                                                                                                                                 |

| 13.4     | 4.4  | CNVSS Pin                                                                                                                                                                                                                                                                                             |

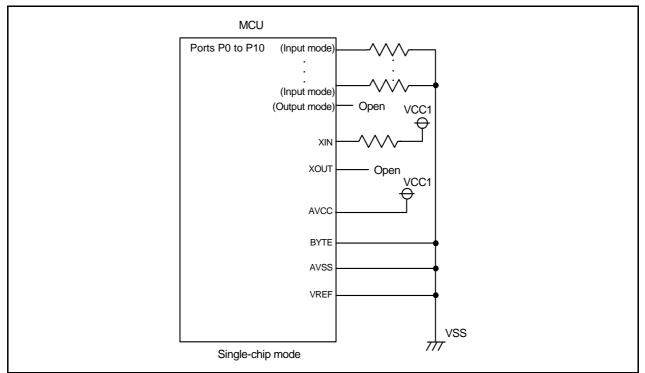

| 13.5     | Una  | assigned Pin Handling194                                                                                                                                                                                                                                                                              |

| 13.6     | Not  | es on Programmable I/O Ports                                                                                                                                                                                                                                                                          |

| 13.6     | 5.1  | Influence of the SD Input                                                                                                                                                                                                                                                                             |

| 13.6     | 6.2  | Influence of SI/O3 and SI/O4 196                                                                                                                                                                                                                                                                      |

| 13.6     | 6.3  | 80-Pin Package                                                                                                                                                                                                                                                                                        |

| 14. Inte | rrup | ots                                                                                                                                                                                                                                                                                                   |

| 14.1     | Intr | oduction197                                                                                                                                                                                                                                                                                           |

| 14.2     | Re   | gisters                                                                                                                                                                                                                                                                                               |

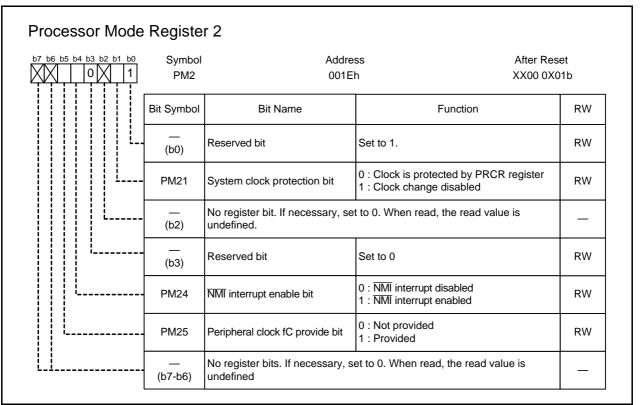

| 14.2     | 2.1  | Processor Mode Register 2 (PM2)                                                                                                                                                                                                                                                                       |

| 14.2     | 2.2  | Interrupt Control Register 1 (TB5IC, TB4IC/U1BCNIC, TB3IC/U0BCNIC,<br>BCNIC, DM0IC to DM3IC, ADIC, S0TIC to S2TIC, S0RIC to S2RIC, TA0IC<br>to TA4IC, TB0IC to TB2IC, U5BCNIC/CEC1IC, S5TIC/CEC2IC, S5RIC to<br>S7RIC, U6BCNIC/RTCTIC, S6TIC/RTCCIC, U7BCNIC/PMC0IC,<br>S7TIC/PMC1IC, IICIC, SCLDAIC) |

| 14.2  | 2.3         | Interrupt Control Register 2 (INT7IC, INT6IC, INT6IC, INT3IC, S4IC/INT5IC, S3IC/INT4IC, KUPIC, INT0IC to INT2IC) | 202   |

|-------|-------------|------------------------------------------------------------------------------------------------------------------|-------|

| 14.2  | Л           | Interrupt Source Select Register 3 (IFSR3A)                                                                      |       |

| 14.2  |             | Interrupt Source Select Register 2 (IFSR2A)                                                                      |       |

| 14.2  | -           | Interrupt Source Select Register (IFSR)                                                                          |       |

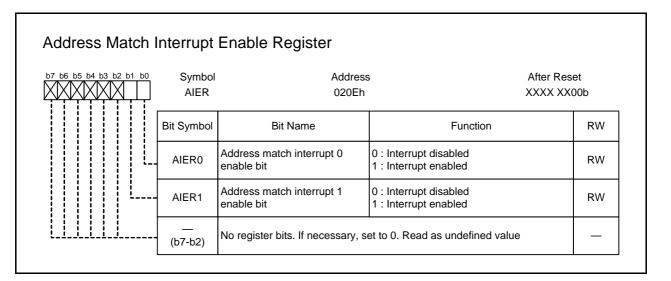

| 14.2  |             | Address Match Interrupt Enable Register (AIER)                                                                   |       |

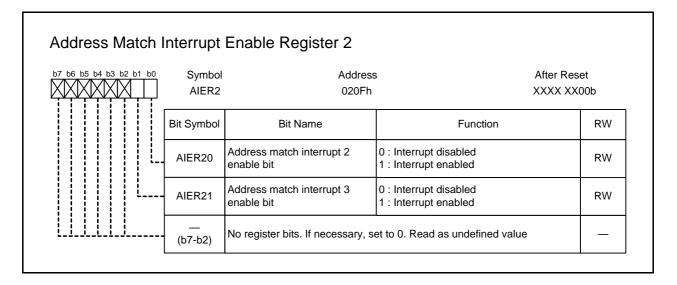

| 14.2  |             | Address Match Interrupt Enable Register 2 (AIER2)                                                                |       |

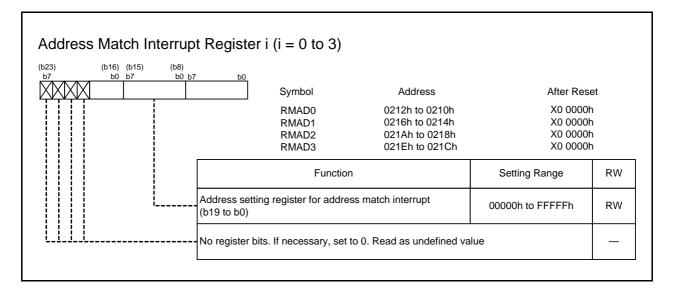

| 14.2  |             | Address Match Interrupt Register i (RMADi) (i = 0 to 3)                                                          |       |

| 14.2  |             |                                                                                                                  |       |

| 14.2  |             | Port Control Register (PCR)                                                                                      |       |

|       |             |                                                                                                                  |       |

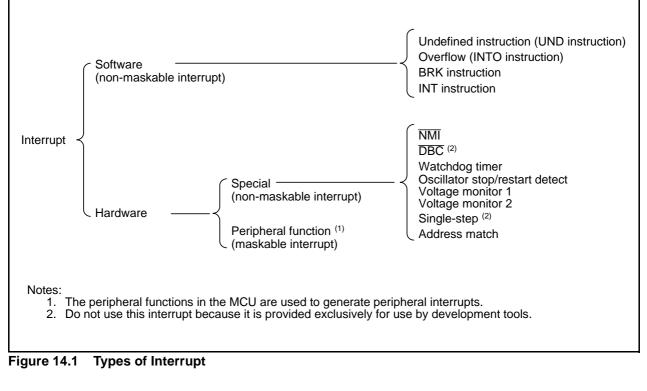

| 14.3  |             | es of Interrupt                                                                                                  |       |

| 14.4  |             | tware Interrupts                                                                                                 |       |

| 14.4  |             | Undefined Instruction Interrupt                                                                                  |       |

| 14.4  |             | Overflow Interrupt                                                                                               |       |

| 14.4  |             | BRK Interrupt                                                                                                    |       |

| 14.4  |             | INT Instruction Interrupt                                                                                        |       |

| 14.5  |             | dware Interrupts                                                                                                 |       |

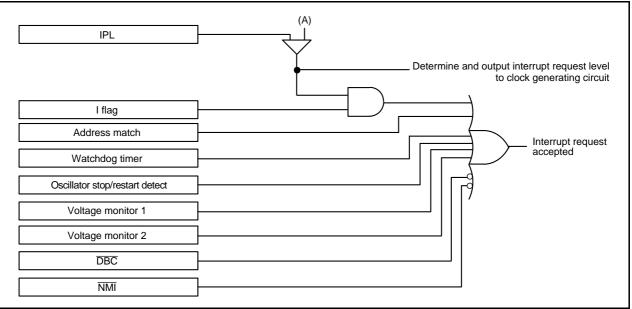

| 14.5  |             | Special Interrupts                                                                                               |       |

| 14.5  |             | Peripheral Function Interrupts                                                                                   |       |

| 14.6  |             | rrupts and Interrupt Vectors                                                                                     |       |

| 14.6  |             | Fixed Vector Tables                                                                                              |       |

| 14.6  | 6.2         | Relocatable Vector Tables                                                                                        | . 214 |

| 14.7  | Inte        | rrupt Control                                                                                                    | . 216 |

| 14.7  | <b>'</b> .1 | Maskable Interrupt Control                                                                                       | . 216 |

| 14.7  | 7.2         | Interrupt Sequence                                                                                               | . 217 |

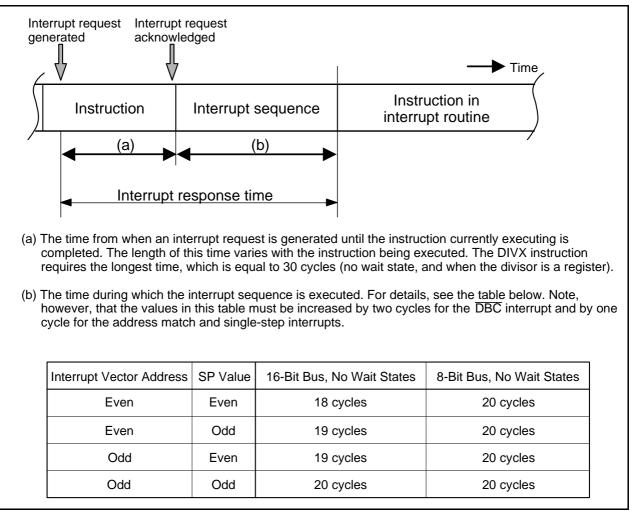

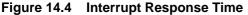

| 14.7  | 7.3         | Interrupt Response Time                                                                                          | . 218 |

| 14.7  | 7.4         | Variation of IPL When Interrupt Request is Accepted                                                              | . 218 |

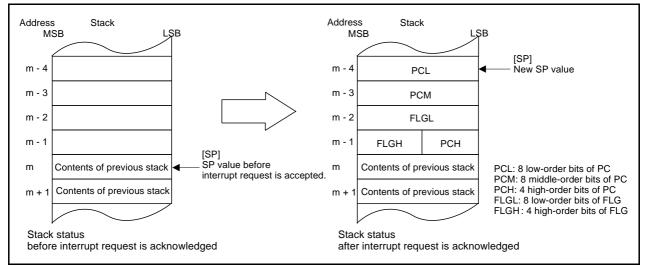

| 14.7  | <b>7</b> .5 | Saving Registers                                                                                                 | . 219 |

| 14.7  | <b>7</b> .6 | Returning from an Interrupt Routine                                                                              | . 220 |

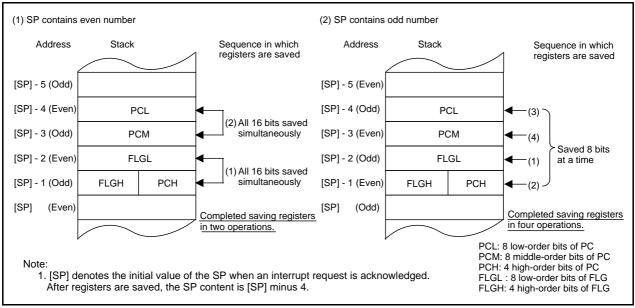

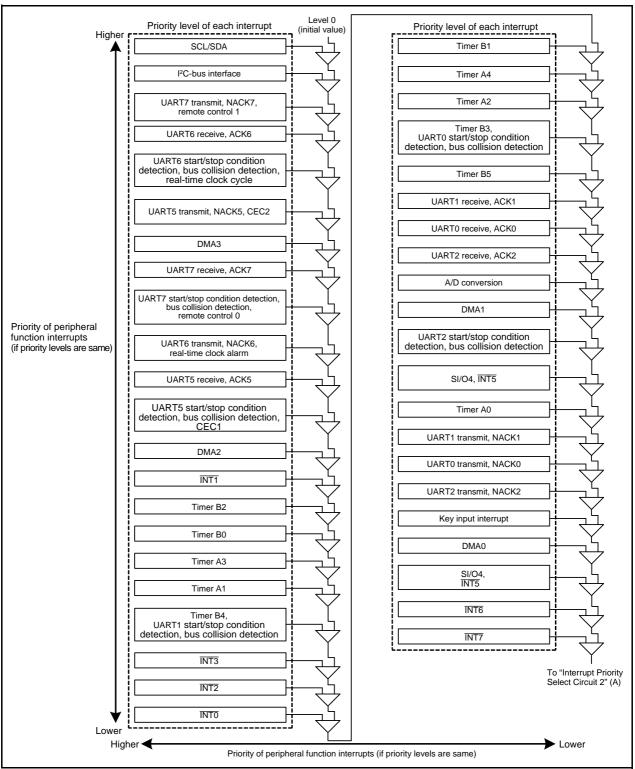

| 14.7  | 7.7         | Interrupt Priority                                                                                               | . 220 |

| 14.7  | 7.8         | Interrupt Priority Level Select Circuit                                                                          | . 220 |

| 14.7  | 7.9         | Multiple Interrupts                                                                                              | . 222 |

| 14.8  | INT         | Interrupt                                                                                                        | . 222 |

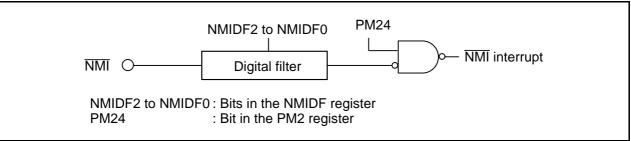

| 14.9  | NM          | Ī Interrupt                                                                                                      | . 223 |

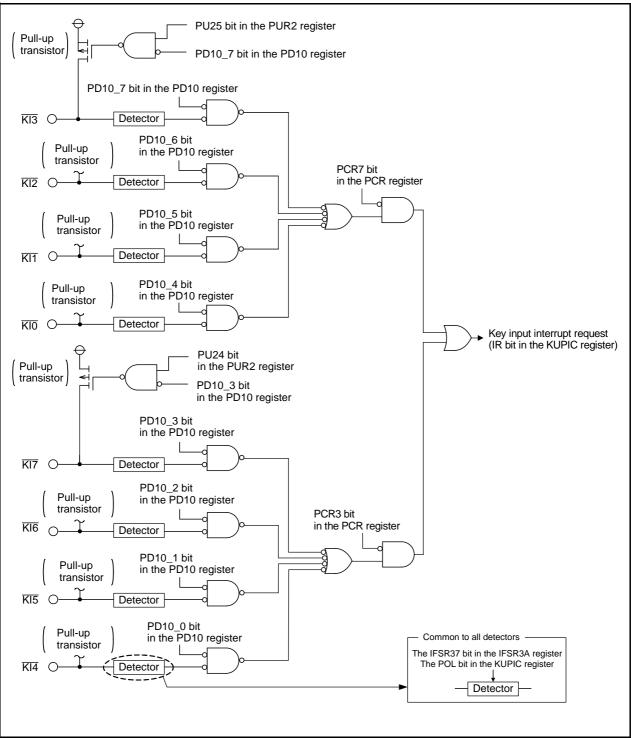

| 14.10 | Key         | nput Interrupt                                                                                                   | . 223 |

| 14.11 Ado  | dress Match Interrupt                                 | 225 |

|------------|-------------------------------------------------------|-----|

| 14.12 No   | n-Maskable Interrupt Source Discrimination            | 226 |

| 14.13 Not  | tes on Interrupts                                     | 227 |

| 14.13.1    | Reading Address 00000h                                | 227 |

| 14.13.2    | SP Setting                                            | 227 |

| 14.13.3    | NMI Interrupt                                         | 227 |

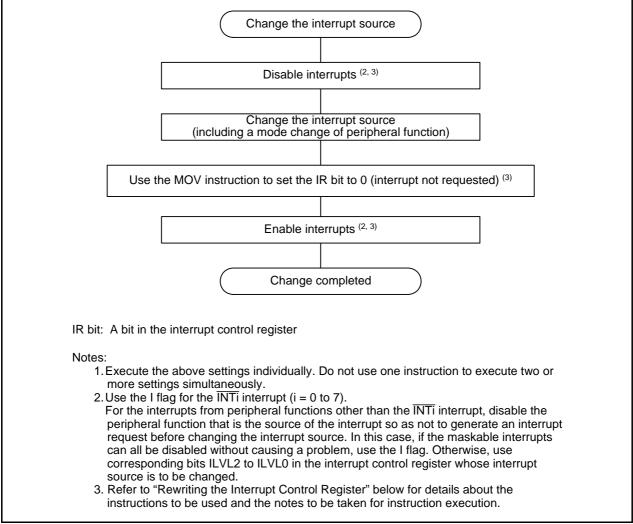

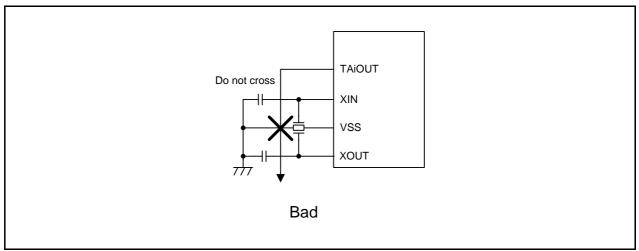

| 14.13.4    | Changing an Interrupt Source                          | 228 |

| 14.13.5    | Rewriting the Interrupt Control Register              | 229 |

| 14.13.6    | Instruction to Rewrite the Interrupt Control Register | 229 |

| 14.13.7    | INT Interrupt                                         |     |

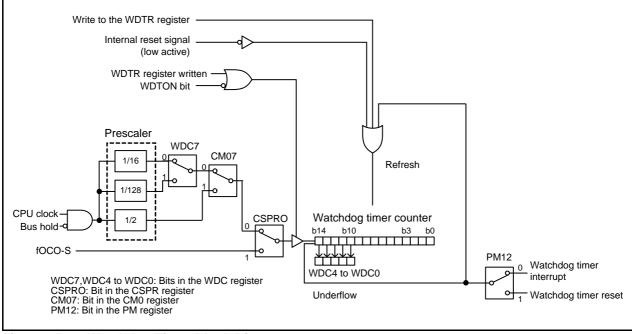

| 15. Watchd | log Timer                                             |     |

| 15.1 Intr  | oduction                                              |     |

| 15.2 Re    | gisters                                               |     |

| 15.2.1     | Voltage Monitor 2 Control Register (VW2C)             |     |

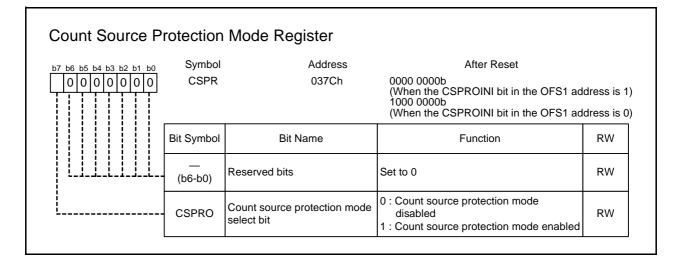

| 15.2.2     | Count Source Protection Mode Register (CSPR)          | 233 |

| 15.2.3     | Watchdog Timer Refresh Register (WDTR)                | 234 |

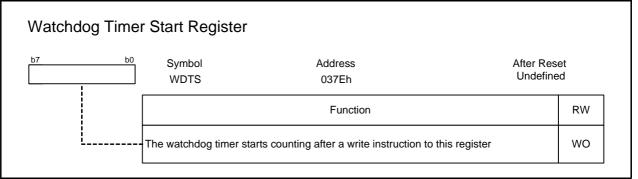

| 15.2.4     | Watchdog Timer Start Register (WDTS)                  | 234 |

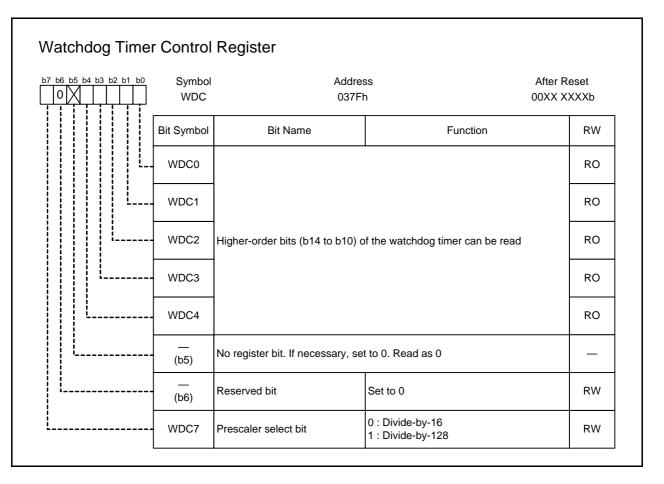

| 15.2.5     | Watchdog Timer Control Register (WDC)                 | 235 |

| 15.3 Op    | tional Function Select Area                           |     |

| 15.3.1     | Optional Function Select Address 1 (OFS1)             |     |

| 15.4 Op    | erations                                              |     |

| 15.4.1     | Count Source Protection Mode Disabled                 | 237 |

| 15.4.2     | Count Source Protection Mode Enabled                  |     |

| 15.5 Inte  | errupts                                               | 239 |

| 15.6 Not   | tes on Watchdog Timer                                 |     |

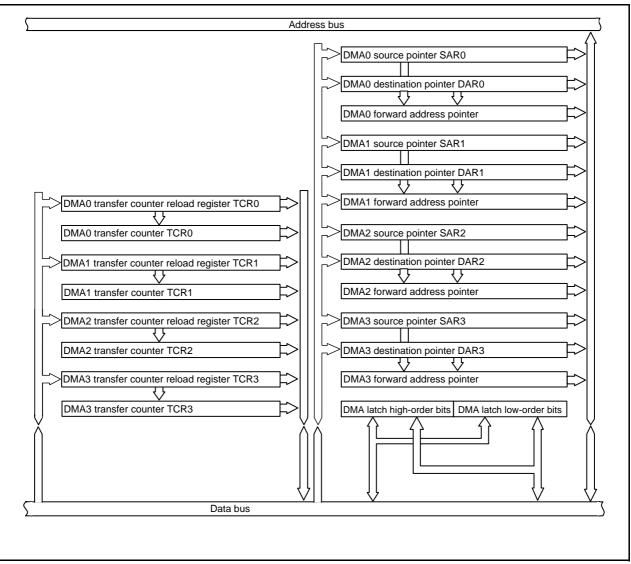

| 16. DMAC.  |                                                       |     |

| 16.1 Intr  | oduction                                              | 241 |

| 16.2 Re    | gisters                                               |     |

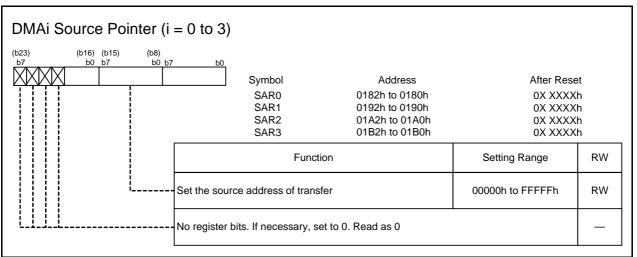

| 16.2.1     | DMAi Source Pointer (SARi) (i = 0 to 3)               |     |

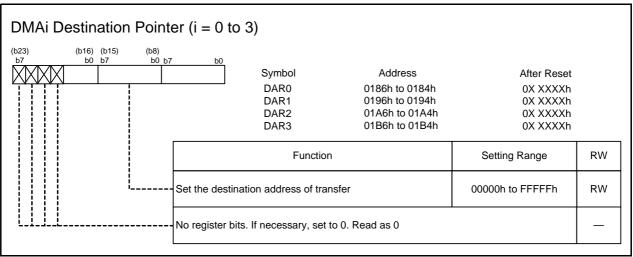

| 16.2.2     | DMAi Destination Pointer (DARi) (i = 0 to 3)          |     |

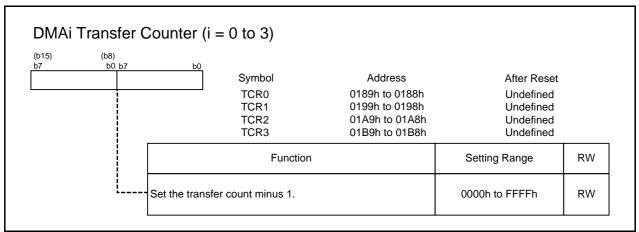

| 16.2.3     | DMAi Transfer Counter (TCRi) (i = 0 to 3)             | 245 |

| 16.2.4     | DMAi Control Register (DMiCON) (i = 0 to 3)           | 246 |

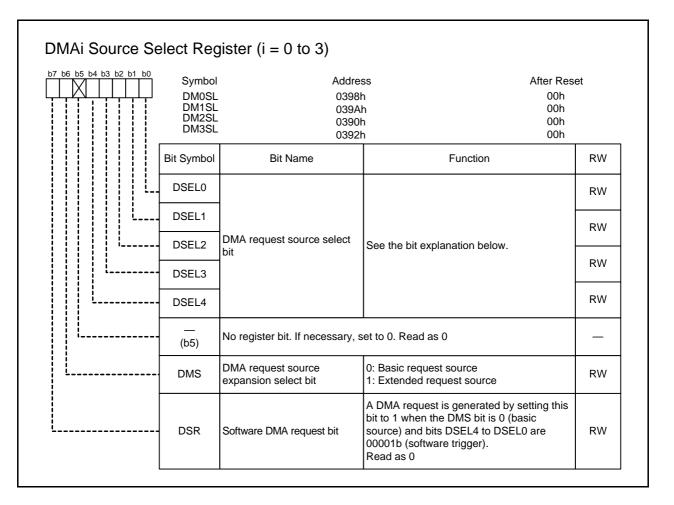

| 16.2.5     | DMAi Source Select Register (DMiSL) (i = 0 to 3)      | 247 |

| 16.3 Op    | erations                                              | 250 |

| 16.3.1     | DMA Enabled                                                           |

|------------|-----------------------------------------------------------------------|

| 16.3.2     | DMA Request                                                           |

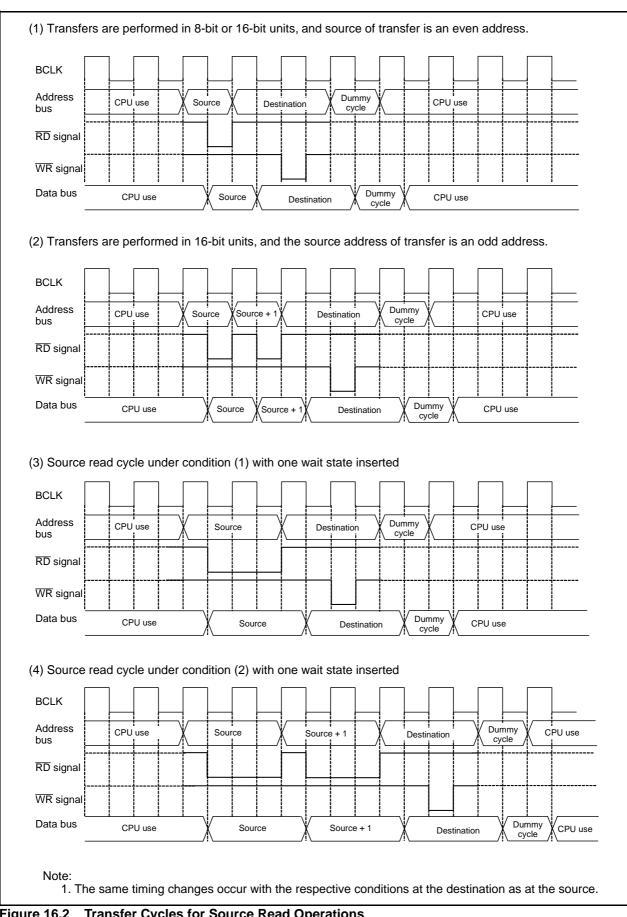

| 16.3.3     | Transfer Cycles                                                       |

| 16.3.4     | DMAC Transfer Cycles                                                  |

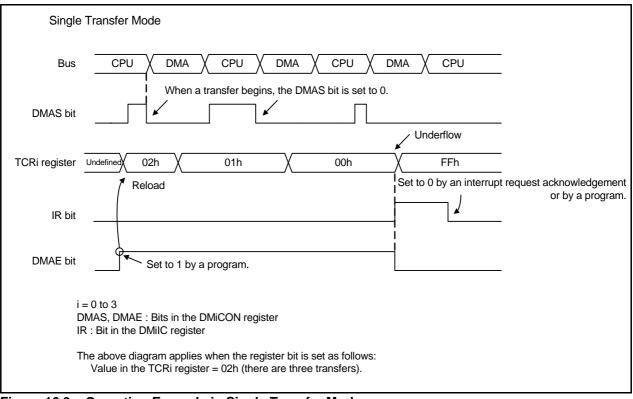

| 16.3.5     | Single Transfer Mode254                                               |

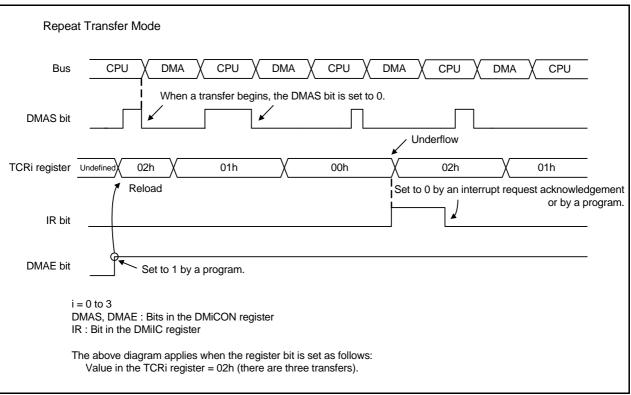

| 16.3.6     | Repeat Transfer Mode                                                  |

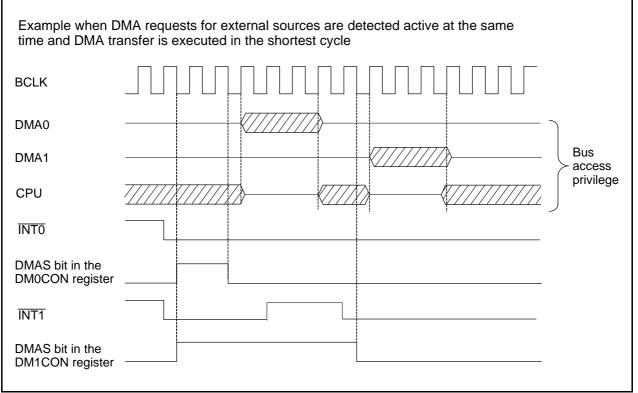

| 16.3.7     | Channel Priority and DMA Transfer Timing256                           |

| 16.4 Inte  | errupts                                                               |

| 16.5 Not   | es on DMAC                                                            |

| 16.5.1     | Write to the DMAE Bit in the DMiCON Register (i = 0 to 3)258          |

| 16.5.2     | Changing the DMA Request Source                                       |

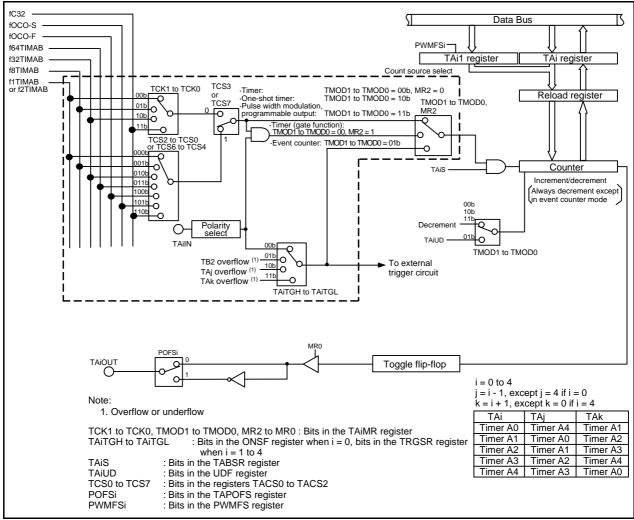

| 17 Timer A |                                                                       |

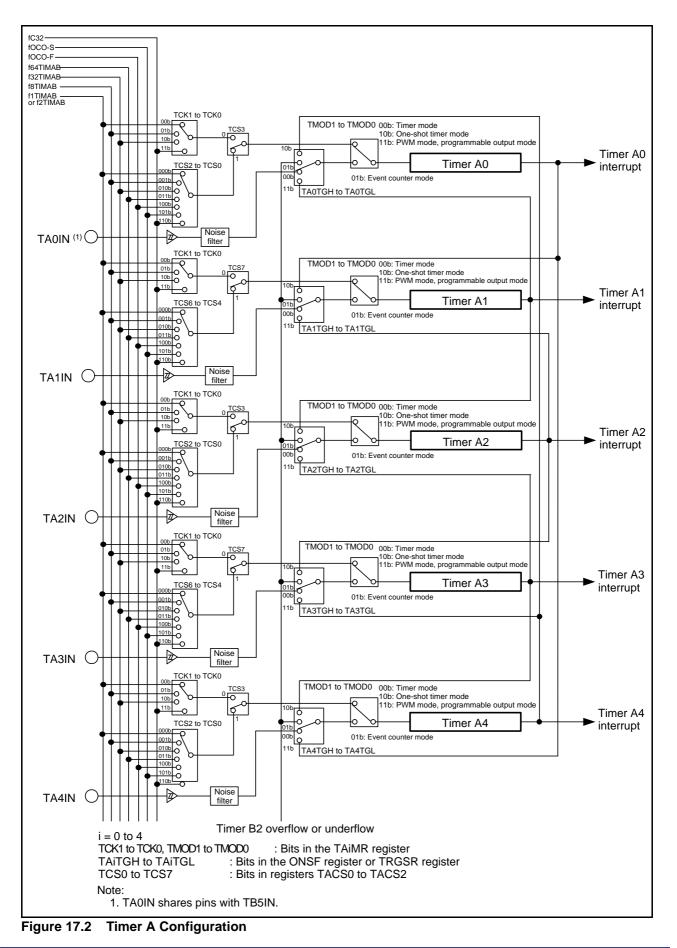

|            | oduction                                                              |

|            | 259<br>gisters                                                        |

| 17.2 17.2  | Peripheral Clock Select Register (PCLKR)                              |

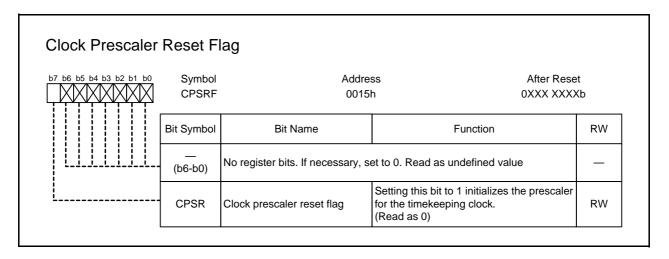

| 17.2.1     | Clock Prescaler Reset Flag (CPSRF)                                    |

| 17.2.2     | Peripheral Clock Stop Register (PCLKSTP1)                             |

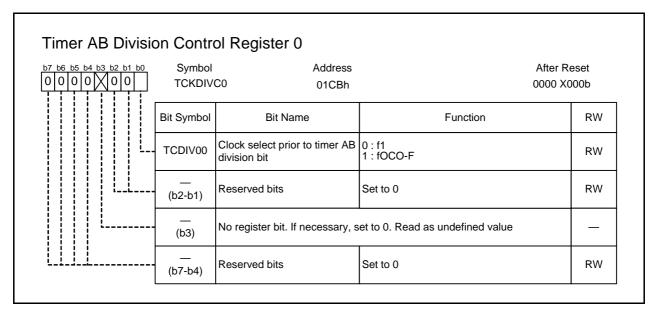

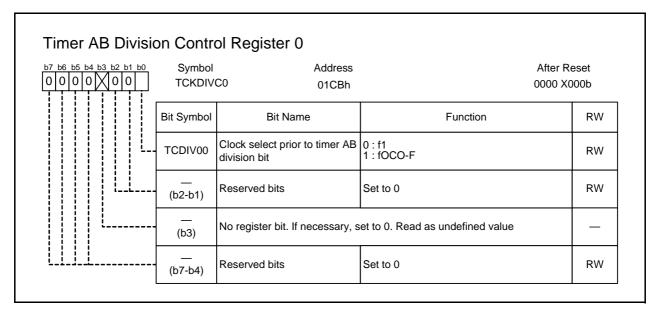

| 17.2.3     | Timer AB Division Control Register 0 (TCKDIVC0)                       |

| 17.2.4     | Timer A Count Source Select Register i (TACSi) (i = 0 to 2)           |

| 17.2.6     | 16-Bit Pulse Width Modulation Mode Function Select Register           |

| 17.2.0     | (PWMFS)                                                               |

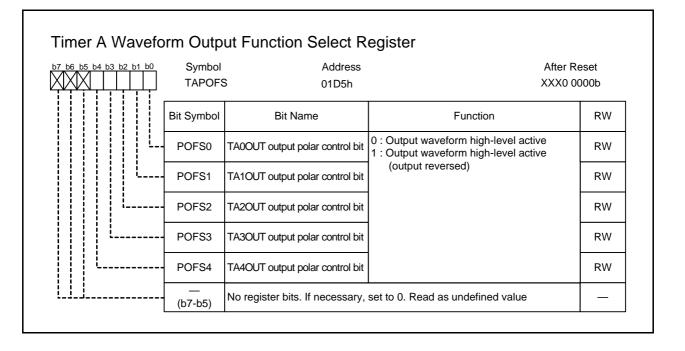

| 17.2.7     | Timer A Waveform Output Function Select Register (TAPOFS)             |

| 17.2.8     | Timer A Output Waveform Change Enable Register (TAOW)                 |

| 17.2.9     | Timer Ai Register (TAi) (i = 0 to 4)                                  |

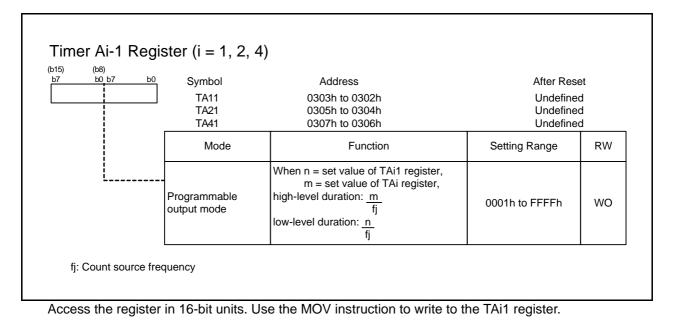

| 17.2.10    | Timer Ai-1 Register (TAi1) (i = 1, 2, 4)                              |

| 17.2.11    | Count Start Flag (TABSR)                                              |

| 17.2.12    | One-Shot Start Flag (ONSF)                                            |

| 17.2.13    | Trigger Select Register (TRGSR)275                                    |

| 17.2.14    | Up/Down Flag (UDF)                                                    |

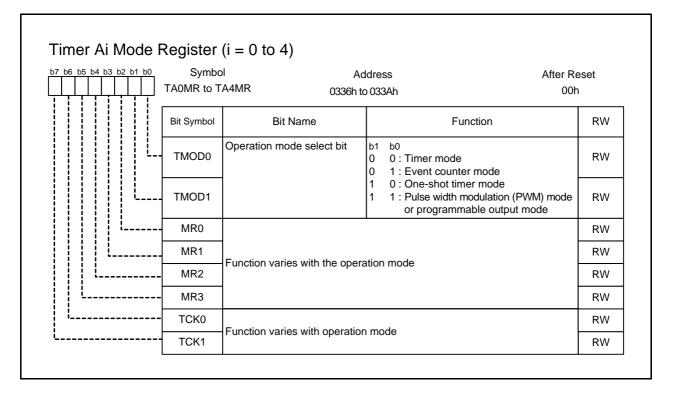

| 17.2.15    | Timer Ai Mode Register (TAiMR) (i = 0 to 4)                           |

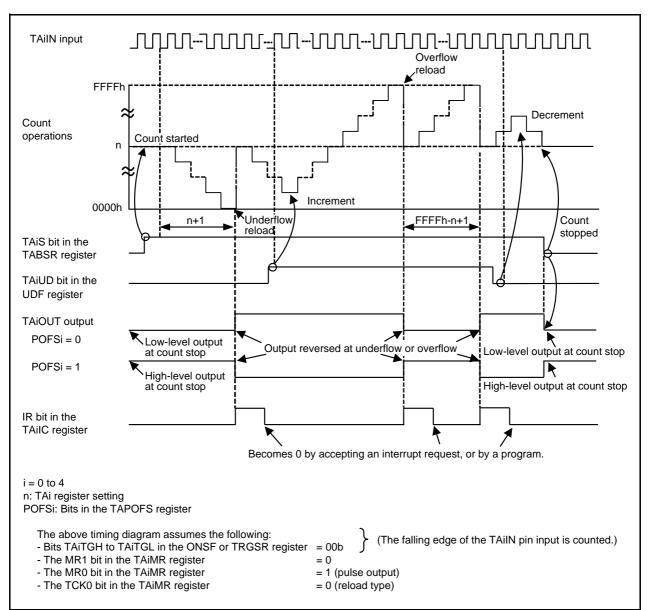

| 17.3 Op    | erations278                                                           |

| 17.3.1     | Common Operations                                                     |

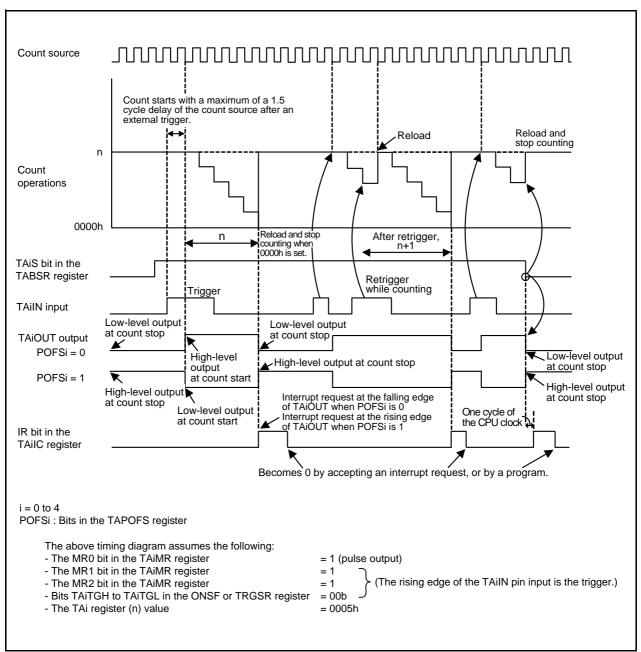

| 17.3.2     | Timer Mode                                                            |

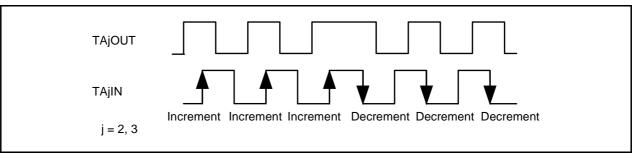

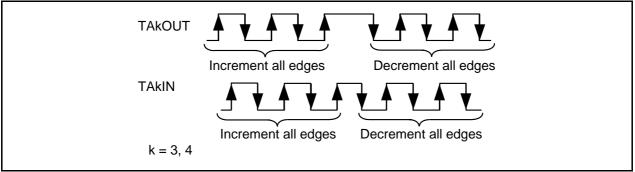

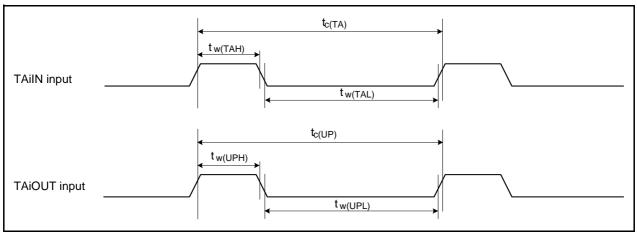

| 17.3.3     | Event Counter Mode (When Not Processing Two-Phase Pulse Signal) . 284 |

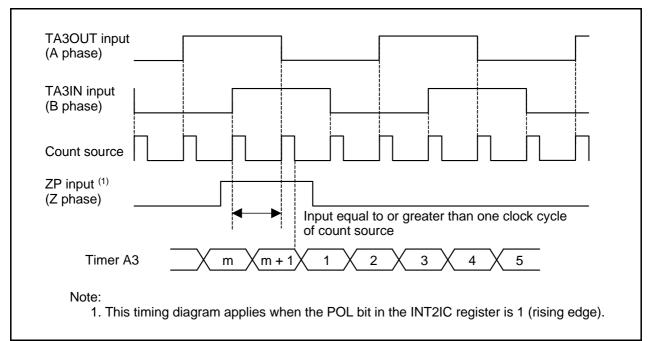

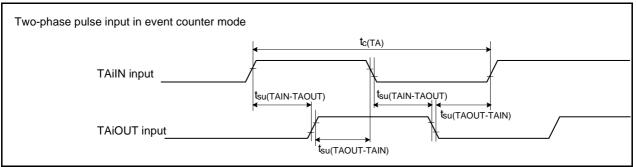

| 17.3.4     | Event Counter Mode (When Processing Two-Phase Pulse Signal) 288       |

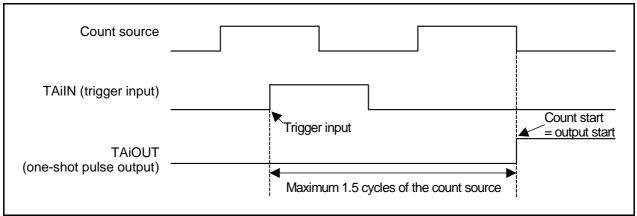

|    | 17.3 | 3.5   | One-Shot Timer Mode                                                                       | . 293 |

|----|------|-------|-------------------------------------------------------------------------------------------|-------|

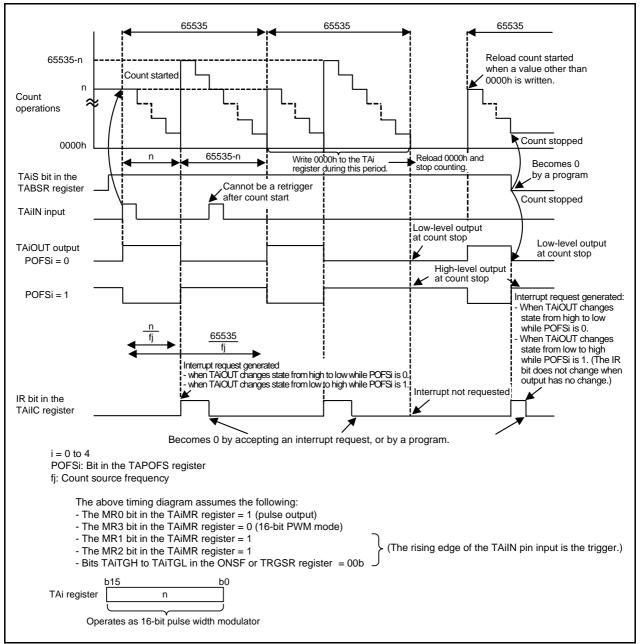

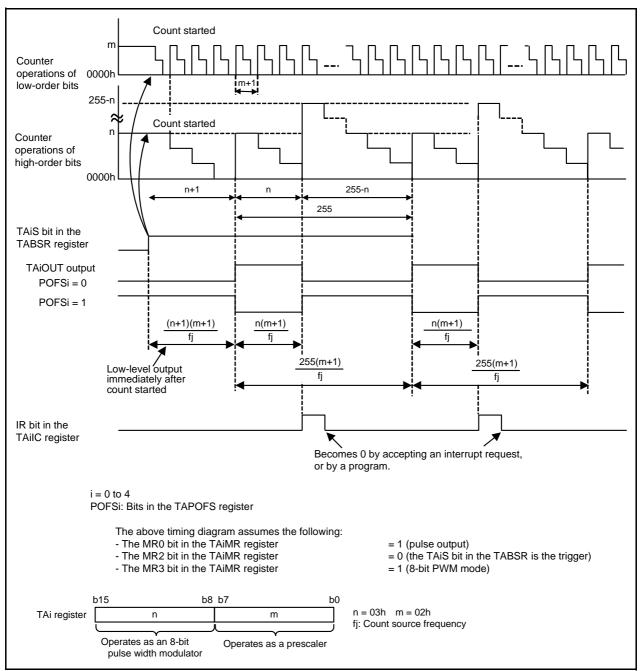

|    | 17.3 | 3.6   | Pulse Width Modulation (PWM) Mode                                                         | . 297 |

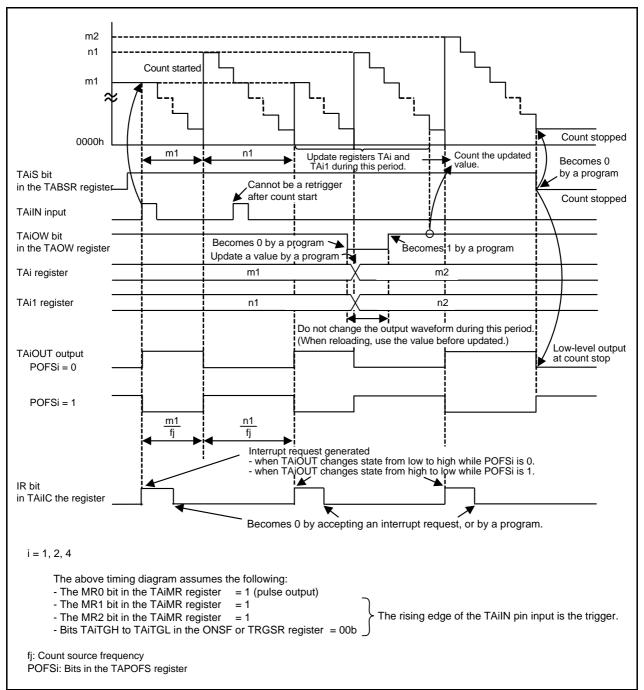

|    | 17.3 | 3.7   | Programmable Output Mode (Timers A1, A2, and A4)                                          | . 302 |

| 17 | .4   | Inte  | rrupts                                                                                    | . 306 |

| 17 | .5   | Not   | es on Timer A                                                                             | . 307 |

|    | 17.5 | 5.1   | Common Notes on Multiple Modes                                                            | . 307 |

|    | 17.5 | 5.2   | Timer A (Timer Mode)                                                                      | . 307 |

|    | 17.5 | 5.3   | Timer A (Event Counter Mode)                                                              | . 307 |

|    | 17.5 | 5.4   | Timer A (One-Shot Timer Mode)                                                             | . 308 |

|    | 17.5 | 5.5   | Timer A (Pulse Width Modulation Mode)                                                     | . 309 |

|    | 17.5 | 5.6   | Timer A (Programmable Output Mode)                                                        | . 310 |

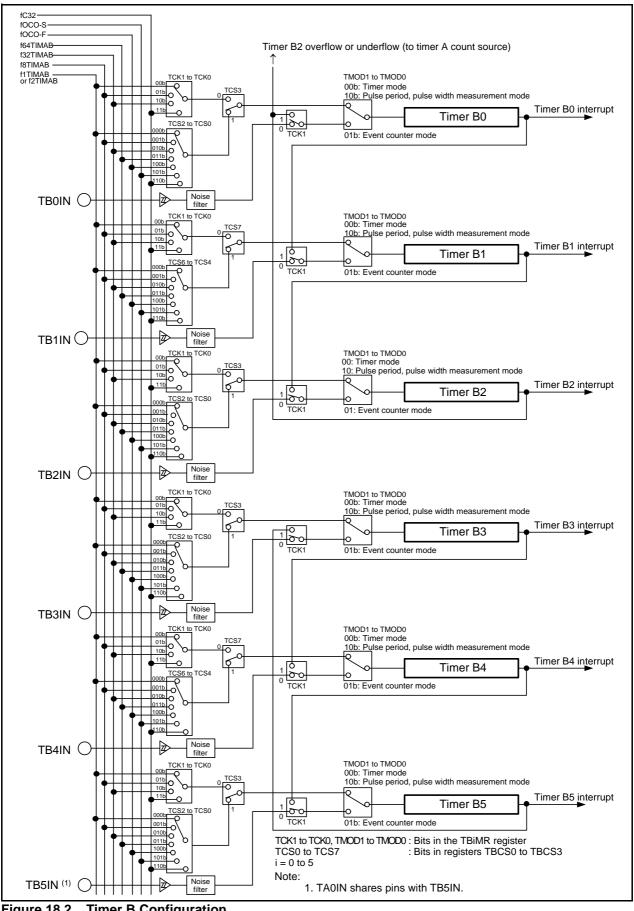

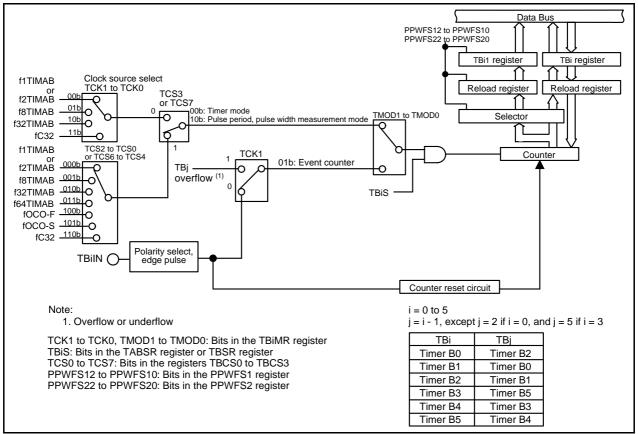

| 18 | Tim  | er B  |                                                                                           | 311   |

| 18 | .1   | Intro | oduction                                                                                  | . 311 |

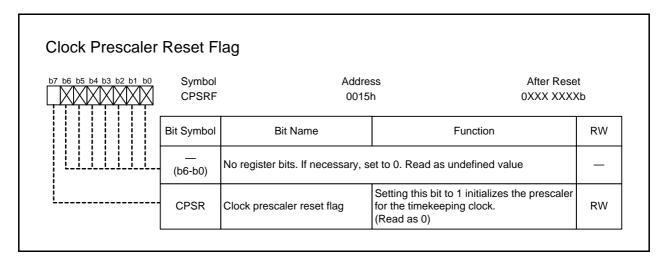

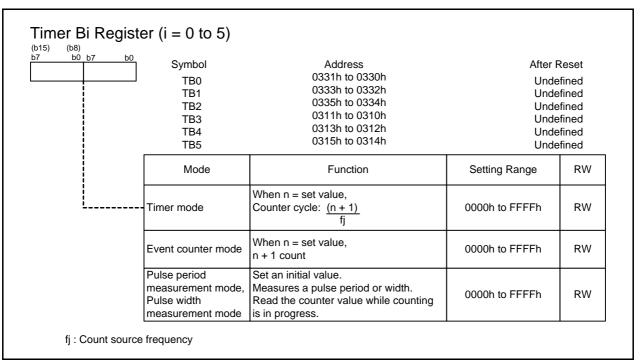

| 18 | .2   | Reg   | gisters                                                                                   | . 314 |

|    | 18.2 | 2.1   | Peripheral Clock Select Register (PCLKR)                                                  | . 315 |

|    | 18.2 | 2.2   | Clock Prescaler Reset Flag (CPSRF)                                                        | . 315 |

|    | 18.2 | 2.3   | Peripheral Clock Stop Register (PCLKSTP1)                                                 | . 316 |

|    | 18.2 | 2.4   | Timer Bi Register (TBi) (i = 0 to 5)                                                      | . 317 |

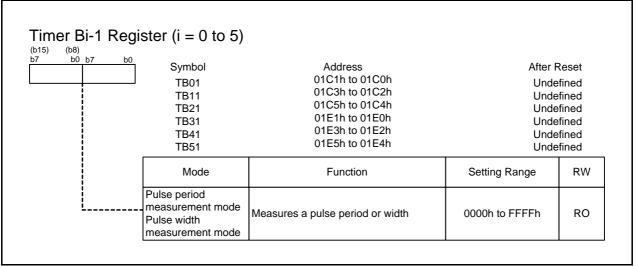

|    | 18.2 | 2.5   | Timer Bi-1 Register (TBi1) (i = 0 to 5)                                                   | . 318 |

|    | 18.2 | 2.6   | Pulse Period/Pulse Width Measurement Mode Function Select Register<br>(PPWFSi) (i = 1, 2) |       |

|    | 18.2 | 2.7   | Timer B Count Source Select Register i (TBCSi) (i = 0 to 3)                               | . 320 |

|    | 18.2 | 2.8   | Timer AB Division Control Register 0 (TCKDIVC0)                                           | . 321 |

|    | 18.2 | 2.9   | Count Start Flag (TABSR)<br>Timer B3/B4/B5 Count Start Flag (TBSR)                        | . 322 |

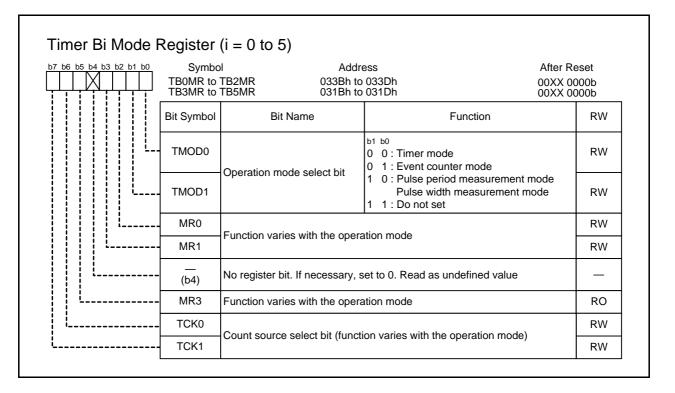

|    | 18.2 | 2.10  | Timer Bi Mode Register (TBiMR) (i = 0 to 5)                                               | . 323 |

| 18 | .3   | Оре   | erations                                                                                  | . 324 |

|    | 18.3 | 3.1   | Common Operations                                                                         | . 324 |

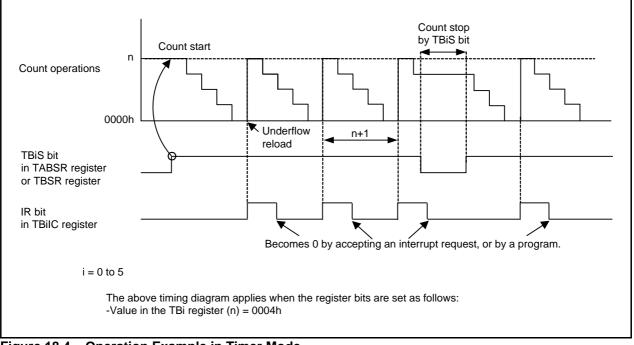

|    | 18.3 | 3.2   | Timer Mode                                                                                | . 326 |

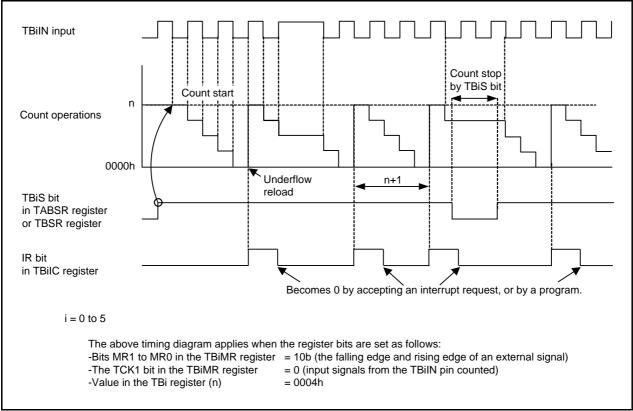

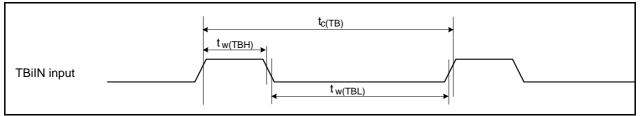

|    | 18.3 | 3.3   | Event Counter Mode                                                                        | . 328 |

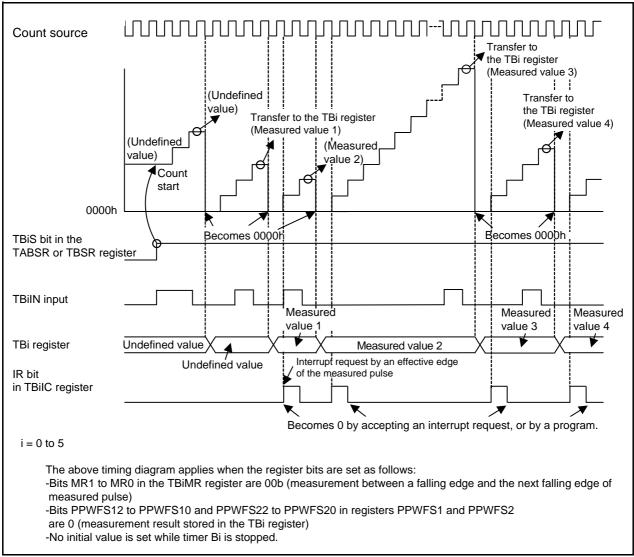

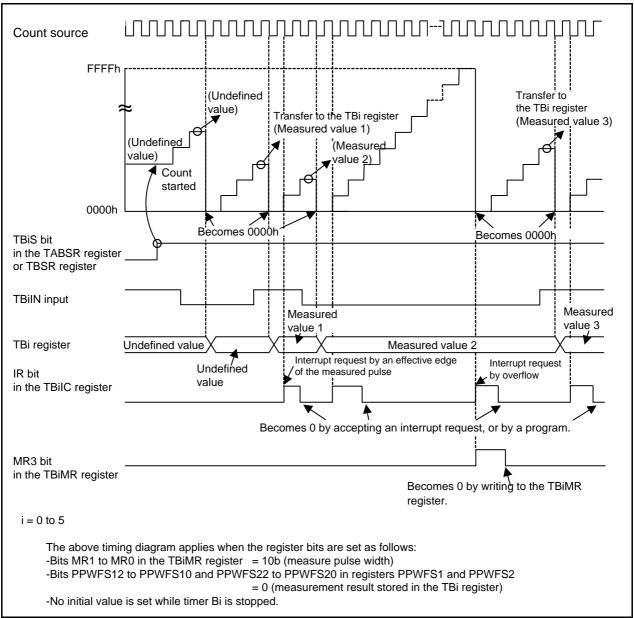

|    | 18.3 | 3.4   | Pulse Period/Pulse Width Measurement Modes                                                | . 331 |

| 18 | .4   | Inte  | rrupts                                                                                    | . 336 |

| 18 | .5   | Not   | es on Timer B                                                                             | . 337 |

|    | 18.5 | 5.1   | Common Notes on Multiple Modes                                                            | . 337 |

|    | 18.5 | 5.2   | Timer B (Timer Mode)                                                                      | . 337 |

|     | 18.5 | 5.3    | Timer B (Event Counter Mode)                                |     |

|-----|------|--------|-------------------------------------------------------------|-----|

|     | 18.5 | 5.4    | Timer B (Pulse Period/Pulse Width Measurement Modes)        |     |

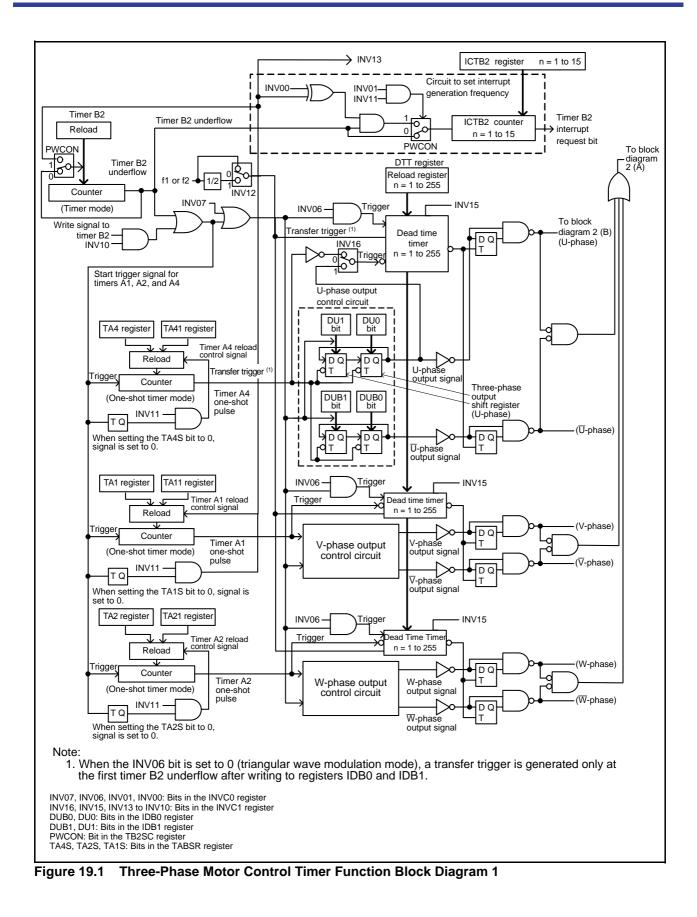

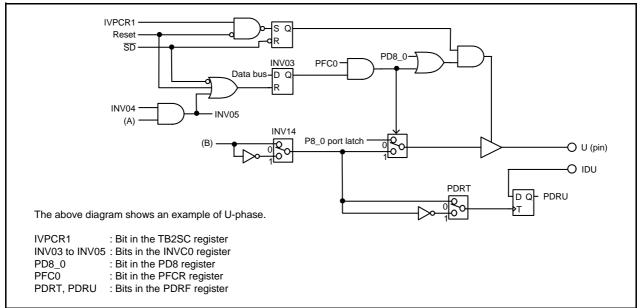

| 19. | Thr  | ee-F   | Phase Motor Control Timer Function                          | 339 |

| 1   | 9.1  | Intr   | oduction                                                    | 339 |

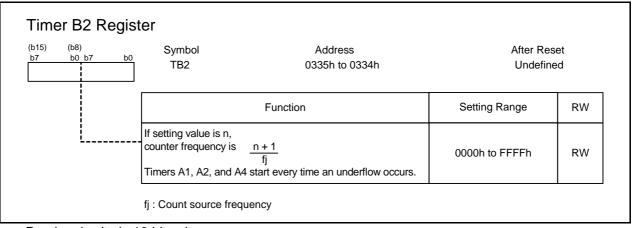

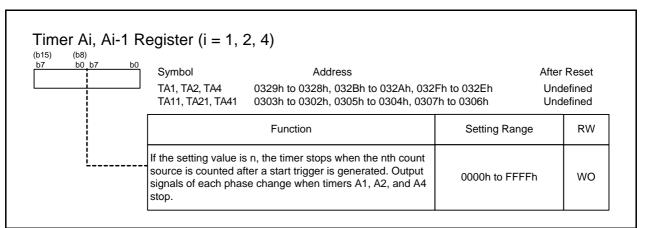

| 1   | 9.2  | Reg    | gisters                                                     |     |

|     | 19.2 | 2.1    | Timer B2 Register (TB2)                                     |     |

|     | 19.2 | 2.2    | Timer Ai, Ai-1 Register (TAi, TAi1) (i = 1, 2, 4)           |     |

|     | 19.2 | 2.3    | Three-Phase PWM Control Register 0 (INVC0)                  |     |

|     | 19.2 | 2.4    | Three-Phase PWM Control Register 1 (INVC1)                  |     |

|     | 19.2 | 2.5    | Three-Phase Output Buffer Register i (IDBi) (i = 0, 1)      |     |

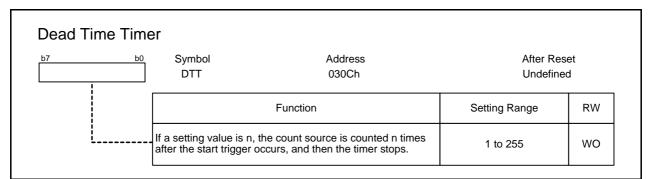

|     | 19.2 | 2.6    | Dead Time Timer (DTT)                                       |     |

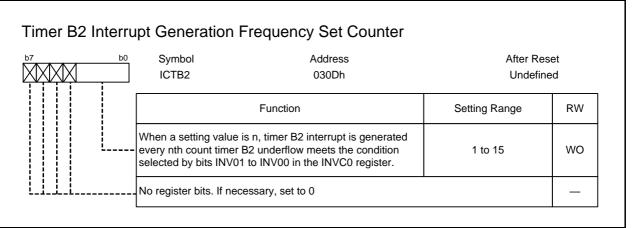

|     | 19.2 | 2.7    | Timer B2 Interrupt Generation Frequency Set Counter (ICTB2) | 350 |

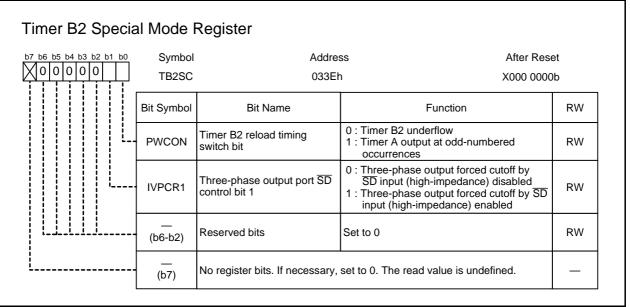

|     | 19.2 | 2.8    | Timer B2 Special Mode Register (TB2SC)                      |     |

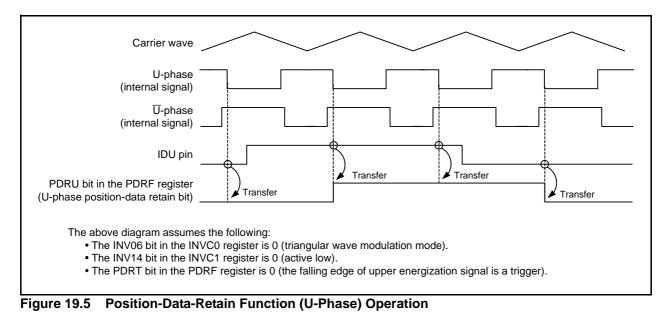

|     | 19.2 | 2.9    | Position-Data-Retain Function Control Register (PDRF)       |     |

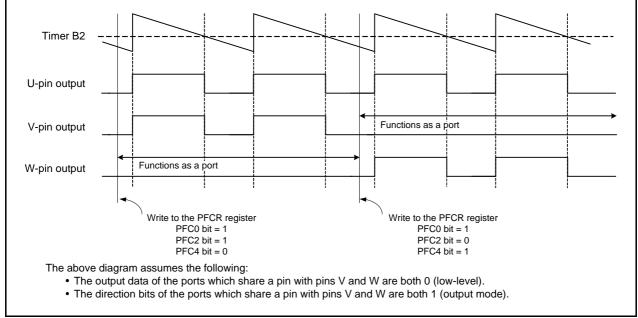

|     | 19.2 | 2.10   | Port Function Control Register (PFCR)                       |     |

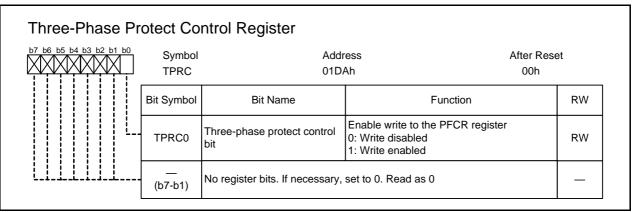

|     | 19.2 | 2.11   | Three-Phase Protect Control Register (TPRC)                 |     |

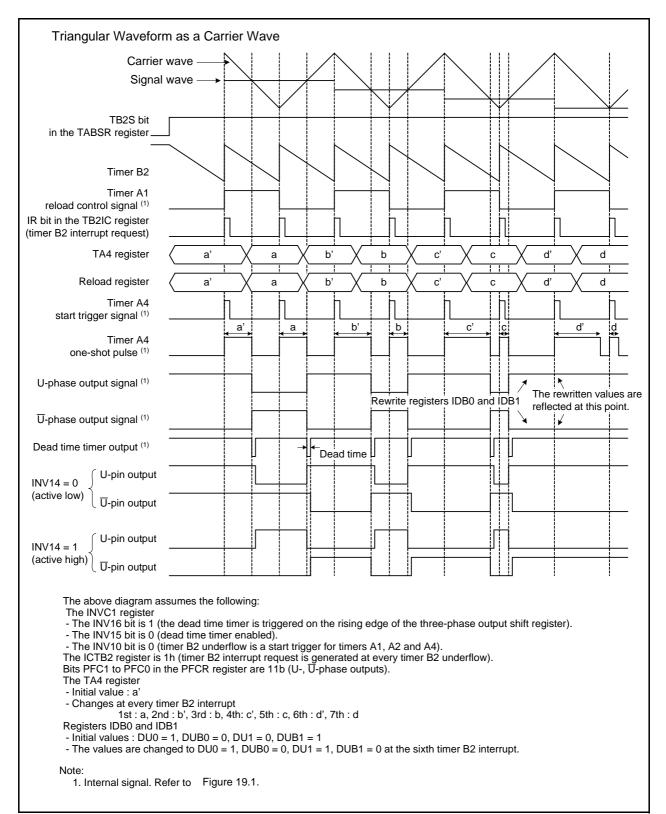

| 1   | 9.3  | Ope    | erations                                                    |     |

|     | 19.3 | 3.1    | Common Operations in Multiple Modes                         |     |

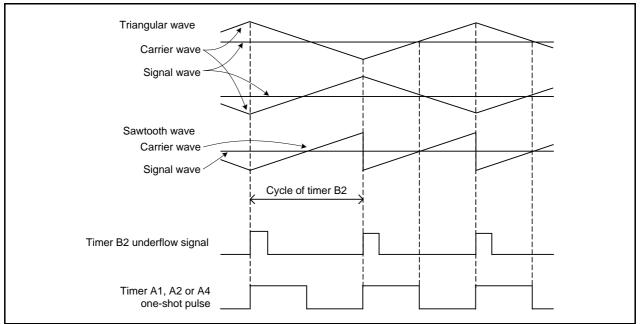

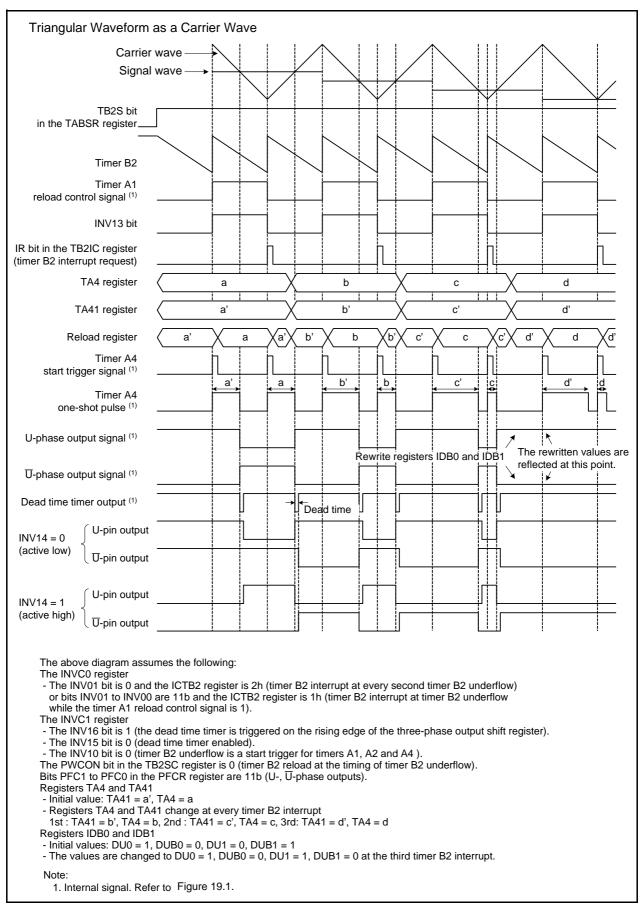

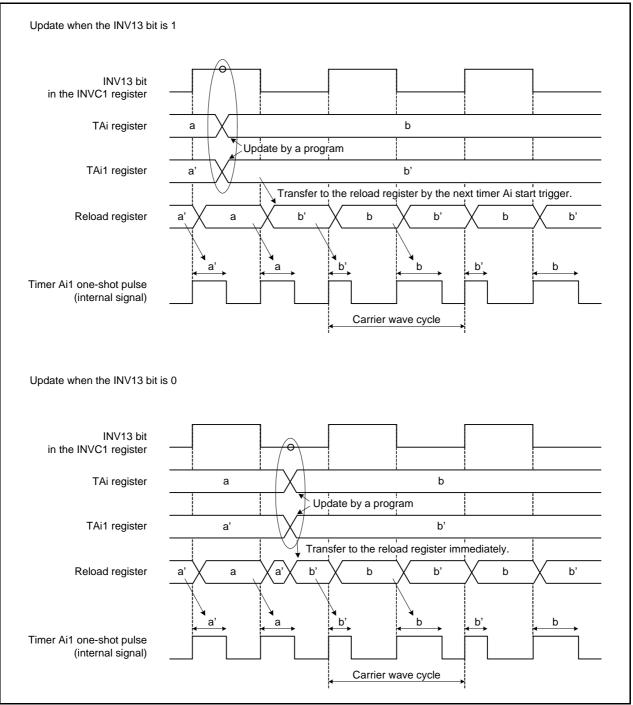

|     | 19.3 | 3.2    | Triangular Wave Modulation Three-Phase Mode 0               |     |

|     | 19.3 | 3.3    | Triangular Wave Modulation Three-Phase Mode 1               |     |

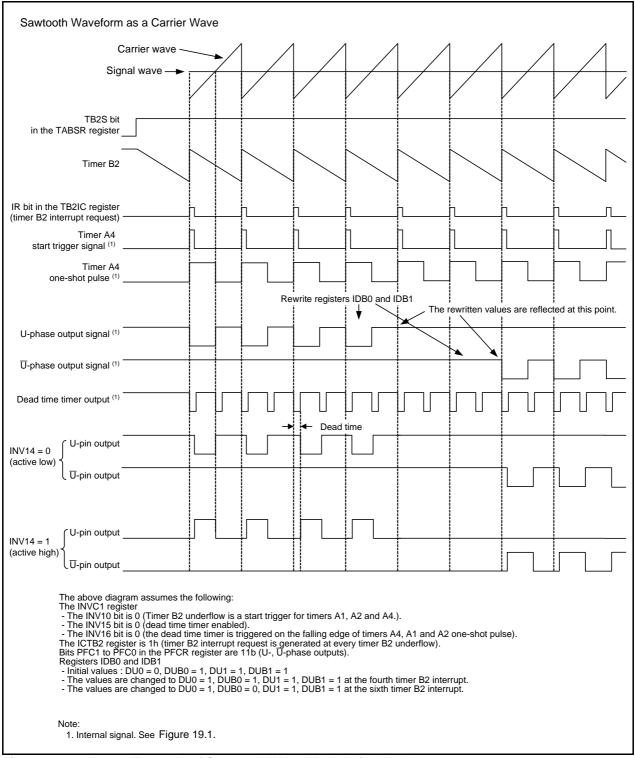

|     | 19.3 | 3.4    | Sawtooth Wave Modulation Mode                               |     |

| 1   | 9.4  | Inte   | errupts                                                     |     |

|     | 19.4 | 4.1    | Timer B2 Interrupt                                          |     |

|     | 19.4 | 4.2    | Timers A1, A2, and A4 Interrupts                            |     |

| 1   | 9.5  | Not    | es on Three-Phase Motor Control Timer Function              |     |

|     | 19.5 | 5.1    | Timer A and Timer B                                         |     |

|     | 19.5 | 5.2    | Forced Cutoff Input                                         |     |

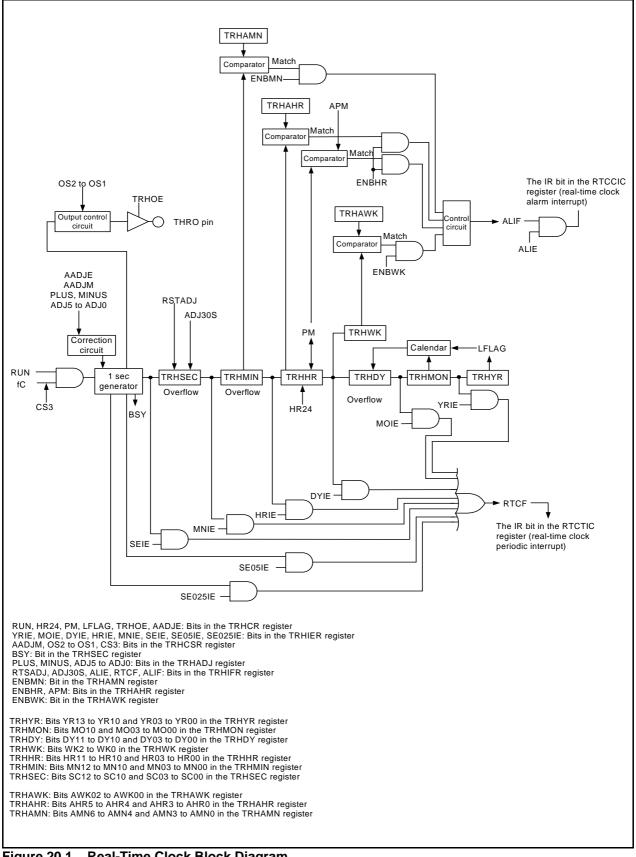

| 20. | Rea  | al-Tii | me Clock                                                    | 379 |

| 2   | 0.1  | Intr   | oduction                                                    |     |

| 2   | 0.2  | Reg    | gisters                                                     |     |

|     | 20.2 | 2.1    | Peripheral Clock Stop Register (PCLKSTP1)                   |     |

|     | 20.2 | 2.2    | Second Data Register (TRHSEC)                               |     |

|     | 20.2 | 2.3    | Minute Data Register (TRHMIN)                               |     |

|     | 20.2 | 2.4    | Hour Data Register (TRHHR)                                  |     |

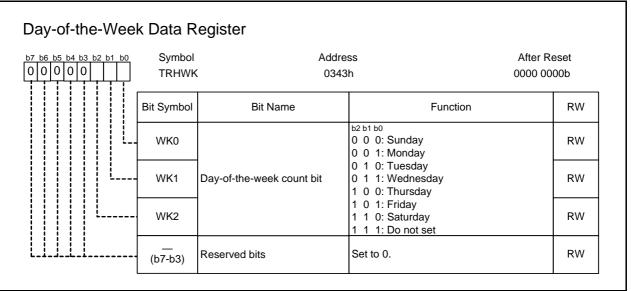

| 20.2.5    | Day-of-the-Week Data Register (TRHWK)          |     |

|-----------|------------------------------------------------|-----|

| 20.2.6    | Date Data Register (TRHDY)                     |     |

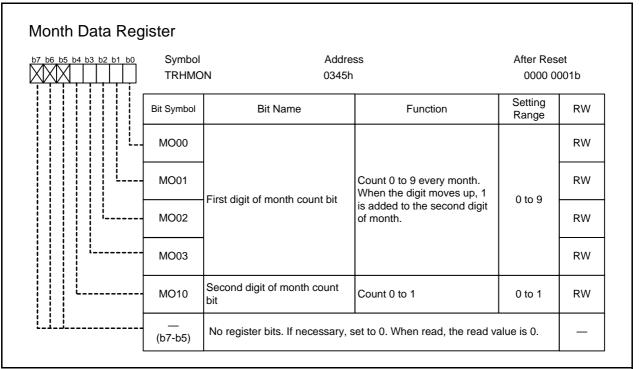

| 20.2.7    | Month Data Register (TRHMON)                   |     |

| 20.2.8    | Year Data Register (TRHYR)                     |     |

| 20.2.9    | Timer RH Control Register (TRHCR)              |     |

| 20.2.10   | Timer RH Count Source Select Register (TRHCSR) |     |

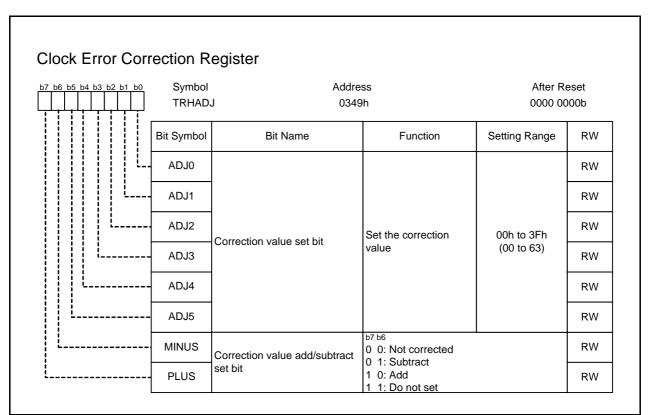

| 20.2.11   | Clock Error Correction Register (TRHADJ)       |     |

| 20.2.12   | 2 Timer RH Interrupt Flag Register (TRHIFR)    |     |

| 20.2.13   | 3 Timer RH Interrupt Enable Register (TRHIER)  |     |

| 20.2.14   | Alarm Minute Register (TRHAMN)                 |     |

| 20.2.15   | 6 Alarm Hour Register (TRHAHR)                 |     |

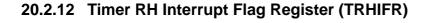

| 20.2.16   | Alarm Day-of-the-Week Register (TRHAWK)        |     |

| 20.2.17   | Timer RH Protect Register (TRHPRC)             |     |

| 20.3 Op   | perations                                      |     |

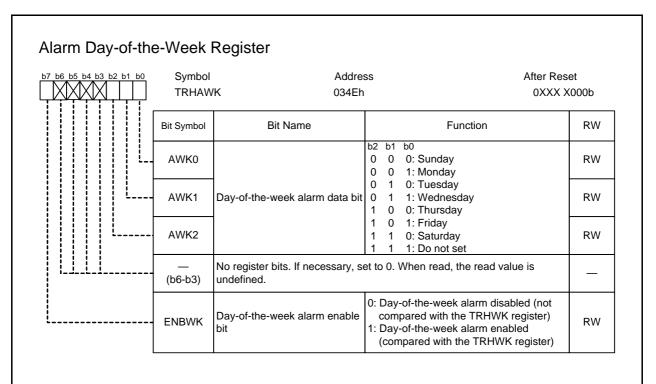

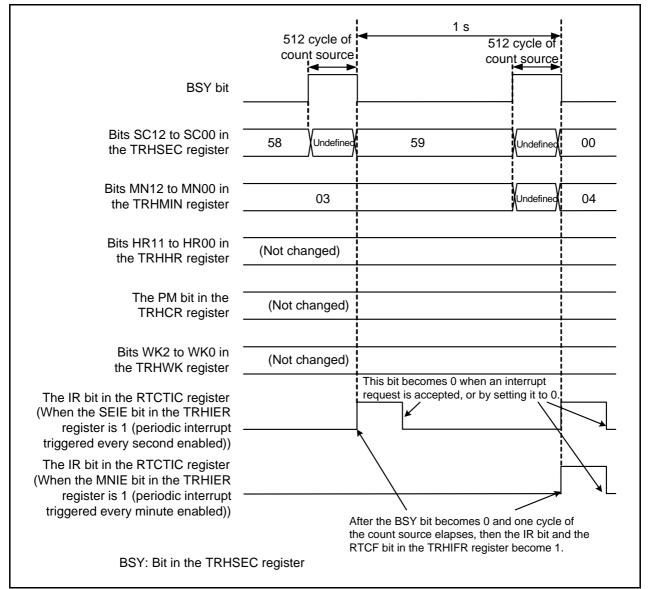

| 20.3.1    | Basic Operation                                |     |

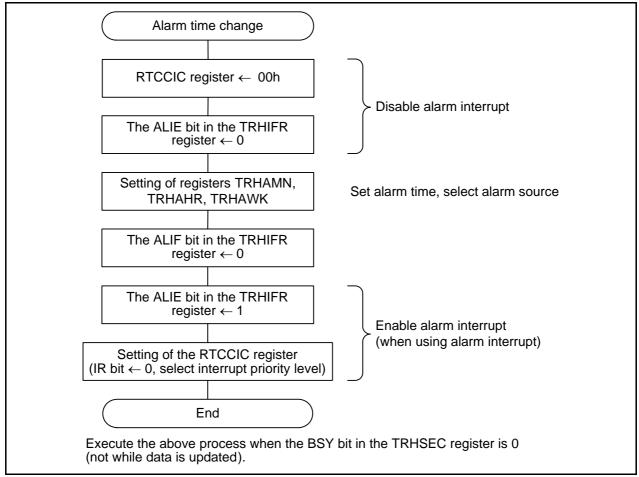

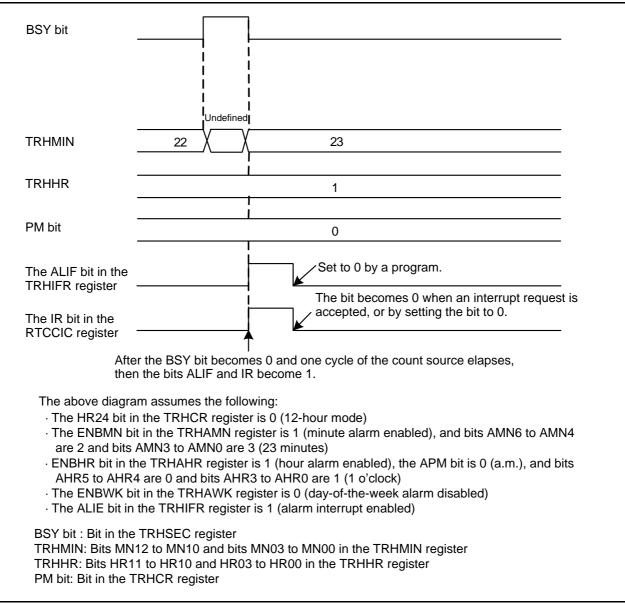

| 20.3.2    | Alarm Function                                 |     |

| 20.3.3    | Second Adjustment Function                     |     |

| 20.3.4    | Clock Error Correction Function                | 405 |

| 20.3.5    | Clock Output                                   |     |

| 20.4 Int  | errupts                                        |     |

| 20.5 No   | otes on Real-Time Clock                        |     |

| 20.5.1    | Register Setting (Time Data, etc.)             |     |

| 20.5.2    | Register Setting (Alarm Data)                  |     |

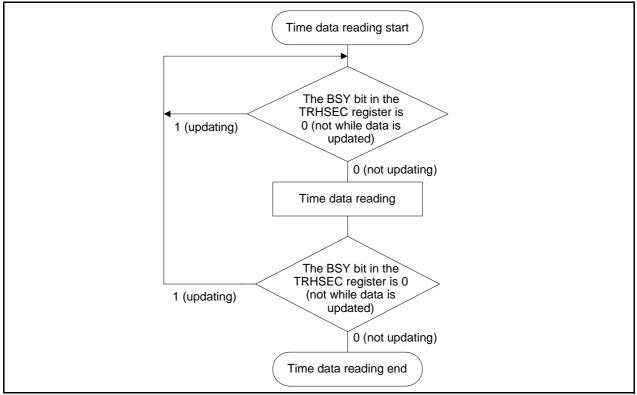

| 20.5.3    | Time Reading Procedure of Real-Time Clock Mode |     |

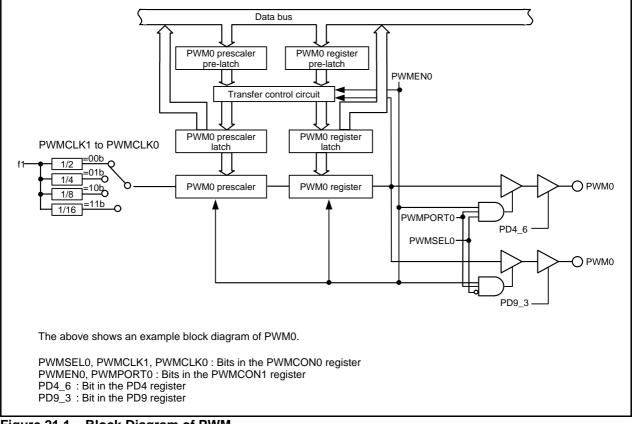

| 21. Pulse | Width Modulator                                | 410 |

| 21.1 Int  | roduction                                      |     |

| 21.2 Re   | egisters                                       | 411 |

| 21.2.1    | Peripheral Clock Stop Register (PCLKSTP1)      |     |

| 21.2.2    | PWM Control Register 0 (PWMCON0)               |     |

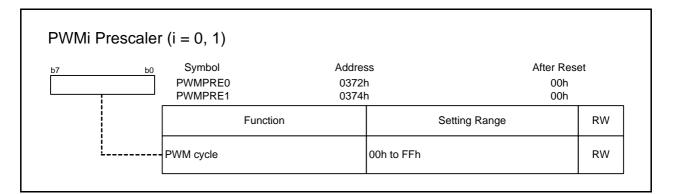

| 21.2.3    | PWMi Prescaler (PWMPREi) (i = 0, 1)            |     |

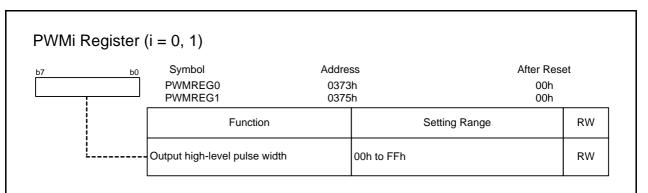

| 21.2.4    | PWMi Register (PWMREGi) (i = 0, 1)             |     |

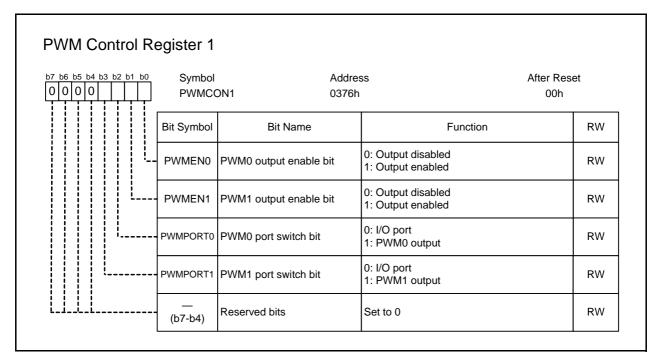

| 21.2.5    | PWM Control Register 1 (PWMCON1)               |     |

| 21.3 Op   | perations                                      |     |

| 21.3.1    | Setting Procedure                              |     |

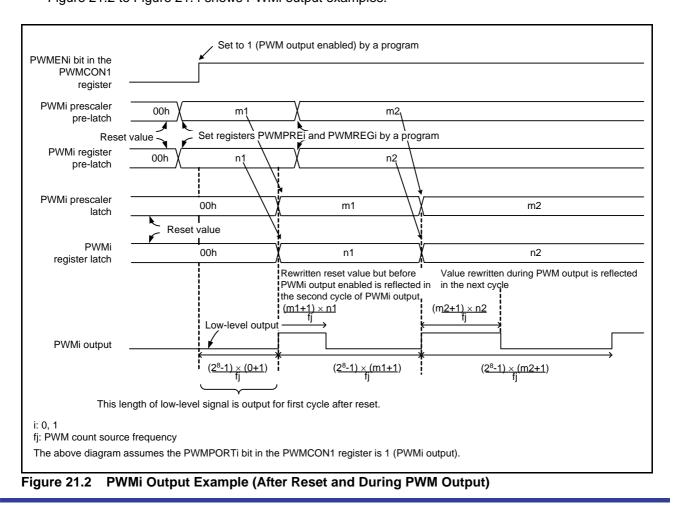

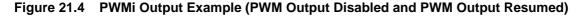

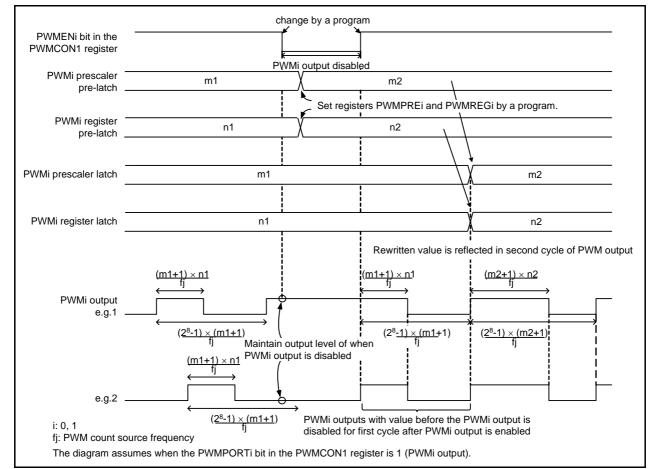

| 21.3    | .2    | Operation Example                                                                                                                                                                                                                                                    | . 416 |

|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 22. Rem | note  | Control Signal Receiver                                                                                                                                                                                                                                              | 418   |

| 22.1    | Intro | oduction                                                                                                                                                                                                                                                             | . 418 |

| 22.2    | Reg   | gisters                                                                                                                                                                                                                                                              | . 421 |

| 22.2    | .1    | Peripheral Clock Stop Register (PCLKSTP1)                                                                                                                                                                                                                            | . 423 |

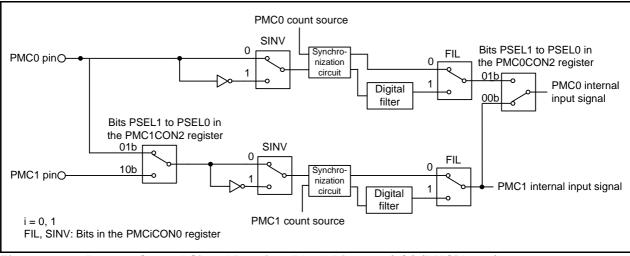

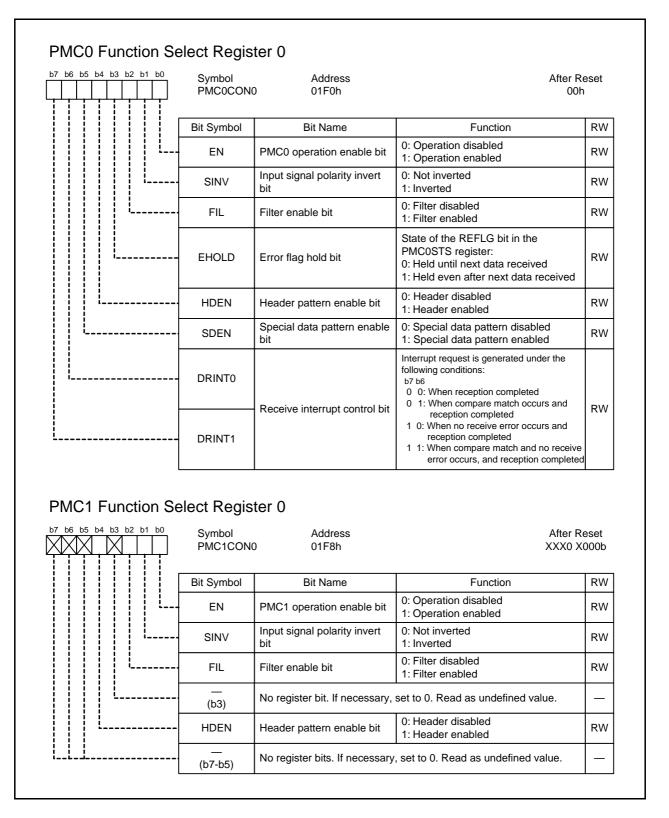

| 22.2    | .2    | PMCi Function Select Register 0 (PMCiCON0) (i = 0, 1)                                                                                                                                                                                                                | . 424 |

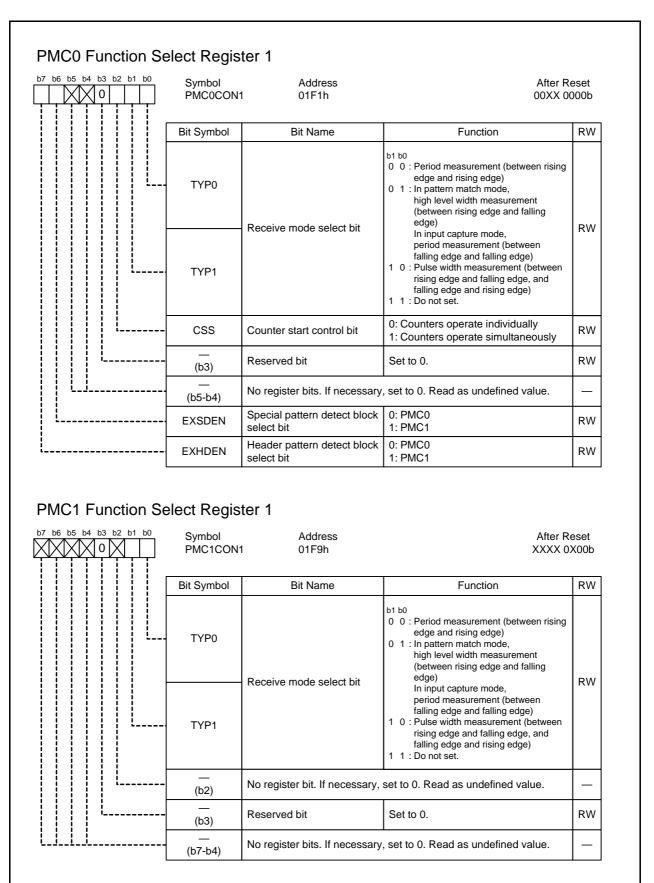

| 22.2    | .3    | PMCi Function Select Register 1 (PMCiCON1) (i = 0, 1)                                                                                                                                                                                                                | . 426 |

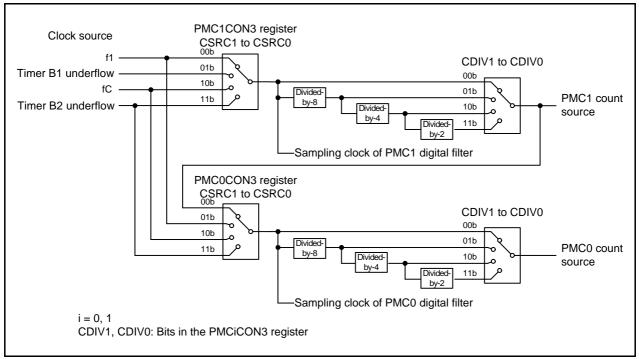

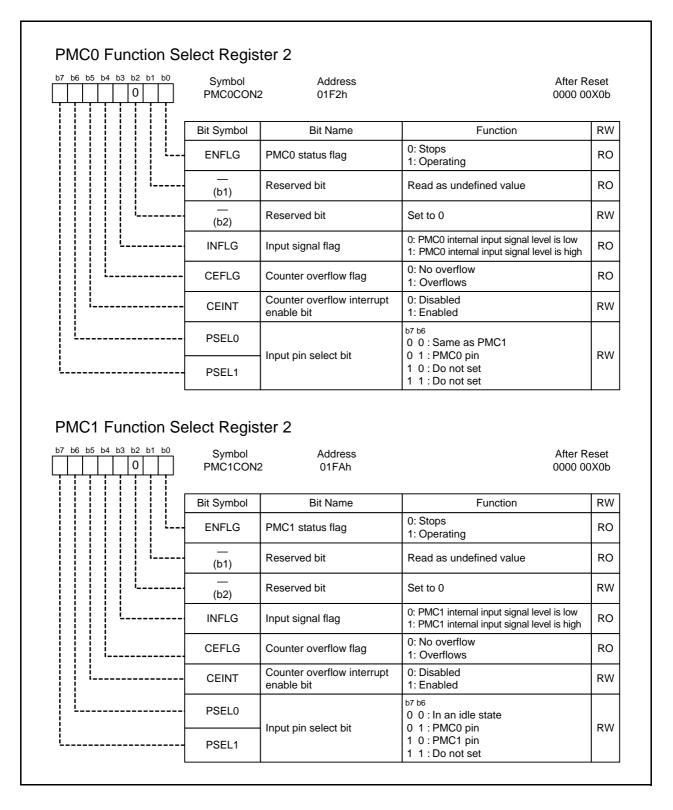

| 22.2    | .4    | PMCi Function Select Register 2 (PMCiCON2) (i = 0, 1)                                                                                                                                                                                                                | . 428 |

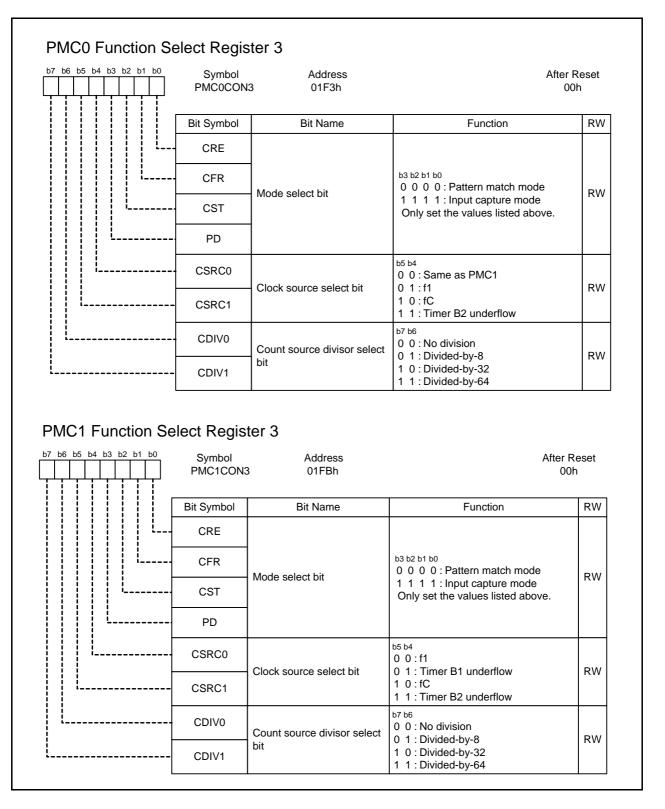

| 22.2    | .5    | PMCi Function Select Register 3 (PMCiCON3) (i = 0, 1)                                                                                                                                                                                                                | . 430 |

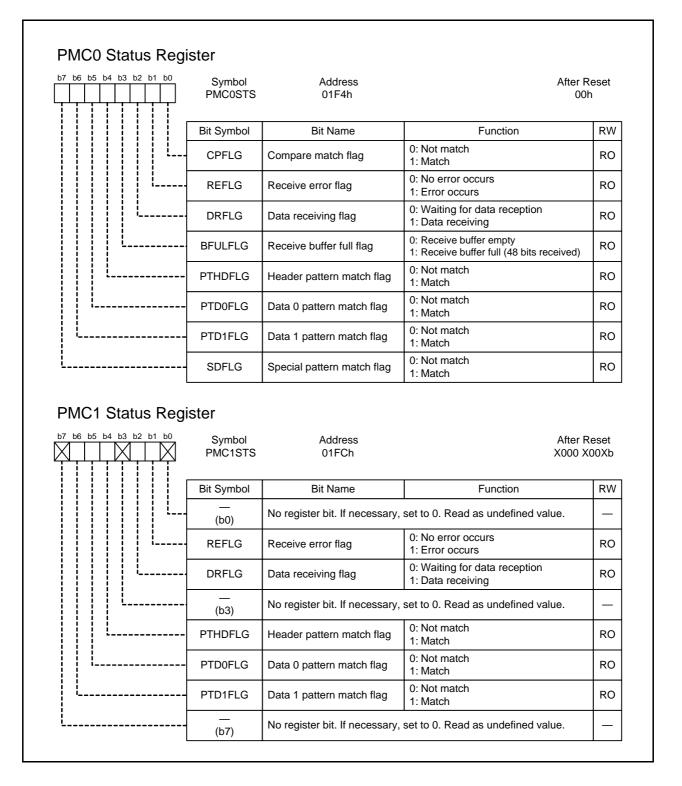

| 22.2    | .6    | PMCi Status Register (PMCiSTS) (i = 0, 1)                                                                                                                                                                                                                            | . 431 |

| 22.2    | .7    | PMCi Interrupt Source Register (PMCiINT) (i = 0, 1)                                                                                                                                                                                                                  | . 434 |

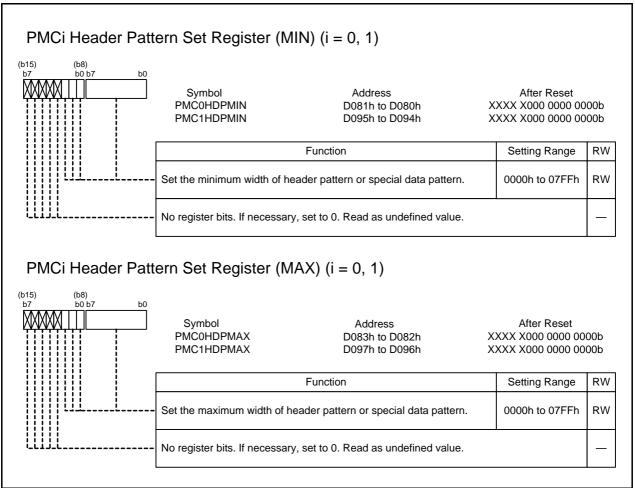

| 22.2    | .8    | PMCi Header Pattern Set Register (MIN) (PMCiHDPMIN) (i = 0, 1)<br>PMCi Header Pattern Set Register (MAX) (PMCiHDPMAX) (i = 0, 1)                                                                                                                                     | . 435 |

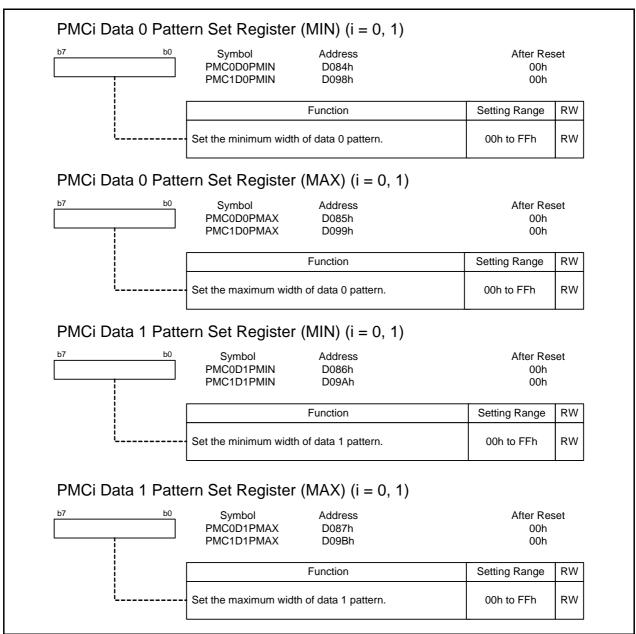

| 22.2.   | .9    | PMCi Data 0 Pattern Set Register (MIN) (PMCiD0PMIN) (i = 0, 1)<br>PMCi Data 0 Pattern Set Register (MAX) (PMCiD0PMAX) (i = 0, 1)<br>PMCi Data 1 Pattern Set Register (MIN) (PMCiD1PMIN) (i = 0, 1)<br>PMCi Data 1 Pattern Set Register (MAX) (PMCiD1PMAX) (i = 0, 1) | . 436 |

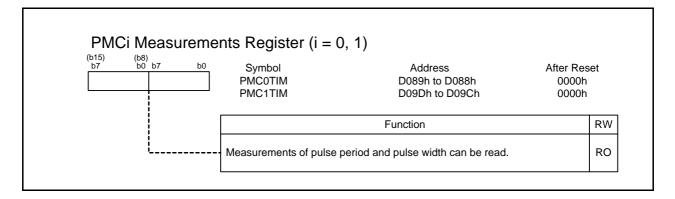

| 22.2    | .10   | PMCi Measurements Register (PMCiTIM) (i = 0, 1)                                                                                                                                                                                                                      | . 437 |

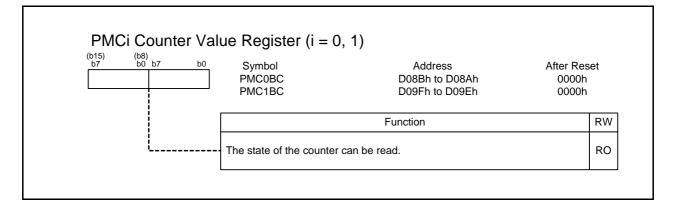

| 22.2    | .11   | PMCi Counter Value Register (PMCiBC) (i = 0, 1)                                                                                                                                                                                                                      | . 437 |

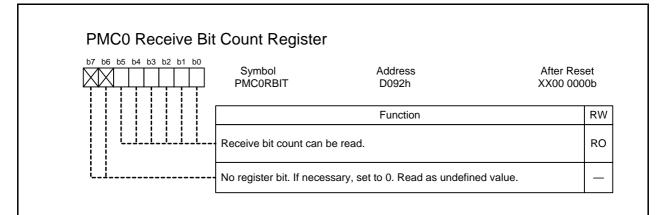

| 22.2    | .12   | PMC0 Receive Bit Count Register (PMC0RBIT)                                                                                                                                                                                                                           | . 437 |

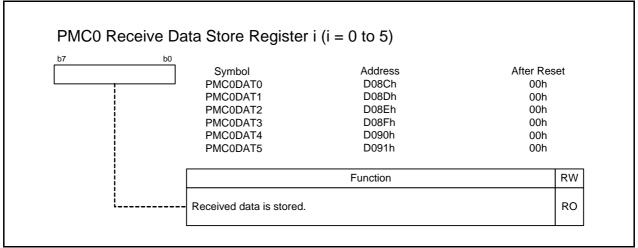

| 22.2    | .13   | PMC0 Receive Data Store Register i (PMC0DATi) (i = 0 to 5)                                                                                                                                                                                                           | . 438 |

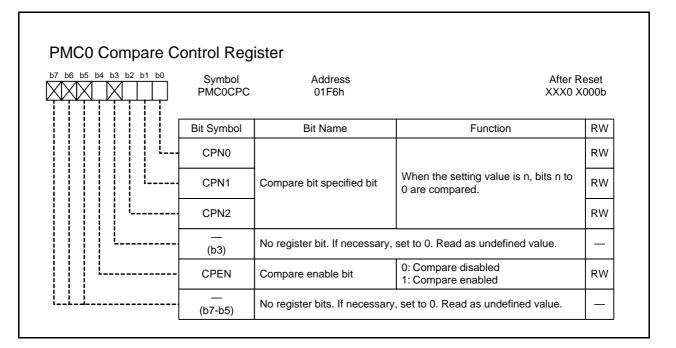

| 22.2    | .14   | PMC0 Compare Control Register (PMC0CPC)                                                                                                                                                                                                                              | . 439 |

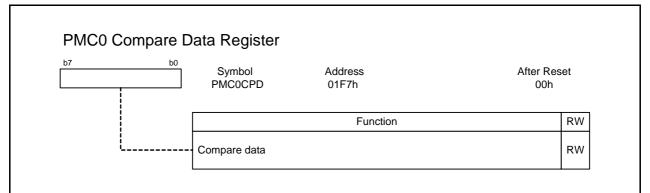

| 22.2    | .15   | PMC0 Compare Data Register (PMC0CPD)                                                                                                                                                                                                                                 | . 440 |

| 22.3    | Ope   | erations                                                                                                                                                                                                                                                             | . 441 |

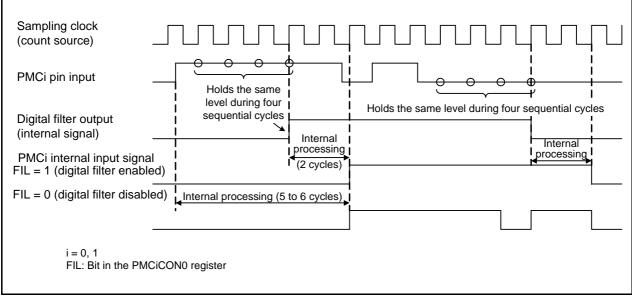

| 22.3    | .1    | Common Operations in Multiple Modes                                                                                                                                                                                                                                  | . 441 |

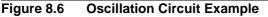

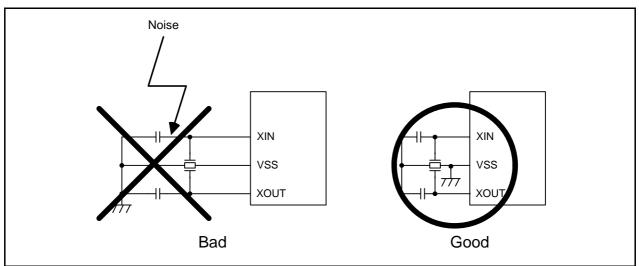

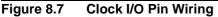

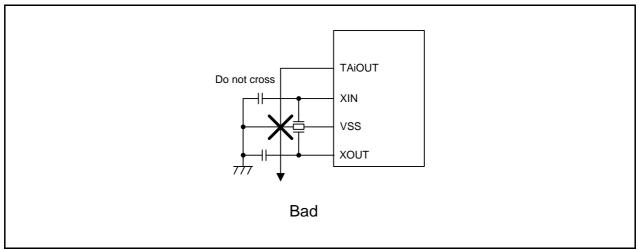

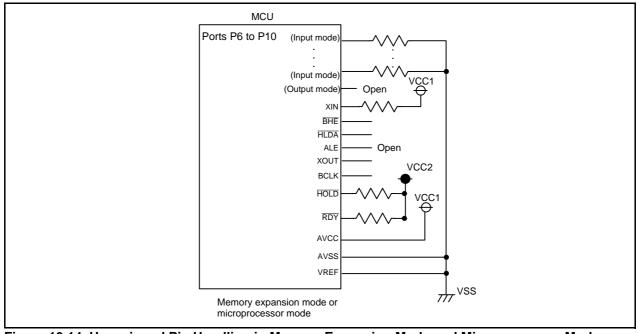

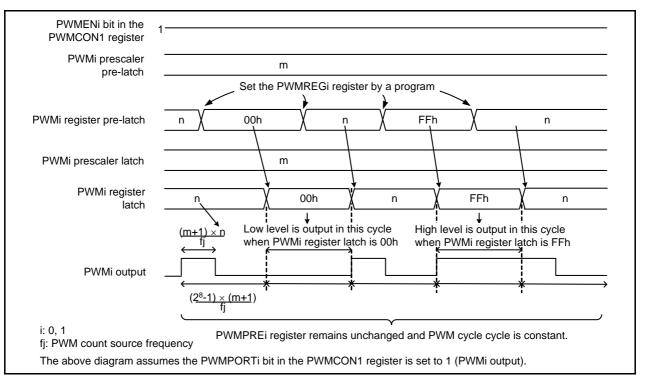

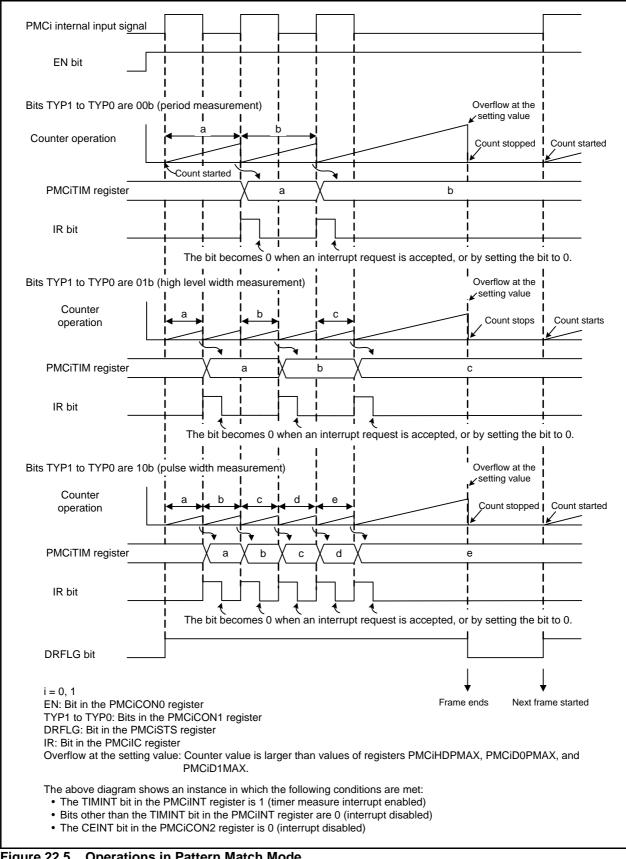

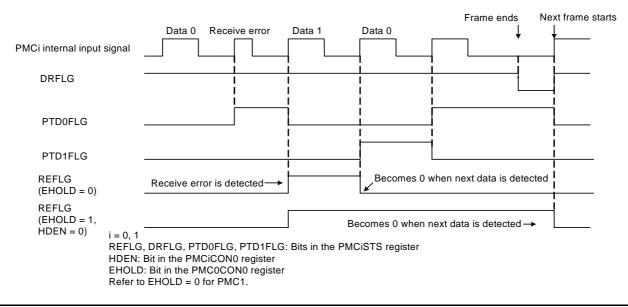

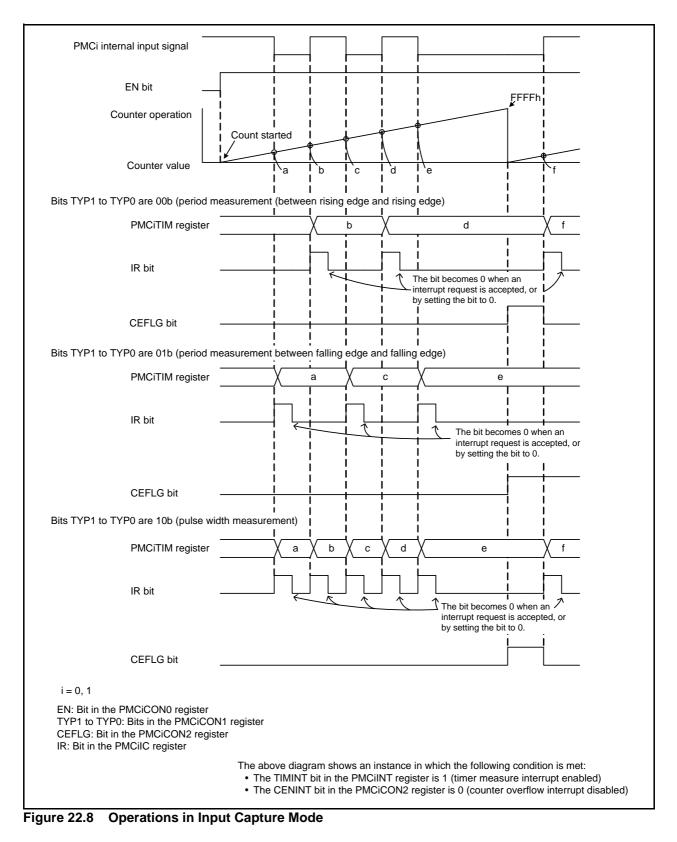

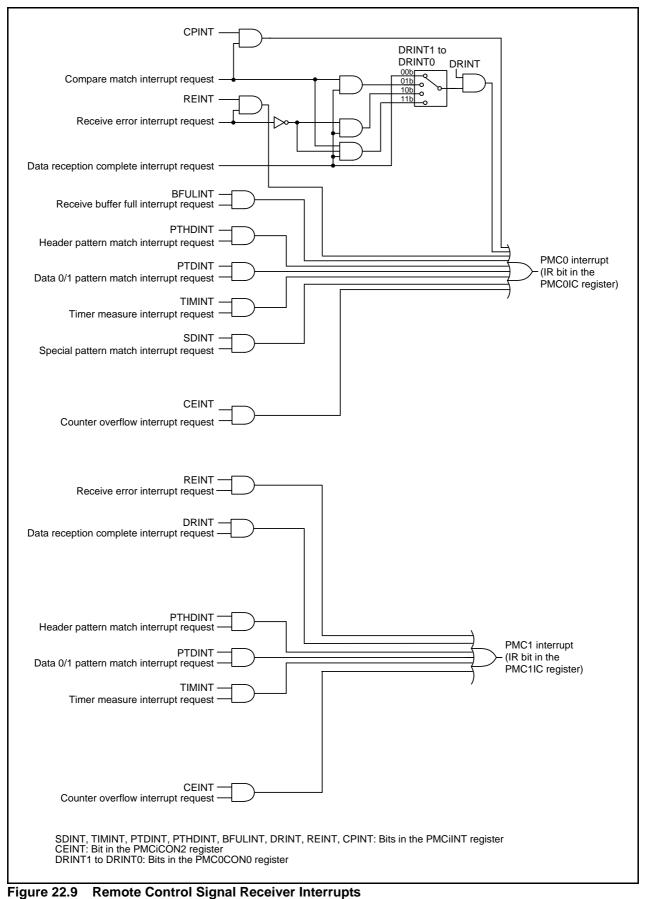

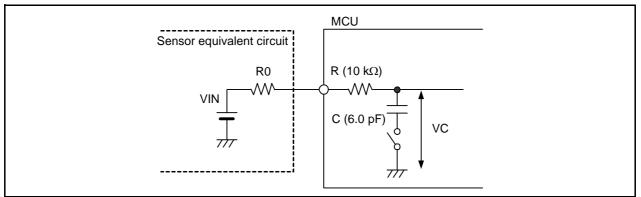

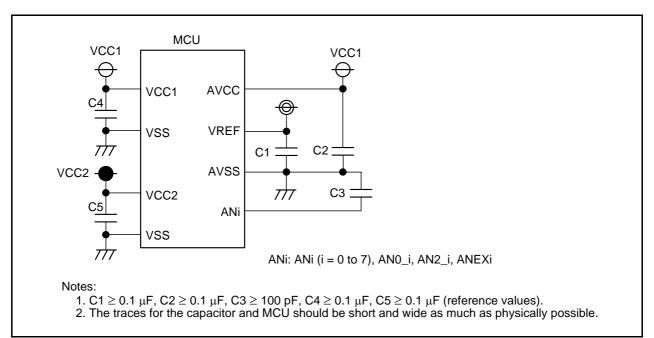

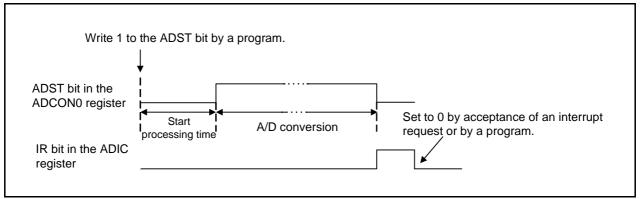

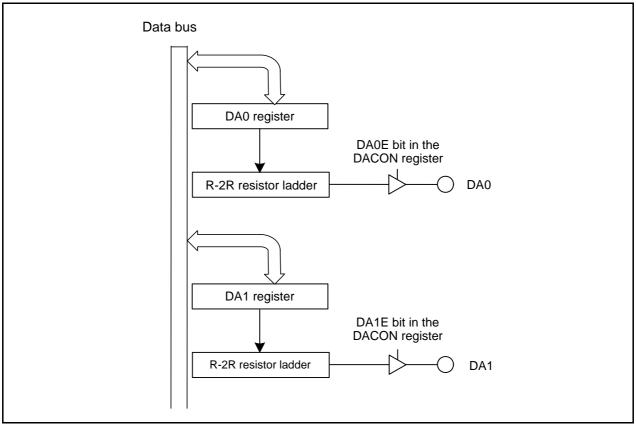

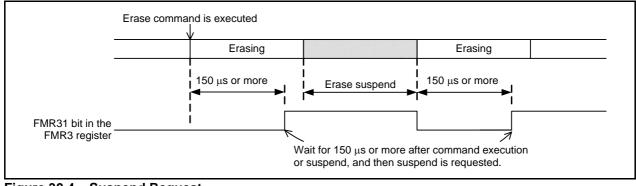

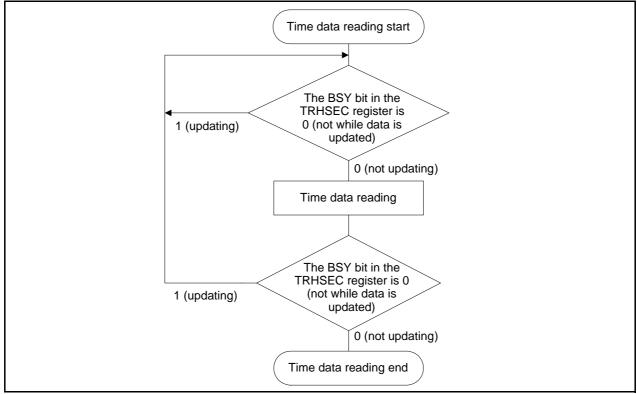

| 22.3    | .2    | Pattern Match Mode (PMC0 and PMC1 Operate Individually)                                                                                                                                                                                                              | . 443 |