# Features

- High Performance, Low Power AVR<sup>®</sup>32 UC 32-Bit Microcontroller

- Compact Single-cycle RISC Instruction Set Including DSP Instruction Set

- Read-Modify-Write Instructions and Atomic Bit Manipulation

- Performing up to 1.39 DMIPS / MHz

- Up to 83 DMIPS Running at 60 MHz from Flash

- Up to 46 DMIPS Running at 30 MHz from Flash

- Memory Protection Unit

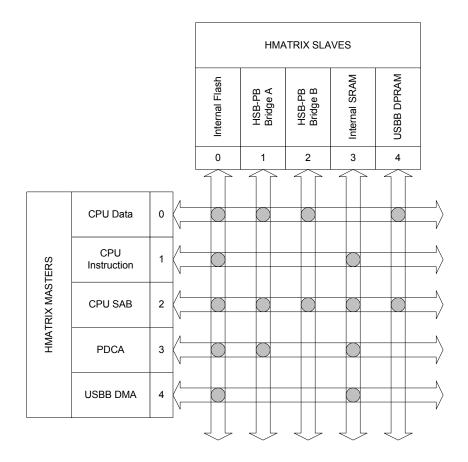

- Multi-hierarchy Bus System

- High-Performance Data Transfers on Separate Buses for Increased Performance

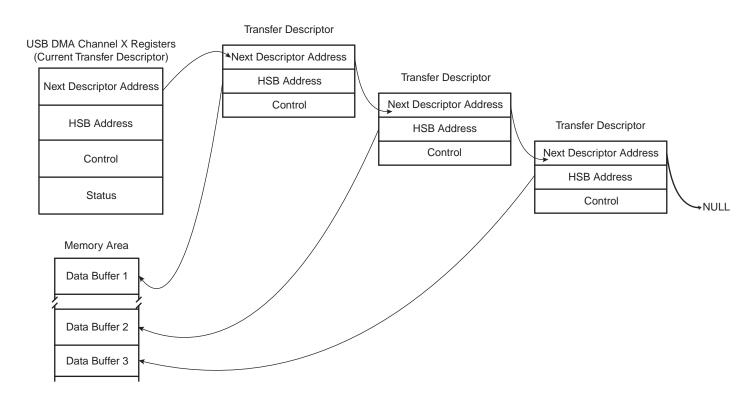

- 7 Peripheral DMA Channels Improves Speed for Peripheral Communication

- Internal High-Speed Flash

- 512K Bytes, 256K Bytes, 128K Bytes, 64K Bytes Versions

- Single Cycle Access up to 30 MHz

- Prefetch Buffer Optimizing Instruction Execution at Maximum Speed

- 4ms Page Programming Time and 8ms Full-Chip Erase Time

- 100,000 Write Cycles, 15-year Data Retention Capability

- Flash Security Locks and User Defined Configuration Area

- Internal High-Speed SRAM, Single-Cycle Access at Full Speed

- 96K Bytes (512KB Flash), 32K Bytes (256KB and 128KB Flash), 16K Bytes (64KB Flash)

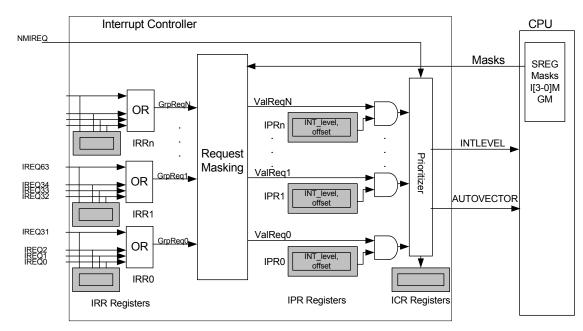

- Interrupt Controller

- Autovectored Low Latency Interrupt Service with Programmable Priority

- System Functions

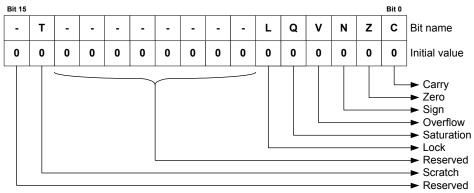

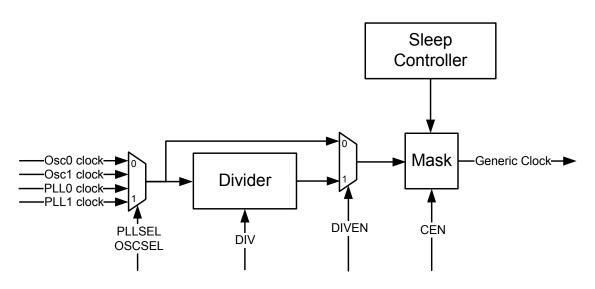

- Power and Clock Manager Including Internal RC Clock and One 32KHz Oscillator

- Two Multipurpose Oscillators and Two Phase-Lock-Loop (PLL) allowing Independant CPU Frequency from USB Frequency

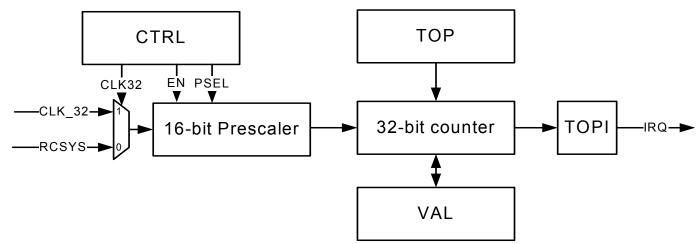

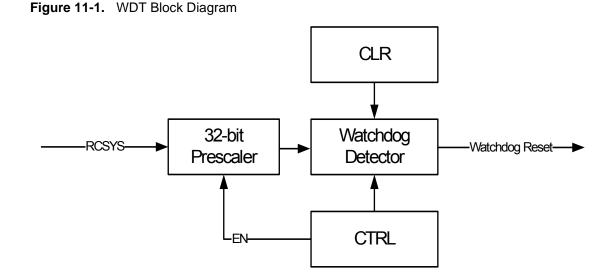

- Watchdog Timer, Real-Time Clock Timer

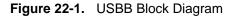

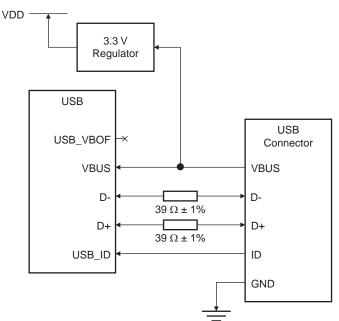

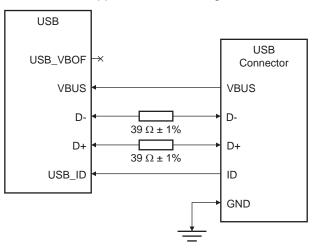

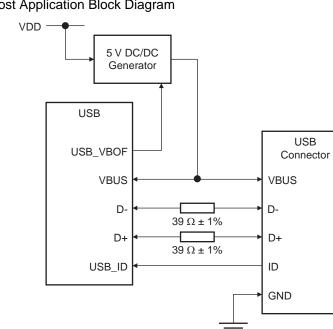

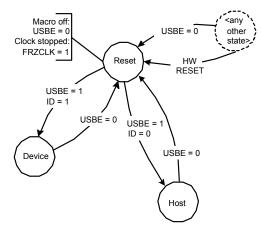

- Universal Serial Bus (USB)

- Device 2.0 and Embedded Host Low Speed and Full Speed

- Flexible End-Point Configuration and Management with Dedicated DMA Channels

- On-chip Transceivers Including Pull-Ups

- USB Wake Up from Sleep Functionality

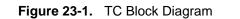

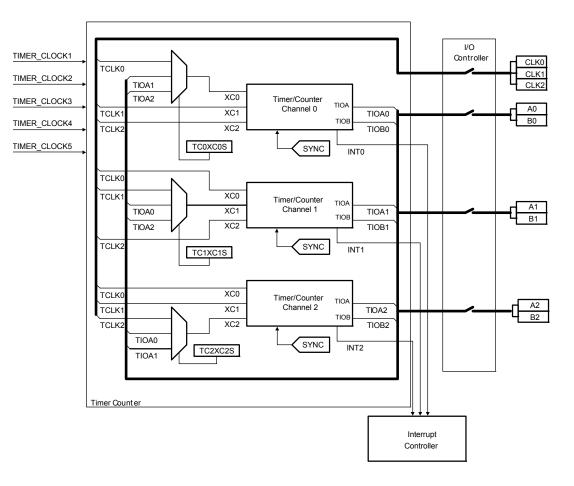

- One Three-Channel 16-bit Timer/Counter (TC)

- Three External Clock Inputs, PWM, Capture and Various Counting Capabilities

- One 7-Channel 20-bit Pulse Width Modulation Controller (PWM)

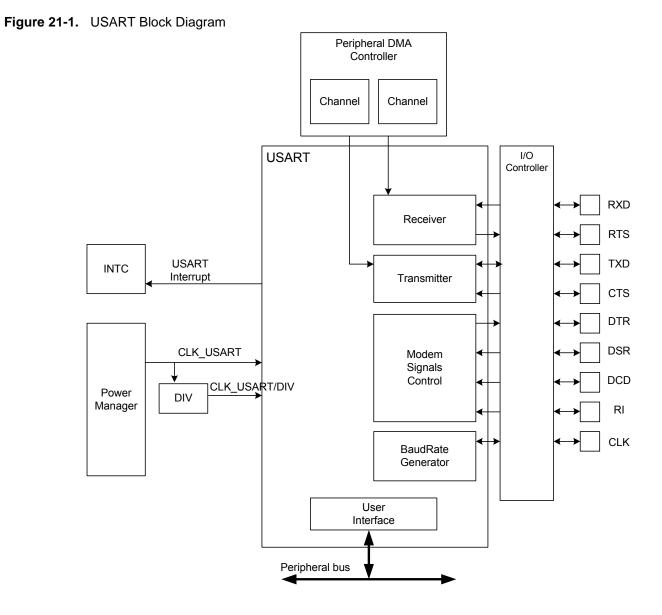

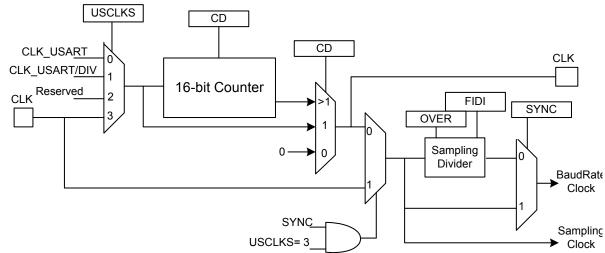

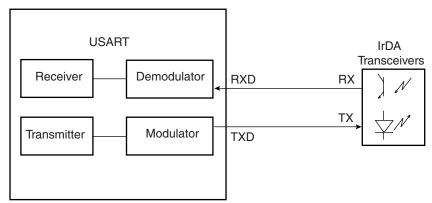

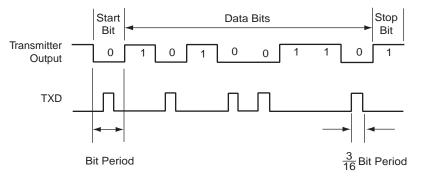

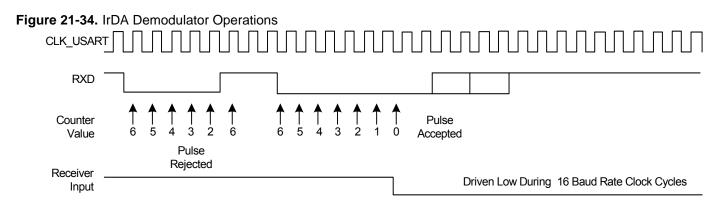

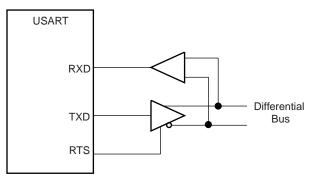

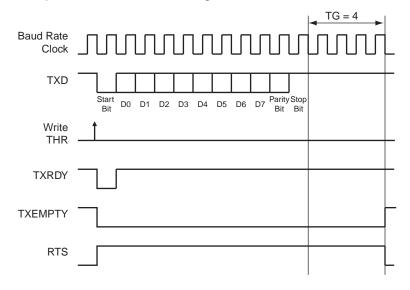

- Three Universal Synchronous/Asynchronous Receiver/Transmitters (USART)

- Independant Baudrate Generator, Support for SPI, IrDA and ISO7816 interfaces

- Support for Hardware Handshaking, RS485 Interfaces and Modem Line

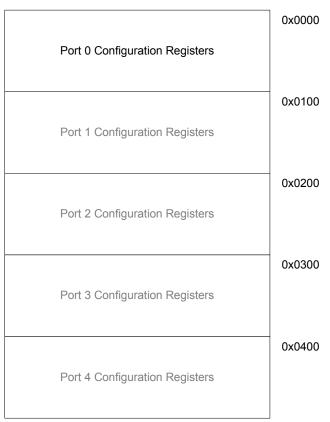

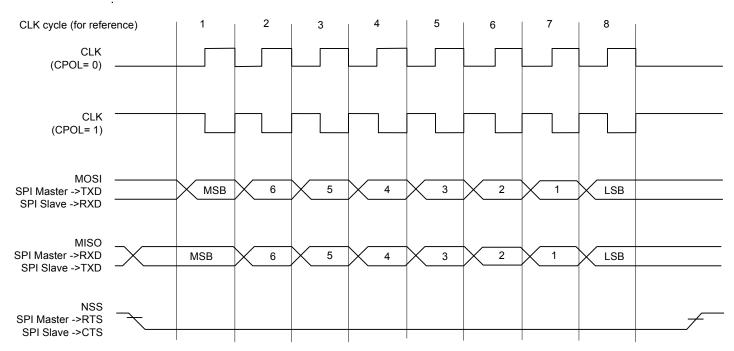

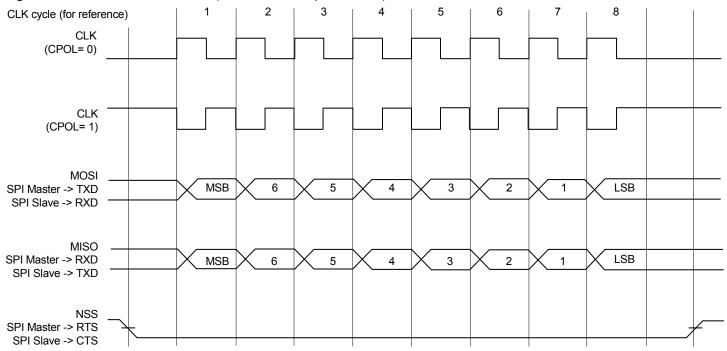

- One Master/Slave Serial Peripheral Interfaces (SPI) with Chip Select Signals

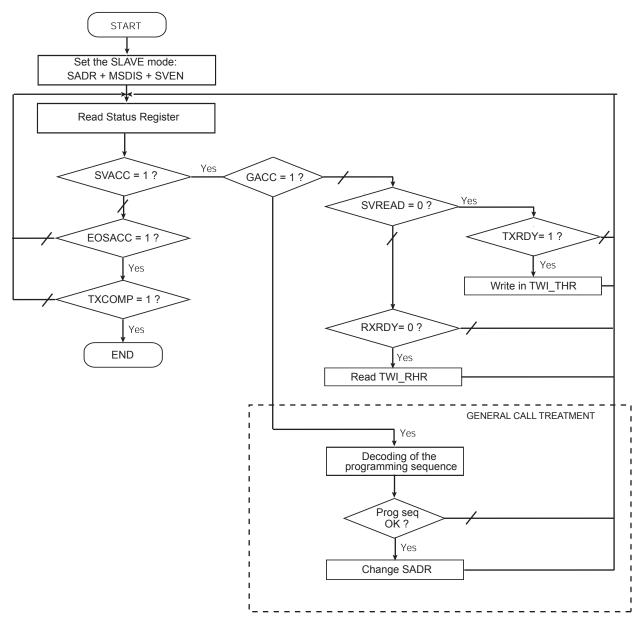

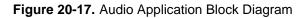

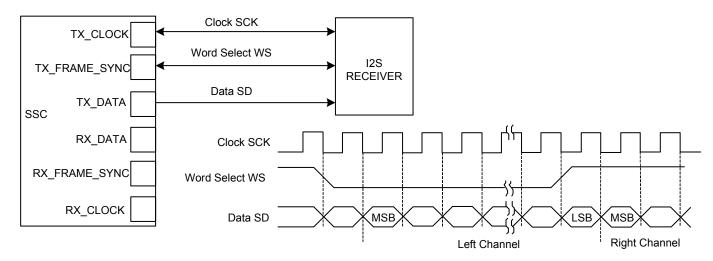

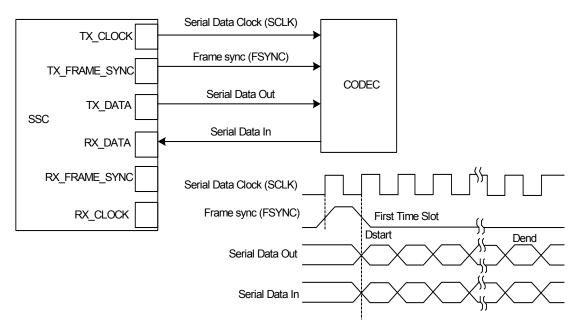

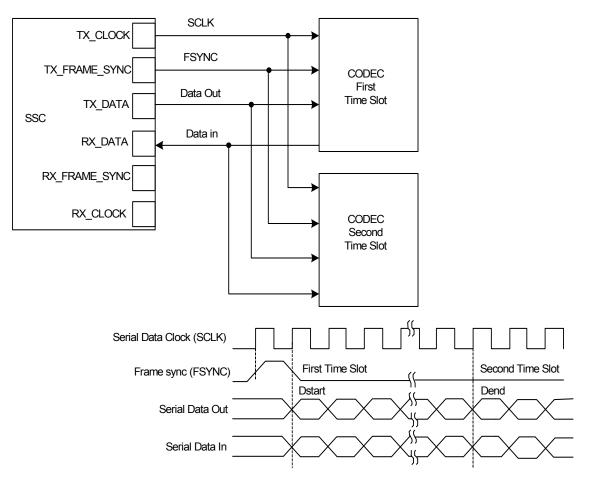

- One Synchronous Serial Protocol Controller

- Supports I<sup>2</sup>S and Generic Frame-Based Protocols

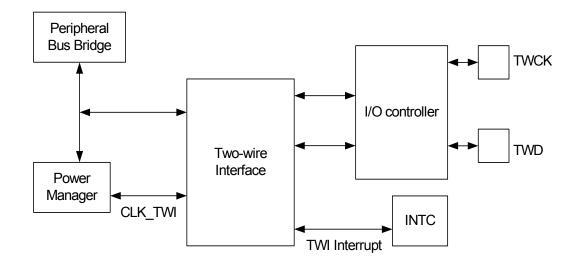

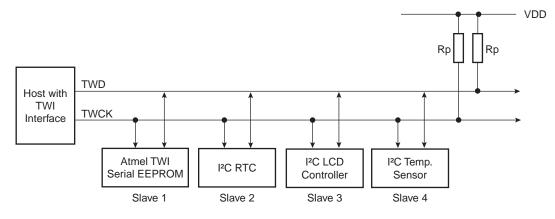

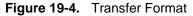

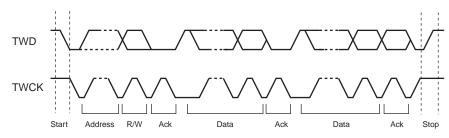

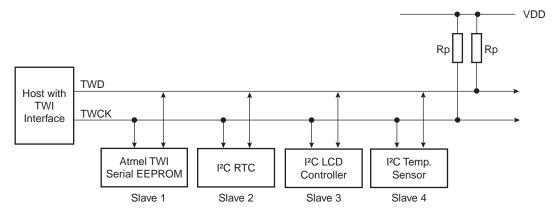

- One Master/Slave Two-Wire Interface (TWI), 400kbit/s I<sup>2</sup>C-compatible

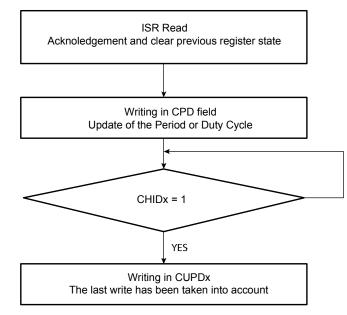

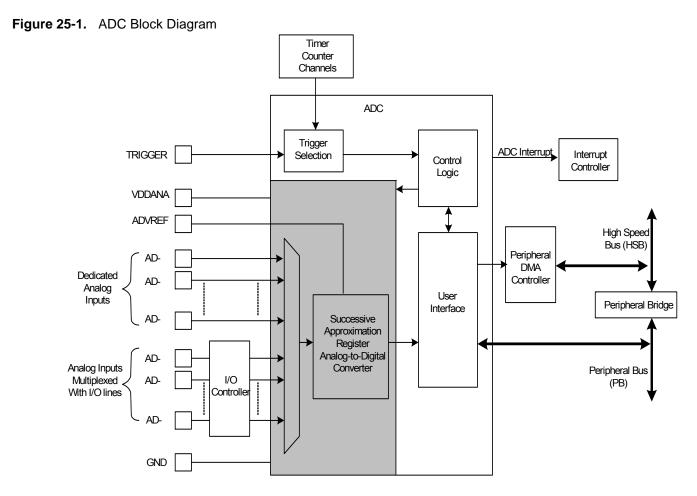

- One 8-channel 10-bit Analog-To-Digital Converter, 384ks/s

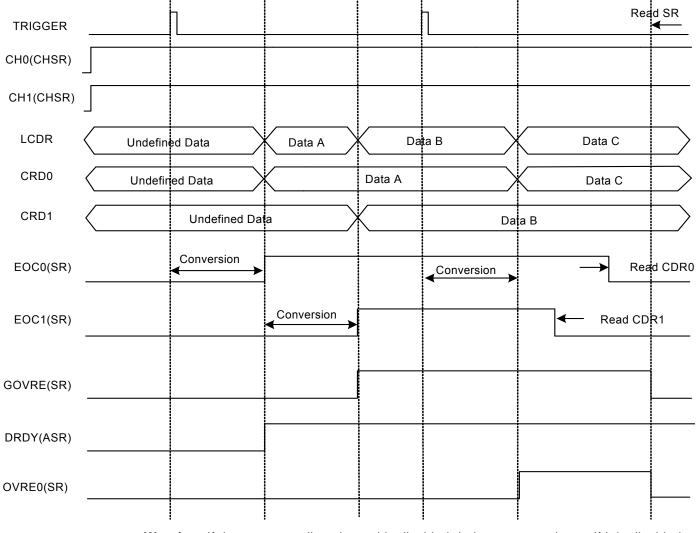

- 16-bit Stereo Audio Bitstream DAC

- Sample Rate Up to 50 KHz

- QTouch<sup>®</sup> Library Support

- Capacitive Touch Buttons, Sliders, and Wheels

- QTouch<sup>®</sup> and QMatrix<sup>®</sup> Acquisition

32-bit AVR<sup>®</sup> Microcontroller

AT32UC3B0512 AT32UC3B0256 AT32UC3B0128 AT32UC3B064 AT32UC3B1512 AT32UC3B1256 AT32UC3B1256 AT32UC3B1128 AT32UC3B164

# AT32UC3B

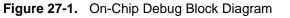

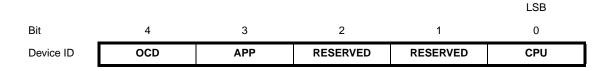

- On-Chip Debug System (JTAG interface)

- Nexus Class 2+, Runtime Control, Non-Intrusive Data and Program Trace

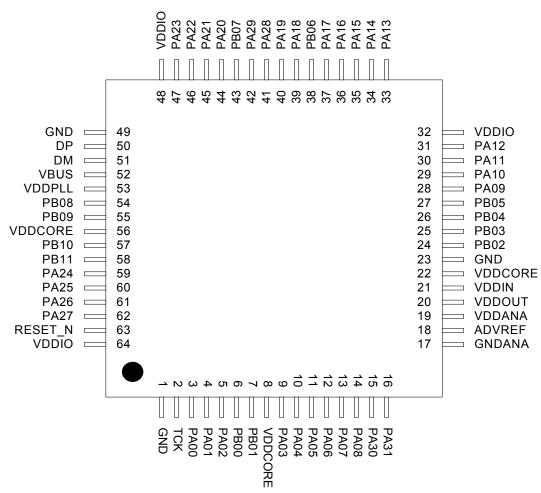

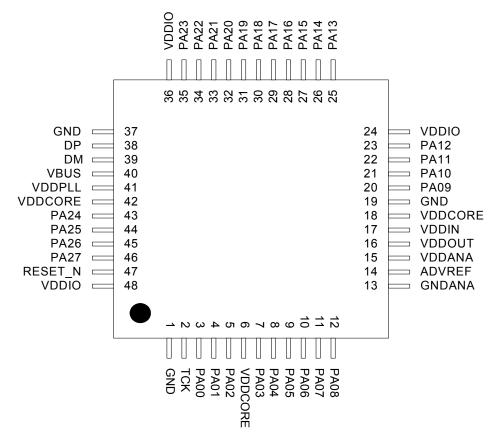

- 64-pin TQFP/QFN (44 GPIO pins), 48-pin TQFP/QFN (28 GPIO pins)

- 5V Input Tolerant I/Os, including 4 high-drive pins

- Single 3.3V Power Supply or Dual 1.8V-3.3V Power Supply

# 1. Description

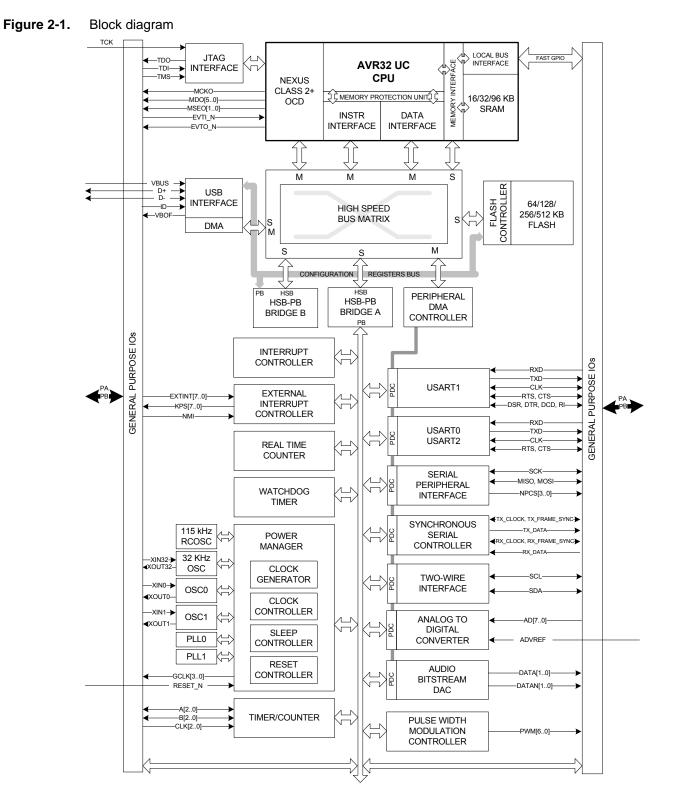

The AT32UC3B is a complete System-On-Chip microcontroller based on the AVR32 UC RISC processor running at frequencies up to 60 MHz. AVR32 UC is a high-performance 32-bit RISC microprocessor core, designed for cost-sensitive embedded applications, with particular emphasis on low power consumption, high code density and high performance.

The processor implements a Memory Protection Unit (MPU) and a fast and flexible interrupt controller for supporting modern operating systems and real-time operating systems.

Higher computation capability is achieved using a rich set of DSP instructions.

The AT32UC3B incorporates on-chip Flash and SRAM memories for secure and fast access.

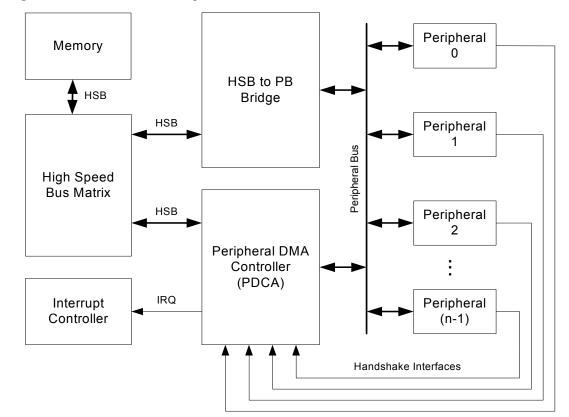

The Peripheral Direct Memory Access controller enables data transfers between peripherals and memories without processor involvement. PDCA drastically reduces processing overhead when transferring continuous and large data streams between modules within the MCU.

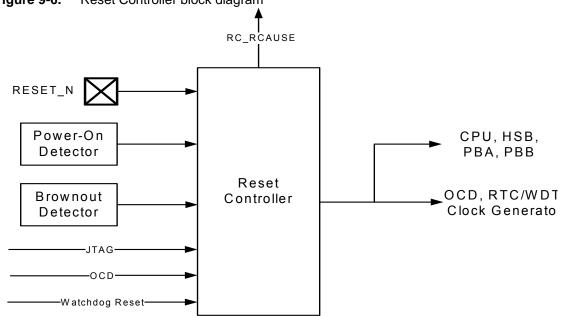

The Power Manager improves design flexibility and security: the on-chip Brown-Out Detector monitors the power supply, the CPU runs from the on-chip RC oscillator or from one of external oscillator sources, a Real-Time Clock and its associated timer keeps track of the time.

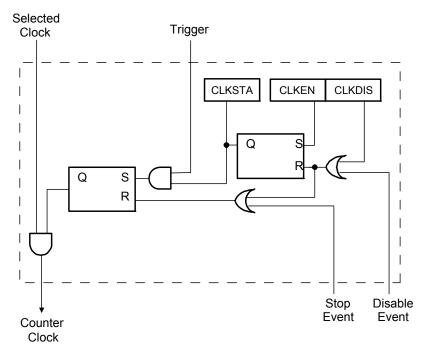

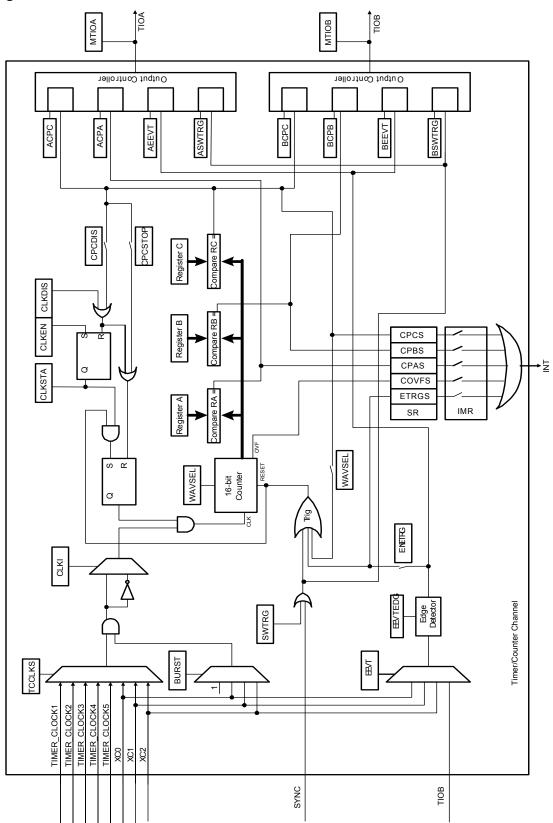

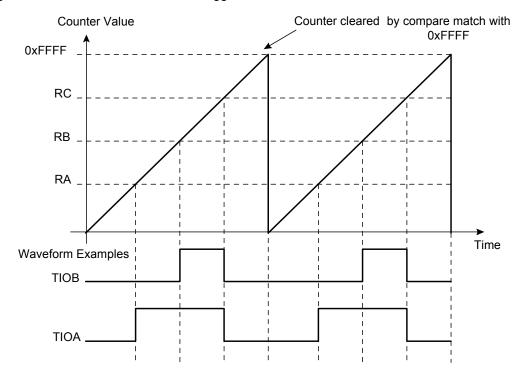

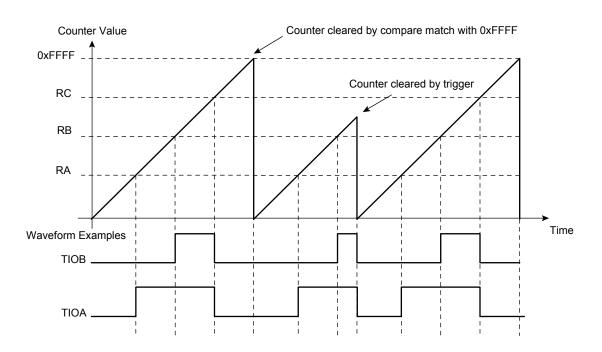

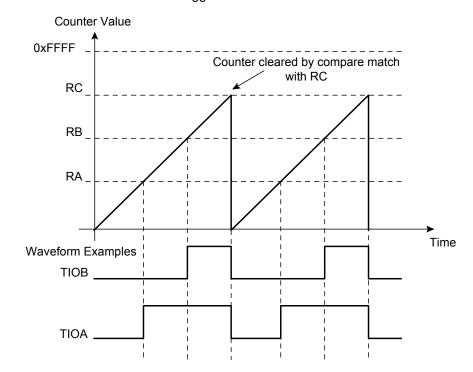

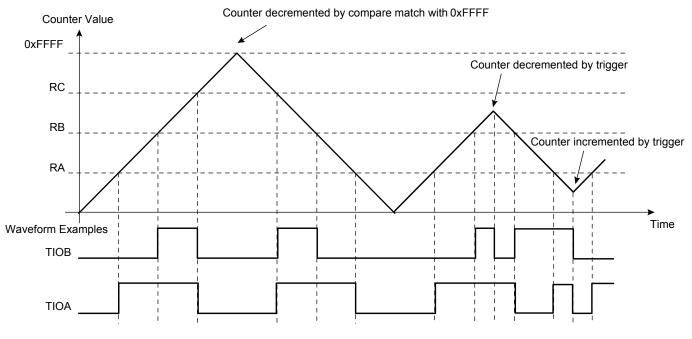

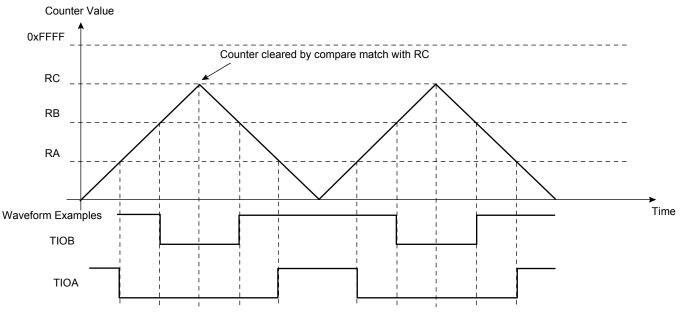

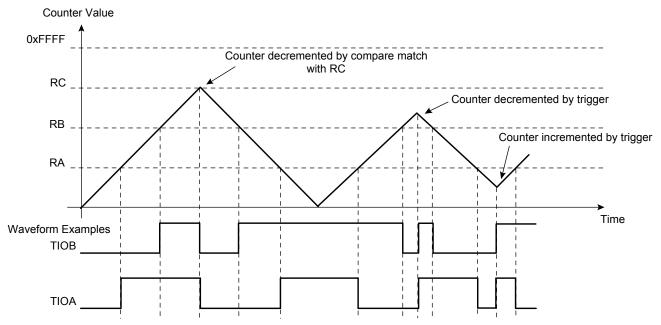

The Timer/Counter includes three identical 16-bit timer/counter channels. Each channel can be independently programmed to perform frequency measurement, event counting, interval measurement, pulse generation, delay timing and pulse width modulation.

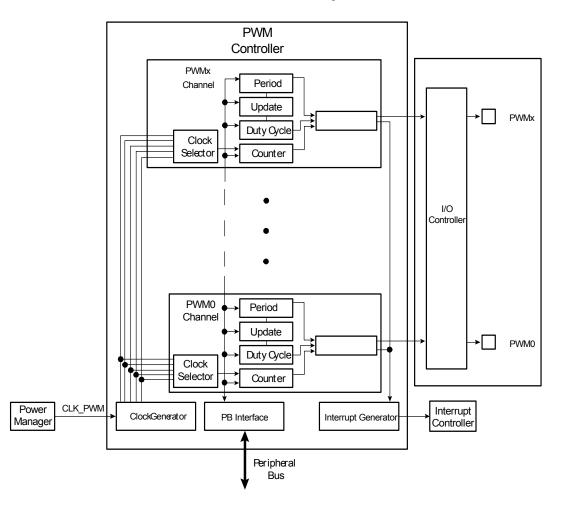

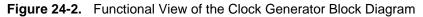

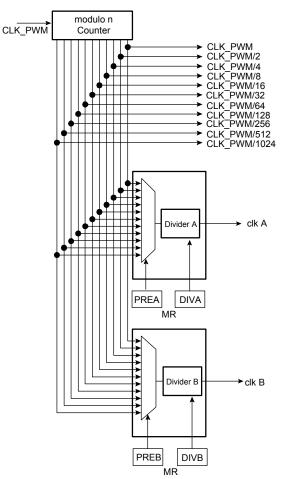

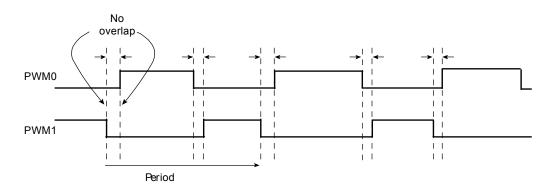

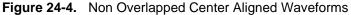

The PWM modules provides seven independent channels with many configuration options including polarity, edge alignment and waveform non overlap control. One PWM channel can trigger ADC conversions for more accurate close loop control implementations.

The AT32UC3B also features many communication interfaces for communication intensive applications. In addition to standard serial interfaces like USART, SPI or TWI, other interfaces like flexible Synchronous Serial Controller and USB are available. The USART supports different communication modes, like SPI mode.

The Synchronous Serial Controller provides easy access to serial communication protocols and audio standards like I<sup>2</sup>S, UART or SPI.

The Full-Speed USB 2.0 Device interface supports several USB Classes at the same time thanks to the rich End-Point configuration. The Embedded Host interface allows device like a USB Flash disk or a USB printer to be directly connected to the processor.

Atmel offers the QTouch library for embedding capacitive touch buttons, sliders, and wheels functionality into AVR microcontrollers. The patented charge-transfer signal acquisition offers robust sensing and included fully debounced reporting of touch keys and includes Adjacent Key Suppression<sup>®</sup> (AKS<sup>®</sup>) technology for unambiguous detection of key events. The easy-to-use QTouch Suite toolchain allows you to explore, develop, and debug your own touch applications.

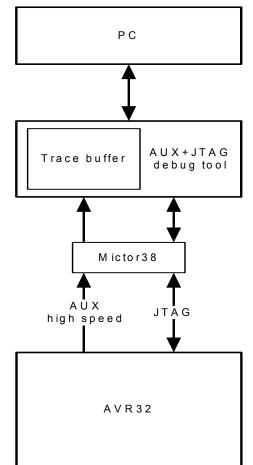

AT32UC3B integrates a class 2+ Nexus 2.0 On-Chip Debug (OCD) System, with non-intrusive real-time trace, full-speed read/write memory access in addition to basic runtime control. The Nanotrace interface enables trace feature for JTAG-based debuggers.

# 2. Overview

# 2.1 Blockdiagram

# 3. Configuration Summary

The table below lists all AT32UC3B memory and package configurations:

| Feature                          | AT32UC3B0512                                                                                                                                                                        | AT32UC3B0256/128/64 | AT32UC3B1512 | AT32UC3B1256/128/64 |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------|---------------------|

| Flash                            | 512 KB                                                                                                                                                                              | 256/128/64 KB       | 512 KB       | 256/128/64 KB       |

| SRAM                             | 96KB                                                                                                                                                                                | 32/32/16KB          | 96KB         | 32/16/16KB          |

| GPIO                             |                                                                                                                                                                                     | 44                  |              | 28                  |

| External Interrupts              |                                                                                                                                                                                     | 8                   |              | 6                   |

| TWI                              |                                                                                                                                                                                     | 1                   |              |                     |

| USART                            |                                                                                                                                                                                     | 3                   |              |                     |

| Peripheral DMA Channels          |                                                                                                                                                                                     | 7                   |              |                     |

| SPI                              |                                                                                                                                                                                     | 1                   |              |                     |

| Full Speed USB                   | Mini-Ho                                                                                                                                                                             | st + Device         | D            | evice               |

| SSC                              | 1 0                                                                                                                                                                                 |                     |              | 0                   |

| Audio Bitstream DAC              | 1                                                                                                                                                                                   | 0                   | 1            | 0                   |

| Timer/Counter Channels           |                                                                                                                                                                                     | 3                   |              |                     |

| PWM Channels                     |                                                                                                                                                                                     | 7                   |              |                     |

| Watchdog Timer                   |                                                                                                                                                                                     | 1                   |              |                     |

| Real-Time Clock Timer            |                                                                                                                                                                                     | 1                   |              |                     |

| Power Manager                    | 1                                                                                                                                                                                   |                     |              |                     |

| Oscillators                      | PLL 80-240 MHz (PLL0/PLL1)<br>Crystal Oscillators 0.4-20 MHz (OSC0)<br>Crystal Oscillator 32 KHz (OSC32K)<br>RC Oscillator 115 kHz (RCSYS)<br>Crystal Oscillators 0.4-20 MHz (OSC1) |                     |              |                     |

|                                  |                                                                                                                                                                                     |                     |              |                     |

| 10-bit ADC<br>number of channels | 8 6                                                                                                                                                                                 |                     |              |                     |

| JTAG                             |                                                                                                                                                                                     | 1                   |              |                     |

| Max Frequency                    | 60 MHz                                                                                                                                                                              |                     |              |                     |

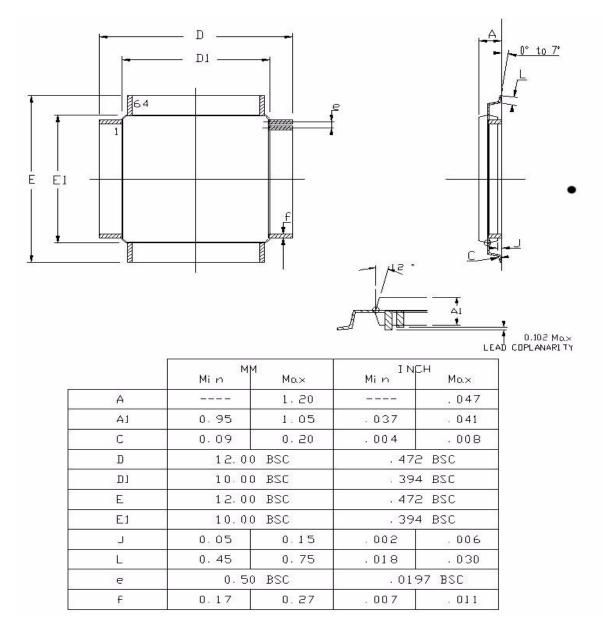

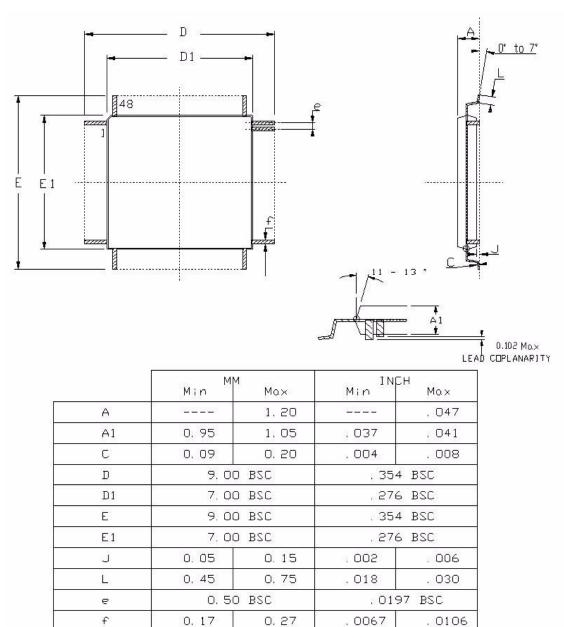

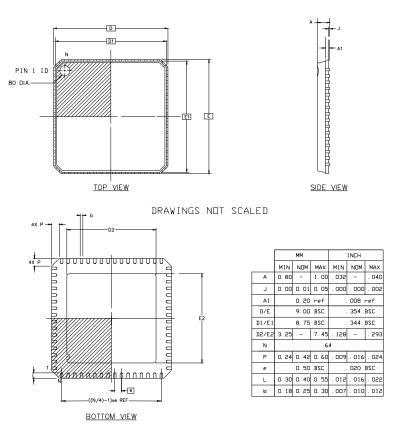

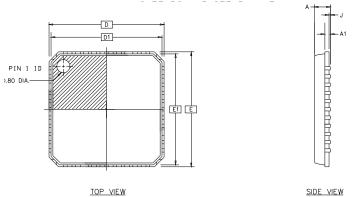

| Package                          | TQFP6                                                                                                                                                                               | 64, QFN64           | TQFP         | 48, QFN48           |

Table 3-1.

Configuration Summary

# 4. Package and Pinout

# 4.1 Package

The device pins are multiplexed with peripheral functions as described in the Peripheral Multiplexing on I/O Line section.

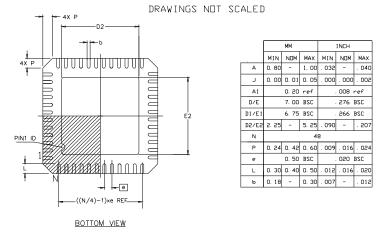

Figure 4-2. TQFP48 / QFN48 Pinout

# 4.2 Peripheral Multiplexing on I/O lines

#### 4.2.1 Multiplexed signals

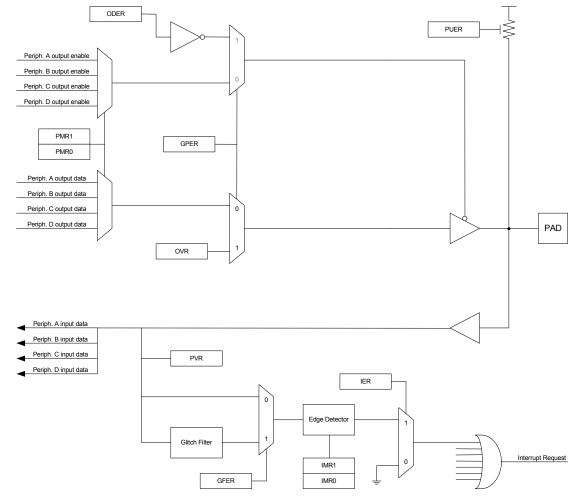

Each GPIO line can be assigned to one of 4 peripheral functions; A, B, C or D (D is only available for UC3Bx512 parts). The following table define how the I/O lines on the peripherals A, B,C or D are multiplexed by the GPIO.

| 48-pin | 64-pin | PIN  | GPIO Pin | Function A      | Function B   | Function C      | Function D<br>(only for UC3Bx512) |

|--------|--------|------|----------|-----------------|--------------|-----------------|-----------------------------------|

| 3      | 3      | PA00 | GPIO 0   |                 |              |                 |                                   |

| 4      | 4      | PA01 | GPIO 1   |                 |              |                 |                                   |

| 5      | 5      | PA02 | GPIO 2   |                 |              |                 |                                   |

| 7      | 9      | PA03 | GPIO 3   | ADC - AD[0]     | PM - GCLK[0] | USBB - USB_ID   | ABDAC - DATA[0]                   |

| 8      | 10     | PA04 | GPIO 4   | ADC - AD[1]     | PM - GCLK[1] | USBB - USB_VBOF | ABDAC - DATAN[0]                  |

| 9      | 11     | PA05 | GPIO 5   | EIC - EXTINT[0] | ADC - AD[2]  | USART1 - DCD    | ABDAC - DATA[1]                   |

| 10     | 12     | PA06 | GPIO 6   | EIC - EXTINT[1] | ADC - AD[3]  | USART1 - DSR    | ABDAC - DATAN[1]                  |

Table 4-1.

GPIO Controller Function Multiplexing

|    | GFIC |      |         | miniumpiexing          |                |                 |                        |

|----|------|------|---------|------------------------|----------------|-----------------|------------------------|

| 11 | 13   | PA07 | GPIO 7  | PWM - PWM[0]           | ADC - AD[4]    | USART1 - DTR    | SSC -<br>RX_FRAME_SYNC |

| 12 | 14   | PA08 | GPIO 8  | PWM - PWM[1]           | ADC - AD[5]    | USART1 - RI     | SSC - RX_CLOCK         |

| 20 | 28   | PA09 | GPIO 9  | TWI - SCL              | SPI0 - NPCS[2] | USART1 - CTS    |                        |

| 21 | 29   | PA10 | GPIO 10 | TWI - SDA              | SPI0 - NPCS[3] | USART1 - RTS    |                        |

| 22 | 30   | PA11 | GPIO 11 | USART0 - RTS           | TC - A2        | PWM - PWM[0]    | SSC - RX_DATA          |

| 23 | 31   | PA12 | GPIO 12 | USART0 - CTS           | TC - B2        | PWM - PWM[1]    | USART1 - TXD           |

| 25 | 33   | PA13 | GPIO 13 | EIC - NMI              | PWM - PWM[2]   | USART0 - CLK    | SSC - RX_CLOCK         |

| 26 | 34   | PA14 | GPIO 14 | SPI0 - MOSI            | PWM - PWM[3]   | EIC - EXTINT[2] | PM - GCLK[2]           |

| 27 | 35   | PA15 | GPIO 15 | SPI0 - SCK             | PWM - PWM[4]   | USART2 - CLK    |                        |

| 28 | 36   | PA16 | GPIO 16 | SPI0 - NPCS[0]         | TC - CLK1      | PWM - PWM[4]    |                        |

| 29 | 37   | PA17 | GPIO 17 | SPI0 - NPCS[1]         | TC - CLK2      | SPI0 - SCK      | USART1 - RXD           |

| 30 | 39   | PA18 | GPIO 18 | USART0 - RXD           | PWM - PWM[5]   | SPI0 - MISO     | SSC -<br>RX_FRAME_SYNC |

| 31 | 40   | PA19 | GPIO 19 | USART0 - TXD           | PWM - PWM[6]   | SPI0 - MOSI     | SSC - TX_CLOCK         |

| 32 | 44   | PA20 | GPIO 20 | USART1 - CLK           | TC - CLK0      | USART2 - RXD    | SSC - TX_DATA          |

| 33 | 45   | PA21 | GPIO 21 | PWM - PWM[2]           | TC - A1        | USART2 - TXD    | SSC -<br>TX_FRAME_SYNC |

| 34 | 46   | PA22 | GPIO 22 | PWM - PWM[6]           | TC - B1        | ADC - TRIGGER   | ABDAC - DATA[0]        |

| 35 | 47   | PA23 | GPIO 23 | USART1 - TXD           | SPI0 - NPCS[1] | EIC - EXTINT[3] | PWM - PWM[0]           |

| 43 | 59   | PA24 | GPIO 24 | USART1 - RXD           | SPI0 - NPCS[0] | EIC - EXTINT[4] | PWM - PWM[1]           |

| 44 | 60   | PA25 | GPIO 25 | SPI0 - MISO            | PWM - PWM[3]   | EIC - EXTINT[5] |                        |

| 45 | 61   | PA26 | GPIO 26 | USBB - USB_ID          | USART2 - TXD   | TC - A0         | ABDAC - DATA[1]        |

| 46 | 62   | PA27 | GPIO 27 | USBB - USB_VBOF        | USART2 - RXD   | TC - B0         | ABDAC - DATAN[1]       |

|    | 41   | PA28 | GPIO 28 | USART0 - CLK           | PWM - PWM[4]   | SPI0 - MISO     | ABDAC - DATAN[0]       |

|    | 42   | PA29 | GPIO 29 | TC - CLK0              | TC - CLK1      | SPI0 - MOSI     |                        |

|    | 15   | PA30 | GPIO 30 | ADC - AD[6]            | EIC - SCAN[0]  | PM - GCLK[2]    |                        |

|    | 16   | PA31 | GPIO 31 | ADC - AD[7]            | EIC - SCAN[1]  | PWM - PWM[6]    |                        |

|    | 6    | PB00 | GPIO 32 | TC - A0                | EIC - SCAN[2]  | USART2 - CTS    |                        |

|    | 7    | PB01 | GPIO 33 | TC - B0                | EIC - SCAN[3]  | USART2 - RTS    |                        |

|    | 24   | PB02 | GPIO 34 | EIC - EXTINT[6]        | TC - A1        | USART1 - TXD    |                        |

|    | 25   | PB03 | GPIO 35 | EIC - EXTINT[7]        | TC - B1        | USART1 - RXD    |                        |

|    | 26   | PB04 | GPIO 36 | USART1 - CTS           | SPI0 - NPCS[3] | TC - CLK2       |                        |

|    | 27   | PB05 | GPIO 37 | USART1 - RTS           | SPI0 - NPCS[2] | PWM - PWM[5]    |                        |

|    | 38   | PB06 | GPIO 38 | SSC - RX_CLOCK         | USART1 - DCD   | EIC - SCAN[4]   | ABDAC - DATA[0]        |

|    | 43   | PB07 | GPIO 39 | SSC - RX_DATA          | USART1 - DSR   | EIC - SCAN[5]   | ABDAC - DATAN[0]       |

|    | 54   | PB08 | GPIO 40 | SSC -<br>RX_FRAME_SYNC | USART1 - DTR   | EIC - SCAN[6]   | ABDAC - DATA[1]        |

|    |      |      |         |                        |                |                 |                        |

Table 4-1.

GPIO Controller Function Multiplexing

Table 4-1.

GPIO Controller Function Multiplexing

| 55 | PB09 | GPIO 41 | SSC - TX_CLOCK         | USART1 - RI | EIC - SCAN[7] | ABDAC - DATAN[1] |

|----|------|---------|------------------------|-------------|---------------|------------------|

| 57 | PB10 | GPIO 42 | SSC - TX_DATA          | TC - A2     | USART0 - RXD  |                  |

| 58 | PB11 | GPIO 43 | SSC -<br>TX_FRAME_SYNC | TC - B2     | USART0 - TXD  |                  |

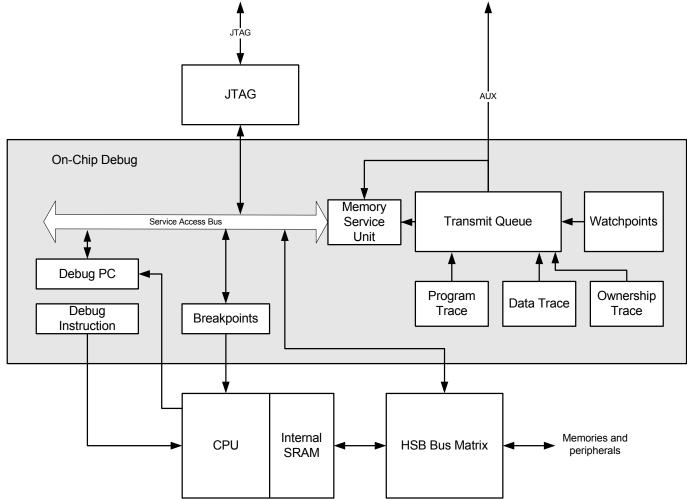

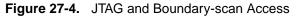

## 4.2.2 JTAG Port Connections

If the JTAG is enabled, the JTAG will take control over a number of pins, irrespective of the I/O Controller configuration.

| Table 4-2. | able 4-2. JTAG Pinoul |          |          |  |  |  |

|------------|-----------------------|----------|----------|--|--|--|

| 64QFP/QFN  | 48QFP/QFN             | Pin name | JTAG pin |  |  |  |

| 2          | 2                     | тск      | ТСК      |  |  |  |

| 3          | 3                     | PA00     | TDI      |  |  |  |

| 4          | 4                     | PA01     | TDO      |  |  |  |

| 5          | 5                     | PA02     | TMS      |  |  |  |

#### Table 4-2. JTAG Pinout

#### 4.2.3 Nexus OCD AUX port connections

If the OCD trace system is enabled, the trace system will take control over a number of pins, irrespectively of the PIO configuration. Two different OCD trace pin mappings are possible, depending on the configuration of the OCD AXS register. For details, see the AVR32 UC Technical Reference Manual.

| Table 4-5. | able 4-5. Nexus OCD AOX poil connectio |       |  |

|------------|----------------------------------------|-------|--|

| Pin        | AXS=0                                  | AXS=1 |  |

| EVTI_N     | PB05                                   | PA14  |  |

| MDO[5]     | PB04                                   | PA08  |  |

| MDO[4]     | PB03                                   | PA07  |  |

| MDO[3]     | PB02                                   | PA06  |  |

| MDO[2]     | PB01                                   | PA05  |  |

| MDO[1]     | PB00                                   | PA04  |  |

| MDO[0]     | PA31                                   | PA03  |  |

| EVTO_N     | PA15                                   | PA15  |  |

| МСКО       | PA30                                   | PA13  |  |

| MSEO[1]    | PB06                                   | PA09  |  |

| MSEO[0]    | PB07                                   | PA10  |  |

#### Table 4-3. Nexus OCD AUX port connections

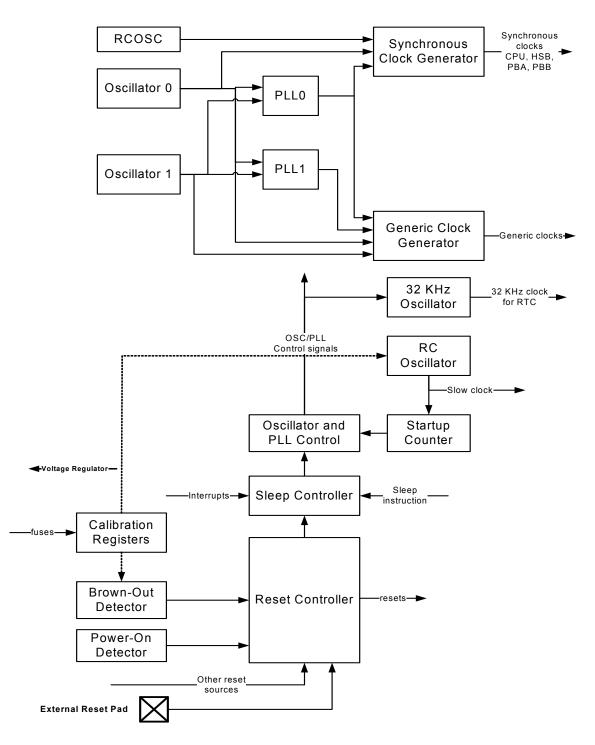

## 4.2.4 Oscillator Pinout

The oscillators are not mapped to the normal A, B or C functions and their muxings are controlled by registers in the Power Manager (PM). Please refer to the power manager chapter for more information about this.

Table 4-4.Oscillator pinout

| QFP48 pin | QFP64 pin | Pad  | Oscillator pin |

|-----------|-----------|------|----------------|

| 30        | 39        | PA18 | XIN0           |

|           | 41        | PA28 | XIN1           |

| 22        | 30        | PA11 | XIN32          |

| 31        | 40        | PA19 | XOUT0          |

|           | 42        | PA29 | XOUT1          |

| 23        | 31        | PA12 | XOUT32         |

# 4.3 High Drive Current GPIO

Ones of GPIOs can be used to drive twice current than other GPIO capability (see Electrical Characteristics section).

Table 4-5.High Drive Current GPIO

| GPIO Name |

|-----------|

| PA20      |

| PA21      |

| PA22      |

| PA23      |

# 5. Signals Description

The following table gives details on the signal name classified by peripheral.

Table 5-1.Signal Description List

| Signal Name | Function                       | Туре           | Active<br>Level | Comments        |  |

|-------------|--------------------------------|----------------|-----------------|-----------------|--|

| Power       |                                |                |                 |                 |  |

| VDDPLL      | PLL Power Supply               | Power<br>Input |                 | 1.65V to 1.95 V |  |

| VDDCORE     | Core Power Supply              | Power<br>Input |                 | 1.65V to 1.95 V |  |

| VDDIO       | I/O Power Supply               | Power<br>Input |                 | 3.0V to 3.6V    |  |

| VDDANA      | Analog Power Supply            | Power<br>Input |                 | 3.0V to 3.6V    |  |

| VDDIN       | Voltage Regulator Input Supply | Power<br>Input |                 | 3.0V to 3.6V    |  |

# Table 5-1. Signal Description List (Continued)

| Signal Name             | Function                      | Туре            | Active<br>Level | Comments        |

|-------------------------|-------------------------------|-----------------|-----------------|-----------------|

| VDDOUT                  | Voltage Regulator Output      | Power<br>Output |                 | 1.65V to 1.95 V |

| GNDANA                  | Analog Ground                 | Ground          |                 |                 |

| GND                     | Ground                        | Ground          |                 |                 |

|                         | Clocks, Oscillators,          | and PLL's       |                 |                 |

| XIN0, XIN1, XIN32       | Crystal 0, 1, 32 Input        | Analog          |                 |                 |

| XOUT0, XOUT1,<br>XOUT32 | Crystal 0, 1, 32 Output       | Analog          |                 |                 |

|                         | JTAG                          |                 |                 |                 |

| ТСК                     | Test Clock                    | Input           |                 |                 |

| TDI                     | Test Data In                  | Input           |                 |                 |

| TDO                     | Test Data Out                 | Output          |                 |                 |

| TMS                     | Test Mode Select              | Input           |                 |                 |

|                         | Auxiliary Port -              | AUX             |                 |                 |

| МСКО                    | Trace Data Output Clock       | Output          |                 |                 |

| MDO0 - MDO5             | Trace Data Output             | Output          |                 |                 |

| MSEO0 - MSEO1           | Trace Frame Control           | Output          |                 |                 |

| EVTI_N                  | Event In                      | Output          | Low             |                 |

| EVTO_N                  | Event Out                     | Output          | Low             |                 |

|                         | Power Manager                 | - PM            |                 |                 |

| GCLK0 - GCLK2           | Generic Clock Pins            | Output          |                 |                 |

| RESET_N                 | Reset Pin                     | Input           | Low             |                 |

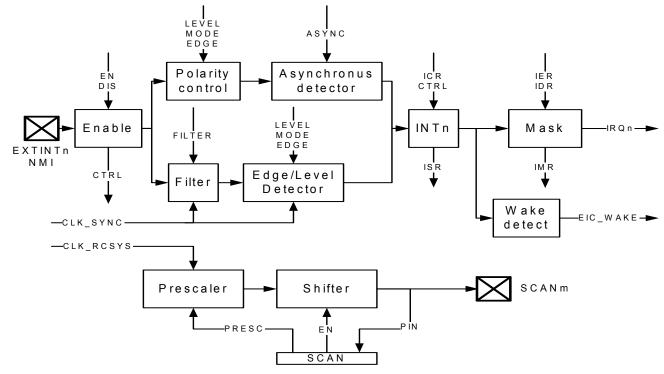

|                         | External Interrupt Con        | troller - EIC   |                 |                 |

| EXTINT0 - EXTINT7       | External Interrupt Pins       | Input           |                 |                 |

| KPS0 - KPS7             | Keypad Scan Pins              | Output          |                 |                 |

| NMI                     | Non-Maskable Interrupt Pin    | Input           | Low             |                 |

|                         | General Purpose I/O pin-      | GPIOA, GPI      | ОВ              |                 |

| PA0 - PA31              | Parallel I/O Controller GPIOA | I/O             |                 |                 |

| PB0 - PB11              | Parallel I/O Controller GPIOB | I/O             |                 |                 |

|                         |                               | 1               | 1               | L               |

Signal Description List (Continued) Table 5-1.

| Signal Name   | Function                                | Туре              | Active<br>Level | Comments       |

|---------------|-----------------------------------------|-------------------|-----------------|----------------|

|               | Serial Peripheral                       | Interface - SPI0  |                 | <u>.</u>       |

| MISO          | Master In Slave Out                     | I/O               |                 |                |

| MOSI          | Master Out Slave In                     | I/O               |                 |                |

| NPCS0 - NPCS3 | SPI Peripheral Chip Select              | I/O               | Low             |                |

| SCK           | Clock                                   | Output            |                 |                |

|               | Synchronous Seria                       | I Controller - SS | C               |                |

| RX_CLOCK      | SSC Receive Clock                       | I/O               |                 |                |

| RX_DATA       | SSC Receive Data                        | Input             |                 |                |

| RX_FRAME_SYNC | SSC Receive Frame Sync                  | I/O               |                 |                |

| TX_CLOCK      | SSC Transmit Clock                      | I/O               |                 |                |

| TX_DATA       | SSC Transmit Data                       | Output            |                 |                |

| TX_FRAME_SYNC | SSC Transmit Frame Sync                 | I/O               |                 |                |

|               | Timer/Count                             | er - TIMER        | I               |                |

| A0            | Channel 0 Line A                        | I/O               |                 |                |

| A1            | Channel 1 Line A                        | I/O               |                 |                |

| A2            | Channel 2 Line A                        | I/O               |                 |                |

| В0            | Channel 0 Line B                        | I/O               |                 |                |

| B1            | Channel 1 Line B                        | I/O               |                 |                |

| B2            | Channel 2 Line B                        | I/O               |                 |                |

| CLK0          | Channel 0 External Clock Input          | Input             |                 |                |

| CLK1          | Channel 1 External Clock Input          | Input             |                 |                |

| CLK2          | Channel 2 External Clock Input          | Input             |                 |                |

|               | Two-wire Inte                           | erface - TWI      |                 |                |

| SCL           | Serial Clock                            | I/O               |                 |                |

| SDA           | Serial Data                             | I/O               |                 |                |

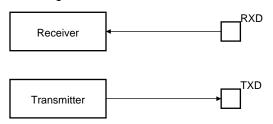

| Un            | iversal Synchronous Asynchronous Receiv | ver Transmitter - | USARTO, L       | ISART1, USART2 |

| CLK           | Clock                                   | I/O               |                 |                |

| CTS           | Clear To Send                           | Input             |                 |                |

| Table 5-1. | Signal Description List (Co | ontinued) |

|------------|-----------------------------|-----------|

|------------|-----------------------------|-----------|

| Signal Name     | Function                                          | Туре            | Active<br>Level | Comments    |

|-----------------|---------------------------------------------------|-----------------|-----------------|-------------|

| DCD             | Data Carrier Detect                               |                 |                 | Only USART1 |

| DSR             | Data Set Ready                                    |                 |                 | Only USART1 |

| DTR             | Data Terminal Ready                               |                 |                 | Only USART1 |

| RI              | Ring Indicator                                    |                 |                 | Only USART1 |

| RTS             | Request To Send                                   | Output          |                 |             |

| RXD             | Receive Data                                      | Input           |                 |             |

| ТХD             | Transmit Data                                     | Output          |                 |             |

|                 | Analog to Digital Con                             | verter - ADC    |                 |             |

| AD0 - AD7       | Analog input pins                                 | Analog<br>input |                 |             |

| ADVREF          | Analog positive reference voltage input           | Analog<br>input |                 | 2.6 to 3.6V |

|                 | Audio Bitstream DA                                | C - ABDAC       | I               |             |

| DATA0 - DATA1   | D/A Data out                                      | Output          |                 |             |

| DATAN0 - DATAN1 | D/A Data inverted out                             | Output          |                 |             |

|                 | Pulse Width Modula                                | ator - PWM      |                 |             |

| PWM0 - PWM6     | PWM Output Pins                                   | Output          |                 |             |

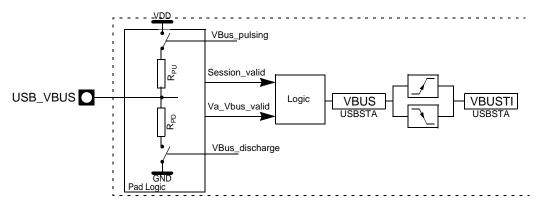

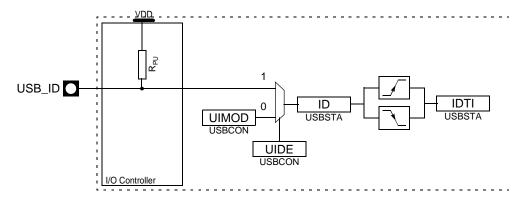

|                 | Universal Serial Bus D                            | evice - USBE    | 3               |             |

| DDM             | USB Device Port Data -                            | Analog          |                 |             |

| DDP             | USB Device Port Data +                            | Analog          |                 |             |

| VBUS            | USB VBUS Monitor and Embedded Host<br>Negociation | Analog<br>Input |                 |             |

| USBID           | ID Pin of the USB Bus                             | Input           |                 |             |

| USB_VBOF        | USB VBUS On/off: bus power control port           | output          |                 |             |

# 5.1 JTAG pins

TMS and TDI pins have pull-up resistors. TDO pin is an output, driven at up to VDDIO, and has no pull-up resistor. These 3 pins can be used as GPIO-pins. At reset state, these pins are in GPIO mode.

TCK pin cannot be used as GPIO pin. JTAG interface is enabled when TCK pin is tied low.

## 5.2 RESET\_N pin

The RESET\_N pin is a schmitt input and integrates a permanent pull-up resistor to VDDIO. As the product integrates a power-on reset cell, the RESET\_N pin can be left unconnected in case no reset from the system needs to be applied to the product.

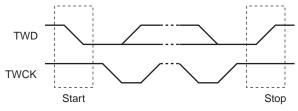

## 5.3 TWI pins

When these pins are used for TWI, the pins are open-drain outputs with slew-rate limitation and inputs with inputs with spike-filtering. When used as GPIO-pins or used for other peripherals, the pins have the same characteristics as GPIO pins.

## 5.4 GPIO pins

All the I/O lines integrate a pull-up resistor. Programming of this pull-up resistor is performed independently for each I/O line through the GPIO Controllers. After reset, I/O lines default as inputs with pull-up resistors disabled, except when indicated otherwise in the column "Reset Value" of the GPIO Controller user interface table.

## 5.5 High drive pins

The four pins PA20, PA21, PA22, PA23 have high drive output capabilities.

## 5.6 **Power Considerations**

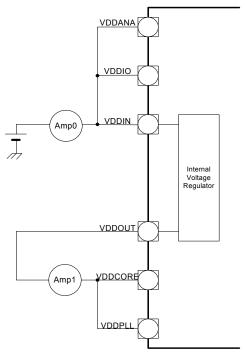

#### 5.6.1 Power Supplies

The AT32UC3B has several types of power supply pins:

- VDDIO: Powers I/O lines. Voltage is 3.3V nominal.

- VDDANA: Powers the ADC Voltage is 3.3V nominal.

- VDDIN: Input voltage for the voltage regulator. Voltage is 3.3V nominal.

- VDDCORE: Powers the core, memories, and peripherals. Voltage is 1.8V nominal.

- VDDPLL: Powers the PLL. Voltage is 1.8V nominal.

The ground pins GND are common to VDDCORE, VDDIO and VDDPLL. The ground pin for VDDANA is GNDANA.

For QFN packages, the center pad must be left unconnected.

Refer to "Electrical Characteristics" on page 617 for power consumption on the various supply pins.

The main requirement for power supplies connection is to respect a star topology for all electrical connection.

# AT32UC3B

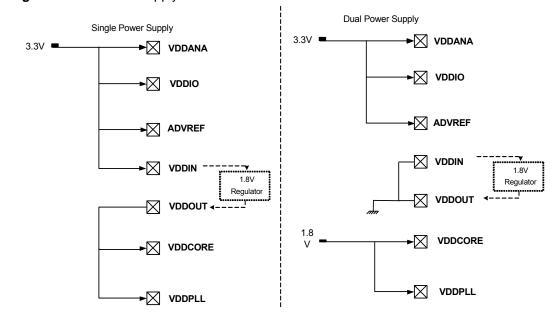

Figure 5-1. Power Supply

#### 5.6.2 Voltage Regulator

#### 5.6.2.1 Single Power Supply

The AT32UC3B embeds a voltage regulator that converts from 3.3V to 1.8V. The regulator takes its input voltage from VDDIN, and supplies the output voltage on VDDOUT that should be externally connected to the 1.8V domains.

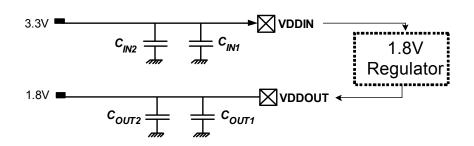

Adequate input supply decoupling is mandatory for VDDIN in order to improve startup stability and reduce source voltage drop. Two input decoupling capacitors must be placed close to the chip.

Adequate output supply decoupling is mandatory for VDDOUT to reduce ripple and avoid oscillations. The best way to achieve this is to use two capacitors in parallel between VDDOUT and GND as close to the chip as possible

Figure 5-2. Supply Decoupling

Refer to Section 28.3 on page 620 for decoupling capacitors values and regulator characteristics.

For decoupling recommendations for VDDIO, VDDANA, VDDCORE and VDDPLL, please refer to the Schematic checklist.

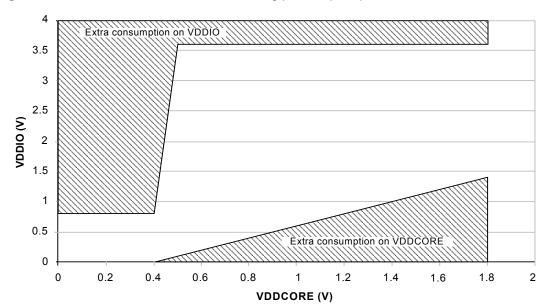

#### 5.6.2.2 Dual Power Supply

In case of dual power supply, VDDIN and VDDOUT should be connected to ground to prevent from leakage current.

To avoid over consumption during the power up sequence, VDDIO and VDDCORE voltage difference needs to stay in the range given Figure 5-3.

Figure 5-3. VDDIO versus VDDCORE during power up sequence

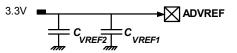

#### 5.6.3 Analog-to-Digital Converter (ADC) reference.

The ADC reference (ADVREF) must be provided from an external source. Two decoupling capacitors must be used to insure proper decoupling.

Figure 5-4. ADVREF Decoupling

Refer to Section 28.4 on page 620 for decoupling capacitors values and electrical characteristics.

In case ADC is not used, the ADVREF pin should be connected to GND to avoid extra consumption.

# 6. Processor and Architecture

Rev: 1.0.0.0

This chapter gives an overview of the AVR32UC CPU. AVR32UC is an implementation of the AVR32 architecture. A summary of the programming model, instruction set, and MPU is presented. For further details, see the *AVR32 Architecture Manual* and the *AVR32UC Technical Reference Manual*.

## 6.1 Features

- 32-bit load/store AVR32A RISC architecture

- 15 general-purpose 32-bit registers

- 32-bit Stack Pointer, Program Counter and Link Register reside in register file

- Fully orthogonal instruction set

- Privileged and unprivileged modes enabling efficient and secure Operating Systems

- Innovative instruction set together with variable instruction length ensuring industry leading code density

- DSP extention with saturating arithmetic, and a wide variety of multiply instructions

- 3-stage pipeline allows one instruction per clock cycle for most instructions

- Byte, halfword, word and double word memory access

- Multiple interrupt priority levels

- MPU allows for operating systems with memory protection

## 6.2 AVR32 Architecture

AVR32 is a high-performance 32-bit RISC microprocessor architecture, designed for cost-sensitive embedded applications, with particular emphasis on low power consumption and high code density. In addition, the instruction set architecture has been tuned to allow a variety of microarchitectures, enabling the AVR32 to be implemented as low-, mid-, or high-performance processors. AVR32 extends the AVR family into the world of 32- and 64-bit applications.

Through a quantitative approach, a large set of industry recognized benchmarks has been compiled and analyzed to achieve the best code density in its class. In addition to lowering the memory requirements, a compact code size also contributes to the core's low power characteristics. The processor supports byte and halfword data types without penalty in code size and performance.

Memory load and store operations are provided for byte, halfword, word, and double word data with automatic sign- or zero extension of halfword and byte data. The C-compiler is closely linked to the architecture and is able to exploit code optimization features, both for size and speed.

In order to reduce code size to a minimum, some instructions have multiple addressing modes. As an example, instructions with immediates often have a compact format with a smaller immediate, and an extended format with a larger immediate. In this way, the compiler is able to use the format giving the smallest code size.

Another feature of the instruction set is that frequently used instructions, like add, have a compact format with two operands as well as an extended format with three operands. The larger format increases performance, allowing an addition and a data move in the same instruction in a single cycle. Load and store instructions have several different formats in order to reduce code size and speed up execution.

The register file is organized as sixteen 32-bit registers and includes the Program Counter, the Link Register, and the Stack Pointer. In addition, register R12 is designed to hold return values from function calls and is used implicitly by some instructions.

## 6.3 The AVR32UC CPU

The AVR32UC CPU targets low- and medium-performance applications, and provides an advanced OCD system, no caches, and a Memory Protection Unit (MPU). Java acceleration hardware is not implemented.

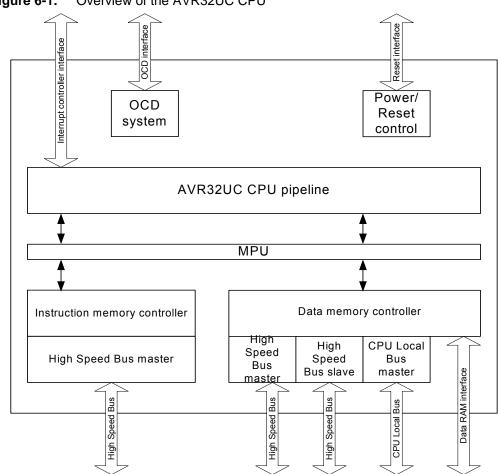

AVR32UC provides three memory interfaces, one High Speed Bus master for instruction fetch, one High Speed Bus master for data access, and one High Speed Bus slave interface allowing other bus masters to access data RAMs internal to the CPU. Keeping data RAMs internal to the CPU allows fast access to the RAMs, reduces latency, and guarantees deterministic timing. Also, power consumption is reduced by not needing a full High Speed Bus access for memory accesses. A dedicated data RAM interface is provided for communicating with the internal data RAMs.

A local bus interface is provided for connecting the CPU to device-specific high-speed systems, such as floating-point units and fast GPIO ports. This local bus has to be enabled by writing the LOCEN bit in the CPUCR system register. The local bus is able to transfer data between the CPU and the local bus slave in a single clock cycle. The local bus has a dedicated memory range allocated to it, and data transfers are performed using regular load and store instructions. Details on which devices that are mapped into the local bus space is given in the Memories chapter of this data sheet.

Figure 6-1 on page 19 displays the contents of AVR32UC.

Figure 6-1. Overview of the AVR32UC CPU

#### 6.3.1 Pipeline Overview

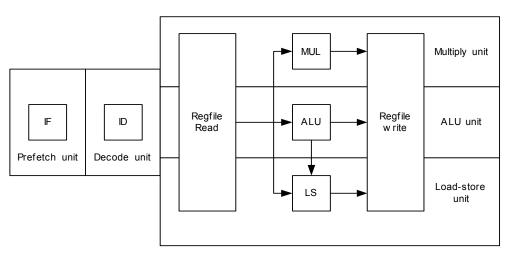

AVR32UC has three pipeline stages, Instruction Fetch (IF), Instruction Decode (ID), and Instruction Execute (EX). The EX stage is split into three parallel subsections, one arithmetic/logic (ALU) section, one multiply (MUL) section, and one load/store (LS) section.

Instructions are issued and complete in order. Certain operations require several clock cycles to complete, and in this case, the instruction resides in the ID and EX stages for the required number of clock cycles. Since there is only three pipeline stages, no internal data forwarding is required, and no data dependencies can arise in the pipeline.

Figure 6-2 on page 20 shows an overview of the AVR32UC pipeline stages.

#### Figure 6-2. The AVR32UC Pipeline

#### 6.3.2 AVR32A Microarchitecture Compliance

AVR32UC implements an AVR32A microarchitecture. The AVR32A microarchitecture is targeted at cost-sensitive, lower-end applications like smaller microcontrollers. This microarchitecture does not provide dedicated hardware registers for shadowing of register file registers in interrupt contexts. Additionally, it does not provide hardware registers for the return address registers and return status registers. Instead, all this information is stored on the system stack. This saves chip area at the expense of slower interrupt handling.

Upon interrupt initiation, registers R8-R12 are automatically pushed to the system stack. These registers are pushed regardless of the priority level of the pending interrupt. The return address and status register are also automatically pushed to stack. The interrupt handler can therefore use R8-R12 freely. Upon interrupt completion, the old R8-R12 registers and status register are restored, and execution continues at the return address stored popped from stack.

The stack is also used to store the status register and return address for exceptions and *scall*. Executing the *rete* or *rets* instruction at the completion of an exception or system call will pop this status register and continue execution at the popped return address.

#### 6.3.3 Java Support

AVR32UC does not provide Java hardware acceleration.

#### 6.3.4 Memory Protection

The MPU allows the user to check all memory accesses for privilege violations. If an access is attempted to an illegal memory address, the access is aborted and an exception is taken. The MPU in AVR32UC is specified in the AVR32UC Technical Reference manual.

#### 6.3.5 Unaligned Reference Handling

AVR32UC does not support unaligned accesses, except for doubleword accesses. AVR32UC is able to perform word-aligned *st.d* and *ld.d*. Any other unaligned memory access will cause an address exception. Doubleword-sized accesses with word-aligned pointers will automatically be performed as two word-sized accesses.

The following table shows the instructions with support for unaligned addresses. All other instructions require aligned addresses.

**Table 6-1.** Instructions with Unaligned Reference Support

| Instruction | Supported alignment |

|-------------|---------------------|

| ld.d        | Word                |

| st.d        | Word                |

#### 6.3.6 Unimplemented Instructions

The following instructions are unimplemented in AVR32UC, and will cause an Unimplemented Instruction Exception if executed:

- All SIMD instructions

- All coprocessor instructions if no coprocessors are present

- retj, incjosp, popjc, pushjc

- tlbr, tlbs, tlbw

- cache

#### 6.3.7 CPU and Architecture Revision

Three major revisions of the AVR32UC CPU currently exist.

The Architecture Revision field in the CONFIG0 system register identifies which architecture revision is implemented in a specific device.

AVR32UC CPU revision 3 is fully backward-compatible with revisions 1 and 2, ie. code compiled for revision 1 or 2 is binary-compatible with revision 3 CPUs.

# 6.4 Programming Model

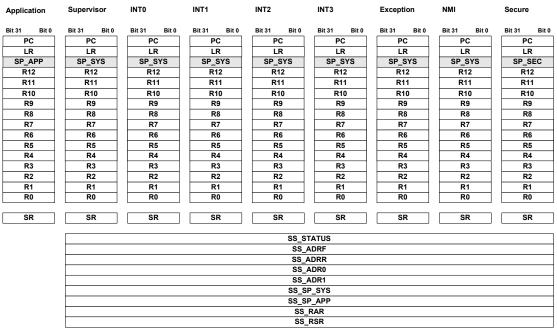

#### 6.4.1 Register File Configuration

The AVR32UC register file is shown below.

#### Figure 6-3. The AVR32UC Register File

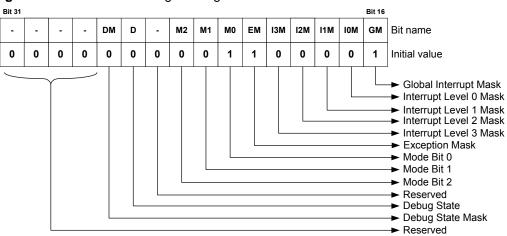

#### 6.4.2 Status Register Configuration

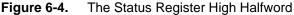

The Status Register (SR) is split into two halfwords, one upper and one lower, see Figure 6-4 on page 22 and Figure 6-5 on page 23. The lower word contains the C, Z, N, V, and Q condition code flags and the R, T, and L bits, while the upper halfword contains information about the mode and state the processor executes in. Refer to the *AVR32 Architecture Manual* for details.

Figure 6-5. The Status Register Low Halfword

#### 6.4.3 Processor States

#### 6.4.3.1 Normal RISC State

The AVR32 processor supports several different execution contexts as shown in Table 6-2 on page 23.

| Priority | Mode                   | Security     | Description                               |

|----------|------------------------|--------------|-------------------------------------------|

| 1        | Non Maskable Interrupt | Privileged   | Non Maskable high priority interrupt mode |

| 2        | Exception              | Privileged   | Execute exceptions                        |

| 3        | Interrupt 3            | Privileged   | General purpose interrupt mode            |

| 4        | Interrupt 2            | Privileged   | General purpose interrupt mode            |

| 5        | Interrupt 1            | Privileged   | General purpose interrupt mode            |

| 6        | Interrupt 0            | Privileged   | General purpose interrupt mode            |

| N/A      | Supervisor             | Privileged   | Runs supervisor calls                     |

| N/A      | Application            | Unprivileged | Normal program execution mode             |

Table 6-2.

Overview of Execution Modes, their Priorities and Privilege Levels.

Mode changes can be made under software control, or can be caused by external interrupts or exception processing. A mode can be interrupted by a higher priority mode, but never by one with lower priority. Nested exceptions can be supported with a minimal software overhead.

When running an operating system on the AVR32, user processes will typically execute in the application mode. The programs executed in this mode are restricted from executing certain instructions. Furthermore, most system registers together with the upper halfword of the status register cannot be accessed. Protected memory areas are also not available. All other operating modes are privileged and are collectively called System Modes. They have full access to all privileged and unprivileged resources. After a reset, the processor will be in supervisor mode.

#### 6.4.3.2 Debug State

The AVR32 can be set in a debug state, which allows implementation of software monitor routines that can read out and alter system information for use during application development. This implies that all system and application registers, including the status registers and program counters, are accessible in debug state. The privileged instructions are also available.

All interrupt levels are by default disabled when debug state is entered, but they can individually be switched on by the monitor routine by clearing the respective mask bit in the status register.

Debug state can be entered as described in the AVR32UC Technical Reference Manual.

Debug state is exited by the *retd* instruction.

#### 6.4.4 System Registers

The system registers are placed outside of the virtual memory space, and are only accessible using the privileged *mfsr* and *mtsr* instructions. The table below lists the system registers specified in the AVR32 architecture, some of which are unused in AVR32UC. The programmer is responsible for maintaining correct sequencing of any instructions following a *mtsr* instruction. For detail on the system registers, refer to the *AVR32UC Technical Reference Manual*.

| Table 6-3. | System Registers |          |                                        |  |

|------------|------------------|----------|----------------------------------------|--|

| Reg #      | Address          | Name     | Function                               |  |

| 0          | 0                | SR       | Status Register                        |  |

| 1          | 4                | EVBA     | Exception Vector Base Address          |  |

| 2          | 8                | ACBA     | Application Call Base Address          |  |

| 3          | 12               | CPUCR    | CPU Control Register                   |  |

| 4          | 16               | ECR      | Exception Cause Register               |  |

| 5          | 20               | RSR_SUP  | Unused in AVR32UC                      |  |

| 6          | 24               | RSR_INT0 | Unused in AVR32UC                      |  |

| 7          | 28               | RSR_INT1 | Unused in AVR32UC                      |  |

| 8          | 32               | RSR_INT2 | Unused in AVR32UC                      |  |

| 9          | 36               | RSR_INT3 | Unused in AVR32UC                      |  |

| 10         | 40               | RSR_EX   | Unused in AVR32UC                      |  |

| 11         | 44               | RSR_NMI  | Unused in AVR32UC                      |  |

| 12         | 48               | RSR_DBG  | Return Status Register for Debug mode  |  |

| 13         | 52               | RAR_SUP  | Unused in AVR32UC                      |  |

| 14         | 56               | RAR_INT0 | Unused in AVR32UC                      |  |

| 15         | 60               | RAR_INT1 | Unused in AVR32UC                      |  |

| 16         | 64               | RAR_INT2 | Unused in AVR32UC                      |  |

| 17         | 68               | RAR_INT3 | Unused in AVR32UC                      |  |

| 18         | 72               | RAR_EX   | Unused in AVR32UC                      |  |

| 19         | 76               | RAR_NMI  | Unused in AVR32UC                      |  |

| 20         | 80               | RAR_DBG  | Return Address Register for Debug mode |  |

| 21         | 84               | JECR     | Unused in AVR32UC                      |  |

| 22         | 88               | JOSP     | Unused in AVR32UC                      |  |

| 23         | 92               | JAVA_LV0 | Unused in AVR32UC                      |  |

| 24         | 96               | JAVA_LV1 | Unused in AVR32UC                      |  |

| 25         | 100              | JAVA_LV2 | Unused in AVR32UC                      |  |

Table 6-3.System Registers

| Table 6-3. | System Registers (Continued) |          |                                        |

|------------|------------------------------|----------|----------------------------------------|

| Reg #      | Address                      | Name     | Function                               |

| 26         | 104                          | JAVA_LV3 | Unused in AVR32UC                      |

| 27         | 108                          | JAVA_LV4 | Unused in AVR32UC                      |

| 28         | 112                          | JAVA_LV5 | Unused in AVR32UC                      |

| 29         | 116                          | JAVA_LV6 | Unused in AVR32UC                      |

| 30         | 120                          | JAVA_LV7 | Unused in AVR32UC                      |

| 31         | 124                          | JTBA     | Unused in AVR32UC                      |

| 32         | 128                          | JBCR     | Unused in AVR32UC                      |

| 33-63      | 132-252                      | Reserved | Reserved for future use                |

| 64         | 256                          | CONFIG0  | Configuration register 0               |

| 65         | 260                          | CONFIG1  | Configuration register 1               |

| 66         | 264                          | COUNT    | Cycle Counter register                 |

| 67         | 268                          | COMPARE  | Compare register                       |

| 68         | 272                          | TLBEHI   | Unused in AVR32UC                      |

| 69         | 276                          | TLBELO   | Unused in AVR32UC                      |

| 70         | 280                          | PTBR     | Unused in AVR32UC                      |

| 71         | 284                          | TLBEAR   | Unused in AVR32UC                      |

| 72         | 288                          | MMUCR    | Unused in AVR32UC                      |

| 73         | 292                          | TLBARLO  | Unused in AVR32UC                      |

| 74         | 296                          | TLBARHI  | Unused in AVR32UC                      |

| 75         | 300                          | PCCNT    | Unused in AVR32UC                      |

| 76         | 304                          | PCNT0    | Unused in AVR32UC                      |

| 77         | 308                          | PCNT1    | Unused in AVR32UC                      |

| 78         | 312                          | PCCR     | Unused in AVR32UC                      |

| 79         | 316                          | BEAR     | Bus Error Address Register             |

| 80         | 320                          | MPUAR0   | MPU Address Register region 0          |

| 81         | 324                          | MPUAR1   | MPU Address Register region 1          |

| 82         | 328                          | MPUAR2   | MPU Address Register region 2          |

| 83         | 332                          | MPUAR3   | MPU Address Register region 3          |

| 84         | 336                          | MPUAR4   | MPU Address Register region 4          |

| 85         | 340                          | MPUAR5   | MPU Address Register region 5          |

| 86         | 344                          | MPUAR6   | MPU Address Register region 6          |

| 87         | 348                          | MPUAR7   | MPU Address Register region 7          |

| 88         | 352                          | MPUPSR0  | MPU Privilege Select Register region 0 |

| 89         | 356                          | MPUPSR1  | MPU Privilege Select Register region 1 |

| 90         | 360                          | MPUPSR2  | MPU Privilege Select Register region 2 |

| 91         | 364                          | MPUPSR3  | MPU Privilege Select Register region 3 |

Table 6-3.

System Registers (Continued)

| Table 6-3. | System Ret | gisters (Continue | u)                                     |

|------------|------------|-------------------|----------------------------------------|

| Reg #      | Address    | Name              | Function                               |

| 92         | 368        | MPUPSR4           | MPU Privilege Select Register region 4 |

| 93         | 372        | MPUPSR5           | MPU Privilege Select Register region 5 |

| 94         | 376        | MPUPSR6           | MPU Privilege Select Register region 6 |

| 95         | 380        | MPUPSR7           | MPU Privilege Select Register region 7 |

| 96         | 384        | MPUCRA            | Unused in this version of AVR32UC      |

| 97         | 388        | MPUCRB            | Unused in this version of AVR32UC      |

| 98         | 392        | MPUBRA            | Unused in this version of AVR32UC      |

| 99         | 396        | MPUBRB            | Unused in this version of AVR32UC      |

| 100        | 400        | MPUAPRA           | MPU Access Permission Register A       |

| 101        | 404        | MPUAPRB           | MPU Access Permission Register B       |

| 102        | 408        | MPUCR             | MPU Control Register                   |

| 103-191    | 448-764    | Reserved          | Reserved for future use                |

| 192-255    | 768-1020   | IMPL              | IMPLEMENTATION DEFINED                 |

Table 6-3.

System Registers (Continued)

## 6.5 Exceptions and Interrupts

AVR32UC incorporates a powerful exception handling scheme. The different exception sources, like Illegal Op-code and external interrupt requests, have different priority levels, ensuring a well-defined behavior when multiple exceptions are received simultaneously. Additionally, pending exceptions of a higher priority class may preempt handling of ongoing exceptions of a lower priority class.

When an event occurs, the execution of the instruction stream is halted, and execution control is passed to an event handler at an address specified in Table 6-4 on page 29. Most of the handlers are placed sequentially in the code space starting at the address specified by EVBA, with four bytes between each handler. This gives ample space for a jump instruction to be placed there, jumping to the event routine itself. A few critical handlers have larger spacing between them, allowing the entire event routine to be placed directly at the address specified by the EVBA-relative offset generated by hardware. All external interrupt sources have autovectored interrupt service routine (ISR) addresses. This allows the interrupt controller to directly specify the ISR address as an address relative to EVBA. The autovector offset has 14 address bits, giving an offset of maximum 16384 bytes. The target address of the event handler is calculated as (EVBA | event\_handler\_offset), not (EVBA + event\_handler\_offset), so EVBA and exception code segments must be set up appropriately. The same mechanisms are used to service all different types of events, including external interrupt requests, yielding a uniform event handling scheme.

An interrupt controller does the priority handling of the external interrupts and provides the autovector offset to the CPU.

#### 6.5.1 System Stack Issues

Event handling in AVR32UC uses the system stack pointed to by the system stack pointer, SP\_SYS, for pushing and popping R8-R12, LR, status register, and return address. Since event code may be timing-critical, SP\_SYS should point to memory addresses in the IRAM section, since the timing of accesses to this memory section is both fast and deterministic.

The user must also make sure that the system stack is large enough so that any event is able to push the required registers to stack. If the system stack is full, and an event occurs, the system will enter an UNDEFINED state.

#### 6.5.2 Exceptions and Interrupt Requests

When an event other than *scall* or debug request is received by the core, the following actions are performed atomically:

- 1. The pending event will not be accepted if it is masked. The I3M, I2M, I1M, I0M, EM, and GM bits in the Status Register are used to mask different events. Not all events can be masked. A few critical events (NMI, Unrecoverable Exception, TLB Multiple Hit, and Bus Error) can not be masked. When an event is accepted, hardware automatically sets the mask bits corresponding to all sources with equal or lower priority. This inhibits acceptance of other events of the same or lower priority, except for the critical events listed above. Software may choose to clear some or all of these bits after saving the necessary state if other priority schemes are desired. It is the event source's responsability to ensure that their events are left pending until accepted by the CPU.

- 2. When a request is accepted, the Status Register and Program Counter of the current context is stored to the system stack. If the event is an INTO, INT1, INT2, or INT3, registers R8-R12 and LR are also automatically stored to stack. Storing the Status Register ensures that the core is returned to the previous execution mode when the current event handling is completed. When exceptions occur, both the EM and GM bits are set, and the application may manually enable nested exceptions if desired by clearing the appropriate bit. Each exception handler has a dedicated handler address, and this address uniquely identifies the exception source.

- 3. The Mode bits are set to reflect the priority of the accepted event, and the correct register file bank is selected. The address of the event handler, as shown in Table 6-4, is loaded into the Program Counter.

The execution of the event handler routine then continues from the effective address calculated.

The *rete* instruction signals the end of the event. When encountered, the Return Status Register and Return Address Register are popped from the system stack and restored to the Status Register and Program Counter. If the *rete* instruction returns from INT0, INT1, INT2, or INT3, registers R8-R12 and LR are also popped from the system stack. The restored Status Register contains information allowing the core to resume operation in the previous execution mode. This concludes the event handling.

#### 6.5.3 Supervisor Calls

The AVR32 instruction set provides a supervisor mode call instruction. The *scall* instruction is designed so that privileged routines can be called from any context. This facilitates sharing of code between different execution modes. The *scall* mechanism is designed so that a minimal execution cycle overhead is experienced when performing supervisor routine calls from time-critical event handlers.

The *scall* instruction behaves differently depending on which mode it is called from. The behaviour is detailed in the instruction set reference. In order to allow the *scall* routine to return to the correct context, a return from supervisor call instruction, *rets*, is implemented. In the AVR32UC CPU, *scall* and *rets* uses the system stack to store the return address and the status register.

#### 6.5.4 Debug Requests

The AVR32 architecture defines a dedicated Debug mode. When a debug request is received by the core, Debug mode is entered. Entry into Debug mode can be masked by the DM bit in the

status register. Upon entry into Debug mode, hardware sets the SR[D] bit and jumps to the Debug Exception handler. By default, Debug mode executes in the exception context, but with dedicated Return Address Register and Return Status Register. These dedicated registers remove the need for storing this data to the system stack, thereby improving debuggability. The mode bits in the status register can freely be manipulated in Debug mode, to observe registers in all contexts, while retaining full privileges.

Debug mode is exited by executing the *retd* instruction. This returns to the previous context.

#### 6.5.5 Entry Points for Events

Several different event handler entry points exists. In AVR32UC, the reset address is 0x8000\_0000. This places the reset address in the boot flash memory area.

TLB miss exceptions and *scall* have a dedicated space relative to EVBA where their event handler can be placed. This speeds up execution by removing the need for a jump instruction placed at the program address jumped to by the event hardware. All other exceptions have a dedicated event routine entry point located relative to EVBA. The handler routine address identifies the exception source directly.

AVR32UC uses the ITLB and DTLB protection exceptions to signal a MPU protection violation. ITLB and DTLB miss exceptions are used to signal that an access address did not map to any of the entries in the MPU. TLB multiple hit exception indicates that an access address did map to multiple TLB entries, signalling an error.

All external interrupt requests have entry points located at an offset relative to EVBA. This autovector offset is specified by an external Interrupt Controller. The programmer must make sure that none of the autovector offsets interfere with the placement of other code. The autovector offset has 14 address bits, giving an offset of maximum 16384 bytes.

Special considerations should be made when loading EVBA with a pointer. Due to security considerations, the event handlers should be located in non-writeable flash memory, or optionally in a privileged memory protection region if an MPU is present.

If several events occur on the same instruction, they are handled in a prioritized way. The priority ordering is presented in Table 6-4. If events occur on several instructions at different locations in the pipeline, the events on the oldest instruction are always handled before any events on any younger instruction, even if the younger instruction has events of higher priority than the oldest instruction. An instruction B is younger than an instruction A if it was sent down the pipeline later than A.

The addresses and priority of simultaneous events are shown in Table 6-4. Some of the exceptions are unused in AVR32UC since it has no MMU, coprocessor interface, or floating-point unit.

# AT32UC3B

| Priority | Handler Address        | Name                        | Event source   | Stored Return Address           |

|----------|------------------------|-----------------------------|----------------|---------------------------------|

| 1        | 0x8000_0000            | Reset                       | External input | Undefined                       |

| 2        | Provided by OCD system | OCD Stop CPU                | OCD system     | First non-completed instruction |

| 3        | EVBA+0x00              | Unrecoverable exception     | Internal       | PC of offending instruction     |

| 4        | EVBA+0x04              | TLB multiple hit            | MPU            |                                 |

| 5        | EVBA+0x08              | Bus error data fetch        | Data bus       | First non-completed instruction |

| 6        | EVBA+0x0C              | Bus error instruction fetch | Data bus       | First non-completed instruction |

| 7        | EVBA+0x10              | NMI                         | External input | First non-completed instruction |

| 8        | Autovectored           | Interrupt 3 request         | External input | First non-completed instruction |

| 9        | Autovectored           | Interrupt 2 request         | External input | First non-completed instruction |

| 10       | Autovectored           | Interrupt 1 request         | External input | First non-completed instruction |

| 11       | Autovectored           | Interrupt 0 request         | External input | First non-completed instruction |

| 12       | EVBA+0x14              | Instruction Address         | CPU            | PC of offending instruction     |

| 13       | EVBA+0x50              | ITLB Miss                   | MPU            |                                 |

| 14       | EVBA+0x18              | ITLB Protection             | MPU            | PC of offending instruction     |

| 15       | EVBA+0x1C              | Breakpoint                  | OCD system     | First non-completed instruction |

| 16       | EVBA+0x20              | Illegal Opcode              | Instruction    | PC of offending instruction     |

| 17       | EVBA+0x24              | Unimplemented instruction   | Instruction    | PC of offending instruction     |

| 18       | EVBA+0x28              | Privilege violation         | Instruction    | PC of offending instruction     |

| 19       | EVBA+0x2C              | Floating-point              | UNUSED         |                                 |

| 20       | EVBA+0x30              | Coprocessor absent          | Instruction    | PC of offending instruction     |

| 21       | EVBA+0x100             | Supervisor call             | Instruction    | PC(Supervisor Call) +2          |

| 22       | EVBA+0x34              | Data Address (Read)         | CPU            | PC of offending instruction     |

| 23       | EVBA+0x38              | Data Address (Write)        | CPU            | PC of offending instruction     |

| 24       | EVBA+0x60              | DTLB Miss (Read)            | MPU            |                                 |

| 25       | EVBA+0x70              | DTLB Miss (Write)           | MPU            |                                 |

| 26       | EVBA+0x3C              | DTLB Protection (Read)      | MPU            | PC of offending instruction     |

| 27       | EVBA+0x40              | DTLB Protection (Write)     | MPU            | PC of offending instruction     |

| 28       | EVBA+0x44              | DTLB Modified               | UNUSED         |                                 |

# Table 6-4. Priority and Handler Addresses for Events

# 6.6 Module Configuration

All AT32UC3B parts do not implement the same CPU and Architecture Revision.

| Part Name    | Architecture Revision |

|--------------|-----------------------|

| AT32UC3Bx512 | 2                     |

| AT32UC3Bx256 | 1                     |

| AT32UC3Bx128 | 1                     |

| AT32UC3Bx64  | 1                     |

Table 6-5.

CPU and Architecture Revision

# 7. Memories

# 7.1 Embedded Memories

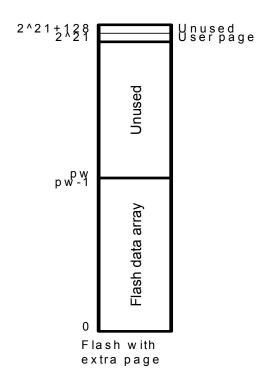

#### • Internal High-Speed Flash

- 512KBytes (AT32UC3B0512, AT32UC3B1512)

- 256 KBytes (AT32UC3B0256, AT32UC3B1256)

- 128 KBytes (AT32UC3B0128, AT32UC3B1128)

- 64 KBytes (AT32UC3B064, AT32UC3B164)

- - 0 Wait State Access at up to 30 MHz in Worst Case Conditions

- - 1 Wait State Access at up to 60 MHz in Worst Case Conditions

- - Pipelined Flash Architecture, allowing burst reads from sequential Flash locations, hiding penalty of 1 wait state access

- - 100 000 Write Cycles, 15-year Data Retention Capability

- - 4 ms Page Programming Time, 8 ms Chip Erase Time

- - Sector Lock Capabilities, Bootloader Protection, Security Bit

- - 32 Fuses, Erased During Chip Erase

- - User Page For Data To Be Preserved During Chip Erase

- Internal High-Speed SRAM, Single-cycle access at full speed

- 96KBytes ((AT32UC3B0512, AT32UC3B1512)

- 32KBytes (AT32UC3B0256, AT32UC3B0128, AT32UC3B1256 and AT32UC3B1128)

- 16KBytes (AT32UC3B064 and AT32UC3B164)

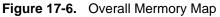

## 7.2 Physical Memory Map

The system bus is implemented as a bus matrix. All system bus addresses are fixed, and they are never remapped in any way, not even in boot. Note that AVR32 UC CPU uses unsegmented translation, as described in the AVR32UC Technical Architecture Manual. The 32-bit physical address space is mapped as follows:

| Table 7-1. | AT32UC3B Physical Memory Map |

|------------|------------------------------|

|------------|------------------------------|

| Device        |                              | Embedded<br>SRAM | Embedded<br>Flash | USB Data    | HSB-PB<br>Bridge A | HSB-PB<br>Bridge B |

|---------------|------------------------------|------------------|-------------------|-------------|--------------------|--------------------|

| Start Address |                              | 0x0000_0000      | 0x8000_0000       | 0xD000_0000 | 0xFFFF_0000        | 0xFFFE_0000        |

|               | AT32UC3B0512<br>AT32UC3B1512 | 96 Kbytes        | 512 Kbytes        | 64 Kbytes   | 64 Kbytes          | 64 Kbytes          |

| 0:=-          | AT32UC3B0256<br>AT32UC3B1256 | 32 Kbytes        | 256 Kbytes        | 64 Kbytes   | 64 Kbytes          | 64 Kbytes          |

| Size          | AT32UC3B0128<br>AT32UC3B1128 | 32 Kbytes        | 128 Kbytes        | 64 Kbytes   | 64 Kbytes          | 64 Kbytes          |

|               | AT32UC3B064<br>AT32UC3B164   | 16 Kbytes        | 64 Kbytes         | 64 Kbytes   | 64 Kbytes          | 64 Kbytes          |

# 7.3 Peripheral Address Map

# Table 7-2. Peripheral Address Mapping

|            | o mapping |                                                                     |

|------------|-----------|---------------------------------------------------------------------|

| Address    |           | Peripheral Name                                                     |

| 0xFFFE0000 | USB       | USB 2.0 Interface - USB                                             |

| 0xFFFE1000 | HMATRIX   | HSB Matrix - HMATRIX                                                |

| 0xFFFE1400 | HFLASHC   | Flash Controller - HFLASHC                                          |

| 0xFFFF0000 | PDCA      | Peripheral DMA Controller - PDCA                                    |

| 0xFFFF0800 | INTC      | Interrupt controller - INTC                                         |

| 0xFFFF0C00 | РМ        | Power Manager - PM                                                  |

| 0xFFFF0D00 | RTC       | Real Time Counter - RTC                                             |

| 0xFFFF0D30 | WDT       | Watchdog Timer - WDT                                                |

| 0xFFFF0D80 | EIM       | External Interrupt Controller - EIM                                 |

| 0xFFFF1000 | GPIO      | General Purpose Input/Output Controller - GPIO                      |

| 0xFFFF1400 | USART0    | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART0 |

| 0xFFFF1800 | USART1    | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART1 |

| 0xFFFF1C00 | USART2    | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART2 |

| 0xFFFF2400 | SPI0      | Serial Peripheral Interface - SPI0                                  |

| 0xFFFF2C00 | TWI       | Two-wire Interface - TWI                                            |

| 0xFFFF3000 | PWM       | Pulse Width Modulation Controller - PWM                             |

| 0xFFFF3400 | SSC       | Synchronous Serial Controller - SSC                                 |

| 0xFFFF3800 | тс        | Timer/Counter - TC                                                  |

|            |           |                                                                     |

Table 7-2.

Peripheral Address Mapping

| 0xFFFF3C00 | ADC   | Analog to Digital Converter - ADC |

|------------|-------|-----------------------------------|

| 0xFFFF4000 | ABDAC | Audio Bitstream DAC - ABDAC       |

# 7.4 CPU Local Bus Mapping

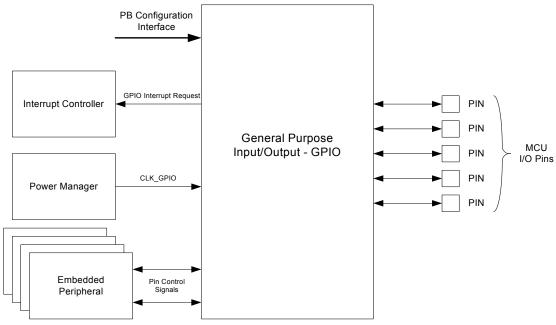

Some of the registers in the GPIO module are mapped onto the CPU local bus, in addition to being mapped on the Peripheral Bus. These registers can therefore be reached both by accesses on the Peripheral Bus, and by accesses on the local bus.

Mapping these registers on the local bus allows cycle-deterministic toggling of GPIO pins since the CPU and GPIO are the only modules connected to this bus. Also, since the local bus runs at CPU speed, one write or read operation can be performed per clock cycle to the local busmapped GPIO registers.

The following GPIO registers are mapped on the local bus:

| Port | Register                             | Mode   | Local Bus<br>Address | Access     |

|------|--------------------------------------|--------|----------------------|------------|

| 0    | Output Driver Enable Register (ODER) | WRITE  | 0x4000_0040          | Write-only |

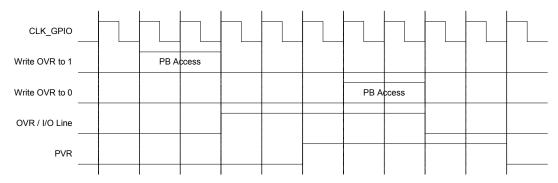

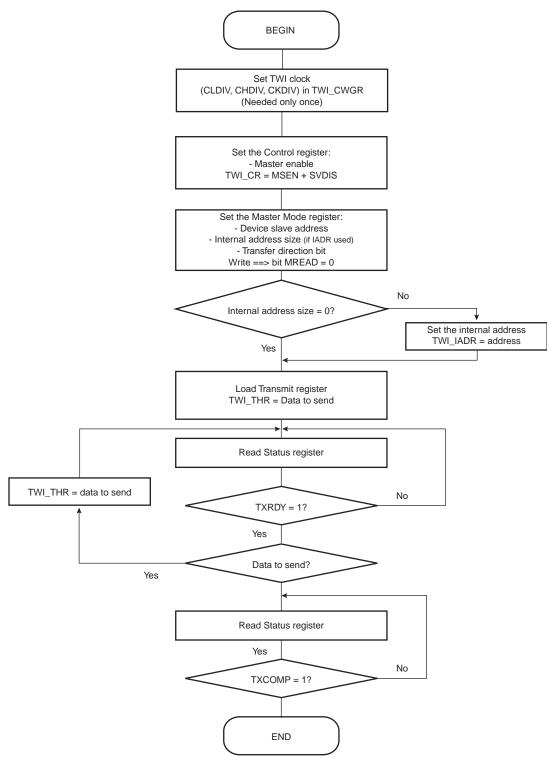

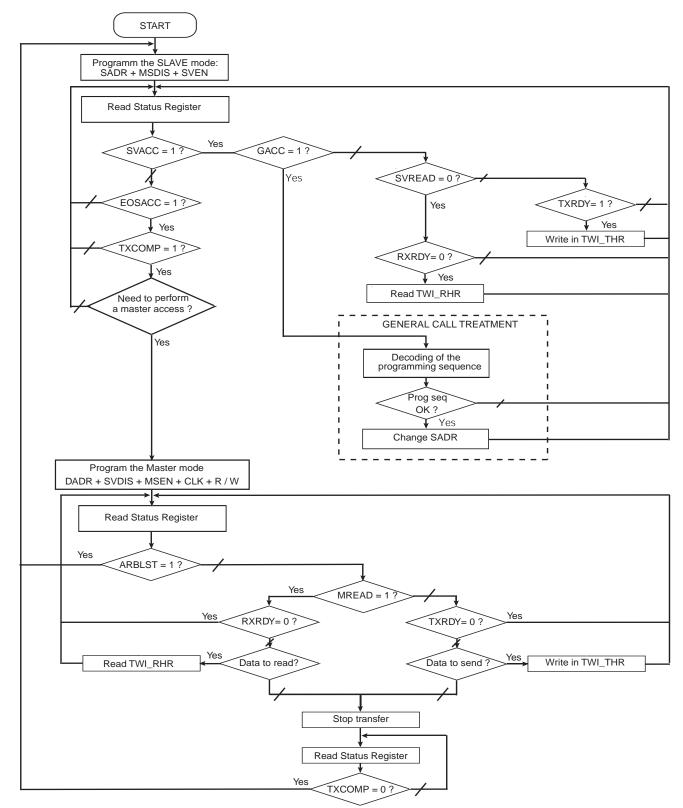

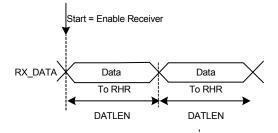

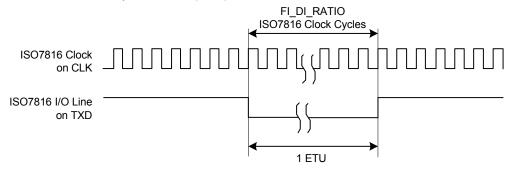

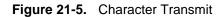

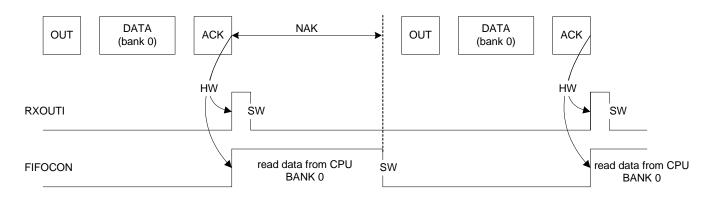

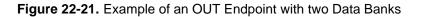

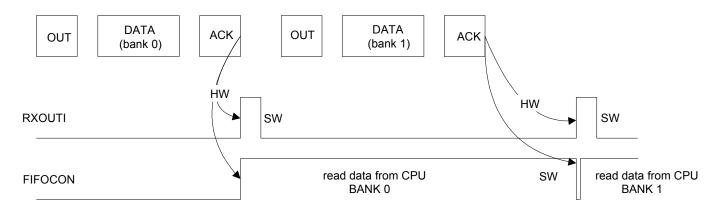

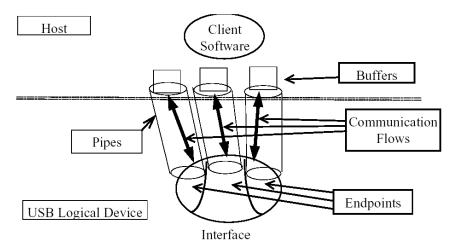

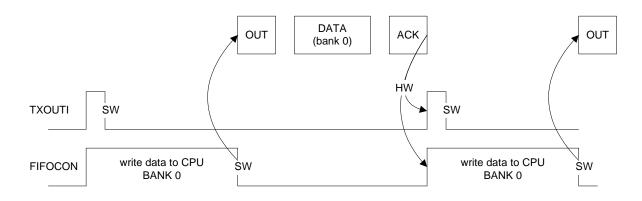

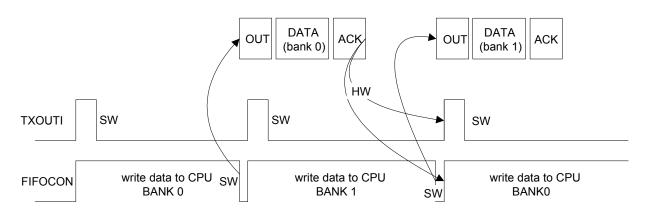

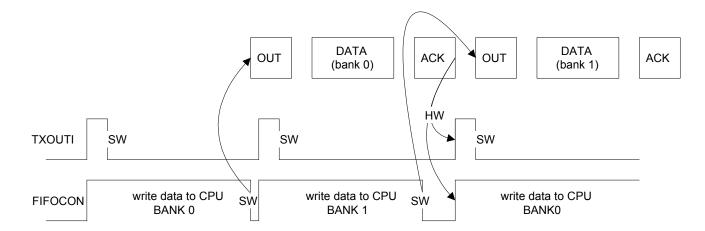

|      |                                      | SET    | 0x4000_0044          | Write-only |