# MCF51JM128 32-bit ColdFire® USB microcontroller

### **Target Applications**

- HVAC building and control systems

- Test and measurement equipment

- Environmental and building automation

- Security and access control panels

- Stationary barcode scanners and barcode printers

- PC peripherals and I/O modules

- Patient monitoring systems

- Laboratory equipment

- Industrial networking products

- Hospital beds and electric wheel chairs

### Overview

The MCF51JM128 is part of the Freescale Flexis<sup>™</sup> microcontroller series, the connection point on the Freescale Controller Continuum where 8-bit and 32-bit compatibility becomes a reality. The Flexis series of devices includes complementary families of 8-bit S08 and 32-bit V1 ColdFire<sup>®</sup> microcontrollers that have a common set of peripherals and development tools to deliver the ultimate in migration flexibility.

The 32-bit MCF51JM128 device further extends the low-end of the ColdFire embedded USB controller family with up to 128 KB of flash memory, a full-speed USB 2.0 controller with host, device and On-The-Go (OTG) support, an integrated CAN module and a 12-channel, 12-bit analog-to-digital converter. The ColdFire JM family also features a hardware cryptographic acceleration unit (CAU), a random number generator accelerator (RNGA) and several system protection features such as low voltage detect and a Computer Operating Properly (COP) module.

The JM128 devices, like the other USB microcontrollers in the Controller Continuum, are supported by the Freescale USB-LITE Stack by CMX. This complimentary\*\*\* USB stack provides support for certain HID, CDC and mass storage classes. Source code for the complimentary stack is available. The MCF51JM128 is software compatible with other devices in the Controller Continuum, providing a direct migration path to higher performing USB microcontrollers.

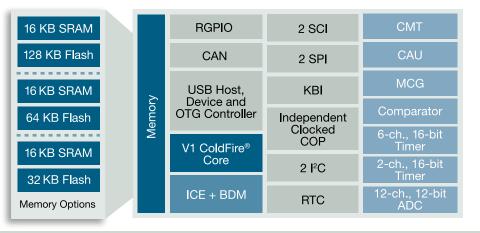

## MCF51JM128 Top-Level Block Diagram

| Features                                                                                                                    | Benefits                                                                                                                                                                                                                  |  |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 32-bit V1 ColdFire <sup>®</sup> Central Processing Unit (CPU)                                                               |                                                                                                                                                                                                                           |  |

| <ul> <li>Up to 50.33 MHz V1 ColdFire core offering 2.7 to 5.5V<br/>across a temperature range of -40°C to +105°C</li> </ul> | Offers strong performance throughout the entire<br>voltage range                                                                                                                                                          |  |

| ColdFire Instruction Set Revision C (ISA_C)                                                                                 | <ul> <li>Provides additional instructions for easy handling<br/>of 8-, 16- and 32-bit data</li> </ul>                                                                                                                     |  |

| Support for up to 30 peripheral interrupt requests     and seven software interrupts                                        | <ul> <li>Allows for exceptional software flexibility and<br/>optimization for real-time applications</li> </ul>                                                                                                           |  |

| On-Chip Memory                                                                                                              |                                                                                                                                                                                                                           |  |

| <ul> <li>Up to 128K flash read/program/erase over full<br/>operating voltage and temperature</li> </ul>                     | <ul> <li>Allows user to take full advantage of in-application,<br/>re-programmability benefits in virtually any environment</li> </ul>                                                                                    |  |

| Up to 16K RAM with security circuit                                                                                         | Helps prevent unauthorized access to RAM                                                                                                                                                                                  |  |

|                                                                                                                             | <ul> <li>Flash contents helps to reduce system power consumption</li> </ul>                                                                                                                                               |  |

| Power-Saving Modes                                                                                                          |                                                                                                                                                                                                                           |  |

| Four low-power modes                                                                                                        | <ul> <li>Allows continuation of sampling application in a reduced<br/>power state which helps to reduces system power consumption</li> </ul>                                                                              |  |

| Multi-purpose clock generator (MCG)                                                                                         | <ul> <li>Frequency-locked loop (FLL): Internal or external<br/>reference can be used to control the FLL</li> </ul>                                                                                                        |  |

|                                                                                                                             | <ul> <li>Phase-locked loop (PLL): Voltage controlled oscillator<br/>(VCO). Modulo VCO frequency divider. Lock detector<br/>with interrupt capability.</li> </ul>                                                          |  |

|                                                                                                                             | Internal reference clock: Can be selected as the clock<br>source for the MCU                                                                                                                                              |  |

|                                                                                                                             | • External reference clock: Provides control for a separate crystal oscillator. Clock monitor with reset capability. Can be selected as the clock source for the MCU.                                                     |  |

|                                                                                                                             | Reference divider provided                                                                                                                                                                                                |  |

|                                                                                                                             | <ul> <li>Clock source can be divided by 1, 2, 4 or 8</li> </ul>                                                                                                                                                           |  |

| Peripherals                                                                                                                 |                                                                                                                                                                                                                           |  |

| <ul> <li>Dual-role USB On-The-Go (OTG) device, supports<br/>USB in either device, host or OTG configuration</li> </ul>      | <ul> <li>On-chip transceiver and 3.3V regualtor help save system<br/>cost, fully compliant with USB Specification 2.0. Allows<br/>control, bulk, interrupt and isochronous transfers</li> </ul>                           |  |

| Controller Area Network (CAN)                                                                                               | <ul> <li>Implementation of the CAN protocol – Version 2.0A/B.<br/>Five receive buffers with FIFO storage scheme. Three<br/>transmit buffers with internal prioritization using a<br/>"local priority" concept.</li> </ul> |  |

| <ul> <li>Two serial communications interface (SCI)<br/>modules offering asynchronous communications</li> </ul>              | <ul> <li>Provides standard UART communications peripheral</li> <li>Allows full-duplex, asynchronous, NRZ serial communication between MCU and remote devices</li> </ul>                                                   |  |

| Features                                                                                                                                                                                                                                                       | Benefits                                                                                                                                                                                                                                                                                                         |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Peripherals (continued)                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                  |  |

| Cryptographic acceleration unit (CAU)                                                                                                                                                                                                                          | Supports DES, 3DES, AES, MD5 and SHA-1 cryptographic algorithms                                                                                                                                                                                                                                                  |  |

| Random number generator accelerator (RNGA)                                                                                                                                                                                                                     | <ul> <li>Generates 32-bit random numbers</li> <li>Complies with FIPS-140 standards for randomness<br/>and non-determinism</li> </ul>                                                                                                                                                                             |  |

| <ul> <li>Analog comparators (ACMP)—One analog<br/>comparator with the option to compare to internal<br/>reference, output can be optionally routed to<br/>timer/pulse width modulation (TPM) as input<br/>capture trigger</li> </ul>                           | Requires only single pin for input signal, freeing up<br>other pin for other use<br>Allows other system components to see comparator<br>result with minimal delay<br>Can be used for single slope ADC and RC time<br>constant measurements                                                                       |  |

| <ul> <li>Analog-to-digital converter (ADC) – 12-channel,<br/>12-bit resolution</li> </ul>                                                                                                                                                                      | <ul> <li>Output formatted in 12-, 10- or 8-bit right-justified format</li> <li>Single or continuous conversion</li> <li>Operation in low power modes for lower noise operation</li> <li>Asynchronous clock source for lower noise operation</li> </ul>                                                           |  |

| <ul> <li>Two I<sup>2</sup>Cs with up to 100 kbps with maximum bus<br/>loading; multi-master operation; programmable slave<br/>address; interrupt driven byte-by-byte data transfer;<br/>supports broadcast mode and 10-bit addressing</li> </ul>               | <ul> <li>Two I<sup>2</sup>C ports enable increased system memory by using an additional I<sup>2</sup>C EEPROM</li> <li>Ability to add an additional I<sup>2</sup>C device</li> </ul>                                                                                                                             |  |

| <ul> <li>SPI—Two serial peripheral interfaces<br/>with full-duplex or single-wire bidirectional;<br/>double-buffered transmit and receive; master<br/>or slave mode; MSB-first or LSB-first shifting</li> <li>SPI2 has 8 byte receive/transmit FIFO</li> </ul> | <ul> <li>Having two SPI allows two separate dedicated<br/>devices, for example, one SPI dedicated to a ZigBee<sup>®</sup><br/>transceiver, and the other to MCUs or peripherals</li> <li>Supports high-speed transmission minimizing<br/>CPU interrupts</li> </ul>                                               |  |

| Carrier modulator timer (CMT)                                                                                                                                                                                                                                  | <ul> <li>Offers four modes of operation:</li> <li>Time with independent control of high and low times</li> <li>Baseband</li> <li>Frequency shift key</li> <li>Direct software control of IRO pin</li> <li>Selectable input clock divide: 1, 2, 4 or 8</li> </ul>                                                 |  |

| <ul> <li>TPM—Two timer modules with up to eight<br/>channels and 16-bit resolution</li> </ul>                                                                                                                                                                  | <ul> <li>Each channel may be input capture, output compare or edge-aligned PWM</li> <li>Input capture trigger on either rising or falling edge</li> <li>Selectable polarity on PWM outputs</li> <li>Timer clock source selectable as prescaled bus clock, fixed system clock or an external clock pin</li> </ul> |  |

| Input/Output                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                  |  |

| <ul> <li>16-bits of rapid general purpose<br/>input output (RGPIO)</li> </ul>                                                                                                                                                                                  | <ul> <li>Memory mapped I/O connected to core's local bus for<br/>fast toggle rates</li> <li>Support for all access sizes</li> </ul>                                                                                                                                                                              |  |

| Up to 8 keyboard interrupt (KBI) pins with<br>selectable polarity                                                                                                                                                                                              | <ul> <li>Each KBI pin is programmable as falling edge only,<br/>rising edge only, falling edge and low level or rising<br/>edge and high level interrupt sensitivity</li> </ul>                                                                                                                                  |  |

| <ul> <li>66 GPIOs and one input-only and one<br/>output-only pin</li> </ul>                                                                                                                                                                                    | Results in a large number of flexible I/O pins that allow<br>vendors to easily interface the device into their own designs                                                                                                                                                                                       |  |

| System Protection                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                  |  |

| <ul> <li>Watchdog computer operating properly (COP)<br/>reset with option to run from dedicated 1 kHz<br/>internal clock source or bus clock</li> </ul>                                                                                                        | <ul> <li>Allows the device to recognize run-away code<br/>(infinite loops) and resets the processor to help<br/>avoid lock-up states</li> </ul>                                                                                                                                                                  |  |

| <ul> <li>Low-voltage detection with reset or interrupt;<br/>selectable trip points</li> </ul>                                                                                                                                                                  | Alerts the developer to voltage drops outside of the<br>typical operating range                                                                                                                                                                                                                                  |  |

| Illegal op code detection with reset                                                                                                                                                                                                                           | <ul> <li>Allows the device to recognize erroneous code and<br/>resets the processor to help avoid lock-up states</li> </ul>                                                                                                                                                                                      |  |

| Flash block protection                                                                                                                                                                                                                                         | <ul> <li>Helps to prevent unauthorized access to flash RAM<br/>which greatly reduces the chance of losing vital system<br/>code for vendor applications</li> </ul>                                                                                                                                               |  |

| Hardware Development Support                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                  |  |

| <ul> <li>Classic ColdFire debug B+ functionality mapped<br/>into a single-pin BDM interface</li> </ul>                                                                                                                                                         | <ul> <li>Allows developers to use the same hardware cables<br/>between S08 and V1 ColdFire platforms</li> </ul>                                                                                                                                                                                                  |  |

| Real-time debug support                                                                                                                                                                                                                                        | <ul> <li>Six hardware breakpoints which can be configured into<br/>a 1- or 2-level trigger with a programmable response<br/>(CPU halt or interrupt)</li> </ul>                                                                                                                                                   |  |

| Program trace support                                                                                                                                                                                                                                          | <ul> <li>Capture of processor status and debug data into<br/>on-chip trace buffer provides program trace capabilities<br/>and programmable start/stop recording conditions</li> </ul>                                                                                                                            |  |

| Package Options |                  |             |

|-----------------|------------------|-------------|

| Part Number     | Temp. Range      | Package     |

| MCF51JM128EVLK* | -40°C to +105°C  | 80-pin LQFP |

| MCF51JM128VLK   | -40°C to +105°C  | 80-pin LQFP |

| MCF51JM128VQH   | -40°C to +105°C  | 64-pin QFP  |

| MCF51JM128VLH   | -40°C to +105°C  | 64-pin LQFP |

| MCF51JM128VLD   | -40°C to +105°C  | 44-pin LQFP |

| MCF51JM64EVLK*  | -40°C to +105°C  | 80-pin LQFP |

| MCF51JM64VLK    | -40°C to +105°C  | 80-pin LQFP |

| MCF51JM64VQH    | -40°C to +105°C  | 64-pin QFP  |

| MCF51JM64VLH    | -40°C to +105°C  | 64-pin LQFP |

| MCF51JM64VLD    | -40°C to +105°C  | 44-pin LQFP |

| MCF51JM32EVLK*  | -40°C to + 105°C | 80-pin LQFP |

| MCF51JM32VLK    | -40°C to + 105°C | 80-pin LQFP |

| MCF51JM32VQH    | -40°C to + 105°C | 64-pin QFP  |

| MCF51JM32VLH    | -40°C to + 105°C | 64-pin LQFP |

| MCF51JM32VLD    | -40°C to + 105°C | 44-pin LQFP |

# Cost-Effective Development Tools DEMOJM \$99 USD\*\*

Cost-effective demonstration kit featuring the ColdFire JM128 and the S08 JM60 daughter cards. Support for USB (host and device) and CAN. Built-in USB-BDM circuitry available for debugging and programming. USB-BDM circuitry includes serial communication and simple logic analyzer.

#### EVB51JM128 \$325 USD\*\*

Full-featured evaluation system for the ColdFire JM128 Flexis USB family. This evaluation system supports USB host, device and OTG as well as integrated CAN.

### CodeWarrior<sup>™</sup> Development Studio for Microcontrollers 6.1 Complimentary\*\*\*

CodeWarrior Development Studio for Microcontrollers is an integrated tool suite that supports software development for Freescale's 8-bit or 32-bit microcontrollers. Designers can further accelerate application development with the help of the Processor Expert<sup>™</sup> tool, which is an award-winning rapid application development tool in the CodeWarrior tool suite.

### Freescale USB-LITE Stack by CMX Complimentary\*\*\*

Freescale is providing a comprehensive USB software solution through a complimentary USB stack. Freescale USB-LITE stack by CMX enables USB host and device modes of operation. The USB stack supports several HID and CDC to UART projects. The complimentary stack also interfaces with CodeWarrior Development Studio, providing a productive, comprehensive development environment for designing embedded applications.

\* The device with CAU \*\* Prices indicated are MSRP

Learn More:

\*\*\* Subject to license agreement

Subject to license agreeme

For more information about the Flexis JM family, please visit **www.freescale.com/flexis**.

Freescale, the Freescale logo, ColdFire, CodeWarrior, Flexis and Processer Expert are trademarks or registered trademarks of Freescale Semiconductor, Inc. in the U.S. and other countries. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2008 freescale semiconductor

Document Number: MCF51JM128FS / REV 1