### MC9S08QE32/16

## Taking the lead in low power

### **Target Applications**

- · Low-power wireless applications

- · Gas, water and heater meters

- · HVAC and building control

- Security systems including sensors and home alarm

- · Personal health care devices

- · Cell phone accessories

- · Commercial smoke detectors

- Toys

#### Overview

Achieving raw performance is no longer the number one issue—it's now "performance within an energy budget." Freescale understands this challenge and offers a wide portfolio of S08 devices that help you reach target performance levels while minimizing low power in your design. The QE family demonstrates extreme energy efficiency for ultra-long operating life in battery-powered applications.

Further expanding the QE family portfolio, the QE32 provides great flexibility for customers to balance performance and power consumption.

The QE32 offers low-power features such as two ultra-low-power stop modes, low-power run and wait modes, 6 usec wake-up time, ultra-low-power external oscillator and clock gating registers to disable clocks to unused peripherals.

The QE32 offers up to 32 KB of flash memory, a 10-channel, 12-bit resolution analog-to-digital converter (ADC), abundant peripherals such as three timers/PWM, two SCI, SPI, I<sup>2</sup>C and two analog comparators. QE32 can operate at 1.8V voltage supply and run up to 50.33 MHz core frequency.

To test your application with the QE family, take the Battery Calculator challenge, available at www.freescale.com/lowpower.

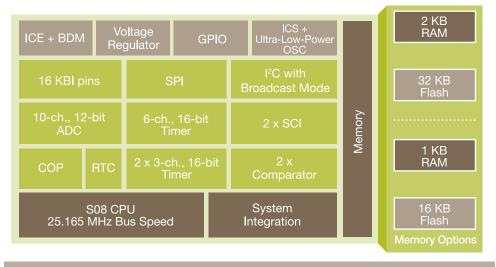

### SO8QE32/16 Block Diagram

| Features                                                                                                                                                                              | Benefits                                                                                                                                  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| Power-Saving Features                                                                                                                                                                 |                                                                                                                                           |  |

| <ul> <li>Two ultra-low-power stop modes, one of which<br/>allows limited use of peripherals</li> </ul>                                                                                | Allows continued application sampling in a reduced<br>power state which extends battery life                                              |  |

| <ul> <li>Low-power run and wait modes</li> </ul>                                                                                                                                      | <ul><li>Allows use of all chip peripherals in a low-power state</li><li>Enables faster execution out of stop modes</li></ul>              |  |

| <ul> <li>6 µs typical wake up time from stop mode</li> </ul>                                                                                                                          |                                                                                                                                           |  |

| <ul> <li>Internal clock Source (ICS)—module containing a<br/>frequency locked-loop (FLL) controlled by internal<br/>or external reference</li> </ul>                                  | Provides choice of frequencies on-the-fly.<br>Reducing frequency saves current.                                                           |  |

| <ul> <li>Oscillator (OSC)—loop-control Pierce oscillator;<br/>crystal or ceramic resonator range of 31.25 kHz to<br/>38.4 kHz or 1 MHz to 16 MHz</li> </ul>                           | Includes ultra-low-power OSC for accurate<br>timebase in low-power modes                                                                  |  |

| Clock gating disables clocks to unused peripherals                                                                                                                                    | <ul><li>Provides flexibility to turn off individual modules</li><li>Reduces power consumption</li></ul>                                   |  |

| 8-bit HCS08 Central Processing Unit (CPU)                                                                                                                                             |                                                                                                                                           |  |

| <ul> <li>Up to 50.33 MHz HCS08 CPU at 3.6V to 2.4V,<br/>40 MHz CPU at 2.4 V to 2.1 V and 20 MHz CPU<br/>at 2.1 V to 1.8 V across temperature range of<br/>-40 °C to +85 °C</li> </ul> | Offers high performance, even at low voltage levels<br>for battery-operated applications                                                  |  |

|                                                                                                                                                                                       | <ul> <li>Provides bus speed operation from 10 MHz to<br/>25.165 MHz under voltage from 1.8V to 3.6V</li> </ul>                            |  |

| HCS08 instruction set with added BGND instruction                                                                                                                                     | <ul> <li>Easy to learn and use architecture</li> </ul>                                                                                    |  |

|                                                                                                                                                                                       | <ul> <li>Backward object code compatibility with 68HC08 and<br/>68HC05 for reuse of existing libraries can still be used</li> </ul>       |  |

|                                                                                                                                                                                       | <ul> <li>Allows for efficient, compact module coding in<br/>assembly or C compiler</li> </ul>                                             |  |

|                                                                                                                                                                                       | <ul> <li>BGND allows user to enter background debug<br/>mode that takes advantage of on-chip<br/>in-circuit emulator (ICE)</li> </ul>     |  |

| On-Chip Memory                                                                                                                                                                        |                                                                                                                                           |  |

| Up to 32 KB flash read/program/erase over full<br>operating voltage and temperature                                                                                                   | <ul> <li>Allows user to take full advantage of<br/>in-application, reprogrammability benefits in<br/>virtually any environment</li> </ul> |  |

| Up to range of 1.8V to 3.6V RAM                                                                                                                                                       | Security circuitry prevents unauthorized access<br>to RAM and flash contents to reduce system<br>power consumption                        |  |

| Features                                                                                                                                                                                                                                           | Benefits                                                                                                                                                                                                          |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Peripherals                                                                                                                                                                                                                                        |                                                                                                                                                                                                                   |  |

| <ul> <li>Analog-to-digital converter (ADC) — 10-channel,<br/>12-bit resolution; 2.5 µs conversion time; automatic<br/>compare function; internal temperature sensor;<br/>internal bandgap reference channel; operation<br/>in stop mode</li> </ul> | <ul> <li>Having 10 channels allows up to 10 analog devices to be sampled at extremely high speeds</li> <li>Accuracy and full functionality guaranteed across 1.8V to 3.6V operating voltage of the MCU</li> </ul> |  |

| <ul> <li>Timer—One 6-channel (TPM3) and two 3-channel<br/>(TPM1 and TPM2); selectable input capture, output<br/>compare, or buffered edge- or center-aligned PWM<br/>on each channel</li> </ul>                                                    | Three TPMs allow for three different time bases,<br>with a total of twelve timer channels                                                                                                                         |  |

| <ul> <li>2 x Serial Communications Interface (SCI)—Two SCI<br/>interface modules with optional 13-bit break; offer</li> </ul>                                                                                                                      | <ul> <li>Have two SCI allows two separate<br/>dedicated devices</li> </ul>                                                                                                                                        |  |

| LIN master/slave extended break generation                                                                                                                                                                                                         | <ul> <li>Allows full-duplex, asynchronous, NRZ serial<br/>communication between MCU and remote devices</li> <li>Edge interrupt can wake up MCU from</li> </ul>                                                    |  |

| Two analog comparators with option to compare                                                                                                                                                                                                      | low-power mode     Requires only single pin for input signal, freeing                                                                                                                                             |  |

| to an internal reference—output can be optionally routed to timer/pulse width modulator (PWM) as                                                                                                                                                   | additional pins for other use  Allows other components in system to see result                                                                                                                                    |  |

| input capture trigger                                                                                                                                                                                                                              | of comparator with minimal delay  Can be used for single slope ADC and RC time                                                                                                                                    |  |

| Serial Peripheral Interface (SPI)—one module                                                                                                                                                                                                       | <ul> <li>constant measurements</li> <li>Allows high-speed (up to 5 Mbps) communications</li> </ul>                                                                                                                |  |

| with full-duplex or single-wire bidirectional;<br>double-buffered transmit and receive; master<br>or slave mode; MSB-first or LSB-first shifting                                                                                                   | to other MCUs or peripherals such as MC1319x<br>RF transceivers                                                                                                                                                   |  |

| <ul> <li>I<sup>2</sup>C with up to 100 kbps with maximum<br/>bus loading; multi-master operation; programmable<br/>slave address; interrupt-driven byte-by-byte<br/>data transfer; supports broadcast mode and<br/>10-bit addressing</li> </ul>    | <ul> <li>I<sup>2</sup>C port enables increased system memory by<br/>using an additional I<sup>2</sup>C EEPROM. This also creates<br/>an opportunity to add an additional I<sup>2</sup>C device.</li> </ul>        |  |

| nput/Output                                                                                                                                                                                                                                        |                                                                                                                                                                                                                   |  |

| <ul> <li>40 General Purpose Input/Output (GPIO),<br/>including one input-only and one output-only pin</li> </ul>                                                                                                                                   | Results in large number of flexible I/O pins that allo<br>developers to easily interface a device into their<br>own designs                                                                                       |  |

| 16 Keyboard Interrupts (KBI) pins with selectable polarity                                                                                                                                                                                         | Can be used for reading input from a keypad or<br>used as general pin interrupts                                                                                                                                  |  |

| System Protection                                                                                                                                                                                                                                  |                                                                                                                                                                                                                   |  |

| <ul> <li>Watchdog computer operating properly (COP)<br/>reset with option to run from dedicated 1 kHz<br/>internal clock source or bus clock</li> </ul>                                                                                            | <ul> <li>Allows device to recognize runaway code<br/>(infinite loops) and resets processor to avoid<br/>lock-up states</li> </ul>                                                                                 |  |

| Low-voltage detection with reset or interrupt;<br>selectable trip points                                                                                                                                                                           | Alarms the developer of voltage drops outside<br>of the typical operating range                                                                                                                                   |  |

| Illegal op code and illegal address detection with reset                                                                                                                                                                                           | Allows the device to recognize erroneous code<br>and resets the processor to avoid lock-up states                                                                                                                 |  |

| Flash block protection                                                                                                                                                                                                                             | Prevents unintentional programming of protected<br>flash memory, which greatly reduces the chance o<br>losing vital system code for vendor applications                                                           |  |

| Development Support                                                                                                                                                                                                                                |                                                                                                                                                                                                                   |  |

| Single-wire background debug interface                                                                                                                                                                                                             | <ul> <li>Allows developers to use the same hardware<br/>cables between S08 and V1 ColdFire<sup>®</sup> platforms</li> </ul>                                                                                       |  |

| Breakpoint capability                                                                                                                                                                                                                              | <ul> <li>Allows single breakpoint setting during in-circuit<br/>debugging (plus three more breakpoints in on-chip<br/>debug module)</li> </ul>                                                                    |  |

| <ul> <li>ICE debug module containing three comparators<br/>and nine trigger modes. Eight deep FIFO for<br/>storing change-of-flow addresses and event-only<br/>data – debug module supports both tag and<br/>force breakpoints.</li> </ul>         | Provides built-in full emulation without expense of traditional emulator                                                                                                                                          |  |

| Package Options |                |         |

|-----------------|----------------|---------|

| Part Number     | Temp. Range    | Package |

| MC9S08QE32CFT   | -40°C to +85°C | 48 QFN  |

| MC9S08QE32CLD   | -40°C to +85°C | 44 LQFP |

| MC9S08QE32CLC   | -40°C to +85°C | 32 LQFP |

| MC9S08QE32CWL   | -40°C to +85°C | 28 SOIC |

| MC9S08QE16CFT   | -40°C to +85°C | 48 QFN  |

| MC9S08QE16CLD   | -40°C to +85°C | 44 LQFP |

| MC9S08QE16CLC   | -40°C to +85°C | 32 LQFP |

| MC9S08QE16CWL   | -40°C to +85°C | 28 SOIC |

# Cost-Effective Development Tools DEMO9S08QE32

### \$69\*

Cost-effective demonstration kit including the QE32 daughter card, as well as serial port and built-in USB-BDM cable for debugging and programming.

### DC9S08QE32

### \$10\*

Daughter card of QE32 to use on your DEMOQE128 or DEMO9S08QE8 demonstration kit.

### CodeWarrior™ Development Studio for Microcontrollers 6.2

Complimentary\*\* Special Edition

CodeWarrior Development Studio for

Microcontrollers is a single tool suite

that supports software development for

Freescale's 8- and 32-bit V1 ColdFire

microcontrollers. Designers can further

accelerate application development with the

help of Processor Expert<sup>TM</sup>, an award-winning

rapid application development tool integrated

into the CodeWarrior tool suite.

Learn More:

For more information about the QE family, please visit **www.freescale.com/lowpower.**

Freescale and the Freescale logo are trademarks or registered trademarks of Freescale Semiconductor, Inc. in the U.S. and other countries. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2008.

Document Number: MC9S08QE32FS REV 0

force breakpoints.

<sup>\*</sup> Prices indicated are MSRP

<sup>\*\*</sup> Subject to license agreement