# PIC16F62X

### PIC16F62X Rev. A Silicon/Data Sheet Errata

The PIC16F62X (Rev. A) parts you have received conform functionally to the Device Data Sheet (DS40300**C**), except for the anomalies described below.

Microchip intends to address all issues listed here in future revisions of the PIC16F62X silicon.

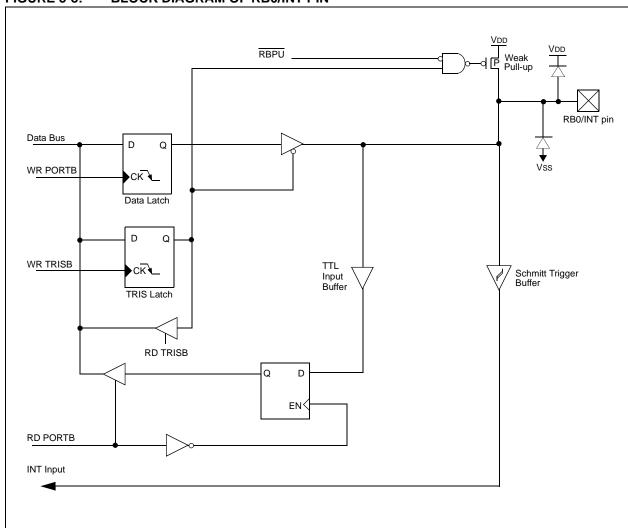

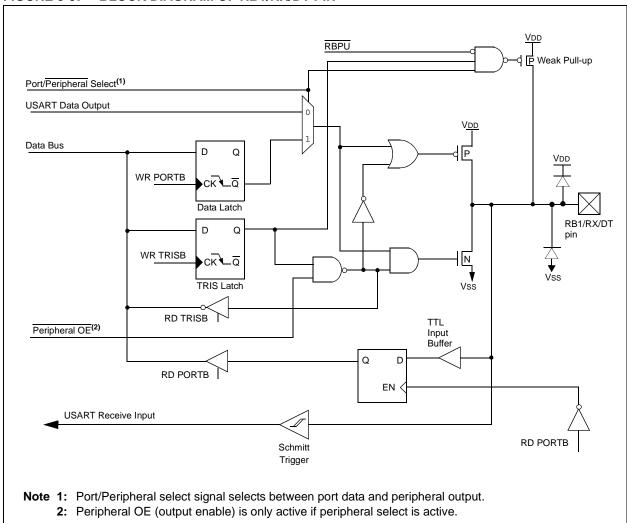

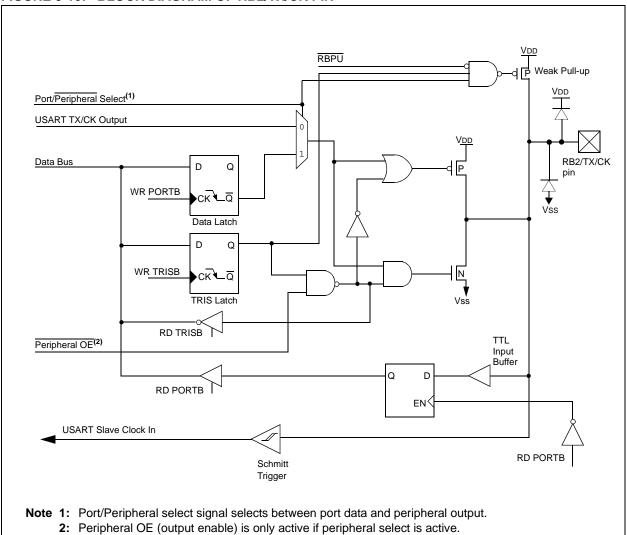

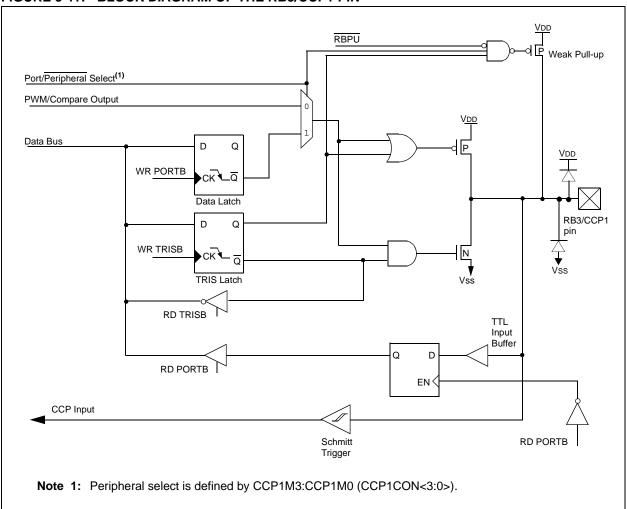

#### 1. Module: I/O Ports

A read of the PORTB Data Direction Register (TRISB) returns the Data Direction state on the port pins themselves and not the contents of the TRISB register latch.

FIGURE 5-8: BLOCK DIAGRAM OF RB0/INT PIN

FIGURE 5-9: BLOCK DIAGRAM OF RB1/RX/DT PIN

FIGURE 5-10: BLOCK DIAGRAM OF RB2/TX/CK PIN

FIGURE 5-11: BLOCK DIAGRAM OF THE RB3/CCP1 PIN

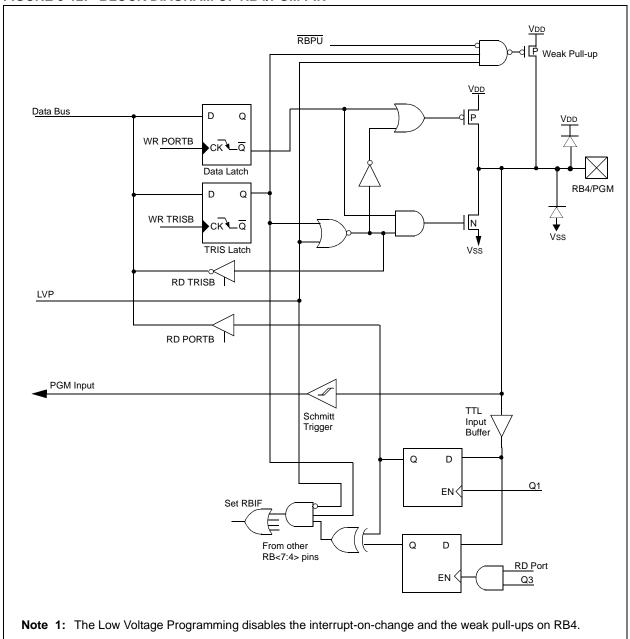

FIGURE 5-12: BLOCK DIAGRAM OF RB4/PGM PIN

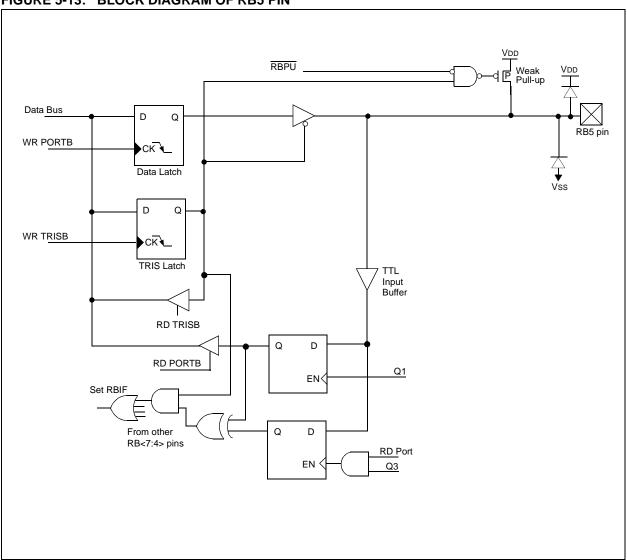

FIGURE 5-13: BLOCK DIAGRAM OF RB5 PIN

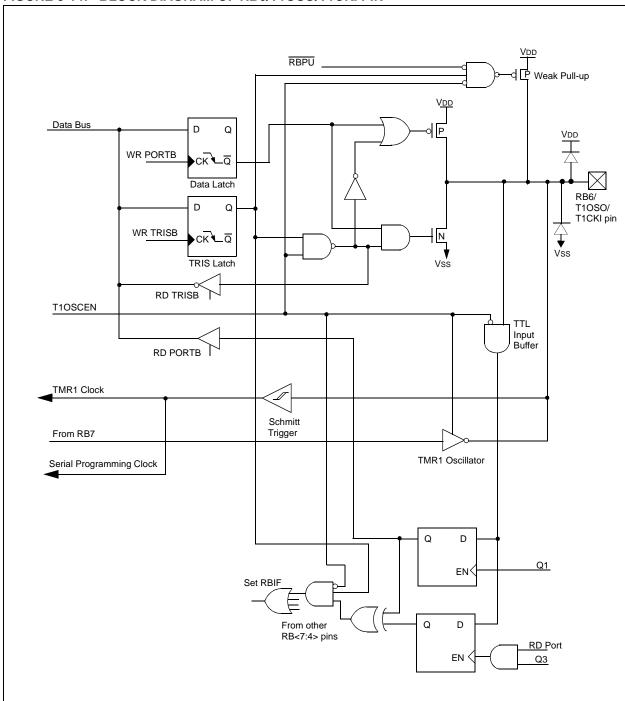

FIGURE 5-14: BLOCK DIAGRAM OF RB6/T10S0/T1CKI PIN

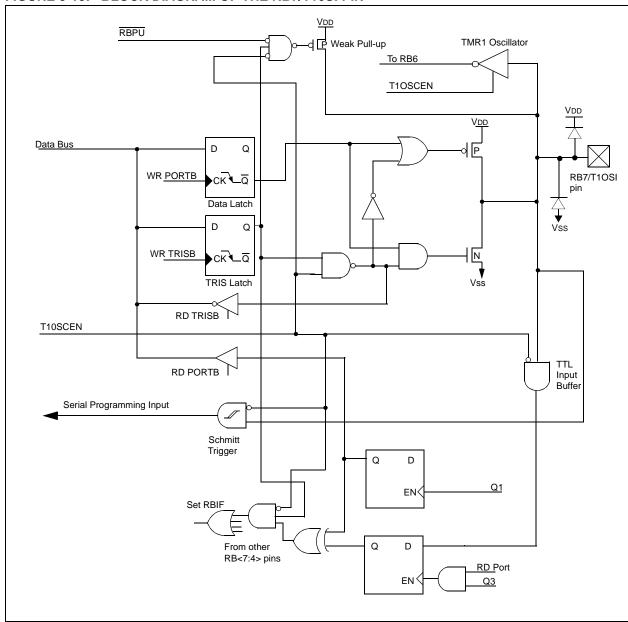

FIGURE 5-15: BLOCK DIAGRAM OF THE RB7/T10SI PIN

#### 2. Module: Comparator Mode 1

Mode 1 allows AN2 to drive the (+) inputs of both comparators. AN1 continues to drive the (-) input of Comparator 2, but AN0 and AN3 can be switched into the (-) input of Comparator 1. The state of the CIS bit chooses which input is to be connected to the comparator. When CIS = 0, AN0 is attached and the comparator functions correctly. When CIS = 1, AN3 is not completely connected to the comparator, resulting in incorrect behavior.

Mode 2 is also a Multiplex mode using the CIS bit. This mode functions correctly.

All other modes are unaffected by this Errata.

#### 3. Module: Low Voltage Programming Mode

The high voltage override for low voltage programming does not operate as specified in the programming specification. In the Low Voltage Programming (LVP) mode, the device can be programmed without using 12V on VPP (pin 4). However, when high voltage programming is used while the part has low voltage programming enabled, the Low Voltage mode is not overridden. If RB4 goes high for any reason during high voltage programming with LVP enabled, the programming will be interrupted.

#### **Work around**

Pull RB4 (pin 10) to ground during the initial programming to prevent programming interruptions. Once LVP has been disabled, it remedies this issue with RB4.

#### 4. Module: CCP (Compare Mode)

The CCP1 output latch, observed on RB3/CCP1/P1A, can change unexpectedly when the CCP module is changed from a set output on match (CCP1CON<3:0> = "1000") to clear output on match (CCP1CON<3:0> = "1001") or vice versa. This condition will occur following a CCP Reset at the beginning of the third iteration of the following sequence.

- CCPR1<3:0> is changed from "1001" to "1000" or vice versa.

- The TMR1H:TMR1L register pair matches the CCP1R1H:CCPR1L register pair.

Step 1 of the third iteration will cause the CCP1 output latch to immediately and erroneously change to the inverse of the CCPR1<0> bit. This gives the appearance of an inverted CCP response to the third and subsequent compare match events.

The apparent inverted response will persist until the CCP1CON<3> bit is cleared (exiting Compare mode). Interrupts always occur correctly on the match condition. The error is only in the state of the CCP1 output latch.

#### Work around

#### Option 1

Use the CCP toggle output on Compare Match mode (CCP1CON<3.0> = "0010").

#### Option 2

Since the problem occurs after two changes to the Compare and Match mode, it is only necessary to reset the CCP1CON register before the third change is made. To remain backwards compatible with earlier versions of the CCP module, always reset the CCP1CON register when changing from the clear output on Match mode to the set output on Match mode, as described in the following steps.

- 1. Ensure the RB3 data latch is set to '0'.

- Clear the CCP1CON register (clrf CCP1CON).

- 3. Set the CCP1CON<3:0> bits to "1000" for set output on match.

#### 5. Module: MCLR/RA5 in LVP Mode

When the PIC16F62X device has LVP enabled, MCLR is always enabled, regardless of the CONFIG register settings.

## PIC16F62X

## Clarifications/Corrections to the Data Sheet:

In the Device Data Sheet (DS40300**C**), the following clarifications and corrections should be noted.

## 1. Module: Special Function Registers (T1SYNC, Register T1CON)

In Table 3-1, "Special Function Registers Summary Bank 0", bit T1SYNC, in Register T1CON (address 10h), should be asserted logic low (i.e., T1SYNC) as shown in bold below.

## 2. Module: Special Function Registers (ADEN, Register RCSTA)

In Table 3-1, "Special Function Registers Summary Bank 0", bit ADEN, in Register RCSTA (address 18h), is misspelled. The correct spelling should be ADDEN, as shown in bold below.

This misspelling also appears in Register 12-2. Tables 12-2, 12-6, 12-7, 12-8, 12-9, 12-10, 12-11 and 12-12. Figures 12-8, 12-9, 12-10 and 12-11. Sections 12.2.2, 12.3.1 and 12.3.1.1.

#### TABLE 3-1: SPECIAL REGISTERS SUMMARY BANK 0

| Address | Name  | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR Reset | Value on all<br>other<br>Resets <sup>(1)</sup> |

|---------|-------|-------|-------|---------|---------|---------|--------|--------|--------|-----------------------|------------------------------------------------|

| Bank 0  |       |       |       |         |         |         |        |        |        |                       |                                                |

| 10h     | T1CON | _     |       | T1CKPS1 | T1CKPS0 | T10SCEN | T1SYNC | TMR1CS | TMR10N | 00 0000               | uu uuuu                                        |

| 18h     | RCSTA | SPEN  | RX9   | SREN    | CREN    | ADDEN   | FERR   | OERR   | RX9D   | 0000 -00x             | 0000 -00x                                      |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations, read as '0', q = value depends on condition, shaded = unimplemented

Note 1: Other (non power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

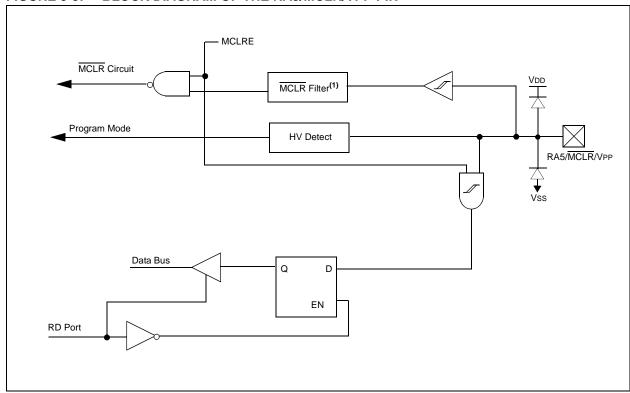

### 3. Module: I/O Ports (RA5/MCLR/VPP)

Figure 5-5, "Block Diagram of the RA5/MCLR/VPP Pin", is incorrect. The following diagram should be used instead.

FIGURE 5-5: BLOCK DIAGRAM OF THE RA5/MCLR/VPP PIN

#### 4. Module: Comparator

Example 9-1, "Initializing Comparator Module", is incorrect. The following code example should be used instead.

#### **EXAMPLE 9-1: INITIALIZING COMPARATOR MODULE**

```

BCF

INTCON, GIE

; Turn OFF Global Interrupts

; Turn OFF Peripheral Interrupts

BCF

INTCON, PEIE

; Init Port A

CLRF

PORTA

MOVLW

0X03

; Init comparator mode

CMCON

MOVWF

; CM<2:0> = 011

; Select BANK 1

STATUS, RPO

BSF

MOVLW

0x07

; Initialize Port A Direction

MOVWF

TRISA

; Set RA<2:0> as Inputs

; RA<4:3> as outputs

; TRIS<5> always reads '0'

STATUS, RPO

; Select BANK 0

BCF

CALL

DELAY10

; Wait 10us for comparator output to become valid

; See Table 17-1 Parameter 301

MOVF

CMCON, F

; Read CMCON to end change condition

PIR1,CMIF

BCF

; Clear pending interrupts

STATUS, RPO

BSF

; Select BANK 1

BSF

PIE1, CMIE

; Enable Comparator Interrupts

BCF

STATUS, RP0

; Select BANK 0

INTCON, PEIE ; Enable Peripheral Inter

INTCON, GIE ; Global Interrupt Enable

BSF

; Enable Peripheral Interrupts

BSF

; Insert Your code....

; Helper function is the Delay for 10us routine show below.

DELAY10

; burns 8 cycles + the call for 10 cycles or 10us at 4Mhz

; goto the next instruction and burn 2 cycles

goto $+1

call retlbl ; goto the next instruction and burn 2 more cycles

retlblreturn; go back and burn 2 cycles (actualy done 2x for 4 cycles consumed)

```

#### 5. Module: Data EEPROM Memory

Examples 13-1, "Data EEPROM Read", 13-2, "Data EEPROM Write", and 13-3, "Write Verify", are incorrect. The EEPROM registers are all located in Bank 1. The examples show the registers in Bank 0 and Bank 1. The following code examples should be used instead.

#### **EXAMPLE 13-1: DATA EEPROM READ**

```

BSF STATUS, RP0 ; Bank 1

MOVLW CONFIG_ADDR ;

MOVWF EEADR ; Address to write

BSF EECON1, RD ; EE Read

MOVF EEDATA, W ; W = EEDATA

BCF STATUS, RP0 ; Bank 0

```

#### **EXAMPLE 13-2: DATA EEPROM WRITE**

```

; set up the data and the address % \left\{ 1\right\} =\left\{ 1\right\} =

STATUS, RPO ; Bank 1

BSF

MOVLW CONFIG_ADDR ;

MOVWF EEADR

; Address to write

MOVLW CONFIG DATA ;

MOVWF EEDATA ; Data to write

; perform the write

operation

BSF

EECON1, WREN; Enable Write

BCF

INTCON, GIE ; Disable INTs

MOVLW 055h

MOVEW 00011

MOVWF EECON2

; Write 55

MOVLW 0AAh

MOVWF EECON2 ; Write AA

BSF

EECON1, WR ; Set WR bit

BCF

STATUS, RPO ; Bank 0

```

#### **EXAMPLE 13-3: WRITE VERIFY**

```

after the write in complete (i.e. in the

write interrupt)

BSF STATUS, RP0 ; Bank 1

MOVF

EEDATA, W ; load the last

written value into W

EECON1, RD ; start a read

BSF

Is the value written (in W Reg) and

read (in EEDATA) the same?

SUBWF EEDATA, W \,; the EEDATA has fresh

data

BTFSS

STATUS, Z ; Is the Zero flag set?

GOTO

WRITE ERR ; NO, Write Error

; YES, Good Write

; continue program

```

#### 6. Module: Timer1 Module

In **Section 7.0, "Timer1 Module"**, in Register 7-1, bit TMR1ON, "Timer1 On" should read as shown in bold below:

#### REGISTER 7-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS: 10h)

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|---------|---------|---------|--------|--------|--------|

| _     | _   | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |     |         |         |         |        |        | bit 0  |

bit 7-6 Unimplemented: Read as '0'

bit 5-4 T1CKPS1/T1CKPS0: Timer1 Input Clock Prescale Select bits

11 = 1:8 prescale value 10 = 1:4 prescale value 01 = 1:2 prescale value 11 = 1:1 prescale value

bit 3 T10SCEN: Timer1 Oscillator Enable Control bit

1 = Oscillator is enabled 0 = Oscillator is shut off<sup>(1)</sup>

bit 2 T1SYNC: Timer1 External Clock Input Synchronization Control bit

TMR1CS = 1

1 = Do not synchronize external clock input

0 = Synchronize external clock input

TMR1CS = 0

This bit is ignored. Timer1 uses the internal clock when TRM1CS = 0.

bit 1 TMR1CS: Timer1 Clock Source Select bit

1 = External clock from pin RB6/T1OSO/T1CKI (on the rising edge)

0 = Internal clock (Fosc/4)

bit 0 TMR1ON: Timer1 On bit

1 = Enables Timer1

0 = Disables Timer1

Note 1: The oscillator inverter and feedback resistor are turned off to eliminate power drain.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### **REVISION HISTORY**

#### Rev A Document (6/00)

Original errata document.

#### Rev B Document (11/00)

Issue 3 (CCP Compare Mode), Table 1 and 2 were added (page 2).

Under the Clarifications/Corrections Section, Item 1, Table 15-12 was updated with additional information (page 3).

#### Rev C Document (6/01)

Issues 2 and 3 were added.

Under Clarifications/Corrections, Items 2 and 3 were changed and Item numbers were renumbered accordingly.

#### Rev D Document (9/01)

Item 3 was rewritten (page 9).

Under the Clarifications/Corrections to the Data Sheet Section, the following items were changed:

Item 2, Tables 17.1 and 17.2, were updated with minor changes.

Item 6 was added.

#### Rev E Document (2/02)

Under Clarifications/Corrections to the Data Sheet, added Module 3: I/O Ports (RA5/MCLR/VPP).

#### Rev G Document (05/19/05)

Under Clarifications/Corrections to the Data Sheet, Added Module 6: Timer1 Module.

## PIC16F62X

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WAR-RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, PICMASTER, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Linear Active Thermistor, MPASM, MPLIB, MPLINK, MPSIM, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance and WiperLock are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the  $\mbox{U.S.A.}$

All other trademarks mentioned herein are property of their respective companies.

© 2005, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona and Mountain View, California in October 2003. The Company's quality system processes and procedures are for its PICmicro® 8-bit MCUs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### WORLDWIDE SALES AND SERVICE

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://support.microchip.com

Web Address: www.microchip.com

Atlanta

Alpharetta, GA Tel: 770-640-0034 Fax: 770-640-0307

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

San Jose

Mountain View, CA Tel: 650-215-1444 Fax: 650-961-0286

Toronto

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8676-6200 Fax: 86-28-8676-6599

China - Fuzhou

Tel: 86-591-8750-3506 Fax: 86-591-8750-3521

China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829

Fax: 86-24-2334-2829

China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Shunde

Tel: 86-757-2839-5507 Fax: 86-757-2839-5571

China - Qingdao

Tel: 86-532-502-7355 Fax: 86-532-502-7205

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-2229-0061 Fax: 91-80-2229-0062

India - New Delhi

Tel: 91-11-5160-8631 Fax: 91-11-5160-8632

Japan - Kanagawa

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or

82-2-558-5934

**Malaysia - Penang** Tel:011-604-646-8870 Fax:011-604-646-5086

Philippines - Manila

Tel: 011-632-634-9065 Fax: 011-632-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Kaohsiung

Tel: 886-7-536-4818 Fax: 886-7-536-4803 Taiwan - Taipei

Tel: 886-2-2500-6610

Fax: 886-2-2508-0102

Taiwan - Hsinchu

Tel: 886-3-572-9526

Fax: 886-3-572-6459

### EUROPE

Austria - Weis

Tel: 43-7242-2244-399 Fax: 43-7242-2244-393 **Denmark - Ballerup**

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Massy

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Ismaning

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399

Fax: 31-416-690340 **England - Berkshire** Tel: 44-118-921-5869

Fax: 44-118-921-5820

04/20/05