# **PIC24FXXKAXXX Flash Programming Specifications**

# 1.0 DEVICE OVERVIEW

This document defines the programming specifications for the PIC24FXXKAXXX family of 16-bit microcontroller devices. This is required only for developing programming support for the PIC24FXXKAXXX family. Users of any one of these devices should use the development tools that are already supporting the device programming.

The programming specifications are specific to the following devices:

- PIC24F08KA101

- PIC24F16KA101

- PIC24F08KA102

- PIC24F16KA102

- PIC24F04KA200

- PIC24F04KA201

# 2.0 PROGRAMMING OVERVIEW OF THE PIC24FXXKAXXX FAMILY

This section describes the two methods of programming the PIC24FXXKAXXX family of devices:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

The ICSP programming method is the most direct method for programming the device. However, it is also the slower of the two methods. It provides native, low-level programming capability to erase, program, and verify the device.

Section 3.0 "Device Programming – ICSP" describes the ICSP method.

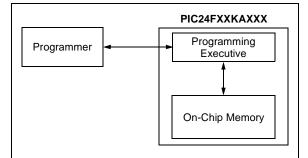

The Enhanced ICSP method is a faster method, which takes advantage of the programming executive as illustrated in Figure 2-1. The programming executive provides the necessary functionality to erase, program and verify the device through a command set. The command set allows the programmer to program the PIC24FXXKAXXX devices without having to deal with the low-level programming protocols of the device.

**Section 4.0 "Device Programming – Enhanced ICSP**" describes the ICSP method using the programming executive.

# FIGURE 2-1:

#### PROGRAMMING SYSTEM OVERVIEW FOR ENHANCED ICSP™ METHOD

# 2.1 **Power Requirements**

All devices in the PIC24FXXKAXXX family are 3.3V supply designs. The core, the peripherals and the I/O pins operate at 3.3V. The device can operate from 1.8V to 3.6V.

# 2.2 Entering Programming Mode Overview

There are two methods of entering the Programming mode (either ICSP or Enhanced ICSP):

Low-Voltage ICSP Entry

When the  $\overline{\text{MCLR}}/\text{VPP/RA5}$  pin is used as  $\overline{\text{MCLR}}$  by applying Vss on  $\overline{\text{MCLR}}$  (low-voltage entry), the device gets reset, and on applying the Programming mode entry sequence on the PGCx and PGDx pins, the device enters the Programming mode.

• High-Voltage ICSP Entry

To enter the Programming mode, if the MCLR function of the MCLR/VPP/RA5 pin needs to be disabled or is already disabled, a voltage VIHH should be applied on VPP (high-voltage entry). This is equivalent to applying Vss on MCLR; the device gets reset. On applying the Programming mode entry sequence on PGCx and PGDx pins, the device enters the Programming mode.

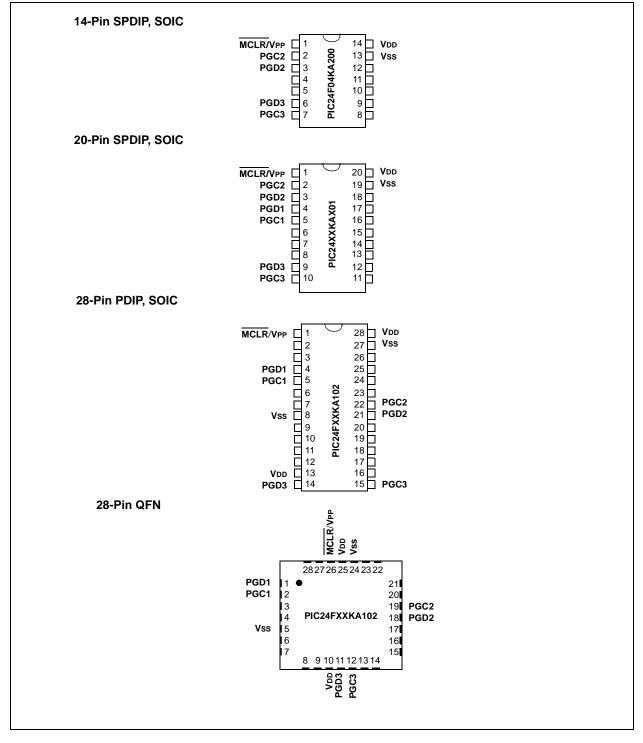

# 2.3 Pin Diagrams

Figure 2-2 provides the pin diagrams for the PIC24FXXKAXXX family.

# Table 2-1 provides the pins that are required for programming (indicated in bold letters in Figure 2-2). Refer to the appropriate device data sheet for pin descriptions.

### FIGURE 2-2: PIN DIAGRAMS

| Pin Name | During Programming |                                       |                    |  |

|----------|--------------------|---------------------------------------|--------------------|--|

|          | Pin Name           | Pin Type                              | Pin Description    |  |

| MCLR/Vpp | MCLR/VPP           | Р                                     | Programming Enable |  |

| Vdd      | Vdd                | Р                                     | Power Supply       |  |

| Vss      | Vss                | Р                                     | Ground             |  |

| PGCx     | PGC                | I Programming Pin Pair: Serial Clock  |                    |  |

| PGDx     | PGD                | I/O Programming Pin Pair: Serial Data |                    |  |

TABLE 2-1: PIN DESCRIPTIONS (DURING PROGRAMMING)

**Legend:** I = Input, O = Output, P = Power

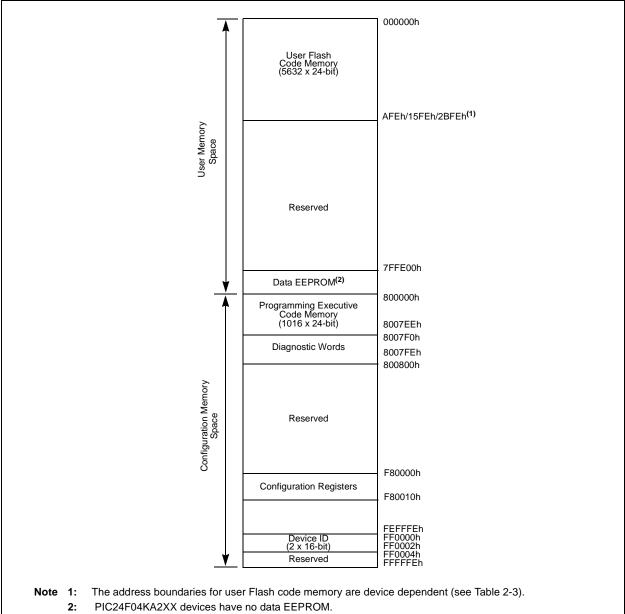

# 2.4 Memory Map

The program memory map extends from 000000h to FFFFFEh. Code storage is located at the base of the memory map, and supports up to 5.5K instruction words (about 16 Kbytes).

Table 2-3 provides the program memory size and number of program memory rows present in each device variant.

The PIC24FXXKA1XX family devices have an on-chip data EEPROM. This data EEPROM is mapped to the program memory area from location 7FFE00h to 7FFFFEh.

Table 2-4 provides the data EEPROM size and the number of rows present in each device variant.

The erase operation can be done on one word, half of a row or one row at a time. The program operation can be done only one word at a time.

Locations, 800000h through 8007FEh, are reserved for executive code memory. This region stores the programming executive, the debugging executive and the Diagnostic Words. The programming executive is used for device programming, and the debug executive is used for in-circuit debugging. This region of memory cannot be used to store user code.

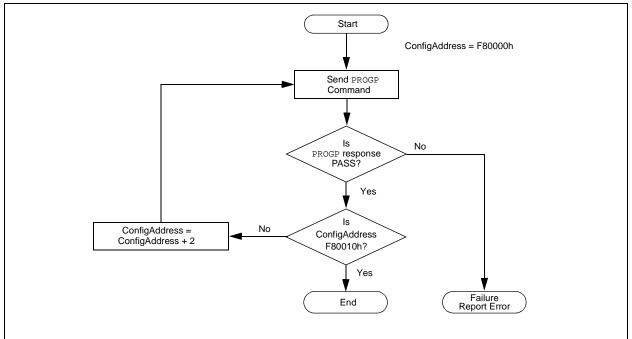

The device Configuration registers are implemented from location F80000h to F80010h, and can be erased or programmed one register at a time.

Table 2-2 provides the implemented Configuration registers and their locations.

Locations, FF0000h and FF0002h, are reserved for the Device ID registers. These bits can be used by the programmer to identify the device type that is being programmed. See **Section 6.0** "**Device ID**" for more information. The Device ID registers read out normally even after code protection is applied.

Figure 2-3 depicts the memory map for the PIC24FXXKAXXX family variants.

# TABLE 2-2:CONFIGURATION REGISTER<br/>LOCATIONS

| Configuration Register | Address |

|------------------------|---------|

| FBS                    | F80000  |

| FGS                    | F80004  |

| FOSCSEL                | F80006  |

| FOSC                   | F80008  |

| FWDT                   | F8000A  |

| FPOR                   | F8000C  |

| FICD                   | F8000E  |

| FDS                    | F80010  |

### TABLE 2-3: CODE MEMORY SIZE

| PIC24FXXKAXXX<br>Device User | Memory No. of<br>Address Limit<br>(Instruction Words) | No. of<br>Rows |

|------------------------------|-------------------------------------------------------|----------------|

| PIC24F08KA101                | 15FE (2.75K)                                          | 88             |

| PIC24F16KA101                | 2BFE (5.5K)                                           | 176            |

| PIC24F08KA102                | 15FE (2.75K)                                          | 88             |

| PIC24F16KA102                | 2BFE (5.5K)                                           | 176            |

| PIC24F04KA200                | AFE (1.375K)                                          | 44             |

| PIC24F04KA201                | AFE (1.375K)                                          | 44             |

**Note:** An erase operation can be performed on one, two or four rows at a time, and a program operation can be performed on one row at a time.

#### TABLE 2-4:DATA EEPROM MEMORY SIZE

| PIC24FXXKA1XX<br>Device | Data EEPROM<br>Size in Words | No. of Rows |

|-------------------------|------------------------------|-------------|

| PIC24F08KA101           | 256                          | 32          |

| PIC24F16KA101           | 256                          | 32          |

| PIC24F08KA102           | 256                          | 32          |

| PIC24F16KA102           | 256                          | 32          |

**Note:** An erase operation can be performed on one, four or eight words at a time and a program operation can be performed on one word at a time.

# FIGURE 2-3: PROGRAM MEMORY MAP

# 3.0 DEVICE PROGRAMMING – ICSP

The ICSP method is a special programming protocol that allows reading and writing to the PIC24FXXKAXXX device family memory. ICSP is the most direct method used to program a device; however, Enhanced ICSP is faster. The ICSP mode also reads the contents of the executive memory to determine if the programming executive is present. This is accomplished by applying control codes and instructions, serially to the device, using PGCx and PGDx pins.

In ICSP mode, the system clock is taken from the PGCx pin regardless of the device's oscillator Configuration bits. All of the instructions are shifted serially to an internal buffer, loaded into the Instruction Register (IR), and then executed. No program is fetched from the internal memory. Instructions are fed in 24 bits at a time. PGDx is used to shift data in, and PGCx is used as both the serial shift clock and the CPU execution clock.

Note: During ICSP operation, the operating frequency of PGCx should not exceed 10 MHz.

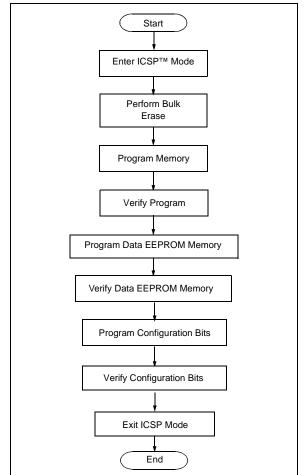

# 3.1 Overview of the Programming Process

Figure 3-1 illustrates the high-level overview of the programming process.

After entering the ICSP mode, perform the following:

- 1. Bulk Erase the device.

- 2. Program and verify the code memory.

- 3. Program and verify the data EEPROM memory.

- 4. Program and verify the device configuration.

- 5. Program the code-protect Configuration bits if required.

#### FIGURE 3-1:

#### HIGH–LEVEL ICSP™ PROGRAMMING FLOW

# 3.2 ICSP Operation

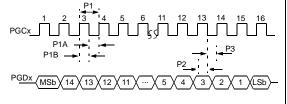

Upon entry into ICSP mode, the CPU is Idle. An internal state machine governs the execution of the CPU. A 4-bit control code is clocked in, using PGCx and PGDx, and this control code is used to command the CPU (see Table 3-1).

The SIX control code is used to send instructions to the CPU for execution, and the REGOUT control code is used to read data out of the device via the VISI register.

| TABLE 3-1: | <b>CPU CONTROL CODES IN</b> |

|------------|-----------------------------|

|            | ICSP™ MODE                  |

| 4-Bit<br>Control Code Mnemonic |        | Description                              |

|--------------------------------|--------|------------------------------------------|

| 0000b                          | SIX    | Shift in 24-bit instruction and execute. |

| 0001b                          | REGOUT | Shift out the VISI<br>(0784h) register.  |

| 0010b-1111b                    | N/A    | This is reserved.                        |

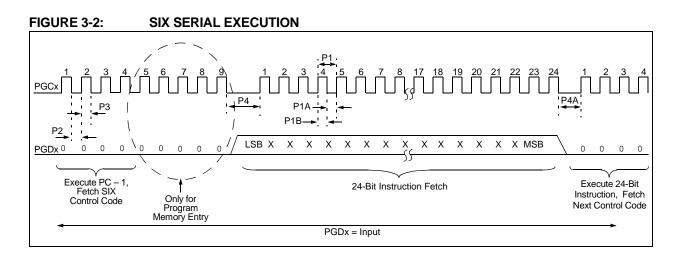

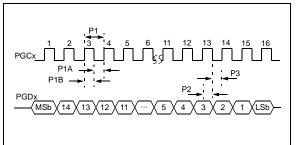

### 3.2.1 SIX SERIAL INSTRUCTION EXECUTION

The SIX control code allows execution of PIC24FXXKAXXX family assembly instructions. When the SIX code is received, the CPU is suspended for 24 clock cycles as the instruction is then clocked into the internal buffer. Once the instruction is shifted in, the state machine allows it to be executed over the next four PGC clock cycles. While the received instruction is executed, the state machine simultaneously shifts in the next 4-bit command (see Figure 3-2).

Coming out of Reset, the first 4-bit control code is always forced to SIX, and a forced NOP instruction is executed by the CPU. Five additional PGCx clocks are needed on start-up; thereby resulting in a 9-bit SIX command, instead of the normal 4-bit SIX command.

After the forced SIX is clocked in, the ICSP operation resumes to normal. That is, the next 24 clock cycles load the first instruction word to the CPU.

| Note: | To account for this forced NOP, all example |  |  |

|-------|---------------------------------------------|--|--|

|       | codes in this specification begin with a    |  |  |

|       | NOP to ensure that no data is lost.         |  |  |

3.2.1.1 Differences Between SIX Instruction Execution and Normal Instruction Execution

There are some differences between executing instructions using the SIX ICSP command and normal device instruction execution. As a result, the code examples in this specification might not match those required to perform the same operations during normal device operation.

The differences are:

• Two-word instructions require 2 SIX operations to clock in all the necessary data.

Examples of two-word instructions are  $\ensuremath{\texttt{GOTO}}$  and  $\ensuremath{\texttt{CALL}}.$

Two-cycle instructions require 2 SIX operations to complete. The first SIX operation shifts in the instruction and begins to execute it. A second SIX operation, which should shift in a NOP to avoid losing data, allows the CPU clocks required to finish executing the instruction.

Examples of two-cycle instructions are table read and table write instructions.

The CPU does not automatically stall to account for pipeline changes. A CPU stall occurs when an instruction modifies a register, which is used by the instruction immediately following the CPU stall for Indirect Addressing. During normal operation, the CPU forces a NOP while the new data is read. To account for this, while using ICSP, any indirect references to a recently modified register should be proceeded with a NOP. For example, MOV #0x0,W0 followed by MOV [W0],W1 must have a NOP inserted in between.

If a two-cycle instruction modifies a register, which is used indirectly, it requires two following NOPs; one to execute the second half of the instruction and the other to stall the CPU to correct the pipeline.

For example, TBLWTL [W0++],[W1] should be followed by 2 NOPs.

• The device Program Counter (PC) continues to automatically increment during the ICSP instruction execution, even though the Flash memory is not being used. As a result, it is possible for the PC to be incremented so that it points to invalid memory locations.

Examples of invalid memory spaces are unimplemented Flash addresses or the vector space (location 0x0 to 0x1FF).

If the PC ever points to these locations, it causes the device to reset, possibly interrupting the ICSP operation. To prevent this, instructions should be periodically executed to reset the PC to a safe space. The optimal method of achieving this is to perform a "GOTO 0x200".

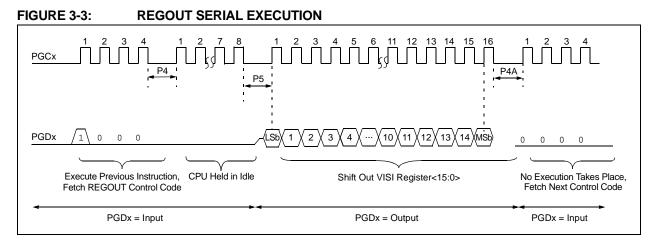

# 3.2.2 REGOUT SERIAL INSTRUCTION EXECUTION

The REGOUT control code allows for the data to be extracted from the device in the ICSP mode. It is used to clock the contents of the VISI register out of the device over the PGDx pin. After the REGOUT control code is received, the CPU is held Idle for 8 cycles. After this, an additional 16 cycles are required to clock the data out (see Figure 3-3).

The REGOUT code is unique as the PGDx pin is an input when the control code is transmitted to the device. However, after the control code is processed, the PGDx pin becomes an output as the VISI register is shifted out.

Note 1: After the contents of VISI are shifted out, the PIC24FXXKAXXX devices maintain PGDx as an output until the first rising edge of the next clock is received.

2: Data changes on the falling edge and latches on the rising edge of PGCx. For all data transmissions, the Least Significant bit (LSb) is transmitted first.

# 3.3 Entering ICSP Mode

### 3.3.1 LOW-VOLTAGE ICSP ENTRY

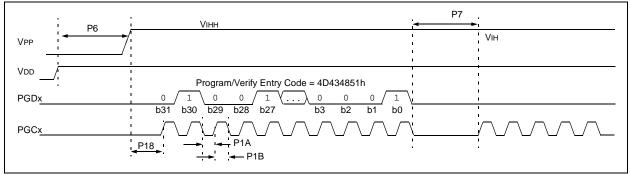

As illustrated in Figure 3-4, the following processes are involved in entering ICSP Program/Verify mode using MCLR:

- 1. MCLR is briefly driven high, then low.

- 2. A 32-bit key sequence is clocked into PGDx.

- 3. MCLR is then driven high within a specified period of time and held.

The programming voltage VIH IS applied to  $\overline{\text{MCLR}}$ ; this is VDD in the case of PIC24FXXKAXXX devices. There is no minimum time requirement for holding at VIH. After VIH is removed, an interval of at least P18 must elapse before presenting the key sequence on PGDx.

The key sequence is a specific 32-bit pattern: '0100 1101 0100 0011 0100 1000 0101 0001' (more easily remembered as 4D434851h in hexadecimal). The device will enter Program/Verify mode only if the sequence is valid. The Most Significant bit (MSb) of the most significant nibble must be shifted in first.

Once the key sequence is complete, VIH must be applied to  $\overline{\text{MCLR}}$  and held at that level for as long as the Program/Verify mode is to be maintained. An

interval of at least P19 and P7 must elapse before presenting data on PGDx. Signals appearing on PGCx before P7 has elapsed would not be interpreted as valid.

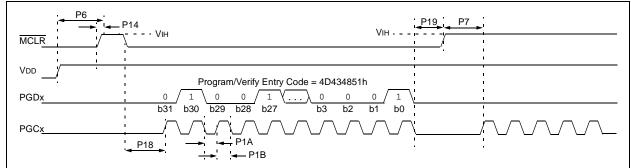

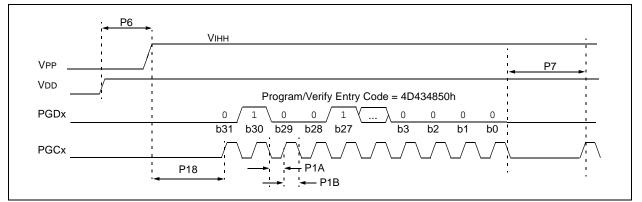

# 3.3.2 HIGH-VOLTAGE ICSP ENTRY

Entering the ICSP Program/Verify mode, using the VPP pin is the same as entering the mode using MCLR. The only difference is the programming voltage applied to VPP is VIHH, and before presenting the key sequence on PGDx, an interval of at least P18 should elapse (see Figure 3-5).

Once the key sequence is complete, an interval of at least P7 should elapse, and the voltage should remain at VIHH. The voltage, VIHH, must be held at that level for as long as the Program/Verify mode is to be maintained. An interval of at least P7 must elapse before presenting the data on PGDx.

Signals appearing on PGDx before P7 has elapsed will not be interpreted as valid.

Upon a successful entry, the program memory can be accessed and programmed in serial fashion. While in ICSP mode, all unused I/Os are placed in a high-impedance state.

### FIGURE 3-4: ENTERING ICSP<sup>™</sup> MODE USING LOW-VOLTAGE ENTRY

# 3.4 Flash Memory Programming in ICSP Mode

# 3.4.1 PROGRAMMING OPERATIONS

The NVMCON register controls the Flash memory write and erase operations. To program the device, set the NVMCON register to select the type of erase operation (see Table 3-2) or write operation (see Table 3-3). Set the WR control bit (NVMCON<15>) to initiate the program.

In ICSP mode, all programming operations are self-timed. There is an internal delay between setting and automatic clearing of the WR control bit when the programming operation is complete. Refer to **Section 7.0 "AC/DC Characteristics and Timing Requirements"** for information on the delays associated with various programming operations.

# TABLE 3-2:NVMCON VALUES FOR<br/>ERASE OPERATIONS

| NVMCON<br>Value      | Erase Operation                                                                                                                 |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 4064h                | Erase the code memory and<br>Configuration registers (does not erase<br>programming executive code and<br>Device ID registers). |

| 404Ch                | Erase the general segment and<br>Configuration bits associated with it.                                                         |

| 4068h                | Erase the boot segment and<br>Configuration bits associated with it.                                                            |

| 405Ah <sup>(1)</sup> | Erase four rows of code memory.                                                                                                 |

| 4059h <sup>(1)</sup> | Erase two rows of code memory.                                                                                                  |

| 4058h <sup>(1)</sup> | Erase a row of code memory.                                                                                                     |

| 4050h                | Erase the entire data EEPROM<br>memory and Configuration bits<br>associated with it.                                            |

| 405Ah <sup>(1)</sup> | Erase eight words of data EEPROM memory.                                                                                        |

| 4059h <sup>(1)</sup> | Erase four words of data EEPROM memory.                                                                                         |

| 4058h <sup>(1)</sup> | Erase one word of data EEPROM memory.                                                                                           |

| 4054h                | Erase all the Configuration registers (except the code-protect fuses).                                                          |

| 4058h <sup>(1)</sup> | Erase Configuration registers except FBS and FGS.                                                                               |

Note 1: The destination address decides the region (code memory, data EEPROM memory or Configuration register) of the erased rows/words.

# TABLE 3-3: NVMCON VALUES FOR WRITE OPERATIONS

| NVMCON<br>Value      | Write Operation                                                            |

|----------------------|----------------------------------------------------------------------------|

| 4004h <sup>(1)</sup> | Write one Configuration register.                                          |

| 4004h <sup>(1)</sup> | Program one row (32 instruction words) of code memory or executive memory. |

| 4004h <sup>(1)</sup> | Program one word of data EEPROM memory.                                    |

|                      | The destination address decides the region (code memory, data EEPROM       |

# 3.4.2 STARTING AND STOPPING A PROGRAMMING CYCLE

erased rows/words.

The WR bit (NVMCON<15>) is used to start an erase or write cycle. Initiate the programming cycle by setting the WR bit.

memory or Configuration register) of the

All erase and write cycles are self-timed. The WR bit should be polled to determine if the erase or write cycle is completed. Start a programming cycle as follows:

BSET NVMCON, #WR

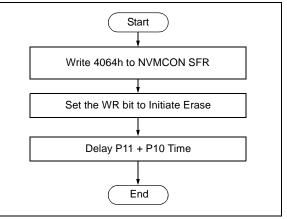

# 3.5 Erasing Program Memory

To erase the program memory (all of code memory, data memory and Configuration bits, including the code-protect bits), set the NVMCON to 4064h and then execute the programming cycle.

Figure 3-6 illustrates the ICSP programming process for Bulk Erase. This process includes the ICSP command code, which must be transmitted (for each instruction), LSB first, using the PGCx and PGDx pins (see Figure 3-2).

Table 3-4 provides the steps for executing serial instruction for the Bulk Erase mode.

**Note:** Program memory must be erased before writing any data to program memory.

# FIGURE 3-6: BULK ERASE FLOW

| Command<br>(Binary) | Data<br>(Hex)                                                                                       | Description                                      |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------|--|--|--|

| Step 1: Exit the    | Step 1: Exit the Reset vector.                                                                      |                                                  |  |  |  |

| 0000                | 000000                                                                                              | NOP                                              |  |  |  |

| 0000                | 040200                                                                                              | GOTO 0x200                                       |  |  |  |

| 0000                | 000000                                                                                              | NOP                                              |  |  |  |

| Step 2: Set the     | NVMCON to erase the                                                                                 | ne entire program memory.                        |  |  |  |

| 0000                | 24064A                                                                                              | MOV #0x4064, W10                                 |  |  |  |

| 0000                | 883B0A                                                                                              | MOV W10, NVMCON                                  |  |  |  |

| Step 3: Set the     | TBLPAG and perform                                                                                  | n dummy table write to select the erased memory. |  |  |  |

| 0000                | 200000                                                                                              | MOV # <pageval>, WO</pageval>                    |  |  |  |

| 0000                | 880190                                                                                              | MOV W0, TBLPAG                                   |  |  |  |

| 0000                | 200000                                                                                              | MOV #0x0000, W0                                  |  |  |  |

| 0000                | BB0800                                                                                              | TBLWTL W0, [W0]                                  |  |  |  |

| 0000                | 000000                                                                                              | NOP                                              |  |  |  |

| 0000                | 000000                                                                                              | NOP                                              |  |  |  |

| Step 4: Initiate    | the erase cycle.                                                                                    |                                                  |  |  |  |

| 0000                | A8E761                                                                                              | BSET NVMCON, #WR                                 |  |  |  |

| 0000                | 000000                                                                                              | NOP                                              |  |  |  |

| 0000                | 000000                                                                                              | NOP                                              |  |  |  |

| Step 5: Repeat      | Step 5: Repeat this step to poll the WR bit (bit 15 of NVMCON) until it is cleared by the hardware. |                                                  |  |  |  |

| 0000                | 000000                                                                                              | NOP                                              |  |  |  |

| 0000                | 040200                                                                                              | GOTO 0x200                                       |  |  |  |

| 0000                | 000000                                                                                              | NOP                                              |  |  |  |

| 0000                | 803B02                                                                                              | MOV NVMCON, W2                                   |  |  |  |

| 0000                | 883C22                                                                                              | MOV W2, VISI                                     |  |  |  |

| 0000                | 000000                                                                                              | NOP                                              |  |  |  |

| 0001                | <visi></visi>                                                                                       | Clock out the contents of the VISI register.     |  |  |  |

| 0000                | 000000                                                                                              | NOP                                              |  |  |  |

# TABLE 3-4: SERIAL INSTRUCTION EXECUTION FOR CHIP ERASE

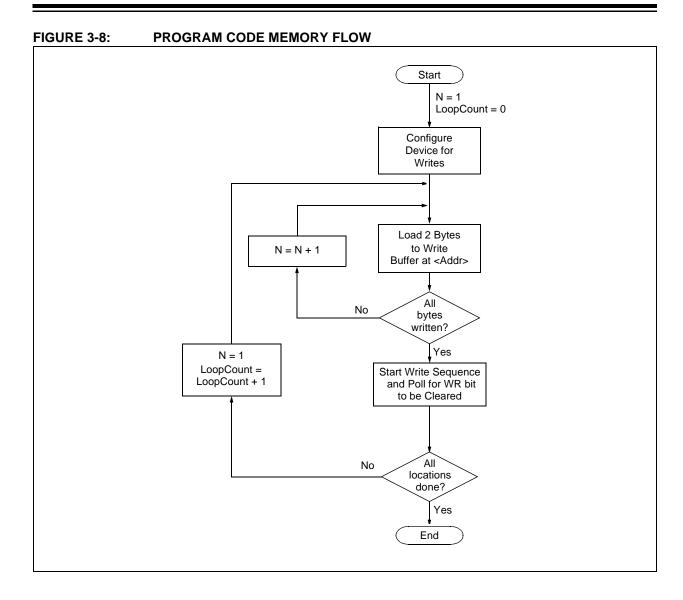

# 3.6 Writing Code Memory

The procedure for writing code memory is the same as writing the Configuration registers. The difference is that the 32 instruction words are programmed one at a time. To facilitate this operation, working registers, W0:W5, are used as temporary holding registers for the data to be programmed. Figure 3-8 illustrates the code memory writing flow.

Table 3-5 provides the ICSP programming details, including the serial pattern with the ICSP command code, which must be transmitted LSB first, using the PGCx and PGDx pins (see Figure 3-2).

In Step 1 of Table 3-5, the Reset vector is exited; in Step 2, the NVMCON register is initialized for programming a full row of code memory, and in Step 3, the 24-bit starting destination address for programming is loaded into the TBLPAG register and W7 register. The upper byte of the starting destination address is stored in TBLPAG and the lower 16 bits of the destination address are stored in W7.

To minimize the programming time, a packed instruction format is used (see Figure 3-7).

In Step 4 of Table 3-5, four packed instruction words are stored in working registers, W0:W5, using the MOV instruction; the Read Pointer, W6, is initialized. Figure 3-7 illustrates the contents of W0:W5 holding the packed instruction word data. In Step 5, eight TBLWT instructions are used to copy the data from W0:W5 to the write latches of the code memory. Since code memory is programmed 32 instruction words at a time, Steps 3 to 5 are repeated eight times to load all the write latches (see Step 6).

After the write latches are loaded, initiate programming by writing to the NVMCON register in Steps 7 and 8. In Step 9, the internal PC is reset to 200h. This is a precautionary measure to prevent the PC from incrementing to unimplemented memory when large devices are being programmed. Finally, in Step 10, repeat Steps 3 through 9 until all of the code memory is programmed.

# FIGURE 3-7: PACKED INSTRUCTION WORDS IN W0:W5

| 15   | 87   |                                      | 0                                              |

|------|------|--------------------------------------|------------------------------------------------|

|      | LSW0 |                                      |                                                |

| MSB1 |      | MSB0                                 |                                                |

|      | LSW1 |                                      |                                                |

|      | LSW2 |                                      |                                                |

| MSB3 |      | MSB2                                 |                                                |

|      | LSW3 |                                      |                                                |

|      |      |                                      |                                                |

|      | MSB1 | LSW0<br>MSB1<br>LSW1<br>LSW2<br>MSB3 | LSW0<br>MSB1 MSB0<br>LSW1<br>LSW2<br>MSB3 MSB2 |

# TABLE 3-5: SERIAL INSTRUCTION EXECUTION FOR WRITING CODE MEMORY

| Command<br>(Binary) | Data<br>(Hex)                  | Description          |                                                                     |  |  |

|---------------------|--------------------------------|----------------------|---------------------------------------------------------------------|--|--|

| Step 1: Exit t      | Step 1: Exit the Reset vector. |                      |                                                                     |  |  |

| 0000                | 000000                         | NOP                  |                                                                     |  |  |

| 0000                | 040200<br>000000               | GOTO<br>NOP          | 0x200                                                               |  |  |

|                     | ne NVMCON to prog              | -                    | uction words.                                                       |  |  |

| 0000                | 24004A                         | MOV                  | #0x4004, W10                                                        |  |  |

| 0000                | 883B0A                         | MOV                  | W10, NVMCON                                                         |  |  |

| Step 3: Initial     | ize the Write Pointe           | r <b>(W7) for</b> тв | LWT instruction.                                                    |  |  |

| 0000                | 200xx0                         | MOV                  | <pre>#<destinationaddress23:16>, W0</destinationaddress23:16></pre> |  |  |

| 0000                | 880190                         | MOV                  | W0, TBLPAG                                                          |  |  |

| 0000                | 2xxxx7                         | MOV                  | <pre>#<destinationaddress15:0>, W7</destinationaddress15:0></pre>   |  |  |

| Step 4: Load        | W0:W5 with the nex             | kt 4 instructio      | on words to program.                                                |  |  |

| 0000                | 2xxxx0                         | MOV                  | # <lsw0>, W0</lsw0>                                                 |  |  |

| 0000                | 2xxxx1                         | MOV                  | # <msb1:msb0>, W1</msb1:msb0>                                       |  |  |

| 0000                | 2xxxx2                         | MOV                  | # <lsw1>, W2</lsw1>                                                 |  |  |

| 0000                | 2xxxx3                         | MOV                  | # <lsw2>, W3</lsw2>                                                 |  |  |

| 0000                | 2xxxx4                         | MOV                  | # <msb3:msb2>, W4</msb3:msb2>                                       |  |  |

| 0000                | 2xxxx5                         | MOV                  | # <lsw3>, W5</lsw3>                                                 |  |  |

| Command<br>(Binary) | Data<br>(Hex)        | Description                                                        |

|---------------------|----------------------|--------------------------------------------------------------------|

|                     |                      | N6) and load the (next set of) write latches.                      |

| 0000                |                      | CLR W6                                                             |

| 0000                | EB0300<br>000000     | NOP                                                                |

|                     |                      |                                                                    |

| 0000<br>0000        | BB0BB6               | TBLWTL [W6++], [W7]                                                |

| 0000                | 000000<br>000000     | NOP<br>NOP                                                         |

|                     |                      |                                                                    |

| 0000                | BBDBB6               | TBLWTH.B [W6++], [W7++]                                            |

| 0000                | 000000               | NOP                                                                |

| 0000                | 000000               |                                                                    |

| 0000                | BBEBB6               | TBLWTH.B [W6++], [++W7]                                            |

| 0000                | 000000               | NOP                                                                |

| 0000                | 000000               | NOP                                                                |

| 0000                | BB1BB6               | TBLWTL [W6++], [W7++]                                              |

| 0000                | 000000               | NOP                                                                |

| 0000                | 000000               |                                                                    |

| 0000                | BB0BB6               | TBLWTL [W6++], [W7]                                                |

| 0000                | 000000               | NOP                                                                |

| 0000                | 000000               | NOP                                                                |

| 0000                | BBDBB6               | TBLWTH.B [W6++], [W7++]                                            |

| 0000                | 000000               | NOP                                                                |

| 0000                | 000000               | NOP                                                                |

| 0000                | BBEBB6               | TBLWTH.B [W6++], [++W7]                                            |

| 0000                | 000000               | NOP                                                                |

| 0000                | 000000               | NOP                                                                |

| 0000                | BB1BB6               | TBLWTL [W6++], [W7++]                                              |

| 0000                | 000000               | NOP                                                                |

| 0000                | 000000               | NOP                                                                |

| <u> </u>            |                      | 5, eight times, to load the write latches for 32 instructions.     |

| Step 7: Initiat     | e the write cycle.   |                                                                    |

| 0000                | A8E761               | BSET NVMCON, #WR                                                   |

| 0000                | 000000               | NOP                                                                |

| 0000                | 000000               | NOP                                                                |

| Step 8: Repe        | at this step to poll | the WR bit (bit 15 of NVMCON) until it is cleared by the hardware. |

| 0000                | 040200               | GOTO 0x200                                                         |

| 0000                | 000000               | NOP                                                                |

| 0000                | 803B02               | MOV NVMCON, W2                                                     |

| 0000                | 883C22               | MOV W2, VISI                                                       |

| 0000                | 000000               | NOP                                                                |

| 0001                | <visi></visi>        | Clock out contents of the VISI register.                           |

| 0000                | 000000               | NOP                                                                |

|                     | t device internal P  |                                                                    |

| 0000                | 040200               | GOTO 0x200                                                         |

| 0000                | 000000               | NOP                                                                |

| 0000                | 00000                | 101                                                                |

# TABLE 3-5: SERIAL INSTRUCTION EXECUTION FOR WRITING CODE MEMORY (CONTINUED)

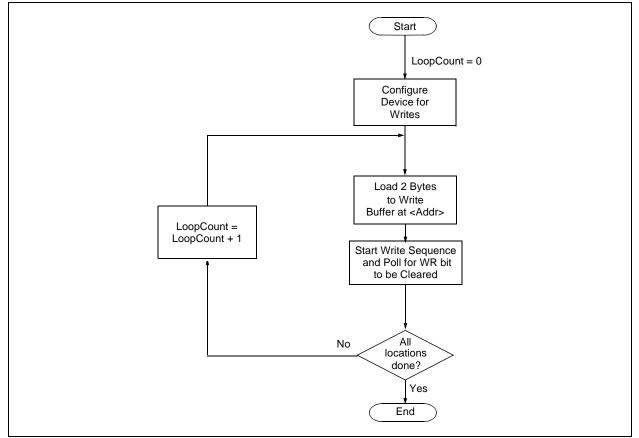

# 3.7 Writing Data EEPROM

Figure 3-9 illustrates the flow of programming the data EEPROM memory. The procedure is the same as writing code memory. The only difference is that only one word is programmed in each operation. When writing data EEPROM, one word is programmed during each operation. Working register, W0, is used as a temporary holding register for the data to be programmed.

Table 3-6 provides the ICSP programming details for writing data EEPROM.

Note: The TBLPAG register is hard-coded to 0x7F (the upper byte address of all locations of data EEPROM).

# FIGURE 3-9: PROGRAM DATA EEPROM MEMORY FLOW

| Command<br>(Binary) | Data<br>(Hex)    |              | Description                                                       |

|---------------------|------------------|--------------|-------------------------------------------------------------------|

| Step 1: Exit t      | he Reset veo     | tor.         |                                                                   |

| 0000                | 000000           | NOP          |                                                                   |

| 0000                | 040200           | GOTO         | 0x200                                                             |

| 0000                | 000000           | NOP          |                                                                   |

| Step 2: Set the     | ne NVMCON        | to program   | 1 data word.                                                      |

| 0000                | 24004A           | MOV          | #0x4004, W10                                                      |

| 0000                | 883B0A           | MOV          | W10, NVMCON                                                       |

| Step 3: Initia      | lize the Write   | Pointer (W   | 7) for TBLWT instruction.                                         |

| 0000                | 2007F0           | MOV          | #0x7F, W0                                                         |

| 0000                | 880190           | MOV          | W0, TBLPAG                                                        |

| 0000                | 2FExx7           | MOV          | <pre>#<destinationaddress15:0>, W7</destinationaddress15:0></pre> |

| Step 4: Load        | W0 with the      | data word t  | o program and load the write latch.                               |

| 0000                | 2xxxx0           | MOV          | <pre>#<data_word_value>, W0</data_word_value></pre>               |

| 0000                | BB1B80           | TBLWTL       | WO, [W7++]                                                        |

| 0000                | 000000           | NOP          |                                                                   |

| 0000                | 000000           | NOP          |                                                                   |

| Step 5: Initia      | te the write c   | ycle.        |                                                                   |

| 0000                | A8E761           | BSET         | NVMCON, #WR                                                       |

| 0000                | 000000           | NOP          |                                                                   |

| 0000                | 000000           | NOP          |                                                                   |

| Step 6: Repe        | eat this step to | o poll the W | R bit (bit 15 of NVMCON) until it is cleared by the hardware.     |

| 0000                | 040200           | GOTO         | 0x200                                                             |

| 0000                | 000000           | NOP          |                                                                   |

| 0000                | 803B02           | MOV          | NVMCON, W2                                                        |

| 0000                | 883C22           | MOV          | W2, VISI                                                          |

| 0000                | 000000           | NOP          |                                                                   |

| 00001               | <visi></visi>    |              | contents of the VISI register.                                    |

| 0000                | 000000           | NOP          |                                                                   |

| Step 7: Rese        | et device inter  | nal PC.      |                                                                   |

| 0000                | 040200           | GOTO         | 0x200                                                             |

| 0000                | 000000           | NOP          |                                                                   |

| Step 8: Repe        | eat Steps 4 th   | rough 7 unt  | il the entire data EEPROM memory is programmed.                   |

# TABLE 3-6: INSTRUCTION EXECUTION FOR WRITING DATA EEPROM

# 3.8 Writing Configuration Registers

The procedure for writing the Configuration registers is the same as for writing code memory. The only difference is that, only one word is programmed in each operation. When writing Configuration registers, one word is programmed during each operation, only working register, W0, is used as a temporary holding register for the data to be programmed.

Table 3-7 provides the default values of the Configuration registers.

**Note:** The TBLPAG register is hard-coded to 0xF8 (the upper byte address of all locations of the Configuration registers).

Table 3-7 provides the ICSP programming details for programming the Configuration registers, including the serial pattern with the ICSP command code, which must be transmitted LSB first using the PGCx and PGDx pins (see Figure 3-2). In Step 1 of Table 3-8, the Reset vector is exited. In Step 2, the NVMCON register is initialized for programming code memory. In Step 3, the 24-bit starting destination address for programming is loaded into the TBLPAG register and W7 register.

Note: The TBLPAG register must be loaded with F8h.

#### TABLE 3-7: DEFAULT VALUES FOR CONFIGURATION REGISTER SERIAL INSTRUCTION

| Configuration<br>Registers | Value |

|----------------------------|-------|

| FBS <sup>(3)</sup>         | 0Fh   |

| FGS                        | 03h   |

| FOSCSEL                    | 87h   |

| FOSC                       | FFh   |

| FWDT                       | DFh   |

| FPOR <sup>(1)</sup>        | FBh   |

| FICD <sup>(2,3)</sup>      | C3h   |

| FDS <sup>(4)</sup>         | FFh   |

Note 1: The I2C2SEL bit (FPOR<4>) is not implemented on PIC24FXXKAX01 and PIC24FXXKAX00 devices and should be programmed as '1'.

- 2: The FICD<6> bit is a reserved bit and should be programmed as '1'.

- 3: The Configuration registers, FBS and FICD, are reserved locations on PIC24F04KA2XX devices, and should be programmed with the default value given above.

- 4: The RTCSOSC bit (FDS<5>) is not implemented on PIC24F04KA2XX devices, and should be programmed as '1'.

| Command<br>(Binary) | Data<br>(Hex)         |                 | Command<br>(Binary)                                |

|---------------------|-----------------------|-----------------|----------------------------------------------------|

| Step 1: Exit the    | e Reset vector.       |                 |                                                    |

| 0000                | 000000                | NOP             |                                                    |

| 0000                | 040200                | GOTO            | 0x200                                              |

| 0000                | 000000                | NOP             |                                                    |

| Step 2: Initializ   | the Write Pointe      | er (W7) for the | TBLWT instruction.                                 |

| 0000                | 200007                | MOV             | #0x0000, W7                                        |

| Step 3: Set the     | e NVMCON registe      | er to program   | Configuration registers.                           |

| 0000                | 24004A                | MOV             | #0x4004, W10                                       |

| 0000                | 883B0A                | MOV             | W10, NVMCON                                        |

| Step 4: Initializ   | the TBLPAG reg        | gister.         |                                                    |

| 0000                | 200F80                | MOV             | #0xF8, W6                                          |

| 0000                | 880190                | MOV             | W0, TBLPAG                                         |

| Step 5: Load t      | he Configuration r    | egister data to | o W6.                                              |

| 0000                | 2xxxx6                | MOV             | <pre>#<fbs_value>, W6</fbs_value></pre>            |

| Step 6: Write t     | he Configuration r    | egister data to | o the write latch and increment the Write Pointer. |

| 0000                | 000000                | NOP             |                                                    |

| 0000                | BB1B96                | TBLWTL          | W6, [W7++]                                         |

| 0000                | 000000                | NOP             |                                                    |

| 0000                | 000000                | NOP             |                                                    |

| Step 7: Initiate    | the write cycle.      |                 |                                                    |

| 0000                | A8E761                | BSET            | NVMCON, #WR                                        |

| 0000                | 000000                | NOP             |                                                    |

| 0000                | 000000                | NOP             |                                                    |

| Step 8: Repea       | t this step to poll t | he WR bit (bit  | 15 of NVMCON) until it is cleared by the hardware. |

| 0000                | 040200                | GOTO            | 0x200                                              |

| 0000                | 000000                | NOP             |                                                    |

| 0000                | 803B02                | MOV             | NVMCON, W2                                         |

| 0000                | 883C22                | MOV             | W2, VISI                                           |

| 0000                | 000000                | NOP             |                                                    |

| 0001                | <visi></visi>         | Clock out o     | contents of the VISI register.                     |

| 0000                | 000000                | NOP             |                                                    |

| Step 9: Reset       | device internal PC    |                 |                                                    |

| 0000                | 040200                | GOTO            | 0x200                                              |

|                     | 000000                | NOP             |                                                    |

### TABLE 3-8: SERIAL INSTRUCTION EXECUTION FOR WRITING CONFIGURATION REGISTERS

# 3.9 Reading Code Memory

To read the code memory, execute a series of TBLRD instructions and clock out the data using the REGOUT command.

Table 3-9 provides the ICSP programming details for reading code memory. In Step 1, the Reset vector is exited. In Step 2, the 24-bit starting source address for reading is loaded into the TBLPAG register and the W6 register. The upper byte of the starting source address is stored in TBLPAG, and the lower 16 bits of the source address are stored in W6.

To minimize the reading time, the packed instruction word format, which was used for writing, is also used for reading (see Figure 3-7). In Step 3, the Write Pointer, W7, is initialized. In Step 4, two instruction words are read from code memory, and clocked out of the device through the VISI register, using the REGOUT command. Step 4 is repeated until the required amount of code memory is read.

| TABLE 3-9: | SERIAL INSTRUCTION EXECUTION FOR READING CODE MEMORY |

|------------|------------------------------------------------------|

|            |                                                      |

| Command<br>(Binary) | Data<br>(Hex)    | Description                                                                          |

|---------------------|------------------|--------------------------------------------------------------------------------------|

| Step 1: Exit Re     | eset vector.     |                                                                                      |

| 0000                | 000000           | NOP                                                                                  |

| 0000                | 040200           | GOTO 0x200                                                                           |

| 0000                | 000000           | NOP                                                                                  |

| Step 2: Initializ   | ze TBLPAG and    | the Read Pointer (W6) for TBLRD instruction.                                         |

| 0000                | 200xx0           | MOV # <sourceaddress23:16>, W0</sourceaddress23:16>                                  |

| 0000                | 880190           | MOV W0, TBLPAG                                                                       |

| 0000                | 2xxxx6           | MOV # <sourceaddress15:0>, W6</sourceaddress15:0>                                    |

| Step 3: Initializ   | ze the Write Poi | nter (W7) to point to the VISI register.                                             |

| 0000                | 207847           | MOV #VISI, W7                                                                        |

| 0000                | 000000           | NOP                                                                                  |

| Step 4: Read        | and clock out t  | he contents of the next two locations of code memory through the VISI register using |

|                     | EGOUT comma      |                                                                                      |

| 0000                | BA1B96           | TBLRDL [W6], [W7]                                                                    |

| 0000                | 000000           | NOP                                                                                  |

| 0000                | 000000           | NOP                                                                                  |

| 0001                | <visi></visi>    | Clock out contents of VISI register.                                                 |

| 0000                | 000000           | NOP                                                                                  |

| 0000                | BADBB6           | TBLRDH [W6++], [W7]                                                                  |

| 0000                | 000000           | NOP                                                                                  |

| 0000                | 000000           | NOP                                                                                  |

| 0000                | BAD3D6           | TBLRDH.B [++W6], [W7]                                                                |

| 0000                | 000000           | NOP                                                                                  |

| 0000                | 000000           | NOP                                                                                  |

| 0001                | <visi></visi>    | Clock out contents of VISI register.                                                 |

| 0000                | 000000           | NOP                                                                                  |

| 0000                | BA0BB6           | TBLRDL [W6++], [W7]                                                                  |

| 0000                | 000000           | NOP                                                                                  |

| 0000                | 000000           | NOP                                                                                  |

| 0001                | <visi></visi>    | Clock out contents of VISI register.                                                 |

| 0000                | 000000           | NOP                                                                                  |

| Step 5: Reset       | device internal  | PC.                                                                                  |

| 0000                | 040200           | GOTO 0x200                                                                           |

| 0000                | 000000           | NOP                                                                                  |

| Step 6: Repea       | t Steps 4 and 5  | until the required code memory is read.                                              |

# 3.10 Reading Data EEPROM Memory

The procedure for reading data EEPROM memory is the same as reading the code memory. The only difference is that the 16-bit data words are read instead of the 24-bit words. Table 3-10 provides the ICSP programming details for reading data memory.

Note: The TBLPAG register is hard-coded to 0x7F (the upper byte address of all locations of data memory).

# TABLE 3-10: SERIAL INSTRUCTION EXECUTION FOR READING DATA EEPROM MEMORY

| Command<br>(Binary) | Data<br>(Hex)      |              | Description                                                          |

|---------------------|--------------------|--------------|----------------------------------------------------------------------|

| Step 1: Exit R      | eset vector.       |              |                                                                      |

| 0000                | 000000             | NOP          |                                                                      |

| 0000                | 040200             | GOTO         | 0x200                                                                |

| 0000                | 000000             | NOP          |                                                                      |

| Step 2: Initializ   | ze TBLPAG and      | the Read P   | Cointer (W6) for TBLRD instruction.                                  |

| 0000                | 2007F0             | MOV          | #0x7F, W0                                                            |

| 0000                | 880190             | MOV          | W0, TBLPAG                                                           |

| 0000                | 2FExx6h            | MOV          | <pre>#<sourceaddress15:0>, W6;(FExx)</sourceaddress15:0></pre>       |

| Step 3: Initializ   | ze the Write Poi   | nter (W7) to | point to the VISI register.                                          |

| 0000                | 207847             | MOV          | #VISI, W7                                                            |

| 0000                | 000000             | NOP          |                                                                      |

| Step 4: Read        | and clock out t    | he contents  | of the next location of data EEPROM memory through the VISI register |

| using               | the REGOUT of      | command.     |                                                                      |

| 0000                | BA1B96             | TBLRDL       | [W6++], [W7]                                                         |

| 0000                | 000000             | NOP          |                                                                      |

| 0000                | 000000             | NOP          |                                                                      |

| 0001                | <visi></visi>      | Clock out o  | contents of VISI register.                                           |

| 0000                | 000000             | NOP          |                                                                      |

| Step 5: Repea       | at Step 4 until th | e required d | ata EEPROM memory is read.                                           |

| Step 6: Reset       | device internal    | PC.          |                                                                      |

| 0000                | 040200             | GOTO         | 0x200                                                                |

| 0000                | 000000             | NOP          |                                                                      |

# 3.11 Reading Configuration Memory

The procedure for reading a Configuration register is the same as reading the code memory. The only difference is that the 16-bit data words are read (with the upper byte read being all '0's) instead of the 24-bit words. There are eight Configuration registers and they are read one register at a time. Table 3-11 provides the ICSP programming details for reading all of the Configuration registers.

Note: The TBLPAG register should be hard-coded to 0xF8 (the upper byte address of the Configuration register) and the Read Pointer, W6, is initialized to 0x00h.

# TABLE 3-11: SERIAL INSTRUCTION EXECUTION FOR READING ALL THE CONFIGURATION REGISTERS

| Command<br>(Binary) | Data<br>(Hex)                                                                     | Description |                                                                                 |  |

|---------------------|-----------------------------------------------------------------------------------|-------------|---------------------------------------------------------------------------------|--|

| Step 1: Exit Re     | eset vector.                                                                      |             |                                                                                 |  |

| 0000                | 000000                                                                            | NOP         |                                                                                 |  |

| 0000                | 040200                                                                            | GOTO        | 0x200                                                                           |  |

| 0000                | 000000                                                                            | NOP         |                                                                                 |  |

| Step 2: Initializ   | e TBLPAG, the                                                                     | Read Pointe | er (W6) and the Write Pointer (W7) for TBLRD instruction.                       |  |

| 0000                | 200F80                                                                            | MOV         | #0xF8, W0                                                                       |  |

| 0000                | 880190                                                                            | MOV         | W0, TBLPAG                                                                      |  |

| 0000                | 200007                                                                            | MOV         | #0x0000,W6                                                                      |  |

| 0000                | 207847                                                                            | MOV         | #VISI, W7                                                                       |  |

| 0000                | 000000                                                                            | NOP         |                                                                                 |  |

|                     | the Configurati register using th                                                 |             | and write it to the VISI register (located at 784h), and clock out the command. |  |

| 0000                | BA0BB6                                                                            | TBLRDL      | [W6++], [W7]                                                                    |  |

| 0000                | 000000                                                                            | NOP         |                                                                                 |  |

| 0000                | 000000                                                                            | NOP         |                                                                                 |  |

| 0001                | <visi></visi>                                                                     | Clock out c | contents of VISI register.                                                      |  |

| Step 4: Repea       | Step 4: Repeat Step 3 to read other fuses. Load W6 with their respective address. |             |                                                                                 |  |

| Step 5: Reset       | device internal I                                                                 | °C.         |                                                                                 |  |

| 0000                | 040200                                                                            | GOTO        | 0x200                                                                           |  |

| 0000                | 000000                                                                            | NOP         |                                                                                 |  |

|                     |                                                                                   |             |                                                                                 |  |

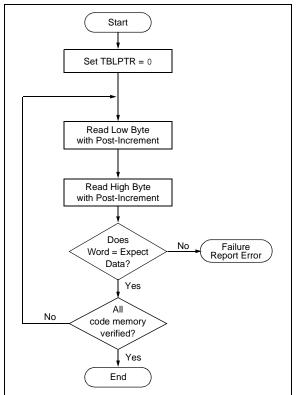

# 3.12 Verifying Code Memory, Data EEPROM Memory and Configuration Registers

To verify the code memory, read the code memory space and compare it with the copy held in the programmer's buffer. To verify the data EEPROM and Configuration registers, follow the similar procedure.

Figure 3-10 illustrates the verify process flowchart. Memory reads occur 1 byte at a time, hence 2 bytes must be read to compare with the word in the programmer's buffer. Refer to **Section 3.9 "Reading Code Memory"** for implementation details of reading code memory. On the same lines, the data EEPROM and Configuration registers can be verified.

| Note: | Code     | memory        |              |         |             |

|-------|----------|---------------|--------------|---------|-------------|

|       |          | iately after  |              |         |             |

|       | is enat  | oled. Since   | Configura    | ation   | registers   |

|       | include  | the device    | code pro     | tectio  | n bit, the  |

|       | device   | will not be r | eadable c    | or veri | fiable if a |

|       | device   | Reset occu    | irs after th | e cod   | e-protect   |

|       | bits are | e set (value  | = 0).        |         |             |

#### FIGURE 3-10: VERIFY CODE MEMORY FLOW

# 3.13 Reading the Application ID Word

The Application ID Word is stored in address 8005BEh in the executive code memory. To read this memory location, use the SIX control code to move this program memory location to the VISI register. Then, the REGOUT control code must be used to clock the contents of the VISI register out of the device. Table 3-12 provides the corresponding control and instruction codes that must be serially transmitted to the device to perform this operation.

After the programmer has clocked out the Application ID Word, it must be inspected. If the Application ID has the value, BBh, the programming executive resides in the memory and the device can be programmed using the mechanism described in **Section 4.0 "Device Programming – Enhanced ICSP**". However, if the Application ID has any other value, the programming executive does not reside in the memory; it must be loaded to memory before the device can be programmed. **Section 5.4 "Programming the Programming Executive to Memory"** describes the procedure for loading the programming executive to memory.

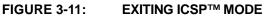

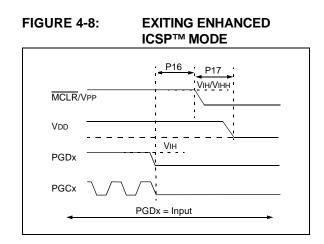

# 3.14 Exiting ICSP Mode

Exit the Program/Verify mode by removing VIH from MCLR/VPP as illustrated in Figure 3-11. The only requirement to exit is that an interval of P16 should elapse between the last clock and program signals on PGCx and PGDx before removing VIH.

| TADLE J-12.         |                  |               |                                  |

|---------------------|------------------|---------------|----------------------------------|

| Command<br>(Binary) | Data<br>(Hex)    |               | Description                      |

| Step 1: Exit Re     | eset vector.     |               |                                  |

| 0000                | 000000           | NOP           |                                  |

| 0000                | 040200           | GOTO          | 0x200                            |

| 0000                | 000000           | NOP           |                                  |

| Step 2: Initializ   | e TBLPAG and t   | he Read Poi   | nter (W0) for TBLRD instruction. |

| 0000                | 200800           | MOV           | #0x80, W0                        |

| 0000                | 880190           | MOV           | W0, TBLPAG                       |

| 0000                | 205BE0           | MOV           | #0x5BE, W0                       |

| 0000                | 207841           | MOV           | #VISI, W1                        |

| 0000                | 000000           | NOP           |                                  |

| 0000                | BA0890           | TBLRDL        | [WO], [W1]                       |

| 0000                | 000000           | NOP           |                                  |

| 0000                | 000000           | NOP           |                                  |

| Step 3: Output      | the VISI registe | r using the R | EGOUT command.                   |

| 0001                | <visi></visi>    | Clock out of  | contents of the VISI register.   |

| 0000                | 000000           | NOP           | -                                |

# TABLE 3-12: SERIAL INSTRUCTION EXECUTION FOR READING THE APPLICATION ID WORD

# 4.0 DEVICE PROGRAMMING – ENHANCED ICSP

This section describes the programming of the device through Enhanced ICSP and the programming executive. The programming executive resides in the executive memory (separate from user memory space), and is executed when Enhanced ICSP Programming mode is entered. The programming executive provides the mechanism for the programmer (host device) to program and verify the PIC24FXXKAXXX devices using a simple command set and communication protocol. The basic functions provided by the programming executive are:

- Read Memory

- Program Memory

- · Blank Check

- Read Executive Firmware Revision

The programming executive performs the low-level tasks required for erasing, programming and verifying a device. This allows the programmer to program the device by issuing the appropriate commands and data.

Table 4-1 provides these commands. For detailed descriptions of each command, see **Section 5.2** "**Programming Executive Commands**".

TABLE 4-1: COMMAND SET SUMMARY

| Command | Description                                                              |

|---------|--------------------------------------------------------------------------|

| SCHECK  | Sanity check.                                                            |

| READC   | Read Device ID registers.                                                |

| READD   | Read data EEPROM memory.                                                 |

| READP   | Read Code register.                                                      |

| PROGC   | Write User ID.                                                           |

| PROGD   | Program and verify one word of data<br>EEPROM memory.                    |

| PROGP   | Program and verify one row of code memory or one Configuration register. |

| QBLANK  | Query if the code memory is blank.                                       |

| QVER    | Query the software version.                                              |

The programming executive uses the device's data RAM for variable storage and program execution. After the programming executive is run, no assumptions should be made about the contents of the data RAM.

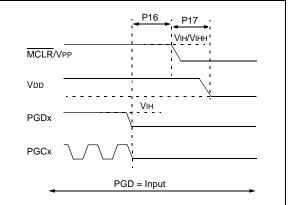

# 4.1 Overview of the Programming Process

Figure 4-1 illustrates the high-level overview of the programming process.

Perform the following steps:

- 1. Enter ICSP mode.

- 2. Erase the device.

- 3. Verify the programming executive.

- 4. Exit ICSP mode.

- 5. Enter Enhanced ICSP mode.

- 6. Program the code memory.

- 7. Verify the code memory.

- 8. Program the Configuration registers.

- 9. Verify the Configuration registers.

Steps 7 and 9 ensure that the programming was successful.

After the programming executive is verified in memory (or loaded if not present), the PIC24FXXKAXXX family can be programmed using the command set provided in Table 4-1.

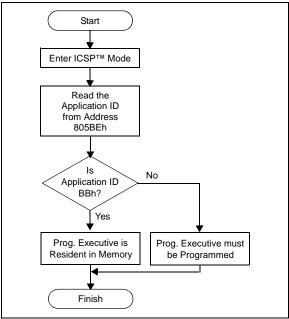

# 4.2 Confirming the Presence of the Programming Executive

Before beginning programming, confirm if the programming executive is stored in the executive memory and perform the following:

- 1. Enter In-Circuit Serial Programming mode (ICSP).

- 2. Read the unique Application ID Word stored in the executive memory.

Figure 4-2 illustrates this procedure.

If the programming executive is resident, the Application ID Word is BBh, which means programming can resume as normal. However, if the Application ID Word is not BBh, the programming executive must be programmed to executive code memory using the method described in Section 5.4 "Programming the Programming Executive to Memory".

Section 3.0 "Device Programming – ICSP" describes the ICSP programming method. Section 3.13 "Reading the Application ID Word" describes the procedure for reading the Application ID Word in ICSP mode.

### FIGURE 4-2: CONFIRMING PRESENCE OF PROGRAMMING EXECUTIVE

# 4.3 Entering Enhanced ICSP Mode

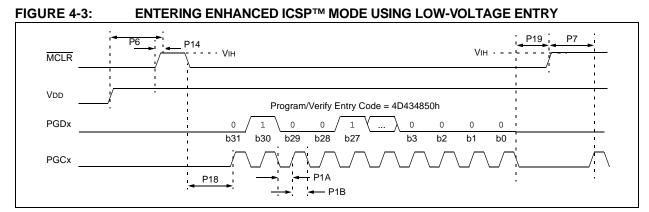

# 4.3.1 LOW-VOLTAGE ENTRY

Perform the following steps to enter Enhanced ICSP Program/Verify mode using MCLR:

- 1. Briefly drive the  $\overline{\text{MCLR}}$  pin high, and then low.

- 2. Clock a 32-bit key sequence into PGDx.

- 3. Drive the MCLR high within a specified period and continue to hold high.

Figure 4-3 illustrates this procedure.

The programming voltage applied to  $\overline{\text{MCLR}}$  is VIH, which is essentially VDD in the case of PIC24FXXKAXXX devices. There is no minimum time requirement for holding at VIH. After VIH is removed, an interval of at least P18 must elapse before presenting the key sequence on PGDx.

The key sequence is a specific 32-bit pattern: '0100 1101 0100 0011 0100 1000 0101 0000' (more easily remembered as 4D434850h in hexadecimal format). The device will enter Program/Verify mode only if the key sequence is valid. The MSB of the most significant nibble must be shifted in first.

Once the key sequence is complete, VIH must be applied to MCLR and held at that level for as long as the Program/Verify mode is to be maintained. An interval of at least P19 and P7 must elapse before presenting data on PGDx. Signals appearing on PGDx before P7 has elapsed will not be interpreted as valid.

# 4.3.2 HIGH-VOLTAGE ENTRY

The procedure for entering Enhanced ICSP Program/Verify mode using the VPP pin is the same as entering the mode using MCLR. The only differences are that the programming voltage applied to VPP is VIHH, and before presenting the key sequence on PGDx, an interval of at least P18 should elapse. Figure 4-4 illustrates this procedure.

Once the key sequence is complete, an interval of at least P19 should elapse and the VIHH should be reduced to VIH. The voltage, VIH, must be applied to VPP and held at that level for as long as the Program/Verify mode is to be maintained. An interval of at least P19 and P7 should elapse before presenting data on PGDx.

Signals appearing on PGDx before P7 has elapsed will not be interpreted as valid.

On successful entry, the program memory can be accessed and programmed in serial fashion. While in the Program/Verify mode, all unused I/Os are placed in the high-impedance state.

# 4.4 Blank Check

The term "Blank Check" implies verifying if the device has been successfully erased and has no programmed memory locations. A blank or erased memory location is always read as '1'.

The Device ID registers (FF0002h:FF0000h) can be ignored by the Blank Check as this region stores device information that cannot be erased. The device Configuration registers are also ignored by the Blank Check. Additionally, all unimplemented memory space should be ignored by the Blank Check.

The QBLANK command is used for the Blank Check. It determines if the code memory is erased by testing these memory regions. A 'BLANK' or 'NOT BLANK' response is returned. If it is determined that the device is not blank, it must be erased before attempting to program the device.

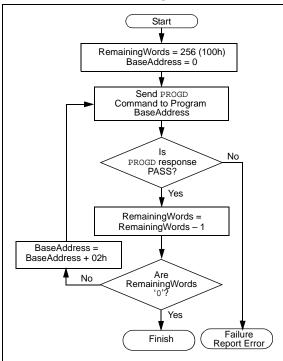

# 4.5 Code Memory Programming

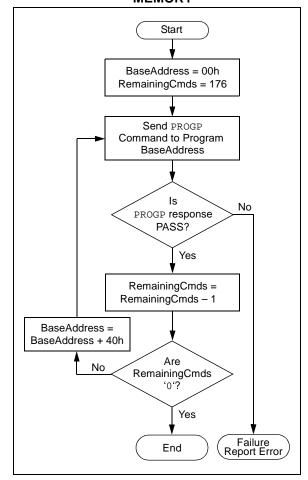

### 4.5.1 PROGRAMMING METHODOLOGY

Code memory is programmed with the PROGP command. PROGP programs one row of code memory, starting from the memory address specified in the command. The number of PROGP commands required to program a device depends on the number of write blocks that must be programmed in the device.

Figure 4-5 illustrates an example flowchart for programming code memory. In this example, all 5.5K instruction words of a PIC24FXXKAXXX device are programmed.