### PIC16F88X

## PIC16F88X Family Silicon Errata and Data Sheet Clarification

The PIC16F88X family devices that you have received conform functionally to the current Device Data Sheet (DS41291F), except for the anomalies described in this document.

The silicon issues discussed in the following pages are for silicon revisions with the Device and Revision IDs listed in Table 1. The silicon issues are summarized in Table 2.

The errata described in this document will be addressed in future revisions of the PIC16F88X silicon.

Note: This document summarizes all silicon errata issues from all revisions of silicon, previous as well as current. Only the issues indicated in the last column of Table 2 apply to the current silicon revision (A0 or A2, as applicable).

Data Sheet clarifications and corrections start on page 13, following the discussion of silicon issues.

The silicon revision level can be identified using the current version of MPLAB<sup>®</sup> IDE and Microchip's programmers, debuggers, and emulation tools, which are available at the Microchip corporate web site (www.microchip.com).

For example, to identify the silicon revision level using MPLAB IDE in conjunction with MPLAB ICD 2, MPLAB ICD 3, PICkit<sup>TM</sup> 2 or PICkit<sup>TM</sup> 3:

- Using the appropriate interface, connect the device to the MPLAB ICD 2 programmer/ debugger, PICkit™ 2 or PICkit™ 3.

- From the main menu in MPLAB IDE, select <u>Configure>Select Device</u>, and then select the target part number in the dialog box.

- Select the MPLAB hardware tool (<u>Programmer>Select Tool</u>).

- Perform a "Connect" operation to the device (<u>Programmer>Connect</u>). Depending on the development tool used, the part number and Device Revision ID value appear in the **Output** window.

**Note:** If you are unable to extract the silicon revision level, please contact your local Microchip sales office for assistance.

The Device ID values for the various devices and silicon revisions are shown in Table 1.

TABLE 1: SILICON DEVREY VALUES

| Part Number | Device ID <sup>(1)</sup> | Revision ID for Silicon Revision <sup>(2)</sup> |     |  |

|-------------|--------------------------|-------------------------------------------------|-----|--|

| Part Number | Device ID.               | A0                                              | A2  |  |

| PIC16F882   | 2000h                    | 00h                                             |     |  |

| PIC16F883   | 2020h                    | 00h                                             |     |  |

| PIC16F884   | 2040h                    | 00h                                             |     |  |

| PIC16F886   | 2060h                    |                                                 | 02h |  |

| PIC16F887   | 2080h                    |                                                 | 02h |  |

Note 1: The device and revision data is stored in the Device ID located at 2006h in program memory.

2: Refer to the "PIC16F88X Memory Programming Specification" (DS41287) for detailed information.

TABLE 2: SILICON ISSUE SUMMARY (PIC16F882)

| Na - ded - | Factoria                 | Item   |                                               | Affected Revisions <sup>(1)</sup> |

|------------|--------------------------|--------|-----------------------------------------------|-----------------------------------|

| Module     | Feature                  | Number | Issue Summary                                 | A0                                |

| LVP        | Programming              | 1.     | Programming disruption                        | Х                                 |

| MSSP       | SPI Master               | 2.     | SPI using Timer2/2                            | X                                 |

| ADC        | VP6 Reference            | 3.     | Disruption of the HFINTOSC                    | X                                 |

| MSSP       | SPI Master               | 4.     | Write collision on loading                    | X                                 |

| MSSP       | I <sup>2</sup> C™ Slave  | 5.     | R/W bit on ACK                                | X                                 |

| MSSP       | I <sup>2</sup> C™ Master | 6.     | Clock-stretching handling                     | Х                                 |

| MSSP       | SPI Slave                | 7.     | Multi-byte transmission                       | X                                 |

| Timer1     | Ext. Crystal             | 8.     | Overflow may take additional count            | X                                 |

| Timer1     | Ext. Crystal             | 9.     | Oscillator may stop running at low temps.     | X                                 |

| Timer0     | Prescaler                | 10.    | Spurious Reset                                | X                                 |

| MSSP       | SPI Master               | 11.    | Disabling the module generates a clock pulse. | Х                                 |

**Note 1:** Only those issues indicated in the last column apply to the current silicon revision.

TABLE 3: SILICON ISSUE SUMMARY (PIC16F883/PIC16F884)

| NA - ded - | Factoria                 | Item   |                                               | Affected Revisions <sup>(1)</sup> |

|------------|--------------------------|--------|-----------------------------------------------|-----------------------------------|

| Module     | Feature                  | Number | Issue Summary                                 | A0                                |

| LVP        | Programming              | 1.     | Programming disruption                        | Х                                 |

| MSSP       | SPI Master               | 2.     | SPI using Timer2/2                            | Х                                 |

| ADC        | VP6 Reference            | 3.     | Disruption of the HFINTOSC                    | Х                                 |

| MSSP       | SPI Master               | 4.     | Write collision on loading                    | X                                 |

| MSSP       | I <sup>2</sup> C™ Slave  | 5.     | R/W bit on ACK                                | Х                                 |

| MSSP       | I <sup>2</sup> C™ Master | 6.     | Clock-stretching handling                     | Х                                 |

| MSSP       | SPI Slave                | 7.     | Multi-byte transmission                       | X                                 |

| Timer1     | Ext. Crystal             | 8.     | Overflow may take additional count            | Х                                 |

| Timer1     | Ext. Crystal             | 9.     | Oscillator may stop running at low temps.     | Х                                 |

| Timer0     | Prescaler                | 10.    | Spurious Reset                                | Х                                 |

| MSSP       | SPI Master               | 11.    | Disabling the module generates a clock pulse. | Х                                 |

Note 1: Only those issues indicated in the last column apply to the current silicon revision.

TABLE 4: SILICON ISSUE SUMMARY (PIC16F886/PIC16F887)

| NA o alcal o | Factoria                 | Item   | January 0                                     | Affected Revisions <sup>(1)</sup> |

|--------------|--------------------------|--------|-----------------------------------------------|-----------------------------------|

| Module       | Feature                  | Number | Issue Summary                                 | A2                                |

| LVP          | Programming              | 1.     | Programming disruption                        | Х                                 |

| MSSP         | SPI Master               | 2.     | SPI using Timer2/2                            | Х                                 |

| ADC          | VP6 Reference            | 3.     | Disruption of the HFINTOSC                    | Х                                 |

| MSSP         | SPI Master               | 4.     | Write collision on loading                    | Х                                 |

| MSSP         | I <sup>2</sup> C™ Slave  | 5.     | R/W bit on ACK                                | Х                                 |

| MSSP         | I <sup>2</sup> C™ Master | 6.     | Clock-stretching handling                     | Х                                 |

| MSSP         | SPI Slave                | 7.     | Multi-byte transmission                       | X                                 |

| Timer1       | Ext. Crystal             | 8.     | Overflow may take additional count            | Х                                 |

| Timer1       | Ext. Crystal             | 9.     | Oscillator may stop running at low temps.     | Х                                 |

| Timer0       | Prescaler                | 10.    | Spurious Reset                                | Х                                 |

| MSSP         | SPI Master               | 11.    | Disabling the module generates a clock pulse. | Х                                 |

**Note 1:** Only those issues indicated in the last column apply to the current silicon revision.

#### Silicon Errata Issues

Note:

This document summarizes all silicon errata issues from all revisions of silicon, previous as well as current. Only the issues indicated by the shaded column in the following tables apply to the current silicon revision (A0 or A2, as applicable).

### 1. Module: Low-Voltage In-Circuit Serial Programming™ (LVD)

If LVP (Low-Voltage Programming) mode is enabled, programming the device using the VPP pin while holding high or toggling the port pin RB3/PGM during Program mode could disrupt the programming sequence.

#### Work around

Pull down pin RB3/PGM using external circuitry during programming of the device.

#### **Affected Silicon Revisions**

#### PIC16F882

| Α0 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

#### PIC16F883/PIC16F884

| Α0 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

#### PIC16F886/PIC16F887

| A2 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

#### 2. Module: MSSP (SPI Mode)

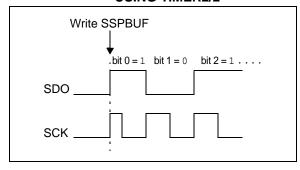

When the SPI is using Timer2/2 as the clock source, a shorter than expected SCK pulse may occur on the first bit of the transmitted/received data (Figure 1).

### FIGURE 1: SCK PULSE VARIATION USING TIMER2/2

#### Work around

To avoid producing the short pulse, turn off Timer2 and clear the TMR2 register, load the SSPBUF with the data to transmit and then turn Timer2 back on. Refer to Example 1 for sample code.

### EXAMPLE 1: AVOIDING THE INITIAL SHORT SCK PULSE

|      |       |               | 0-0-              |

|------|-------|---------------|-------------------|

| LOOP | BTFSS | SSPSTAT, BF   | ;Data received?   |

|      |       |               | ;(Xmit complete?) |

|      | GOTO  | LOOP          | ;No               |

|      | MOVF  | SSPBUF, W     | ;W = SSPBUF       |

|      | MOVWF | RXDATA        | ;Save in user RAM |

|      | MOVF  | TXDATA, W     | ;W = TXDATA       |

|      | BCF   | T2CON, TMR2ON | ;Timer2 off       |

|      | CLRF  | TMR2          | ;Clear Timer2     |

|      | MOVWF | SSPBUF        | ;Xmit New data    |

|      | BSF   | T2CON, TMR2ON | ;Timer2 on        |

|      |       |               |                   |

#### **Affected Silicon Revisions**

#### PIC16F882

| A0 |  |  |  |

|----|--|--|--|

| X  |  |  |  |

#### PIC16F883/PIC16F884

| Α0 |  |  |  |  |

|----|--|--|--|--|

| Х  |  |  |  |  |

| A2 |  |  |  |  |

|----|--|--|--|--|

| Х  |  |  |  |  |

### 3. Module: Analog-To-Digital Converter (ADC) Module

Selecting the VP6 reference as the analog input source (CHS<3:0>=1111) for the ADC conversion after sampling another analog channel with input voltages approximately greater than 3.6V can temporarily disturb the HFINTOSC oscillator.

Note:

This only occurs when selecting the VP6 reference ADC channel using the CHS<3:0> bits in the ADCON0 register and NOT during the start of an actual ADC conversion using the GO/DONE bit in the ADCON0 register.

#### Work around

Select an ADC channel with input voltages lower than 3.6V prior to selecting the VP6 reference voltage input. Any analog channel can be used, even if that channel is configured as a digital I/O (configured as an output) that is driving the output pin low. An alternative is to configure the CVREF module to output a voltage less than 3.6V and then selecting that analog channel CHS<3:0> = 1110 as the analog input source.

### EXAMPLE 2: AVOID DISTURBING THE HFINTOSC OSCILLATOR

BANKSEL ADCONO ;

MOVLW B'XX111001' ;Select ADC

MOVWF ADCONO ;Channel CVREF

MOVLW B'XX111101' ;Select ADC

MOVWF ADCONO ;Channel VP6

#### **Affected Silicon Revisions**

#### PIC16F882

| Α0 |  |  |  |  |

|----|--|--|--|--|

| Х  |  |  |  |  |

#### PIC16F883/PIC16F884

| A0 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

#### PIC16F886/PIC16F887

| A2 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

#### 4. Module: MSSP (SPI Master Mode)

With MSSP in SPI Master mode, Fosc/64 or Timer2/2 clock rate and CKE = 0, a write collision may occur if SSPBUF is loaded immediately after the transfer is complete. A delay may be required after the MSSP Interrupt Flag bit, SSPIF, is set or the Buffer Full bit, BF, is set and before writing SSPBUF. If the delay is insufficiently short, a write collision may occur as indicated by the WCOL bit being set.

#### Work around

Add a software delay of one SCK period after detecting the completed transfer and prior to updating the SSPBUF contents. Verify the WCOL bit is clear after writing SSPBUF. If the WCOL is set, clear the bit in software and rewrite the SSPBUF register.

#### **Date Codes that pertain to this issue:**

All engineering and production devices.

#### **Affected Silicon Revisions**

#### PIC16F882

| A0 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

#### PIC16F883/PIC16F884

| A0 |  |  |  |  |

|----|--|--|--|--|

| Х  |  |  |  |  |

| A2 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

#### 5. Module: MSSP (I<sup>2</sup>C™ Slave Mode)

When the master device wants to terminate receiving any more data from the slave device, it will do so by sending a NACK in response to the last data byte received from the slave. When the slave receives the NACK, the R/W bit of the SSPSTAT register remains set improperly.

#### Work around

Use the CKP bit of the SSPCON register to determine when the master has responded with a NACK. The CKP bit will be clear when the response is an ACK, and set when the response is a NACK. The CKP bit is automatically cleared to stretch the clock when the master responds to received data with an ACK. This gives the slave time to load the SSPBUF register before setting the CKP bit to release the clock stretching. When the master responds to received data with a NACK the CKP bit properly remains set, and there is no clock stretching.

#### **Affected Silicon Revisions**

| Ы  | IC1 | 6F | 882 |

|----|-----|----|-----|

| ГΙ | ı   | UΓ | 002 |

| Α0 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

#### PIC16F883/PIC16F884

| Α0 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

| A2 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

#### 6. Module: MSSP (I<sup>2</sup>C™ Master Mode)

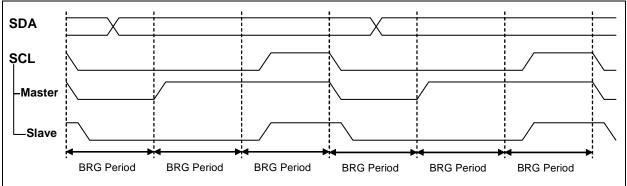

When the MSSP is  $I^2C^{TM}$  Master mode with a slave device stretching the clock, the clock generation does not function as described in the data sheet.

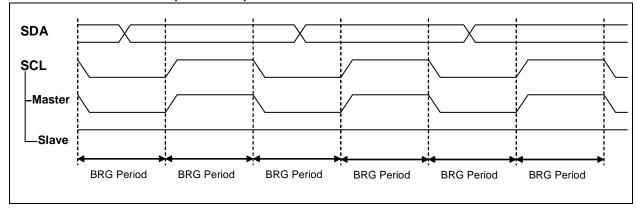

When a slave device is performing clock stretching by pulling the SCL line low, the master device should continuously sample the SCL line to determine when all slaves have released SCL. When SCL is released, the master device should wait one BRG period to ensure a constant SCL high time.

The current implementation does not ensure accurate SCL high time. During clock stretch, the MSSP device will erroneously continue running the BRG counter. At the end of the clock stretch the BRG counter continues to count down for the remainder of the BRG period, and then the MSSP device will immediately resume transmitting the data.

Figure 1 illustrates an expected I<sup>2</sup>C transmission in which the SCL line is completely controlled by the master device and the slave device does not attempt to stretch the clock period.

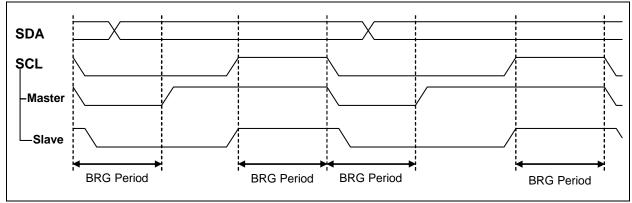

Figure 2 illustrates the expected operation of an I<sup>2</sup>C transmission in which the slave device has stretched the clock period by holding the SCL line low. The high time of the SCL pulse is constant, regardless of the duration of the clock stretch.

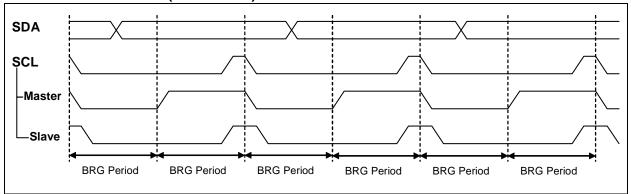

Figure 3 and Figure 4 illustrate an actual I<sup>2</sup>C transmission in which the slave has stretched the clock period by holding the SCL line low. Note that the high time of the SCL signal has shortened from the expected time.

FIGURE 1: ACTUAL (CORRECT) OPERATION WITHOUT CLOCK STRETCHING

FIGURE 2: EXPECTED OPERATION WITH CLOCK STRETCHING

#### FIGURE 4: ACTUAL (INCORRECT) OPERATION WITH CLOCK STRETCHING – EXAMPLE 2

#### Work around

Set the communication speed to match the slowest device on the bus. This ensures that no slave device will perform clock stretching.

It is possible to dynamically adjust the communication speed to match the device being addressed by modifying the BRG register. However, the behavior of slower slave devices must be understood and speed adjustments made such that no slave performs clock stretching.

#### **Affected Silicon Revisions**

#### PIC16F882

| Α0 |  |  |  |  |

|----|--|--|--|--|

| Х  |  |  |  |  |

#### PIC16F883/PIC16F884

| Α0 |  |  |  |  |

|----|--|--|--|--|

| Х  |  |  |  |  |

| A2 |  |  |  |  |

|----|--|--|--|--|

| Х  |  |  |  |  |

#### 7. Module: MSSP

When all of the following conditions are met:

- 1. The module is configured as a SPI slave

- 2. CKP = 1

- 3. CKE = 1

- 4. Multiple bytes are sent to the Slave with the SS line remaining low between bytes

The SSPIF flag will only be set on reception of the first byte and the following bytes will not be correctly received.

#### Work around

- SPI Master toggles the SS line between bytes

- On reception of the first byte modify the SSPM0 bit in the SSPCON register to configure the module as a SPI slave with SS pin disabled.

Then restore the SSPM0 bit to the configuration for SPI slave with SS pin enabled. The module is then ready for reception of the following byte.

BSF SSPCON, SSPM0 BCF SSPCON, SSPM0

#### **Affected Silicon Revisions**

#### PIC16F882

| A0 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

#### PIC16F883/PIC16F884

| A0 |  |  |  |  |

|----|--|--|--|--|

| Х  |  |  |  |  |

| A2 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

#### 8. Module: Asynchronous Timer1

This Errata supersedes Errata DS80233 and DS80329.

When TImer1 is started or updated, the timer needs to see a falling edge from the external clock source before a rising edge can increment the counter. If writes to TMR1H and TMR1L are not completed while the external clock pulse is still high, Timer1 will not count the first clock pulse after the update.

When using an external crystal, the pulse width from rising to falling edge is temperature dependent and may decrease with temperature. As a result, the timer may require an additional oscillation to overflow.

#### Work around

Switching to the HFINTOSC after reloading, the timer ensures the Timer1 will see a falling edge before switching back to the external clock source.

Due to the time from Timer1 overflow to the reload being application specific, wait for the timer to increment before beginning the reload sequence. This ensures the timer does not miss a rising edge during reload.

#### **EXAMPLE 3:**

```

BTFSC TMR1L,0

GOTO

$-1

BTFSS

TMR1L,0

;Timer has just incremented, 31 \mu s before next rising edge to

GOTO

$-1

;complete reload

Update:

T1CON, TMR1CS ; Select HFINTOSC for Timer1

BCF

TMR1H,7 ;Timer1 high byte 0x80

BSF

BCF

T1CON, TMR1ON

;Timer1 off

BSF

T1CON, TMR1CS

;Select external crystal

T1CON,TMR1ON ;Timer1 on

BCF

-Critical Timing of code sequence for instructions following last write to TMR1L or TMR1H.

```

#### **Affected Silicon Revisions**

#### PIC16F882

| Α0 |  |  |  |  |

|----|--|--|--|--|

| X  |  |  |  |  |

#### PIC16F883/PIC16F884

| Α0 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

| A2 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

### 9. Module: LP/Timer1 Oscillator Operation Below 25°C

1-2% of devices experience reduced drive as temperatures approach -40°C. This will result in a loss of Timer1 counts or stopped Timer1 oscillation.

This can also prevent Timer1 oscillator start-up under cold conditions.

#### Work around

Use of low-power crystals properly matched to the device will reduce the likelyhood of failure. A  $1m\Omega$  resister between OSC2 and VDD will further improve the drive strength of the circuit.

#### **Affected Silicon Revisions**

#### PIC16F882

| Α0 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

#### PIC16F883/PIC16F884

| Α0 |  |  |  |  |

|----|--|--|--|--|

| Х  |  |  |  |  |

#### PIC16F886/PIC16F887

| A2 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

### 10. Module: Timer0 and WDT Prescaler Assignment Spurious Reset

A spurious Reset may occur if the Timer0/ Watchdog Timer (WDT) prescaler is assigned from the WDT to Timer0 and then back to the WDT.

#### Summary

The issue only arises when all of the below conditions are met:

- Timer0 external clock input (TOCKI) is enabled.

- The Prescaler is assigned to the WDT, then to the Timer0 and back to the WDT.

- During the assignments, the TOCKI pin is high when bit TOSE is set, or low when TOSE is clear

- The 1:1 Prescaler option is chosen.

#### Description

On a POR, the Timer0/WDT prescaler is assigned to the WDT.

If the prescaler is reassigned to Timer0 and Timer0 external clock input (TOCKI) is enabled then the prescaler would be clocked by a transition on the TOCKI pin.

On power-up, the TOCKI pin is (by default) enabled for Timer0 in the OPTION register.

If the TOCKI pin is:

- High and Timer0 is configured to transition on a falling edge (TOSE set), or

- Low and Timer0 is configured to transition on a rising edge (TOSE clear)

Then, if the prescaler is reassigned to the WDT, a clock pulse to the prescaler will be generated on the reassignment.

If the prescaler is configured for the 1:1 option, the clock pulse will incorrectly cause a WDT Time-out Reset of the device.

#### Work around

- Disable the Timer0 external clock input by clearing the TOCKI bit in the OPTION register.

- Modify the TOSE bit in the OPTION register to the opposite configuration for the logic level on the TOCKI pin.

- 3. Select a prescaler rate other than 1:1 and issue a CLRWDT instruction before switching to the final prescaler rate.

#### **Affected Silicon Revisions**

#### PIC16F882

| Α0 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

#### PIC16F883/PIC16F884

| A0 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

| A2 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

#### 11. Module: MSSP (SPI Master Mode)

When the MSSP module is configured as a SPI master with CKP set, (SPI clock idles high) disabling the module by clearing the SSPEN bit will cause the clock line to be driven low for 2 Tosc before the setting of the RC3 output in the PORTC register takes effect.

Similarly on enabling the module. There is a 1 Tosc period where the clock line will be driven low before the CKP bit takes effect and the line is driven high.

#### Work around

A pull-up resistor on the SCK line allows the pin to be configured as high-impedance during disabling/ enabling the module and the line to be pulled high by the resistor.

The TRISC3 bit should be set before disabling or enabling the module to tristate the pin, and then cleared before transmission.

#### **Affected Silicon Revisions**

#### PIC16F882

| A0 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

#### PIC16F883/PIC16F884

| Α0 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

| A2 |  |  |  |  |

|----|--|--|--|--|

| Χ  |  |  |  |  |

#### **Data Sheet Clarifications**

The following typographical corrections and clarifications are to be noted for the latest version of the device data sheet (DS41291**F**):

**Note:** Corrections are shown in **bold**. Where possible, the original bold text formatting has been removed for clarity.

#### 1. Module: ADC (Block Diagram)

Figure 9-1: ADC Block Diagram changes references from AVss to Vss and AVDD to VDD.

#### 2. Module: ADC

Acquisition Time Example calculation correction.

#### **EQUATION 9-1: ACQUISITION TIME EXAMPLE**

Assumptions: Temperature =  $50^{\circ}$ C and external impedance of  $10k\Omega$  5.0V VDD

$$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$$

=  $TAMP + TC + TCOFF$

=  $2\mu s + TC + [(Temperature - 25°C)(0.05\mu s/°C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD}$$

;[1] VCHOLD charged to within 1/2 lsb

$$V_{APPLIED}\left(1-e^{\frac{-Tc}{RC}}\right) = V_{CHOLD}$$

;[2] VCHOLD charge response to VAPPLIED

$$V_{APPLIED}\left(1-e^{\frac{-Tc}{RC}}\right) = V_{APPLIED}\left(1-\frac{1}{(2^{n+1})-1}\right)$$

; combining [1] and [2]

Solving for TC:

$$TC = -C_{HOLD}(RIC + RSS + RS) \ln(1/2047)$$

$$= -10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)$$

$$= 1.37\mu s$$

Therefore:

$$TACQ = 2\mu s + 1.37\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.67\mu s

### APPENDIX A: DOCUMENT REVISION HISTORY

#### Rev. A Document (2/2007)

First revision of this document.

Added Module 1: Low-Voltage In-Circuit Serial Programming™ (PIC16F884/883 Silicon Rev. A0); Added Module 2: MSSP (SPI Mode).

Clarifications/Corrections to the Data Sheet - Added Module 1: Product Identification System.

#### Rev. B Document (5/2007)

Clarifications/Corrections to the Data Sheet - Added Module 2: Electrical Specification - Supply Current.

#### Rev. C Document (7/2007)

Added Module 3: Analog-to-Digital Converter (ADC) Module.

#### Rev. D Document (8/2007)

Added Module 4: MSSP (SPI Master Mode), Module 5: MSSP (I<sup>2</sup>C Slave Mode) and Module 6: MSSP (I<sup>2</sup>C Master Mode).

#### Rev. E Document (4/2009)

Updated Errata to new format.

Data Sheet Clarification: Added Module 1: Timer1 (Block Diagram); Module 2: Comparator (C2 Block Diagram); Module 3: ADC (Block Diagram); Module 4: Comparator Voltage Reference; Module 5: Comparator Voltage Reference.

Added Module 7: MSSP; Added Module 8: Asynchronous Timer1; Added Module 9: LP/Timer1 Oscillator Operation Below 25°C; Module 10: Timer0 and WDT Prescaler Assignment Spurious Reset.

#### Rev. F Document (8/2009)

Added Module 11: MSSP (SPI Master Mode); Updated Tables 2, 3, 4.

Data Sheet Clarification: Removed Modules 1, 2, 4 and 5 as the Data Sheet has already been updated according to this version of the errata.

Added Module 2: ADC.

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, PIC<sup>32</sup> logo, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

#### WORLDWIDE SALES AND SERVICE

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277

Technical Support:

http://support.microchip.com

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago

Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2401-1200

Fax: 852-2401-3431

Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4080

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Yokohama

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-6578-300 Fax: 886-3-6578-370

Taiwan - Kaohsiung

Tel: 886-7-536-4818 Fax: 886-7-536-4803

Taiwan - Taipei

Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich**

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91 UK - Wokingham

Tel: 44-118-921-5869 Fax: 44-118-921-5820

03/26/09