# CY8CKIT-020

# PSoC® Development Kit Guide

Doc. # 001-56971 Rev. \*\* February 1, 2010

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone (USA): 800.858.1810 Phone (Intnl): 408.943.2600 http://www.cypress.com

#### Copyrights

© Cypress Semiconductor Corporation, 2009 - 2010. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATE-RIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

PSoC® Designer™, and PSoC® Creator™ are trademarks and PSoC® is a registered trademark of Cypress Semiconductor Corp. All other trademarks or registered trademarks referenced herein are property of the respective corporations.

#### Flash Code Protection

Cypress products meet the specifications contained in their particular Cypress PSoC Data Sheets. Cypress believes that its family of PSoC products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

# Contents

| 1. | Introdu  | ction                                                       | 5  |

|----|----------|-------------------------------------------------------------|----|

|    | 1.1      | Kit Overview                                                | 5  |

|    | 1.2      | Kit Contents                                                | 5  |

|    | 1.3      | Installation                                                |    |

|    |          | 1.3.1 Before You Begin                                      | 5  |

|    |          | 1.3.2 Prerequisites                                         |    |

|    |          | 1.3.3 Installing PSoC 1 Development Software                |    |

|    | 1.4      | PSoC Development Board                                      |    |

|    |          | 1.4.1 Default Switch and Jumper Settings                    | 7  |

|    | 1.5      | Conventions                                                 | 8  |

|    | 1.6      | Document Revision History                                   |    |

| 2. | Loading  | g My First PSoC Project                                     | 9  |

|    | 2.1      | My First PSoC 1 Project                                     | 9  |

|    |          | 2.1.1 Loading My First PSoC 1 Project                       |    |

|    |          | 2.1.2 Building My First PSoC 1 Project                      | 10 |

|    |          | 2.1.3 Programming My First PSoC 1 Project                   | 11 |

|    |          | 2.1.4 Running My First PSoC 1 Project                       | 11 |

| 3. | Sample   | Projects                                                    | 13 |

|    | 3.1      | CY8C28 Family Processor Module Example Projects             | 13 |

|    |          | 3.1.1 My First PSoC 1 Project                               |    |

|    |          | 3.1.1.1 Creating My First PSoC 1 Project                    | 13 |

|    |          | 3.1.1.2 main.c                                              |    |

|    |          | 3.1.2 ADC to LCD Project                                    | 22 |

|    |          | 3.1.2.1 Creating ADC to LCD Project                         |    |

|    |          | 3.1.2.2 main.c                                              | 27 |

|    |          | 3.1.3 ADC to UART with DAC                                  | 29 |

|    |          | 3.1.3.1 Creating ADC to UART with DAC Project               | 29 |

|    |          | 3.1.3.2 main.c                                              | 38 |

|    |          | 3.1.4 CapSense®                                             | 41 |

|    |          | 3.1.4.1 Creating CapSense Project                           | 41 |

|    |          | 3.1.4.2 main.c                                              | 47 |

| A  | pendix . | A. Board Specifications and Layout                          | 51 |

|    | 2.1      | PSoC Development Board                                      | 51 |

|    |          | 2.1.1 Factory Default Configuration                         | 51 |

|    |          | 2.1.1.1 Power Supply                                        |    |

|    |          | 2.1.2 Power Supply Configuration Examples                   |    |

|    |          | 2.1.2.1 Setting a 5V Supply from VREG                       |    |

|    |          | 2.1.2.2 Setting a 3.3V Supply from VREG                     |    |

|    |          | 2.1.2.3 Setting VDD ANLG as VADJ and VDD DIG as VDD for VDD |    |

|      |        |        | 2.1.2.4    | Setting VDD DIG as VADJ and VDD ANLG as VDD for VDD : | = 3.3V     |

|------|--------|--------|------------|-------------------------------------------------------|------------|

|      |        |        |            | 53                                                    | <b>-</b> 4 |

|      |        |        | 2.1.2.5    | Setting a 5V Supply from VBUS                         |            |

|      |        |        | 2.1.2.6    | Setting a 3.3V Supply from VBUS                       |            |

|      |        |        | 2.1.2.7    |                                                       |            |

|      |        |        | 2.1.2.8    | 9V Battery Terminals                                  |            |

|      |        |        | 2.1.2.9    | J8 - 5V Source                                        |            |

|      |        |        |            | VDD Select Switch                                     |            |

|      |        |        |            | J7 - VDD DIG Select                                   |            |

|      |        |        |            | R11 - Adjustable Regulator Variable Resistor          |            |

|      |        | 2.1.3  |            | ing Components                                        |            |

|      |        | 2.1.0  | 2.1.3.1    | Prototyping Area                                      |            |

|      |        |        | 2.1.3.2    | P15 - DB9 Serial Communications Port                  |            |

|      |        |        | 2.1.3.3    | J10 - Serial Port Power                               |            |

|      |        |        | 2.1.3.4    | J9 - Full Speed USB Port                              |            |

|      |        |        | 2.1.3.5    | P17 - Artaflex WirelessUSB LP Radio Module Receptacle |            |

|      |        |        | 2.1.3.6    | J14 - Wireless Radio Module Power                     |            |

|      |        |        | 2.1.3.7    | R20 - Multipurpose Variable Resistor                  |            |

|      |        |        | 2.1.3.8    | J11 - Variable Resistor Power                         |            |

|      |        |        | 2.1.3.9    |                                                       |            |

|      |        | 2.1.4  | LCD Mo     | dule                                                  |            |

|      |        |        | 2.1.4.1    |                                                       |            |

|      |        |        | 2.1.4.2    | J12 - LCD Module Power                                |            |

|      |        | 2.1.5  | CapSens    | se Elements                                           | 60         |

|      |        | 2.1.6  | Processo   | or Module                                             | 60         |

|      |        |        | 2.1.6.1    | J2, J3, J4 and J5 - VDDIO Select                      | 60         |

|      |        |        | 2.1.6.2    |                                                       |            |

|      |        |        | 2.1.6.3    |                                                       |            |

|      |        |        | 2.1.6.4    | P1, P2, P3 and P4 - Processor Module Receptacles      |            |

|      |        | 2.1.7  |            | on Ports                                              |            |

|      |        |        | 2.1.7.1    | <b>'</b>                                              |            |

|      |        |        | 2.1.7.2    | = 1,5                                                 |            |

|      |        |        | 2.1.7.3    | Expansion Port C                                      | 65         |

| Appe | ndix l | B. Mi  | niProg3    |                                                       | 67         |

|      | B.1    | MiniPr | og3 LEDs   |                                                       | 67         |

|      | B.2    |        | 0          | Power Cycle Mode                                      |            |

|      | B.3    |        |            | signment Table                                        |            |

|      | B.4    |        |            | itry                                                  |            |

|      | B.5    | Level  | Translatio | n                                                     | 68         |

| Δnne | ndix ( | C. Mir | niProg3    | Technical Description                                 | 69         |

| .ppc | C.1    |        | _          | Teenmed Description                                   |            |

|      | U. I   |        |            |                                                       |            |

|      |        |        |            |                                                       |            |

|      |        |        |            | VV                                                    |            |

|      |        |        |            | v v                                                   |            |

|      | C.2    |        |            |                                                       |            |

|      | ٥.٢    |        |            | nnector                                               |            |

|      |        |        |            | onnector                                              |            |

|      | C.3    |        |            |                                                       |            |

|      |        |        |            |                                                       |            |

# 1. Introduction

### 1.1 Kit Overview

This guide and the CY8C28 Family Processor Module gives you a practical understanding of PSoC<sup>®</sup> technology. The kit gives several example projects with step-by-step instructions to enable you to easily get started developing PSoC solutions.

To accompany the CY8CKIT-020 kit, you are required to have the CY8CKIT-001 PSoC Development Kit which provides you a common development platform where you can prototype and evaluate different solutions using any one of the PSoC 1, PSoC 3, or PSoC 5 architectures.

### 1.2 Kit Contents

The CY8CKIT-020 PSoC Development Kit includes:

- PSoC CY8C28 Family Processor Module

- Printed Documentation

- Quick Start

- □ Schematic PSoC Development Board Design

- Software CD for PSoC 1, which includes

- □ PSoC<sup>®</sup> Designer<sup>™</sup> IDE

- □ PSoC<sup>®</sup> Programmer<sup>™</sup> Software

- □ CY8C28 Data Sheets

- Example Project Files, Firmware, and Documentation

### 1.3 Installation

Everything you need to use the PSoC Development Kit is included, but you only need to install the software for the processor module you plan to use.

Proceed with following the PSoC Development Kit Quick Start Guide. This guide instructs you on how to install the CY8C28 Family Processor Module with the CY8CKIT-001 PSoC Development Kit. The Quick Start Guide also instructs how to install the Cypress software development tools.

### 1.3.1 Before You Begin

All Cypress software installations require administrator privileges but is not required to run the installed software.

Shut down any currently running Cypress software.

Disconnect any ICE Cube or MiniProg devices from your computer.

### 1.3.2 Prerequisites

PSoC Designer uses the Microsoft .NET Framework, Adobe Acrobat Reader, and a Windows Installer. If .NET Framework and Windows Installer are not on your computer, the installation automatically installs it for you. If you do not have Adobe Acrobat Reader, you have to manually download from Adobe website and install it.

### 1.3.3 Installing PSoC 1 Development Software

To use the CY8C28 Family Processor Module (PSoC 1) you need:

- PSoC Designer 5.0 SP6 or higher

- PSoC Programmer 3.06 or higher

If PSoC Designer 5.0 is currently installed, uninstall it. Click **Start**, click **Control Panel**, and then double click **Add or Remove Programs**.

PSoC Designer 5.0 SP6 is not presently compatible with Microsoft Internet Explorer 8 beta (any beta version). If you have Internet Explorer 8 beta, uninstall it and replace it with the released version of Microsoft Internet Explorer 8.

Insert the CY8C28 Family Processor Module Software CD and, using the menu, select **Install Software for PSoC 1**.

After installation, guides and key documents are located in the \Documentation subdirectory of the PSoC Designer installation directory. The default location is:

C:\Program Files\Cypress\PSoC Designer 5\Documentation

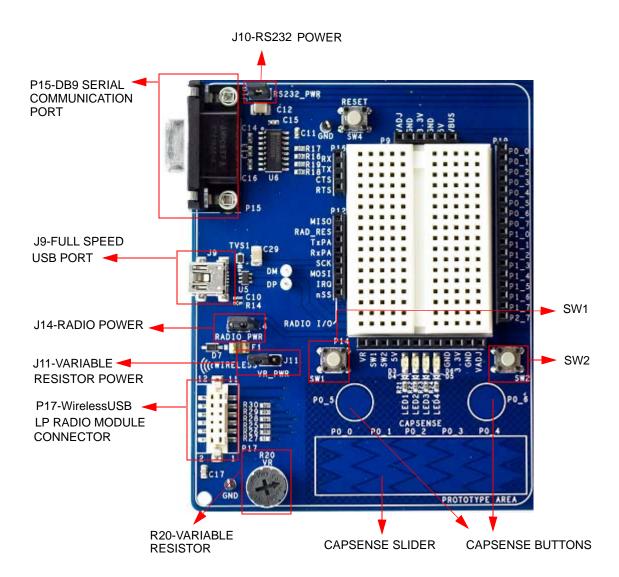

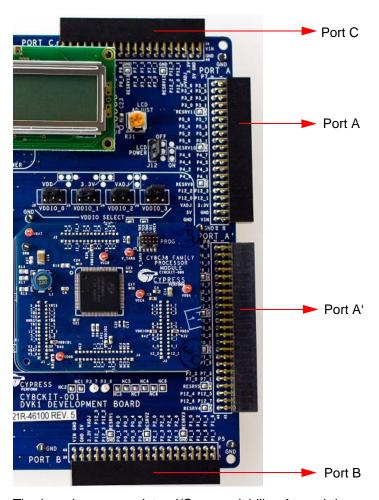

## 1.4 PSoC Development Board

Sold seperately, the CY8CKIT-001 PSoC Development Board is designed to aid hardware, firmware, and software developers in building their own systems around Cypress's PSoC devices. The flexibility to configure the power domains is one of the foremost features of this board. Input power to the board is from one of two sources:

- 12V 1A wall wart power supply

- 9V alkaline battery (not included)

This full featured board incorporates three onboard linear regulators that power peripherals and PSoC modules at voltages between 1.7V and 5.5V. These regulators include a fixed 5V 1A linear regulator, a fixed 3.3V 300 mA linear regulator, and a 1.5V to 5.5V 300 mA adjustable regulator. The board also provides the ability to separate the PSoC core VCC rail into two separate rails, analog and digital. In addition, the board is able to separate the I/O VCC rails, giving the flexibility to power the I/O ports at different voltages.

The board is equipped with a 2x16 alphanumeric LCD module capable of 1.8V to 5.5V I/O. In addition, there is a mini-B full speed USB interface and a female DB9 serial communications interface. Also included is a x-pin wireless radio module interface which can be used to develop CyFi™ Low-Power RF or other embedded RF solutions with this kit. The board also has a prototyping area containing a small breadboard complete with I/O port sockets nearby, multipurpose LEDs, mechanical push buttons, and a multipurpose variable resistor. In addition, three capacitive sensing elements (two buttons and a five segment slider) are included on the board to allow the evaluation of CapSense™ applications.

The board has four GPIO expansion slots, allowing the I/O to expand to external boards.

The board was designed with modularity in mind and, as a result, supports removable processor modules. This allows you to plug different PSoC modules into the board based upon the desired features of both 8-bit and 32-bit PSoC devices.

### 1.4.1 Default Switch and Jumper Settings

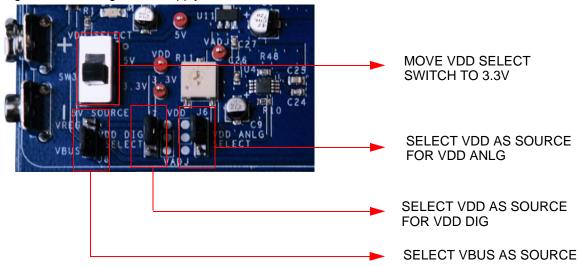

Jumpers on the CY8CKIT-001 PSoC Development Main Board have a default setting for 3.3V operation. For Default configuration, each of the jumpers must be set according to these instructions.

**Note:** All CY8C28 family processor module example projects are configured for 5V. Configure the board to 5V, before creating the example projects.

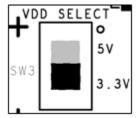

SW3 - VDD Select. Default Position: 3.3V (down position)

J8 - 5V Source. Default Position: VREG (upper two pins)

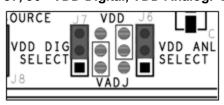

### J7, J6 - VDD Digital, VDD Analog. Default Position: VDD (upper two pins, both headers)

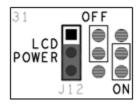

### J12 - LCD Power. Default Position: ON (lower two pins)

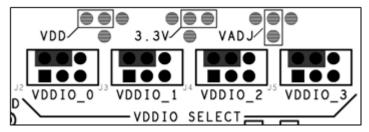

### J2-J5 - VDDIO Power Select. Default Position: VDD (upper left two pins)

## J10 - RS232 Power (Serial Communications). Default Position: Installed

### J14 - Radio Power. Default Position: Installed

### J11 - Variable Resistor Power. Default Position: Installed

# 1.5 Conventions

These conventions are used throughout this guide.

Table 1-1. Documentation Conventions

| Convention                 | Usage                                                                                                                        |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Courier New<br>Size 12     | Displays file locations and source code: C:\cd\icc\.                                                                         |

| Italics                    | Displays file names and reference documentation: sourcefile.hex                                                              |

| [bracketed, bold]          | Displays keyboard commands in procedures: [Enter] or [Ctrl] [C]                                                              |

| $Bold \to With \to Arrows$ | Represents menu paths, user entered text: File $\rightarrow$ New Project $\rightarrow$ Clone                                 |

| Bold                       | Displays commands and selections, and icon names in procedures: Click the <b>Debugger</b> icon, and then click <b>Next</b> . |

| Note:                      | Displays functionality unique to PSoC Designer, PSoC Creator, or the PSoC device.                                            |

| WARNING:                   | Displays cautions that are important to the subject.                                                                         |

# 1.6 Document Revision History

| Document Title: CY8CKIT-020 PSoC Development Kit Guide Document Number: 001-56971 |            |                     |                       |  |  |  |

|-----------------------------------------------------------------------------------|------------|---------------------|-----------------------|--|--|--|

| Revision                                                                          | Issue Date | Origin of<br>Change | Description of Change |  |  |  |

| **                                                                                | 11/18/09   | AESA                | New Guide             |  |  |  |

# 2. Loading My First PSoC Project

The CY8CKIT-020 PSoC Development Kit supports projects across the CY8C28 family architectures. This section walks you through the high level design process for opening, building, programming, and running your first PSoC projects using this kit.

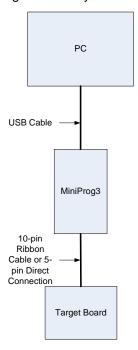

To begin with be sure you have the CY8CKIT-001 and the CY8CKIT-020 kit. Follow each of these steps to make certain that your software and hardware environments are properly configured and ready for these projects:

- 1. Install PSoC Designer using the steps listed in Installing PSoC 1 Development Software on page 6.

- 2. Connect the MiniProg3 into your PC using the supplied USB cable. When you connect the MiniProg3, Microsoft Windows<sup>®</sup> may indicate that it has found new hardware. All required drivers were installed as part of the PSoC Programmer installation process; however, if Windows opens the driver installation dialog boxes, accept the defaults and allow Windows to automatically find the appropriate driver.

- 3. Configure the PSoC Development Board (jumper settings and switches) in its default configuration, as described in Default Switch and Jumper Settings on page 7.

- 4. Use the PSoC CY8C28 Family Processor Module for the PSoC 1 version of your first PSoC project (My First PSoC 1 Project on page 9).

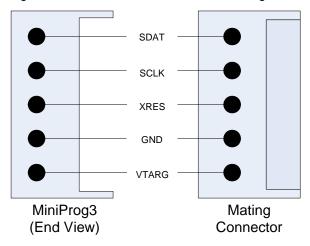

- 5. For a PSoC 1 project, use the ISSP header on the PSoC CY8C28 Family Processor Module and connect the MiniProg3 ISSP port.

- 6. Power the PSoC Development Board using the 12V AC Power Adapter

# 2.1 My First PSoC 1 Project

This is a simple PSoC 1 project using a PWM peripheral inside PSoC, and software to control the blinking rates of two different LED outputs. For this project, be sure you have the PSoC CY8C28 Family Processor Module inserted into the PSoC Development Board and the appropriate software installed. This section walks you through the high level steps of opening, building, and programming a project.

## 2.1.1 Loading My First PSoC 1 Project

- 1. Open PSoC Designer.

- 2. In the Start Page, navigate to File → Open Project/Workspace

- 3. Navigate to the project directory

C:\Cypress\CY8CKIT-001\CY8C28 Projects\

- 4. Open the folder Ex1\_LED\_with\_PWM.

- 5. Double click **Ex1\_LED\_with\_PWM.app**.

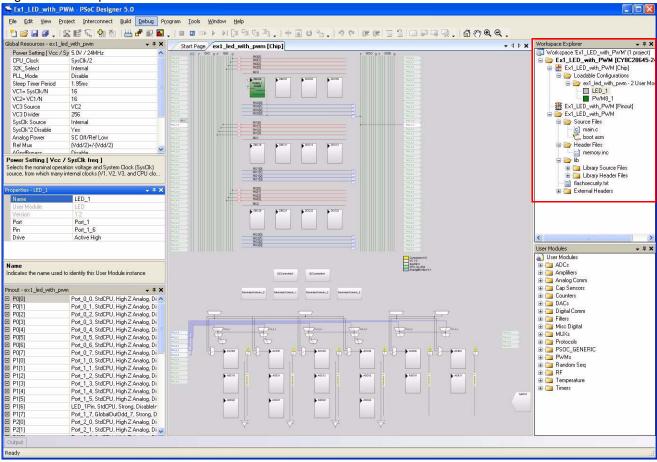

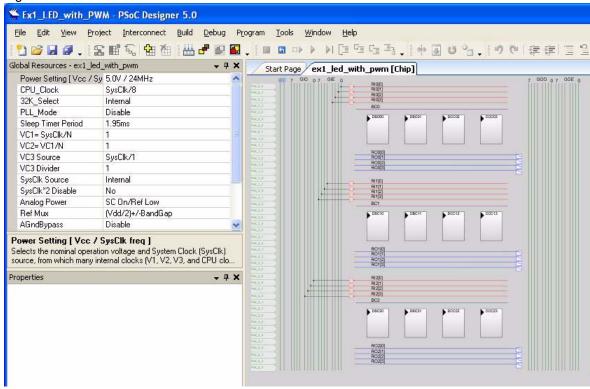

- 6. The project opens in the Chip Editor view. All the project files are in the Workspace Explorer.

Figure 2-1. Chip Editor View

### 2.1.2 Building My First PSoC 1 Project

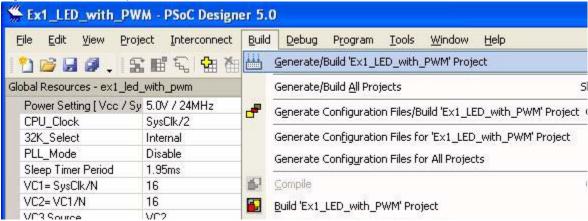

1. Select Build → Generate/Build 'Ex1\_LED\_with\_PWM' Project.

Figure 2-2. Build Project

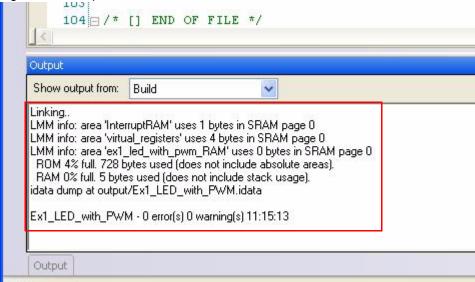

2. PSoC Designer builds the project and displays comments in the **Output** window. When you see the message that the project built with 0 errors and 0 warnings you are ready to program the device.

Figure 2-3. Output Window

### 2.1.3 Programming My First PSoC 1 Project

**Note** The CY8C28 Family Processor Module is designed to accommodate the use of the CY3215-DK In-Circuit Emulator (ICE Cube). When using the ICE Cube debugger, make certain that PSoC Designer is configured so that the ICE Cube DOES NOT provide power to the processor module. Within the **PSoC Designer** application, select **Project** > **Settings** and select **Debugger** from the tree list. Make sure **External only** is selected under the **Pod Power Source** section.

- 1. Open **Program Part** from within PSoC Designer by selecting **Program** → **Program Part**.

- 2. In the Program Part window, ensure that MiniProg3 is selected in the Port Selection box.

- 3. In the Program Part window, set Accquire Mode to Reset.

- 4. In the **Program Part** window, set **Verifcation** to **On**. This ensures that downloaded checksum matches the actual checksum.

- 5. In the **Program Part** window, click the program arrow to program the device.

- 6. Wait until programming is completed to continue.

## 2.1.4 Running My First PSoC 1 Project

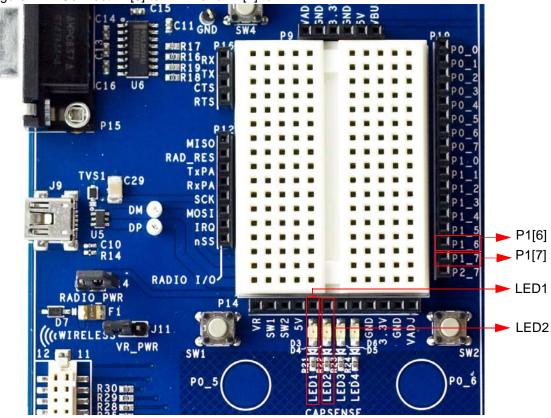

- 1. Connect P1[6] to LED1 and P1[7] to LED2. Verify that LED1 and LED2 are blinking based on the project's use of the PWM and software. Now that the PSoC 1 device is programmed, reset the PSoC Development Board by pressing and releasing the reset switch (SW4).

- 2. LED1 blinks approximately once every second and LED2 blinks about three times a second.

Figure 2-4. Connect P1[6] to LED1 and P1[7] to LED2

3. For more details regarding this project, see the detailed step-by-step project instructions in My First PSoC 1 Project on page 13.

# 3. Sample Projects

This chapter shows you how to create the sample projects included with this kit.

Read these precautions before you create example projects:

- All CY8C28 family processor module example projects are configured for 5V.

- Close any open project in PSoC Designer before loading or creating an example project.

- When working with example projects, use 12V wall wart power supply.

- Remove power before changing board jumpers for each example project. Reapply power after you place jumpers on the breadboard.

- When you complete each project make certain to save the project.

# 3.1 CY8C28 Family Processor Module Example Projects

### 3.1.1 My First PSoC 1 Project

### 3.1.1.1 Creating My First PSoC 1 Project

- 1. Open PSoC Designer 5.0

- 2. To create a new project, click **File** → **New Project**. The **New Project** window opens.

- 3. In the **New Project window**, select the **Chip-Level Project**. **Name** the project **Ex1\_LED\_with\_PWM**.

- 4. In **Location**, click **Browse** and navigate to the appropriate directory.

Figure 3-1. New Project Window

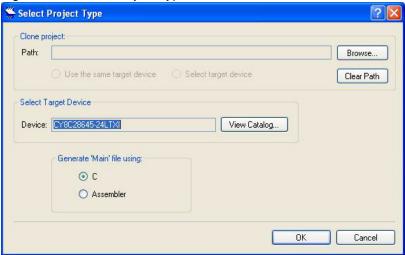

5. Click **OK**. The **Select Project Type** window opens.

Figure 3-2. Select Project Type Window

- 6. In this window under Select Target Device, click View Catalog.

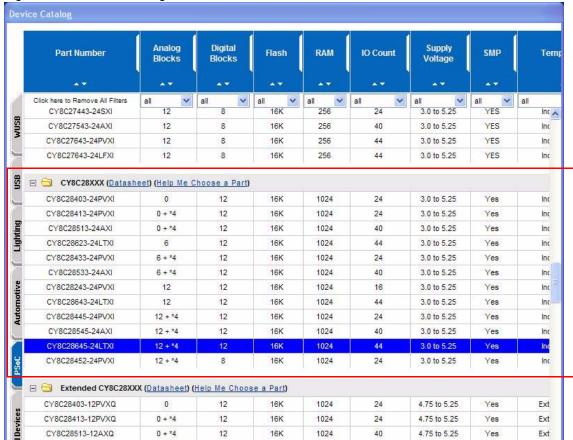

- 7. The **Device Catalog** window opens. Click on the **PSoC** tab, and scroll down to the **CY8C28XXX** section.

- 8. For this project click CY8C28645-24LTXI device in this section and then click **Select**.

Figure 3-3. Device Catalog Window

- 9. Under Generate 'Main' File Using:, for this project select C, then click OK.

- 10. By default, the project opens to chip view

Figure 3-4. Default View.

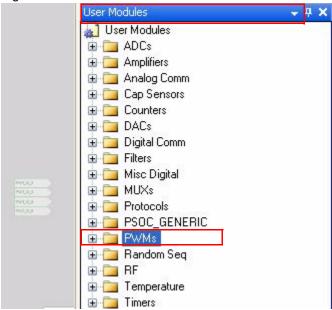

11. In the **User Modules** window, expand the **PWMs** folder.

Figure 3-5. User Modules Window

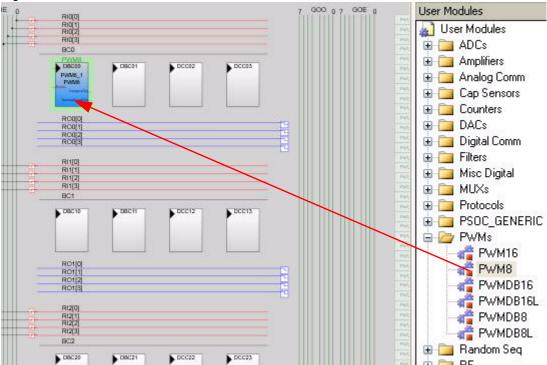

12. In this folder right click on a **PWM8** and select place. The User Module (UM) is placed in the first available digital block.

Figure 3-6. Place User Module PWM8

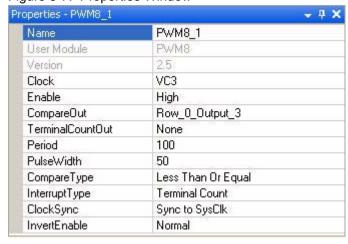

13. Click the placed PWM8\_1 UM; the **Properties** window opens on the left side of the screen. Configure the PWM with the settings as in the following figure. If the **Properties** window does not appear, click **View** → **Properties** Window.

Figure 3-7. Properties Window

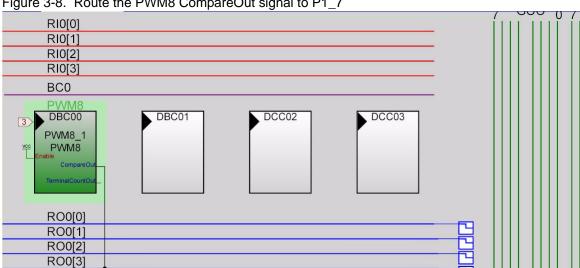

14. Next, route the PWM **CompareOut** signal to P1\_7. The first step is to configure the Look Up Table (LUT) on **Row\_0\_Output3**.

Figure 3-8. Route the PWM8 CompareOut signal to P1\_7

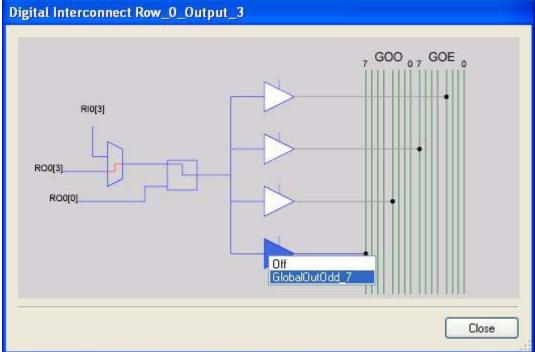

- 15. Double click the **LUT**, the **Digital Interconnect** window opens.

- 16. In this window enable Row\_0\_Output\_3\_Drive\_3 to connect to GlobalOutOdd\_7.

Figure 3-9. Digital Interconnect Window

- 17. Click Close.

- 18. Click on GlobalOutOdd\_7. A window appears, in this window configure PIN for Port\_1\_7.

Port 2 3

Figure 3-10. Configure PIN for Port\_1\_7

Port\_1\_4

Port\_1\_5

Port\_1\_6

Port\_1\_7

Port\_2\_0

Port\_2\_1

Port\_2\_1

Port\_2\_1

- 19. Click **OK** to continue.

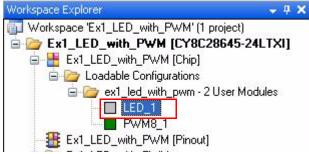

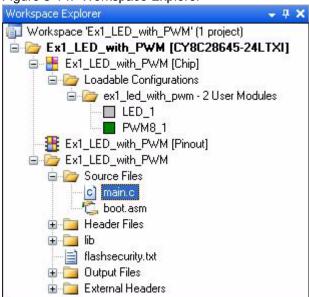

- 20. In the User Modules window expand the Misc Digital folder. In this folder right click the LED and select place, this adds the UM to the project. This UM does not use digital or analog blocks. It appears in the Workspace Explorer → Ex1\_LED\_with\_PWM[CY8C28] → Ex1\_LED\_with\_PWM[Chip] → Loadable Configurations → Ex1\_LED\_with\_PWM 2 User Modules.

OK

Cancel

Figure 3-11. Workspace Explorer

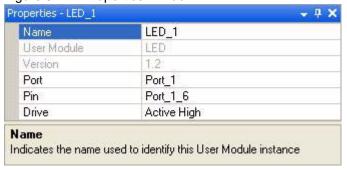

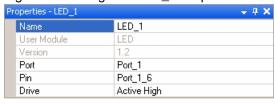

21. Click the LED\_1 UM and navigate to the Properties window. Configure the LED for P1\_6.

Figure 3-12. Properties Window

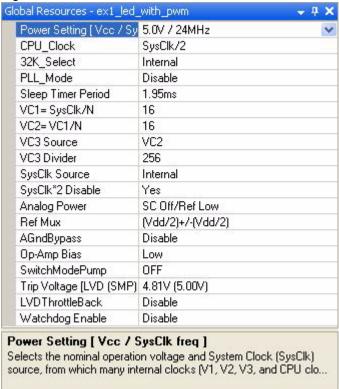

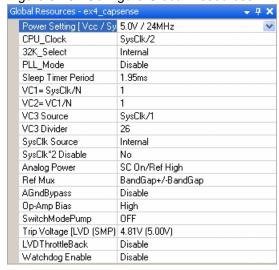

22. Configure the **Global Resources** window to match the following figure.

Figure 3-13. Global Resources Window

23. Open the existing *main.c* file within Workspace Explorer. Replace the existing *main.c* content with the content of the embedded *CY8C28\_main\_Ex1.c* file, which can be found within the attachments feature of this PDF document.

Figure 3-14. Workspace Explorer

- 24. Save the project.

- 25. Build the project. Build → Generate/Build 'Ex1\_LED\_with\_PWM' Project.

- 26. Disconnect power to the board.

- 27. Configure the DVK board SW3 to 5V.

- 28. Configure the DVK breadboard using the included jumper wires:

- □ P1\_6 to LED1

- □ P1\_7 to LED2

- 29. Reapply power to the board.

- 30.Use PSoC Designer as described in Programming My First PSoC 1 Project on page 11 to program the device.

- 31. Reset the DVK, and observe the blinking LEDs.

- 32. Save and close the project.

#### 3.1.1.2 main.c

- 1. Open the existing *main.c* file within **Workspace Explorer**.

- 2. Replace the existing *main.c* content with the content of the embedded *CY8C28\_main\_Ex1.c* file, which can be found within the attachments feature of this PDF document.

**Note:** To access the embedded attachments feature in the PDF document, click on the paper clip icon located in the lower left corner of the Adobe Reader application.

```

#include <m8c.h>

/* Part specific constants and macros */

#include "PSoCAPI.h"

/* PSoC API definitions for all User Modules */

* Function Name: main

*******************

* The main function initializes the PWM and starts the PWM clock which will

* blink LED1. Then the main loop is entered which delays enough for LED2 to

* blink at a quicker rate than LED1.

* Parameters:

void

* Return:

void

********************************

void main(void)

{

WORD i;

/* Variable used for delay */

PWM8_1_Start(); /* Turn on the PWM to blink LED on P1.6 */

LED_1_Start();

/* Enable Software controlled LED */

/* The following loop controls the software LED connected to P1.7 */

while(1)

/* Delay time depends on compiler optimization levels and CPU clock */

for (i = 0; i < 60000; i++);

/* Switch the state of Software LED (on or off) */

LED_1_Invert();

} /* End of while(1) */

} /* End of main */

/* [] END OF FILE */

```

### 3.1.2 ADC to LCD Project

This project demonstrates a 9-bit Delta Sigma ADC by measuring the voltage of the potentiometer center tap wiper and displaying the result on the LCD. Connect the voltage potentiometer (VR) to the ADC input P0\_1. The program reads the 9-bit ADC result and prints it to the LCD.

### 3.1.2.1 Creating ADC to LCD Project

- 1. Follow steps 1 to 10 in section 3.1.1.1 on page 13, change the **Name** of the project to **Ex2\_ADC\_to\_LCD**.

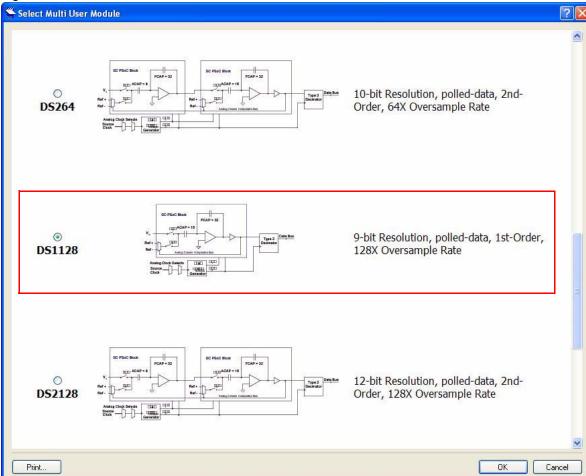

- In the User Modules window expand the ADCs folder, and then right click DelSigPlus and choose Place. A window opens with multiple options for the DelSigPlus UM. In this case the DS1128 configuration is used. Scroll down in the window to verify that this is the case.

Figure 3-15. Select Multi User Module Window

- 3. Click OK.

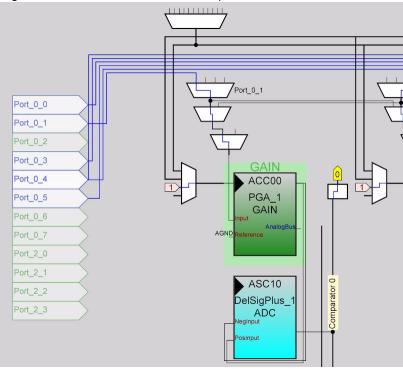

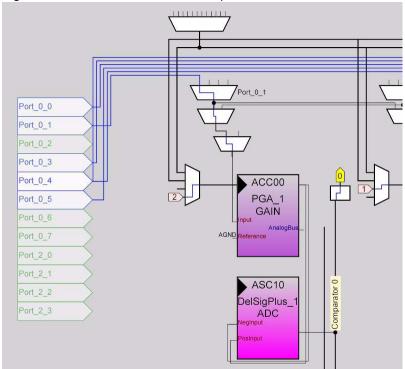

- 4. Verify that the **DelSigPlus\_1** UM is placed in **ASC10**.

- 5. In the **User Modules** window expand the **Amplifiers** window. Right click **PGA**, select place. Ensure that the **PGA** is placed in **ACC00**.

Figure 3-16. Ensure that the PGA is placed in ACC00.

- 6. In the User Modules window expand Misc Digital, Right click LCD and click place.

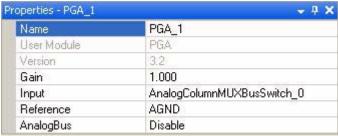

- 7. Click PGA\_1 and configure the properties to match this figure.

Figure 3-17. PGA\_1 Properties

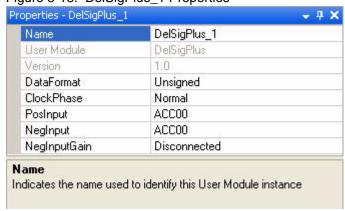

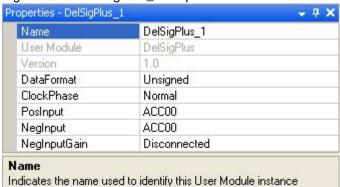

8. Click **DelSigPlus\_1** and configure the properties to match this figure.

Figure 3-18. DelSigPlus\_1 Properties

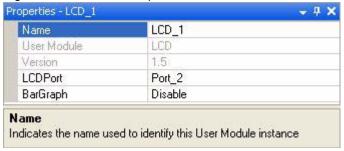

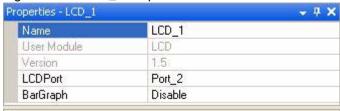

9. Click **LCD** 1 and configure the properties to match this figure.

Figure 3-19. LCD\_1 Properties

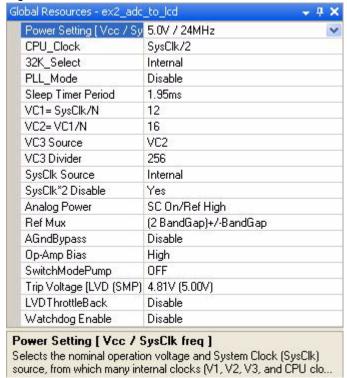

10. Configure the Global Resources to match the following figure.

Figure 3-20. Global Resources

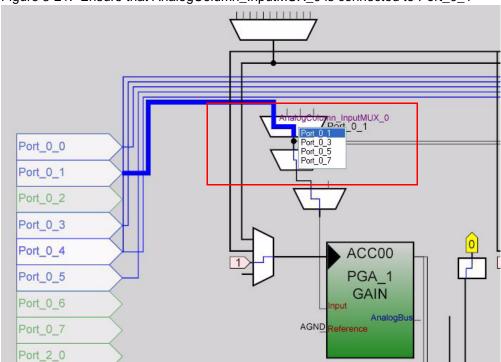

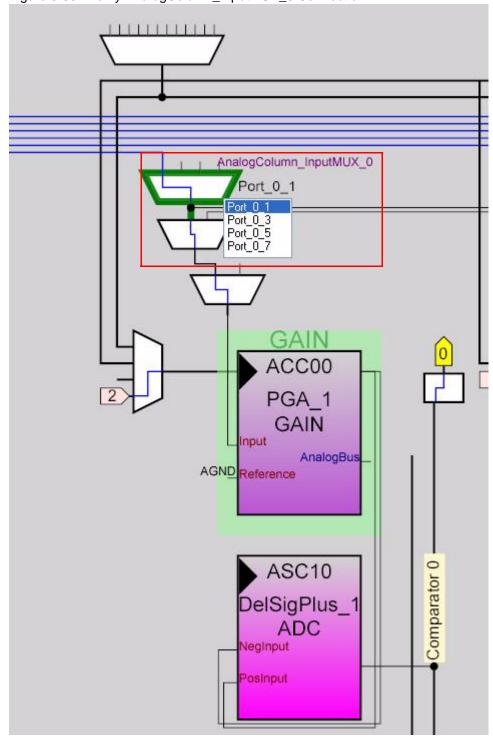

11. Ensure that **AnalogColumn\_InputMUX\_0** is connected to **Port\_0\_1**. If it is not configured for this port, double click the **MUX** and choose **Port\_0\_1**.

Figure 3-21. Ensure that AnalogColumn\_InputMUX\_0 is connected to Port\_0\_1

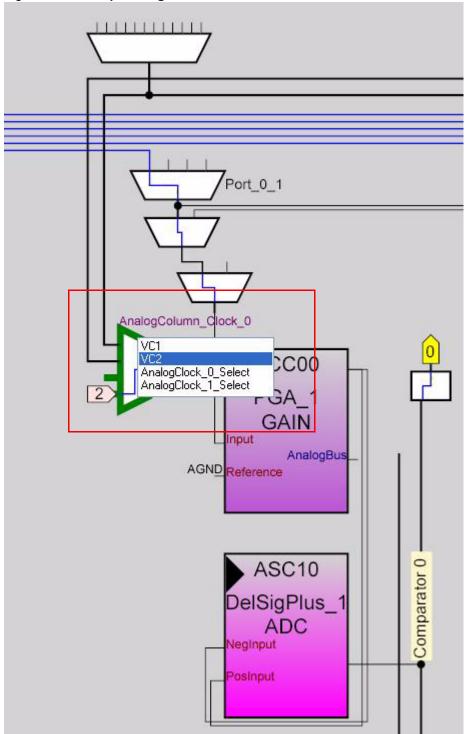

12. Ensure that **AnalogColumn\_Clock\_0**, is connected to **VC1**. If it is not, double click the **MUX** and choose **VC1**.

Port\_0\_1

Port\_0\_1

AnalogClock\_0\_Select GA\_1

GAIN

Input

AnalogBus

AGND

Reference

Figure 3-22. Ensure that AnalogColumn\_Clock\_0, is connected to VC1

- 13. Open the existing *main.c* file within Workspace Explorer. Replace the existing *main.c* content with the content of the embedded *CY8C28\_main\_Ex2.c* file, which can be found within the attachments feature of this PDF document.

- 14. Save the project.

- 15. Build the project. **Build** → **Generate/Build 'Ex2\_ADC\_to\_LCD' Project**.

- 16. Disconnect power to the board.

- 17. Configure the DVK breadboard SW3 to 5V.

- 18. Configure the DVK breadboard using the included jumper wires:

- □ P0 1 to VR

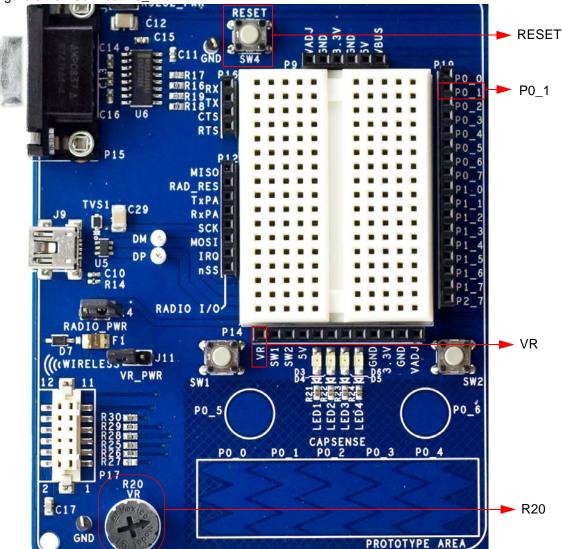

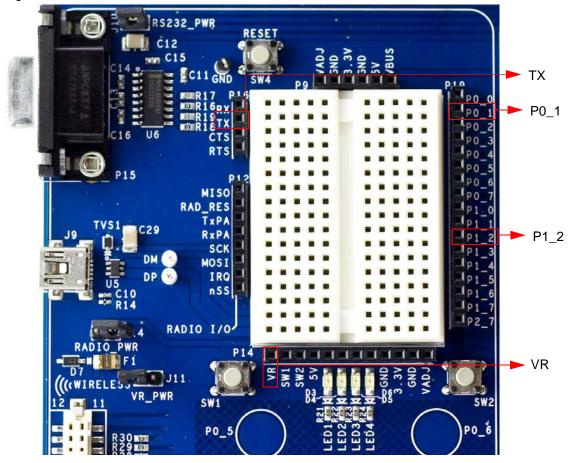

Figure 3-23. Connect P0\_1 to VR

- 19. Reapply power to the board.

- 20.Use PSoC Designer as described in Programming My First PSoC 1 Project on page 11 to program the device.

- 21. After programming the device, press the reset button and vary the POT (R20) to see the results on the LCD.

**Note:** The ADC output values may not reach full range due to potentiometer and ADC limitations. ADC values may fluctuate several counts due to system noise, and if the potentiometer voltage is at the edge of an ADC count.

22. Save and close the project.

#### 3.1.2.2 main.c

- 1. Open the existing *main.c* file within **Workspace Explorer**.

- 2. Replace the existing *main.c* content with the content of the embedded *CY8C28\_main\_Ex2.c* file, which can be found within the attachments feature of this PDF document.

**Note:** To access the embedded attachments feature in the PDF document, click on the paper clip icon located in the lower left corner of the Adobe Reader application.

```

/* part specific constants and macros */

#include <m8c.h>

#include "PSoCAPI.h"

/* PSoC API definitions for all User Modules */

/* LCD specific */

#define ROW_0 0 /* LCD row 0

#define ROW_1

1 /* LCD row 1

#define COLUMN_0 0 /* LCD column 0 */

#define COLUMN_9 9 /* LCD column 9 */

/*****************************

* Function Name: main

The main function initializes both the ADC and LCD, starts and waits for an

ADC conversion, then it displays the raw counts to the LCD.

* Parameters:

void

* Return:

void

*************************

void main(void)

{

WORD adcResult; /* Holds the integer ADC result */

/* Initialize the PGA used to buffer input from the potentiometer (VR) on

P0.1 to the ADC */

PGA_1_Start(PGA_1_HIGHPOWER);

DelSigPlus_1_Start(DelSigPlus_1_HIGHPOWER); /* Initialize the ADC */

LCD_1_Start();

/* Initialize the LCD */

/* Set the LCD to (Row=0,Column=0) */

LCD_1_Position(ROW_0, COLUMN_0);

LCD_1_PrCString("V Count: ");

DelSigPlus_1_StartAD(); /* Start gathering conversions from the ADC */

/* Enable Global interrupts */

M8C_EnableGInt;

/\!\!^* This loop waits for a valid ADC result, and displays it on the LCD ^*/\!\!

while (1)

/* Is there ADC data? */

if(DelSigPlus_1_fIsDataAvailable())

/* Store result from ADC */

```

### 3.1.3 ADC to UART with DAC

This project demonstrates sine wave generation by using a 6-bit DAC. The sine wave period is based on the current value of the ADC. The firmware reads the voltage output by the DVK board potentiometer and displays the raw counts on the DVK board character LCD display similarly to those shown in the previous project. A 6-bit DAC outputs a table generated sine wave at a frequency proportional to the ADC count. The frequency outputs to an oscilloscope. A 38400 BAUD UART outputs the current ADC count as ASCII formatted into a hexadecimal number.

### 3.1.3.1 Creating ADC to UART with DAC Project

- Follow steps 1 to 10 in section 3.1.1.1 on page 13, change the Name of the project to Ex3\_ADC\_to\_UART\_with\_DAC.

- 2. In the **User Modules** window expand the **ADCs** folder, and then right click **DelSigPlus** and choose **Place**. A window opens with multiple options for the DelSigPlus UM. In this case the **DS1128** configuration is used. Scroll down in the window to verify that this is the case.

- 3. Click OK.

- 4. Verify that the UM is placed in ASC10.

- 5. In the **User Modules** window expand the **Amplifiers** window. Right click **PGA**, select place. Ensure that the **PGA** is placed in **ACC00**.

Figure 3-24. Ensure that the PGA is placed in ACC00

- 6. In the User Modules window expand Misc Digital, right click LCD, and click place.

- 7. In the User Modules window expand Counters, right click Counter16, and select place.

- 8. In the User Modules window expand Digital Comm, right click TX8, and click place.

- 9. In the User Modules window expand DACs, right click DAC6, and click place.

- 10. Move the UMs so that they match the configuration shown in Figure 3-25 on page 30.

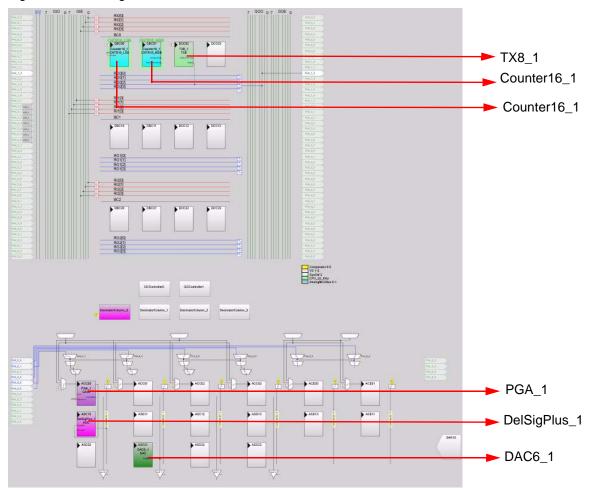

Figure 3-25. Configure User Modules

11. Click on **DelSigPlus\_1** and configure it to match this figure.

Figure 3-26. DelSigPlus\_1 Properties

### 12. Click **PGA\_1** and configure it to match this figure.

Figure 3-27. PGA\_1 Properties

| Name        | PGA_1                      |

|-------------|----------------------------|

| User Module | PGA                        |

| Version     | 3.2                        |

| Gain        | 1.000                      |

| Input       | AnalogColumnMUXBusSwitch_0 |

| Reference   | AGND                       |

| AnalogBus   | Disable                    |

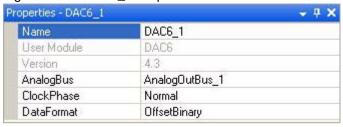

13. Click **DAC6\_1** and configure it to match this figure.

Figure 3-28. DAC6\_1 Properties

14. Click **LCD\_1** and configure it to match this figure.

Figure 3-29. LCD\_1 Properties

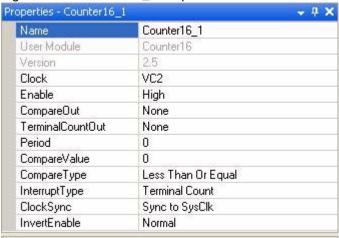

15. Click on **Counter16\_1** and configure it to match this figure.

Figure 3-30. Counter16\_1 Properties

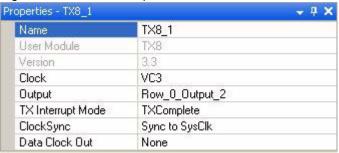

16. Click **TX8\_1** and configure it to match this figure.

Figure 3-31. TX8\_1 Properties

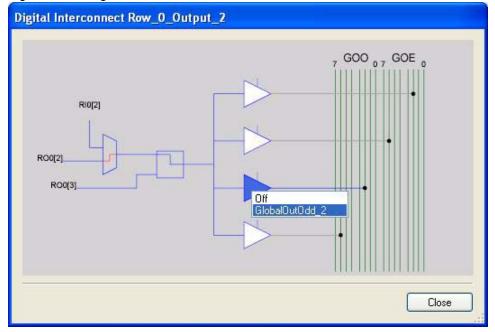

17. Click RO0[2] LUT, enable Row\_0\_Output\_2\_Drive\_2 to connect GlobalOutOdd\_2.

Figure 3-32. Digital Interconnect Window

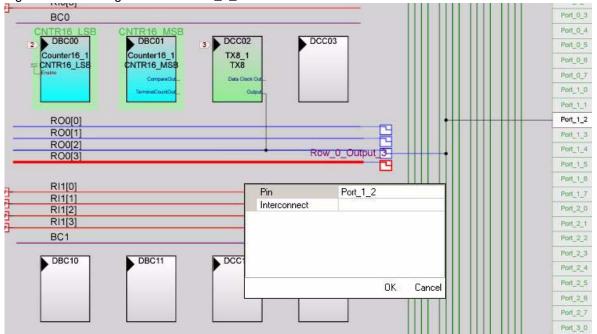

18. Click GlobalOutOdd\_2. A window appears; in this window configure PIN for Port\_1\_2.

Figure 3-33. Configure PIN for Port\_1\_2

- 19. Click **OK** to continue.

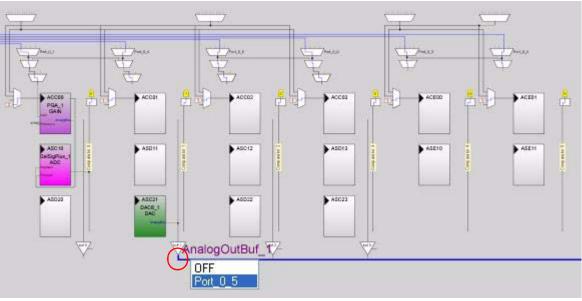

- 20. Click AnalogOutBuf\_1 and configure it for Port\_0\_5.

Figure 3-34. Configure AnalogOutBuf\_1

21. Verify that **AnalogColumn\_InputMUX\_0** is connected to **Port\_0\_1**. If it is not configured for this port, double click the **MUX** and choose **Port\_0\_1**.

Figure 3-35. Verify AnalogColumn\_InputMUX\_0 Connection

22. Verify that AnalogColumn\_Clock\_0 and AnalogColumn\_Clock\_1 are connected to VC2. If it is not, double click the MUX and chose VC2.

Figure 3-36. Verify AnalogColumn\_Clock\_0 Connection

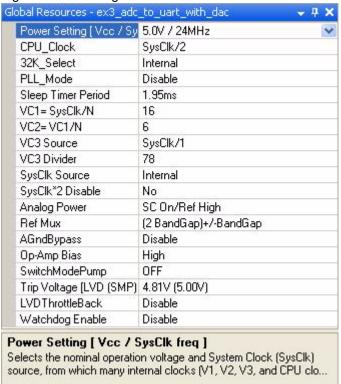

23. Configure **Global Resources** to match the following figure.

Figure 3-37. Configure Global Resources

- 24. Open the existing *main.c* file within Workspace Explorer. Replace the existing *main.c* content with the content of the embedded *CY8C28\_main\_Ex3.c* file, which can be found within the attachments feature of this PDF document.

- 25. Save the project.

- 26. To Generate the project, click **Build** → **Generate/Build 'Ex3\_ADC\_to\_UART\_with\_DAC'** Project.

- 27. Open your *boot.tpl* file in the project folder **Files** → **Open File**. Select **All Files** for **Files of the type**:

- 28. Select *boot.tpl* in the list of files and click **Open**.

- 29. Find the line '@INTERRUPT\_9' (for PSoC Block DBC01) and replace that line with: ljmp \_Counter16\_C\_ISR

- 30. Save the project.

- 31. To Build the project, click  $Build \rightarrow Build 'Ex3\_ADC\_to\_UART\_with\_DAC'$  Project.

- 32. Disconnect power to the board.

- 33. Configure the DVK breadboard SW3 to 5V.

- 34. Configure the DVK breadboard using the included jumper wires as follows:

- □ P0 1 to VR

- □ P1 2 to TX

- □ P0 5 to Scope

**Note:** An LED (P0\_5 to LED1) by nature does not accurately show the changes in frequency the best way to see this is to use a Scope(P0\_5 to Scope).

Figure 3-38. Connect P0\_1 to VR, P1\_2 to TX, and P0\_5 to LED1

- 35. Connect a serial cable to the PC and the DVK board.

- 36. On the DVK board, verify that RS232\_PWR(J10) is jumpered to ON.

- 37. Reapply power to the board.

- 38.Use a terminal application such as TeraTerm or HyperTerminal with these setup parameters.

- □ Baud Rate: 38400

- □ Data: 8-bit

- □ Parity: none

- □ Stop: 1bit

- □ Flow Control: none

- 39. Use PSoC Designer as described in Programming My First PSoC 1 Project on page 11 to program the device.

After programming the device, press Reset and vary the pot to see the result on the LCD as well as in the terminal application. View the DAC output on a scope or with an LED.

**Note:** The ADC output values may not reach full range due to potentiometer and ADC limitations. ADC values may fluctuate several counts due to system noise, and if the potentiometer voltage is at the edge of an ADC count.

40. Save and close the project.

#### 3.1.3.2 main.c

- 1. Open the existing *main.c* file within **Workspace Explorer**.

- 2. Replace the existing *main.c* content with the content of the embedded *CY8C28\_main\_Ex3.c* file, which can be found within the attachments feature of this PDF document.

**Note:** To access the embedded attachments feature in the PDF document, click on the paper clip icon located in the lower left corner of the Adobe Reader application.

```

/* part specific constants and macros */

#include <m8c.h>

#include "PSoCAPI.h"

/* PSoC API definitions for all User Modules */

/* Counter16 Interrupt Handler */

#pragma interrupt_handler Counter16_C_ISR

/* LCD specific */

#define ROW 1 1 /* LCD row 1

* /

#define COLUMN_0 0 /* LCD column 0 */

#define COLUMN_9 9 /* LCD column 9 */

const BYTE sinTable[]=

0\,,\quad 0\,,\quad 1\,,\quad 2\,,\quad 3\,,\quad 4\,,\quad 6\,,\quad 7\,,\ 10\,,\ 12\,,\ 14\,,\ 17\,,\ 20\,,\ 23\,,\ 26\,,\ 29\,,

31, 33, 36, 39, 41, 44, 46, 49, 51, 53, 55, 56, 58, 59, 59, 60,

60, 60, 59, 59, 58, 56, 55, 53, 51, 49, 47, 44, 42, 39, 36, 33,

31, 28, 25, 22, 19, 16, 13, 11, 9, 7, 5, 3, 2, 1, 0, 0

};

BYTE tablePos = 0;

/********************************

* Function Name: main

*************************

* Summary:

The main function initializes the ADC, PGA, LCD, Counter, DAC and UART.

In the main loop, it continuously checks for an ADC conversion. If there is

one then it displays the ADC raw count to the LCD, transmits the raw count

serially, and updates the Counter16 period (based on the raw count) for the

DAC output.

* Parameters:

void

* Return:

* void

*************************************

void main(void)

/* Variable for holding ADC result, and updating counter period */

WORD adcResult;

Counter16_1_Start();

/* Enable the counter used for DAC update rate */

Counter16_1_EnableInt();  /* Enable DAC update interrupt */

```

```

/* Start the TX8 UM with no parity (baud rate = 38400) */

TX8_1_Start(TX8_1_PARITY_NONE);

/* Enable to PGA to buffer signal from VR to ADC */

PGA_1_Start(PGA_1_HIGHPOWER);

DAC6_1_Start(DAC6_1_HIGHPOWER);

/* Start the DAC */

DelSigPlus_1_Start(DelSigPlus_1_HIGHPOWER); /* Start the ADC */

DelSigPlus_1_StartAD();

/* Start reading values on the ADC */

LCD_1_Start();

/* Start the character LCD */

LCD_1_Position(ROW_0, COLUMN_0); /* Set the LCD to (Row=0,Column=0) */

LCD_1_PrCString("V Count: ");

M8C EnableGInt;

/* Enable Global Interrupts */

while(1)

/* Step 1: Get BYTE data from the ADC

Step 2: Write BYTE data from ADC to the counter in order to

change the DAC update rate

Step 3: Move the LCD cursor back to the beginning and display new

ADC data

Step 4: Write ADC data out the TX port, and then send a return

* /

/* Is new data available from the ADC? */

if (DelSigPlus_1_fIsDataAvailable())

adcResult = DelSigPlus_1_wGetDataClearFlag(); /* Get new ADC data */

/* Change DAC update rate counter */

Counter16_1_WritePeriod((adcResult << 4) + 200);</pre>

LCD_1_Position(ROW_0, COLUMN_9); /* Move LCD (row=0,column=0) */

LCD_1_PrHexInt(adcResult); /* Print ADC result to LCD */

TX8_1_PutSHexInt(adcResult); /* Write LCD result to TX8 -> PC */

/* Write return character to TX8 */

TX8 1 PutCRLF();

} /* End of while(1) */

} /* End of Main */

/******************************

* Function Name: Counter16_C_ISR

******************

* Summary:

This is the interrupt service routine for the Counter16 usermodule written

in C. The boot.tpl has been modified to jump to this ISR every terminal

count. The related #pragma above is necessary for the boot.asm file to jump

to it. Every time a terminal count is reached the DAC will get the next

value from the sinTable.

* Parameters:

* void

* Return:

biov *

```

# 3.1.4 CapSense<sup>®</sup>

This project demonstrates CapSense. The firmware displays the CapSense button presses on the LCD (row 1) and associated LEDs. It also displays the CapSense slider position on the LCD (row 2).

Note that this project uses IDAC. But if using external Rb with CSD is desired then populate R15 (connected to P3[1]). Rb can range from 2k to 10k. Do refer to CapSense user module datasheet for more information on using Rb.

## 3.1.4.1 Creating CapSense Project

- 1. Follow steps 1 to 10 in section 3.1.1.1 on page 13, change the **Name** of the project to **Ex4 CapSense**.

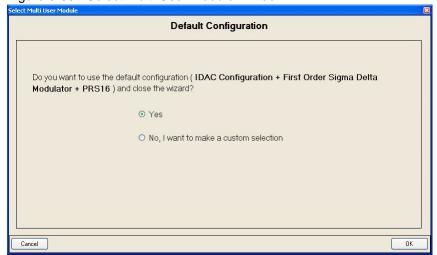

- 2. In the User Modules window expand the Cap Sensors folder. Right click **CSD** and choose **Place**. A window appears with the option to use the default configuration.

Figure 3-39. Select Multi User Module Window

- 3. Select Yes and click OK.

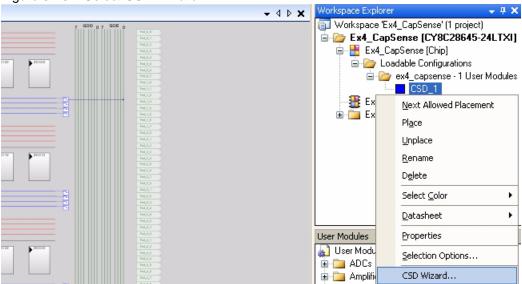

- 4. Right click the CSD user module in the workspace explorer and select CSD Wizard.

Figure 3-40. Select CSD Wizard

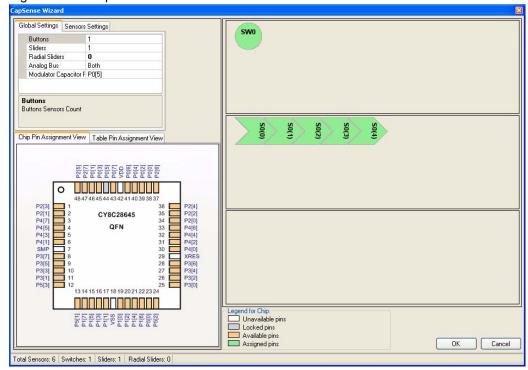

5. CapSense Wizard window opens.

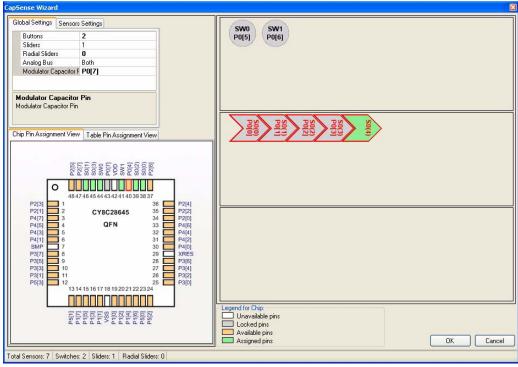

Figure 3-41. CapSense Wizard

- 6. In the CapSense Wizard window, under the **Global Settings** Tab, set the # of buttons to 2.

- 7. Select P0.7 as the Modulator Capacitor Pin.

OK

Cancel

Global Settings | Sensors Settings Buttons Radial Sliders Analog Bus Both

Modulator Capacitor F P0[7] Modulator Capacitor Pin Modulator Capacitor Pin Chip Pin Assignment View Table Pin Assignment View 0 P2[3] P2[1] P4[7] P4[5] P4[3] P4[1] SMP P3[7] P3[5] P3[3] P2[4] P2[2] P2[0] P4[6] P4[4] P4[2] P4[0] XRES P3[6] P3[4] P3[2] P3[0] Legend for Chip:

Unavailable pins

Locked pins Available pins

Assigned pins

Figure 3-42. CapSense Wizard Place Buttons

8. Click and hold **SW0** and drag it to P0.5.

Total Sensors: 7 | Switches: 2 | Sliders: 1 | Radial Sliders: 0 |

9. Do the same for SW1 and drag it to P0.6

Figure 3-43. CapSense Wizard Slider Sensors

10. Do the same thing for each slider sensor and corresponding pin.

- □ S0.0 to P0.0

- □ S0.1 to P0.1

- □ S0.2 to P0.2

- □ S0.3 to P0.3

- □ S0.4 to P0.4

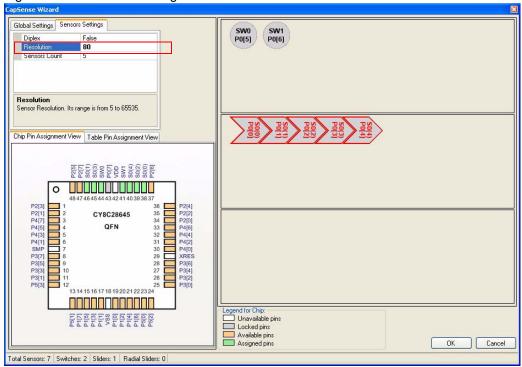

- 11. Select the **Sensors Settings** Tab

- 12. Set the Resolution to 80.

Figure 3-44. Sensors Settings Tab

#### 13.Click OK

- 14. In the User Modules window expand Misc Digital, right click LCD, and click place.

- 15. In the User Modules window expand Misc Digital, right click LED, and click place.

- 16. In the User Modules window expand Misc Digital, right click LED, and click place.

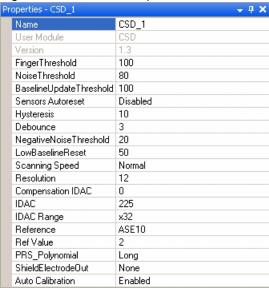

- 17. Click CSD\_1 and configure it to match this figure.

Figure 3-45. CSD\_1 Properties

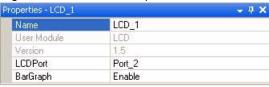

18. Click **LCD\_1** and configure it to match this figure.

Figure 3-46. LCD\_1 Properties

19. Click **LED\_1** and configure it to match this figure.

Figure 3-47. Figure . LED\_1 Properties

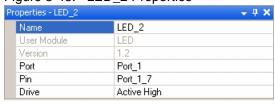

20. Click **LED\_2** and configure it to match this figure.

Figure 3-48. LED\_2 Properties

21. Configure Global Resources to match the following figure.

Figure 3-49. Configure Global Resources

- 22. Open the existing *main.c* file within Workspace Explorer. Replace the existing *main.c* content with the content of the embedded *CY8C28\_main\_Ex4.c* file, which can be found within the attachments feature of this PDF document.

- 23. Save the project.

- 24. To Generate and build the project, click Build → Generate/Build 'Ex4\_CapSense' Project.

- 25. Disconnect power to the board.

- 26. Configure the DVK board SW3 to 5V.

- 27. Configure the DVK breadboard using the included jumper wires:

- P1 6 to LED1

- P1 7 to LED2

- 28. Ensure that P0\_1, P0\_5, and P0\_7 are disconnected.

- 29. Reapply power to the board.

- 30. Use PSoC Designer as described in Programming My First PSoC 1 Project on page 13 to program the device.

- 31.Reset the DVK. An LED lights up when either CapSense button is pushed. If B1 (P0[5]) is pushed it also displays "Button1" in the top row of the LCD display. Likewise, if B2 (P0[6]) is pushed it displays "Button2" in the top row of the LCD display. The bottom row of the LCD displays the Slider position with a Horizontal Bar graph.

- 32. Save and close the project.

#### 3.1.4.2 main.c

- 1. Open the existing *main.c* file within **Workspace Explorer**.

- 2. Replace the existing *main.c* content with the content of the embedded *CY8C28\_main\_Ex4.c* file, which can be found within the attachments feature of this PDF document.

**Note:** To access the embedded attachments feature in the PDF document, click on the paper clip icon located in the lower left corner of the Adobe Reader application.

```

/* PSoC API definitions for all User Modules */

/* LCD specific */

\#define ROW_0 0 /* LCD row 0

1 /* LCD row 1

#define ROW 1

#define COLUMN_0 0 /* LCD column 0 */

#define NUM_CHARACTERS 16 /* Number of characters on LCD */

/* For clearing a row of the LCD*/

#define CLEAR ROW STR

/* Button 1 only string for row 0 of the LCD */

/* Button 2 only string for row 0 of the LCD */

#define BUTTON 2 STR

II .

Button2"

/* Button 1 and 2 string for row 0 of the LCD */

/* Default string for button row of the LCD */

#define DEFAULT_ROW_0_STR "Touch Buttons "

/* Default string for slider row of the LCD */

#define DEFAULT ROW 1 STR "Touch The Slider"

/* CapSense specific */

#define SLIDER_RESOLUTION 80

#define SCANSENSOR_BTN_B1 0

#define SCANSENSOR_BTN_B2 1

void UpdateButtonState(BYTE sensor_1, BYTE sensor_2);

void UpdateSliderPosition(BYTE value);

/*********************************

* Function Name: main

******************

* The main function initializes CapSense and the LCD. Then it continuously

* scans all CapSense sensors (slider sensors and buttons), gets the state of

^{\star} the buttons and slider and updates the LCD with the current state.

* Parameters:

void

* Return:

* void

*************************

void main(void)

```

```

/* Slider Position */

BYTE stateB_1; /* Button1 State */

BYTE stateB_2; /* Button2 State */

M8C_EnableGInt; /* Enable Global Interrupts */

/* LCD Initialization */

LCD_1_Start();

/* For Bargraph display on LCD */

LCD_1_InitBG(LCD_1_SOLID_BG);

/* LED1 Initialization */

LED_1_Start();

/* LED2 Initialization */

LED 2 Start();

/* CapSense Initialization */

CSD 1 Start();

/* Initialize the baselines by scanning all sensors and getting the initial

raw data values */

CSD 1 InitializeBaselines();

/* Load finger thresholds set in user module parameters */

CSD_1_SetDefaultFingerThresholds();

while(1)

/* Scan each CapSense sensor and update their raw data value */

CSD_1_ScanAllSensors();

/* Update baselines for each sensor */

CSD_1_UpdateAllBaselines();

/* Update state to active/inactive for each button sensor */

stateB_1 = CSD_1_bIsSensorActive(SCANSENSOR_BTN_B1);

stateB_2 = CSD_1_bIsSensorActive(SCANSENSOR_BTN_B2);

/* Get Linear Slider Position */

pos = CSD_1_wGetCentroidPos(1);

/* Update LCD and LED's with current Button and Linear Slider states */

UpdateButtonState(stateB_1, stateB_2);

UpdateSliderPosition(pos);

}

}

/**********************************

* Function Name: UpdateButtonState

***********************

* Summary:

Updates the LCD screen with the current button state by displaying which

* button is being touched on row 0. LED's are also updated according to button

state.

* Parameters:

* sensor_1: Button state for B1

* sensor_2: Button state for B2

* Return:

```

```

void

void UpdateButtonState(BYTE sensor_1, BYTE sensor_2)

LCD_1_Position(ROW_0,COLUMN_0);

/* Check the state of the buttons and update the LCD and LEDs */

if (sensor_1 && sensor_2)

/* Display both Button strings on LCD if both button sensors are active */

LCD_1_PrCString(BUTTON_1_2_STR);

/* Both LED's are on in this state */

LED 1 On();

LED_2_On();

else if (sensor_1 || sensor_2)

if (sensor_1)

/* Display Button 1 state on LCD and LED1 */

LCD_1_PrCString(BUTTON_1_STR);

LED_1_On();

/* Button 2 is not active */

LED_2_Off();

else // sensor_2

/* Display Button 2 state on LCD and LED2 */

LCD_1_PrCString(BUTTON_2_STR);

LED_2_On(); /* Turn on LED2 */

LED_1_Off(); /* Turn off the LED1 */

}

else

/* Display default string on LCD and set LED's to off */

LCD_1_PrcString(DEFAULT_ROW_0_STR);

/* Set both LED's off in this state */

LED_1_Off();

LED_2_Off();

}

/****************************

* Function Name: UpdateSliderPosition

* Summary:

Updates the LCD screen with the current slider position by displaying the

horizontal bar graph.

* Parameters:

value: Centroid position from CapSense slider.

* Return:

void

```

# Appendix A. Board Specifications and Layout

This appendix gives detailed specifications of the PSoC Development Kit Board components

# 2.1 PSoC Development Board

# 2.1.1 Factory Default Configuration

## 2.1.1.1 Power Supply

The board has several power nets. Below are the definitions of the different power nets.

VIN (9V or 12V) - This is the input power before it is fed to any of the regulators. A 9-12V wall wart supply or a 9V battery is used as the source.

VREG (5V) - This is fed by VIN and is the output of the onboard 5V regulator. VREG can be selected as the main 5V source by using the J8 header.

VBUS (5V) - This is power derived from the USB interface via a USB host. VBUS can be selected as the main 5V source by using the J8 header.

VDD (3.3V or 5V) - This is fed by VREG, VBUS, or the onboard 3.3V regulator. VDD can be chosen either to be 3.3V or 5V by the simple positioning of the VDD select switch.

VADJ (1.25V to 3.9V) - This is fed by VDD and is the output of the onboard adjustable regulator. It is mainly used when the PSoC core must be powered at lower voltages. An adjustable resistor R11 is used for adjusting the voltage.

VDD DIG - This is power derived from either VDD or VADJ. It is used to power the PSoC core. The source for VDD DIG can be chosen as VDD or VADJ using the J7 header.

VDD ANLG - This is power derived from either VDD or VADJ. It is mainly used when user wants to separate the analog power from the digital power. The source for VDD ANLG can be chosen as VDD or VADJ using the J7 header.

VDDIO - This is power derived from either VDD or VADJ. It is used to power digital I/O on the PSoC device. There are four sections of GPIO, which can be powered to 5V, 3.3V, or VADJ using four headers. It enables the user to power the PSoC GPIOs at different voltages.

# 2.1.2 Power Supply Configuration Examples

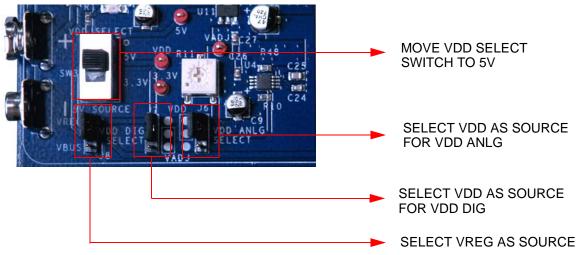

# 2.1.2.1 Setting a 5V Supply from VREG

- 1. Place the jumper on J8 header to select VREG as the source.

- 2. Move the VDD select switch to select the 5V.

- 3. Place the jumper on J6 header to select VDD as source for VDD ANLG.

- 4. Place the jumper on J7 header to select VDD as source for VDD DIG.

Note 5V operation is not recommended with ES1 Silicon. See the silicon errata for details.

Figure 2-1. Setting a 5V Supply from VREG

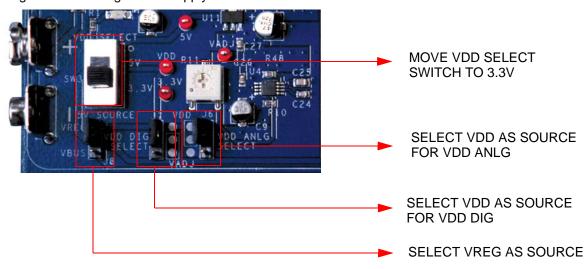

#### 2.1.2.2 Setting a 3.3V Supply from VREG

- 1. Place the jumper on J8 header to select VREG as the source.

- 2. Move the VDD select switch to select 3.3V.

- 3. Place the jumper on J6 header to select VDD as source for VDD ANLG.

- 4. Place the jumper on J7 header to select VDD as source for VDD DIG.

Figure 2-2. Setting a 3.3V Supply from VREG

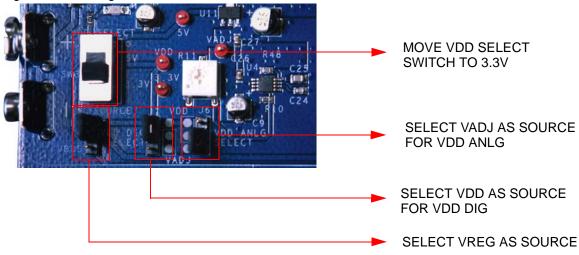

#### 2.1.2.3 Setting VDD ANLG as VADJ and VDD DIG as VDD for VDD = 3.3V

- 1. Place the jumper on J8 header to select VREG as the source.

- 2. Move the VDD select switch to select 3.3V.

- 3. Place the jumper on J6 header to select VADJ as source for VDD ANLG.

- 4. Place the jumper on J7 header to select VDD as source for VDD DIG.

Figure 2-3. Setting VDD ANLG as VADJ and VDD DIG as VDD for VDD = 3.3V

This helps to separate the analog supply from the digital supply and VDD.

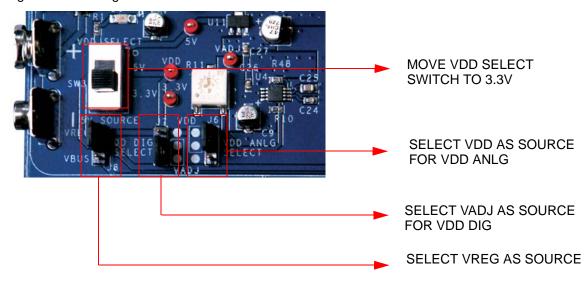

# 2.1.2.4 Setting VDD DIG as VADJ and VDD ANLG as VDD for VDD = 3.3V

- 1. Place the jumper on J8 header to select VREG as the source.

- 2. Move the VDD select switch to select 3.3V.

- 3. Place the jumper on J6 header to select VDD as source for VDD ANLG.

- 4. Place the jumper on J7 header to select VADJ as source for VDD DIG.

Figure 2-4. Setting VDD DIG as VADJ and VDD ANLG as VDD for VDD = 3.3V

This helps to separate the digital supply from the analog supply and VDD.

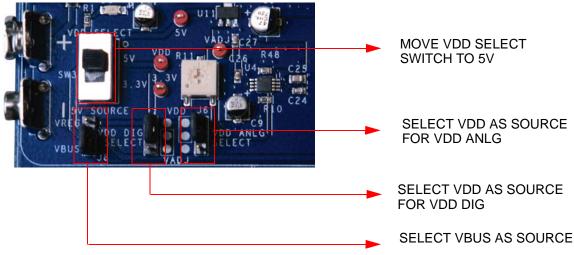

## 2.1.2.5 Setting a 5V Supply from VBUS

- 1. Place the jumper on J8 header to select VBUS as the source.

- 2. Move the VDD select switch to select the 5V.

- 3. Place the jumper on J6 header to select VDD as source for VDD ANLG.

- 4. Place the jumper on J7 header to select VDD as source for VDD DIG.

Note 5V operation is not recommended with ES1 Silicon. See the silicon errata for details.

Figure 2-5. Setting a 5V Supply from VBUS

# 2.1.2.6 Setting a 3.3V Supply from VBUS

Due to the nature of the PSoC Development Board, powering the system from USB 'VBUS' could potentially reset other USB devices on the same hub.

By design, the PSoC Development Board is capable of drawing more than 500mA of current during normal operation, which exceeds USB bus power limits. Additionally, the development board exceeds inrush current limits due to 'VBUS' capacitance greater than 10uF. As a result, plugging the PSoC Development Board into a USB hub could potentially cause other devices on the same hub to reset due to excessive inrush currents. Careful consideration should be taken when powering the PSoC Development Board from 'VBUS'. In general, it is good practice to plug the PSoC Development Board into a host root hub, or a "self-powered" external hub when doing USB development. Bus powered applications done outside the realm of the PSoC Development Board should comply to the USB specification for inrush current limits and recommended bulk capacitance on 'VBUS'. See the Universal Serial Bus Specification Revision 2.0 for more details.

- 1. Place the jumper on J8 header to select VBUS as the source.

- 2. Move the VDD select switch to select 3.3V.

- 3. Place the jumper on J6 header to select VDD as source for VDD ANLG.

- 4. Place the jumper on J7 header to select VDD as source for VDD DIG.

Figure 2-6. Setting a 3.3V supply from VBUS

You can measure current from VREG, VBUS, VDD ANLG, VDD DIG and VDDIOs by removing the jumpers and connecting the meter across the respective header.

#### 2.1.2.7 J1 - DC Power Jack

Figure 2-7. DC Power Jack

Use a 12V/1A wall wart power supply when powering from the barrel power jack. This input power is VIN.

## 2.1.2.8 9V Battery Terminals

Figure 2-8. Battery Terminals

Use a 9V alkaline battery to connect to the 9V battery terminals. This input power is VIN.

#### 2.1.2.9 J8 - 5V Source

This header allows the user to select the 5V source from either the onboard 5V regulator (VREG) or from the USB 5V rail (VBUS).

#### 2.1.2.10 VDD Select Switch

This switch allows for selecting either 5V or 3.3V. VDD feeds VDD DIG, VDD ANLG and VDDIO.

#### 2.1.2.11 J7 - VDD DIG Select

This header allows the user to select the PSoC core source power. If you need to power the PSoC core at either 5V or 3.3V (based on the position of the VDD select switch), place the jumper on the upper two pins. If you need to power the PSoC core at lower voltages (1.25V to 3.9V), then place the jumper on the lower two pins. When the jumper is on the lower two pins, you must adjust R11 to tune the adjustable regulator to output the desired voltage.

#### 2.1.2.12 J6 - VDD ANLG Select

If you want to separate the analog power from the digital power, you can position the jumper on the upper two pins to source analog power at 5V or 3.3V (based on the position of the VDD select switch), or on the lower two pins to source analog power at lower voltages (1.25V to 3.9V).

### 2.1.2.13 R11 - Adjustable Regulator Variable Resistor

This adjustable resistor is used to tune the VADJ voltage. Turning this variable resistor swings the VADJ voltage between 1.25V and 2.3V when the VDD select switch is in the 3.3V position. When the VDD select switch is in the 5V position, turning this variable resistor swings the VADJ voltage between 1.25V and 3.9V.

# 2.1.3 Prototyping Components

## 2.1.3.1 Prototyping Area

Note Port1 pins are used for SWD/JTAG. The P1\_6 and P1\_7 pins are used for CapSense.

#### 2.1.3.2 P15 - DB9 Serial Communications Port

This is a standard female DB9 serial communications connector. Four signals are brought from the RS232 transceiver to receptacle P16. These signals are Rx, Tx, Clear To Send, and Request To Send. To connect these signals to the PSoC I/O pins, use wires to jumper from P16 to P19, where sockets for ports zero and one are available.

Table 2-1. Connector Pin Assignments - RS232 (DTE) Serial Communications Socket

| Pin Number | P15     |

|------------|---------|

| 1          | (Empty) |

| 2          | TX      |

| 3          | RX      |

| 4          | (Empty) |

| 5          | GND     |

| 6          | (Empty) |

| 7          | CTS     |

| 8          | RTS     |

| 9          | (Empty) |

#### 2.1.3.3 J10 - Serial Port Power

Header J10 must be jumpered in order to use the serial communications port. Placing a jumper on J10 provides VDD power to the RS232 transceiver. This power can be either 3.3V or 5V, depending on which the position of the VDD select switch.

## 2.1.3.4 J9 - Full Speed USB Port

The board has a mini-B full speed USB connector. There are also two test points for the differential pair signals D- and D+. These signals are routed to the processor module socket P1, pins 6 and 8 respectively. The power net VBUS is brought into the board through this interface.

## 2.1.3.5 P17 - Artaflex WirelessUSB LP Radio Module Receptacle

Receptacle P17 is used specifically for the Artaflex AWP24S WirelessUSB module. Eight signals are routed from this receptacle to P12 receptacle. These signals are 4 SPI (serial peripheral interface) signals MISO (master-in-slave-out), MOSI (master-out-slave-in), nSS (slave select), SCK (serial clock), an IRQ (interrupt request) and RD\_RESET (radio reset). The other two signals are radio transmit and receive signals. **Note**: These I/O signals must not be greater than 3.3V.

Table 2-2. Connector Pin Assignments - Wireless Radio Module Socket

| Pin Number | P17      |

|------------|----------|

| 1          | GND      |

| 2          | V3_3     |

| 3          | IRQ      |

| 4          | RD_RESET |

| 5          | MOSI     |

| 6          | nSS      |

| 7          | SCK      |

| 8          | MISO     |

| 9          | GND      |

| 10         | (Empty)  |

| 11         | TxPA     |

| 12         | RxPA     |

#### 2.1.3.6 J14 - Wireless Radio Module Power

Header J14 must be jumpered in order to use the Artaflex radio module. Placing a jumper on J14 provides 3.3V power to the P17 module socket. This power is drawn directly from the 3.3V regulator.

## 2.1.3.7 R20 - Multipurpose Variable Resistor

The board is equipped with a 10 k $\Omega$  thumbwheel variable resistor referenced to ground. The high side of the resistor is tied to jumper J11. The wiper is tied to a receptacle pin on P14.

#### 2.1.3.8 J11 - Variable Resistor Power

Header J11 must be jumpered in order to use the variable resistor. Placing a jumper on J11 provides VDD ANLG power to the high side of the resistor.

## 2.1.3.9 SW1 and SW2 - Multipurpose Push Button Switches

The board has two multipurpose mechanical push buttons, SW1 and SW2, that are referenced to ground. The other sides of the switches are tied to receptacle pins on P14. The switches follow an inverted logic as they connect ground to receptacle pins on P14 when pressed.

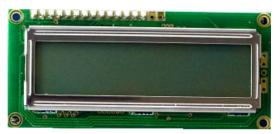

#### 2.1.4 LCD Module

The board has a 2x16 alpha-numeric LCD. I/Os of the module are connected to port two of the PSoC device and are routed to the processor module socket P2. This LCD is rated for 5V. However, the I/Os have a level translator inline so that signaling may be as low as 1.8V and still be recognized by the LCD. The header J12 must be jumpered for the LCD Module to be powered. If J12 is not jumpered, it removes power from level translator. If the LCD module is removed, the receptacle pins of P18 can be used as port 2.

Table 2-3. Connector Pin Assignments - LCD Module Socket

| Pin Number | P18     |

|------------|---------|

| 1          | GND     |

| 2          | VCC_LCD |

| 3          | VO      |

| 4          | RS      |

| 5          | R/nW    |

| 6          | EN      |

| 7          | D0      |

| 8          | D1      |

| 9          | D2      |

| 10         | D3      |

| 11         | D4      |

| 12         | D5      |

Table 2-3. Connector Pin Assignments - LCD Module Socket (continued)

| Pin Number | P18                |

|------------|--------------------|

| 13         | D6                 |

| 14         | D7                 |

| 15         | BACKLT LED ANODE   |

| 16         | BACKLT LED CATHODE |

#### 2.1.4.1 R31 - LCD Contrast Adjustment

The board is equipped with an LCD contrast adjustment resistor R31. Turning the wiper counterclockwise increases the contrast, while turning the wiper clockwise decreases the contrast.

#### 2.1.4.2 J12 - LCD Module Power

Power for the LCD module is provided through header J12. Placing a jumper on the upper two pins shorts the VCC pin of the module to ground. Placing the jumper on the lower two pins provides 5V to the VCC pin of the module. This 5V power is taken directly from the onboard 5V regulator.

## 2.1.5 CapSense Elements

The prototyping area has three capacitive sensing elements. There are two CapSense buttons connected directly to port zero pins. In addition, there is a five segment CapSense slider also connected directly to port zero. Series resistors are placed on these port zero I/Os and should be loaded with appropriate values. A value of  $0\Omega$  is used for general purpose CapSense applications, but a value of  $560\Omega$  should be used for achieving best performance. The board is loaded with  $0\Omega$  series resistors by default. The presence of CapSense elements does not affect the general purpose use of port zero pins.

#### 2.1.6 Processor Module

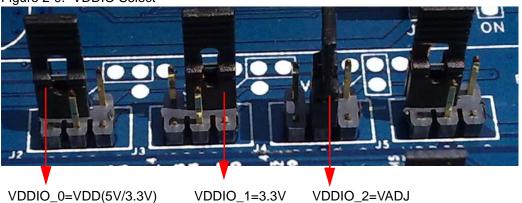

# 2.1.6.1 J2, J3, J4 and J5 - VDDIO Select

These four headers allow the user to power the PSoC GPIOs at different voltages. For instance, some of the I/O may be powered at 5V, some at 3.3V and some at 1.8V. There are four blocks of GPIO, each having its own source power. Each VDDIO header provides power to specific GPIO's and is selectable from VDD, 3.3V or VADJ. For details on which GPIOs are powered by which VDDIO header, refer to the data sheet for the PSoC device used with this board.

For example, VDDIO\_0 is configured to VDD, VDDIO\_1 is configured to 3.3V and VDDIO\_2 is configured to VADJ by placing the jumpers in the respective positions as shown in Figure 2-9.

Figure 2-9. VDDIO Select

#### 2.1.6.2 SW4 - Processor Reset Button

The board has a push button switch that resets the PSoC device attached to the processor module. One side of the switch is tied to the XRES pin of the processor module socket. The other end of the switch is tied to the HW\_RESET pin of the processor module socket. Doing this allows the module designer to tie the HW\_RESET line either high or low, depending on which direction the processor reset is active.

**Note** PSoC 1 devices are active high reset. Therefore, a light pull-down resistor may be necessary on the XRES pin of designs with these devices to avoid unintentional device resets. PSoC 3 and PSoC 5 devices are active low reset. Therefore, a light pull-up resistor may be necessary on the XRES pin of designs with these devices to avoid unintentional device resets.

#### 2.1.6.3 U8 - External MHz Oscillator

The board supports the use of an external high frequency 8-pin PDIP oscillator. The speed of the oscillator supported is dependent on the specifications of the PSoC device used. The output of this oscillator is routed to P15 4 on receptacle P2 and TP62 near P2 of the DVK board.

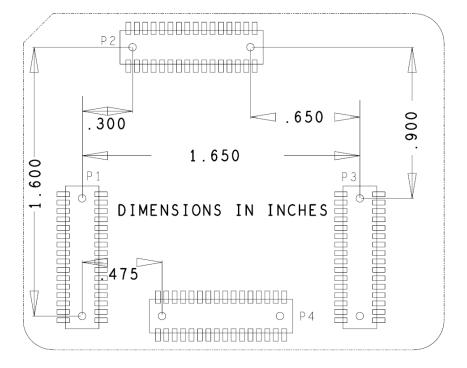

## 2.1.6.4 P1, P2, P3 and P4 - Processor Module Receptacles

Processor modules provide modularity to this board. Sockets P1-P4 are used to connect a processor module to the board. All supported GPIOs (including special I/Os), along with VDD DIG, VDD ANLG, 5V, 3.3V, VBUS and VBAT (only connected to a surface mount pad on the board) are connected to these receptacles. In addition, each of the VDDIO power pins are connected to these receptacles. The full speed USB D+ and D- signals are also connected to one of the sockets. Processor reset is connected to P1. Any "no connect" pins are brought out to surface mount test pads.

| Table 2-4  | Connector Pin | Assignments        | - Processor  | Module Sockets |

|------------|---------------|--------------------|--------------|----------------|

| IADIC Z-T. |               | - Maaiuiiii leiita | - 1 10053301 | MODULE OUCKELS |

| Pin Number | P1 (West) | P2 (North) | P3 (East) | P4 (South) |

|------------|-----------|------------|-----------|------------|

| 1          | GND       | GND        | GND       | GND        |

| 2          | VDDD      | GND        | GND       | P7_7       |

| 3          | V5_0      | P6_1       | P12_2     | NC7        |

| 4          | GND       | P6_0       | P12_3     | NC8        |

| 5          | VBAT      | P6_3       | P8_0      | NC5        |

| 6          | DM        | P6_2       | P8_1      | NC6        |

| 7          | V3_3      | P15_5      | P4_0      | NC3        |

| 8          | DP        | P15_4      | P4_1      | NC4        |

| 9          | VBUS      | P9_2       | P8_2      | P7_6       |

| 10         | VDDIO1    | P9_0       | P8_3      | P7_5       |

| 11         | P5_6      | P2_1       | P0_0      | P12_0      |

| 12         | P5_7      | P2_0       | P0_1      | P12_1      |

| 13         | P5_4      | P2_3       | P0_2      | P3_6       |

| 14         | P5_5      | P2_2       | P0_3      | P3_7       |

| 15         | P12_6     | VDDIO2     | VDDIO0    | P7_4       |

| 16         | P12_7     | P9_3       | VDDA      | VDDIO3     |

| 17         | P1_6      | P2_5       | P0_4      | P3_4       |

| 18         | P1_7      | P2_4       | P0_5      | P3_5       |

| 19         | P1_4      | P2_7       | P0_6      | P3_2       |

| 20         | P1_5      | P2_6       | P0_7      | P3_3       |

Table 2-4. Connector Pin Assignments - Processor Module Sockets (continued)

| Pin Number | P1 (West) | P2 (North) | P3 (East) | P4 (South) |

|------------|-----------|------------|-----------|------------|

| 21         | HW_RESET  | P9_4       | P8_4      | P3_0       |

| 22         | P1_3      | P9_5       | P8_5      | P3_1       |

| 23         | P1_1      | P12_5      | P8_6      | P7_2       |

| 24         | P1_2      | P12_4      | P8_7      | P7_3       |

| 25         | P1_0      | P9_6       | P4_2      | (Empty)    |

| 26         | P5_3      | P9_7       | P4_3      | (Empty)    |

| 27         | P5_2      | P6_5       | P4_4      | P7_0       |

| 28         | P5_1      | P6_4       | P4_5      | P7_1       |

| 29         | P5_0      | P6_7       | P4_6      | NC1        |

| 30         | XRES      | P6_6       | P4_7      | NC2        |

| 31         | GND       | GND        | GND       | GND        |

| 32         | GND       | GND        | P9_1      | GND        |

Figure 2-10. Mechanical Layout Details for Processor Module Connector

# 2.1.7 Expansion Ports

The board accommodates I/O expandability. Around the upper, lower and right sides of the board are 0.100" pitch, dual row right angle receptacles, each having at least three full 8-bit ports (one has four full ports). Each also has four special I/O pins available. Three of the ports have power and ground pins as well. The fourth is simply I/O and ground exclusively. These sockets can be used to join the processor module I/Os with external I/Os through the use of daughter boards.

Table 2-5. Connector Pin Assignments - Expansion Port Sockets

| Pin Number | P5 (PORT B) | P6 (PORT A') | P7 (PORT A) | P8 (PORT C) |

|------------|-------------|--------------|-------------|-------------|

| 1          | P1_7        | P6_7         | P3_7        | P9_7        |

| 2          | P1_6        | P6_6         | P3_6        | P9_6        |

| 3          | P1_5        | P6_5         | P3_5        | P9_5        |

| 4          | P1_4        | P6_4         | P3_4        | P9_4        |

| 5          | P1_3        | P6_3         | P3_3        | P9_3        |

| 6          | P1_2        | P6_2         | P3_2        | P9_2        |

| 7          | P1_1        | P6_1         | P3_1        | P9_1        |

| 8          | P1_0        | P6_0         | P3_0        | P9_0        |

| 9          | GND         | GND          | GND         | GND         |

Table 2-5. Connector Pin Assignments - Expansion Port Sockets (continued)

| Pin Number | P5 (PORT B) | P6 (PORT A') | P7 (PORT A) | P8 (PORT C) |

|------------|-------------|--------------|-------------|-------------|

| 10         | RESRV3      | RESRV8       | RESRV11     | RESRV14     |

| 11         | P2_7        | P2_7         | P5_7        | P8_7        |

| 12         | P2_6        | P2_6         | P5_6        | P8_6        |

| 13         | P2_5        | P2_5         | P5_5        | P8_5        |

| 14         | P2_4        | P2_4         | P5_4        | P8_4        |

| 15         | P2_3        | P2_3         | P5_3        | P8_3        |

| 16         | P2_2        | P2_2         | P5_2        | P8_2        |

| 17         | P2_1        | P2_1         | P5_1        | P8_1        |

| 18         | P2_0        | P2_0         | P5_0        | P8_0        |