# CYIL2SM1300AA

# LUPA 1300-2: High Speed CMOS Image Sensor

# Features

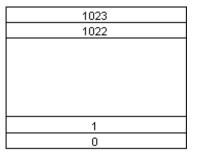

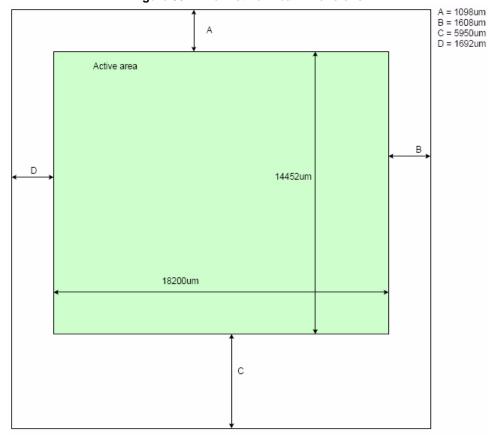

- 1280 x 1024 Active Pixels

- 14 µm X 14 µm Square Pixels

- 1" Optical Format

- Monochrome or Color Digital Output

- 500 fps Frame Rate

- On-Chip 10-Bit ADCs

- 12 LVDS Serial Outputs

- Random Programmable ROI Readout

- Pipelined and Triggered Snapshot Shutter

- On-Chip Column FPN Correction

- Serial to Parallel Interface (SPI)

- Limited Supplies: Nominal 2.5V and 3.3V

- 0°C to 70°C Operational Temperature Range

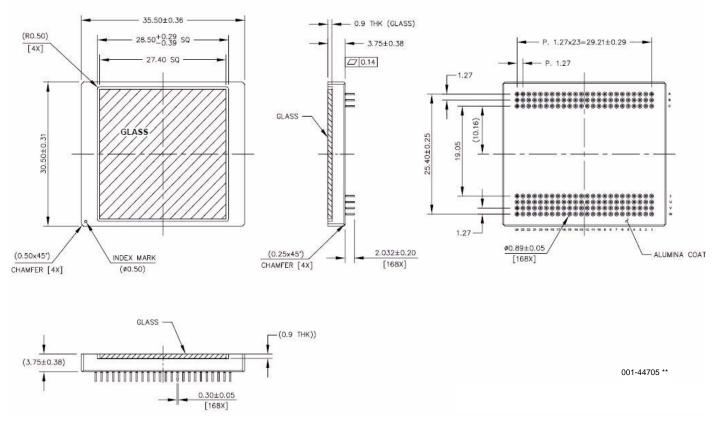

- 168-Pin µPGA Package

- Power Dissipation: 1350 mW

# Applications

- High Speed Machine Vision

- Motion Analysis

- Intelligent Traffic System

- Medical Imaging

- Industrial Imaging

# Description

The LUPA 1300-2 is an integrated SXGA high speed, high sensi-tivity CMOS image sensor. This sensor targets high speed machine vision and industrial monitoring applications. The LUPA 1300-2 sensor runs at 500 fps and has triggered and pipelined shutter modes. It packs 24 parallel 10-bit A/D converters with an aggregate conversion rate of 740 MSPS. On-chip digital column

# **Ordering Information**

FPN correction enables the sensor to output ready to use image data for most applications. To enable simple and reliable system integration, the 12 channels, 1 sync channel, 8 Gbps, and LVDS serial link protocol supports skew correction and serial link integrity monitoring.

The peak responsivity of the 14  $\mu$ m x 14  $\mu$ m 6T pixel is 7350 V.m2/W.s. Dynamic range is measured at 57 dB. In full frame video mode, the sensor consumes 1350 mW from the 2.5V power supply. The sensors integrate A/D conversion, on-chip timing for a wide range of operating modes, and has an LVDS interface for easy system integration.

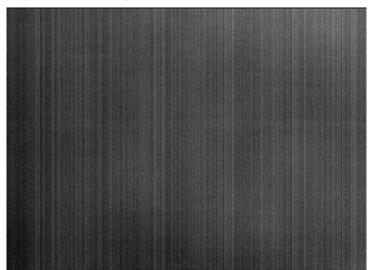

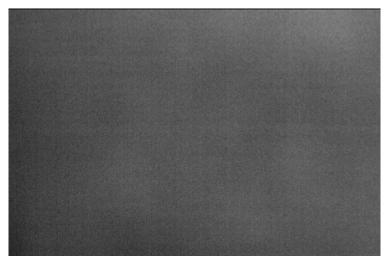

By removing the visually disturbing column patterned noise, this sensor enables building a camera without any offline correction or the need for memory. In addition, the on-chip column FPN correction is more reliable than an offline correction, because it compensates for supply and temperature variations. The sensor requires one master clock for operations up to 500 fps.

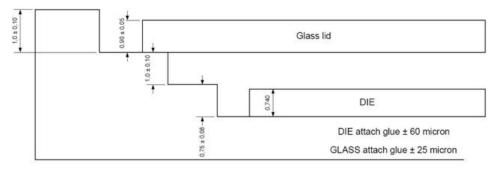

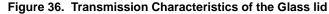

The LUPA 1300-2 is housed in a 168 pin  $\mu$ PGA package and is available in a monochrome version and Bayer (RGB) patterned color filter array. The monochrome version is available without glass. Contact your local Cypress office.

### Figure 1. LUPA 1300-2 Die Photo

| Marketing Part Number | Mono/Color                        | Package      |

|-----------------------|-----------------------------------|--------------|

| CYIL2SM1300AA-GZDC    | Mono with Glass                   |              |

| CYIL2SM1300AA-GWCES   | Mono without Glass <sup>[1]</sup> | 168 pin µPGA |

| CYIL2SC1300AA-GZDC    | Color with Glass                  |              |

| CYIL2SM1300-EVAL      | Mono Demo Kit                     | Demo Kit     |

Note

1. Contact your local sales office for the windowless option.

Cypress Semiconductor Corporation Document Number: 001-24599 Rev. \*C 198 Champion Court

San Jose, CA 95134-1709 • 408-943-2600 Revised September 18, 2009

# Overview

This data sheet describes the interface of the LUPA1300-2 image sensor. The SXGA resolution CMOS active pixel sensor features synchronous shutter and a maximal frame rate of

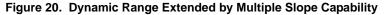

500 fps in full resolution. The readout speed is boosted by sub sampling and the windowed region of interest (ROI) readout. FPN correction cannot be used in conjunction with sub-sampling and windowed region of interest readout. High dynamic range scenes can be captured using the double and multiple slope functionality. User programmable row and column start and stop positions enables windowing. Sub sampling reduces resolution while maintaining the constant field of view and an increased frame rate.

The LUPA1300-2 sensor has 12 LVDS high speed outputs that transfer image data over longer distances. This simplifies the surrounding system. The LVDS interface can receive high speed and wide bandwidth data signals and maintain low noise and distortion. A special training mode enables the receiving system to synchronize the coming data stream when switching to master, slave, or triggered mode. The image sensor also integrates a programmable offset and gain amplifier for each channel.

A 10-bit ADC converts the analog data to a 10-bit digital word stream. The sensor uses a 3-wire Serial-Parallel Interface (SPI). It requires only one master clock for operation up to 500 fps.

The sensor is available in a monochrome version or Bayer (RGB) patterned color filter array. It is placed in a 168-pin ceramic  $\mu$ PGA package.

# **Specifications**

### Table 1. General Specifications

| Parameter                 | Specifications                                                 |

|---------------------------|----------------------------------------------------------------|

| Active Pixels             | 1280 (H) x 1024 (V)                                            |

| Pixel Size                | 14 μm x 14 μm                                                  |

| Pixel Type                | 6T pixel architecture                                          |

| Pixel Rate                | 630 Mbps per channel (12 serial LVDS outputs)                  |

| Shutter Type              | Pipelined and Triggered Global Shutter                         |

| Frame Rate                | 500 fps at 1.3 Mpixel (boosted by subsampling and windowing)   |

| Master Clock              | 315 MHz for 500 fps                                            |

| Windowing (ROI)           | Randomly programmable ROI read out up to four multiple windows |

| Read Out                  | Windowed, flipped, mirrored, and subsampled read out possible  |

| ADC Resolution            | 10-bit, on-chip                                                |

| Sensitivity               | 10.16 V/lux.s at 550 nm                                        |

| Extended Dynamic<br>Range | Multiple slope (up to 90 dB optical dynamic range)             |

### **Table 2. Electro Optical Specifications**

| Parameter                   | Value                                |

|-----------------------------|--------------------------------------|

| Conversion gain             | 34µV/e⁻                              |

| Full well charge            | 30000e <sup>-</sup>                  |

| Responsivity                | 7350 V.m <sup>2</sup> /W.s at 680 nm |

| Fill factor                 | 40%                                  |

| Parasitic light sensitivity | < 1/10000                            |

| Dark noise                  | 37e <sup>-</sup>                     |

| QE x FF                     | 35% at 680 nm                        |

| FPN                         | 2% rms of the output swing           |

| PRNU                        | <1% rms of the output signal         |

| Dark signal                 | 170 mV/s at 30°C                     |

| Power dissipation           | 1350 mW                              |

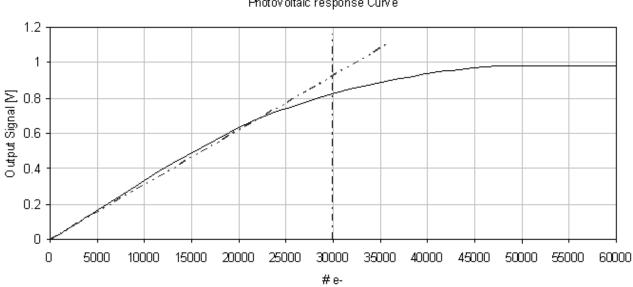

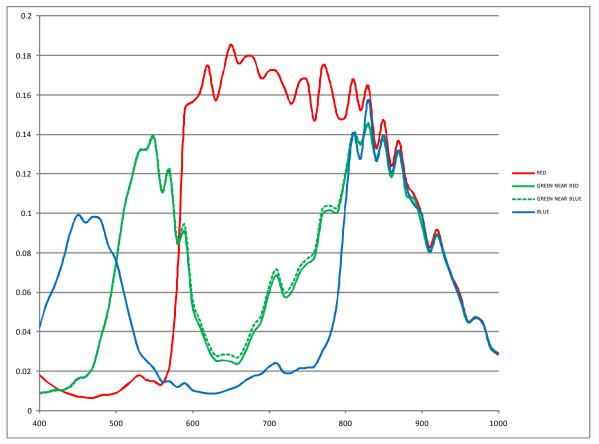

### Photovoltaic Response Curve

Photovoltaic response Curve

Figure 2. Photo Voltaic Response of LUPA 1300-2

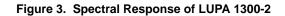

Spectral Response Curve

Document Number: 001-24599 Rev. \*C

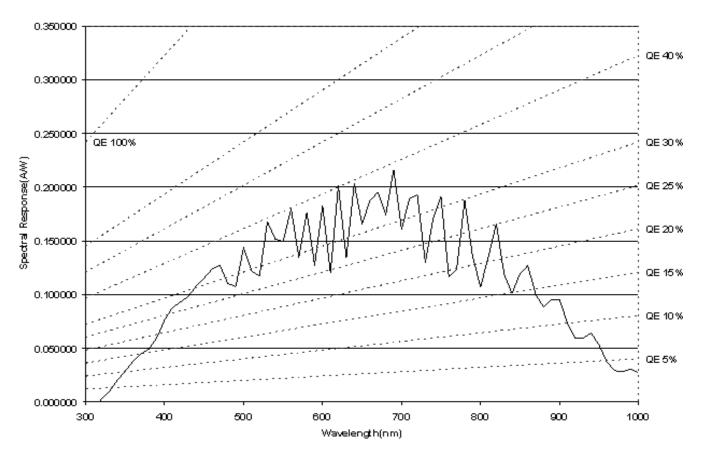

Figure 4. Spectral Response of LUPA 1300-2 Color Sensor

# **Electrical Specifications**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

### Table 3. Absolute Ratings <sup>[2]</sup>

| Symbol           | Parameter                   | Min  | Max | Unit<br>s |

|------------------|-----------------------------|------|-----|-----------|

| V <sub>DIG</sub> | Core digital supply voltage | -0.5 | 5.5 | V         |

| V <sub>IN</sub>  | Analog supply voltage       | -0.5 | 5.5 | V         |

| I <sub>IO</sub>  | DC supply current           |      |     | mA        |

| ESD: HBM         | Human Body Model            | 2000 |     | V         |

| ESD: CDM         | Charged Device Model        | 500  |     | V         |

| TJ               | Temperature range           | 0    | 70  | °C        |

# Table 4. Power Supply Ratings <sup>[3, 4, 5]</sup>

# Boldface limits apply for $T_A=T_{MIN}$ to $T_{MAX}$ , all other limits $T_A=+25^{\circ}C$ . Clock = 315 MHz

| Symbol                                            | Power Supply   | Parameter               | Condition                                          | Min | Тур | Max | Units |

|---------------------------------------------------|----------------|-------------------------|----------------------------------------------------|-----|-----|-----|-------|

| V <sub>ANA</sub> , GND <sub>ANA</sub>             | Analog Supply  | Operating voltage       |                                                    | -5% | 2.5 | +5% | V     |

|                                                   |                | Dynamic Current         | Clock enabled, lux=0                               |     | 7   | 20  | mA    |

|                                                   |                | Peak Current            | Clock enabled, lux=0                               |     | 16  |     | mA    |

|                                                   |                | Standby current         | Shutdown mode, lux=0                               |     | 1   |     | mA    |

| V <sub>DIG</sub> , GND <sub>DIG</sub>             | Digital Supply | Operating voltage       |                                                    | -5% | 2.5 | +5% | V     |

|                                                   |                | Dynamic Current         | Clock enabled, lux=0                               |     | 80  | 120 | mA    |

|                                                   |                | Peak Current            | Clock enabled, lux=0                               |     | 130 |     |       |

|                                                   |                | Standby current         | Shutdown mode, lux=0                               |     | 52  |     | mA    |

| V <sub>PIX,</sub> GND <sub>PIX</sub> Pixel Supply | Pixel Supply   | Operating voltage       |                                                    | -5% | 2.5 | +5% | V     |

|                                                   |                | Dynamic Current         | Clock enabled, lux=0                               |     | 6   | 50  | mA    |

|                                                   |                | Peak Current during FOT | Clock enabled, lux=0,<br>transient duration=9 µs   |     | 1.4 |     | Α     |

|                                                   |                | Peak Current during ROT | Clock enabled, lux=0,<br>transient duration=2.5 µs |     | 35  |     | mA    |

|                                                   |                | Standby current         | Shutdown mode, lux=0                               |     | 1   |     | mA    |

| V <sub>LVDS</sub> ,                               | LVDS Supply    | Operating voltage       |                                                    | -5% | 2.5 | +5% | V     |

| GND <sub>LVDS</sub>                               |                | Dynamic Current         | Clock enabled, lux=0                               |     | 220 | 275 | mA    |

|                                                   |                | Peak current            | Clock enabled, lux=0                               |     | 280 |     | mA    |

|                                                   |                | Standby current         | Shutdown mode, lux=0                               |     | 100 |     | mA    |

| V <sub>ADC</sub> , GND <sub>ADC</sub>             | ADC Supply     | Operating voltage       |                                                    | -5% | 2.5 | +5% | V     |

|                                                   |                | Dynamic Current         | Clock enabled, lux=0                               |     | 210 | 275 | mA    |

|                                                   |                | Peak Current            | Clock enabled, lux=0                               |     | 260 |     | mA    |

|                                                   |                | Standby current         | Shutdown mode, lux=0                               |     | 3   |     | mA    |

Notes

- 2. Absolute ratings are those values beyond which damage to the device may occur.

- All parameters are characterized for DC conditions after thermal equilibrium is established.

Peak currents were measured without the load capacitor from the LDO (Low Dropout Regulator). The 100 nF capacitor bank was connected to the pin in question.

- This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is recommended that normal precautions be taken to avoid application of any voltages higher than the maximum rated voltages to this high impedance circuit. 5.

## Table 4. Power Supply Ratings <sup>[3, 4, 5]</sup> (continued)

# Boldface limits apply for $T_A=T_{MIN}$ to $T_{MAX}$ , all other limits $T_A=+25^{\circ}C$ . Clock = 315 MHz

| Symbol                                         | Power Supply                 | Parameter                         | Condition                 | Min  | Тур | Max  | Units |

|------------------------------------------------|------------------------------|-----------------------------------|---------------------------|------|-----|------|-------|

| V <sub>BUF</sub> , GND <sub>BUF</sub>          | Buffer Supply                | Operating voltage                 |                           | -5%  | 2.5 | +5%  | V     |

|                                                |                              | Dynamic Current                   | Clock enabled, lux=0      |      | 30  | 50   | mA    |

|                                                |                              | Peak Current                      | Clock enabled, lux=0      |      | 85  |      | mA    |

|                                                |                              | Standby current                   | shutdown mode, lux=0      |      | 0.1 |      | mA    |

| V <sub>SAMPLE</sub> ,                          | Sampling                     | Operating voltage                 |                           | -5%  | 2.5 | +5%  | V     |

| GND <sub>SAMPLE</sub>                          | Circuitry Supply             | Dynamic Current                   | Clock enabled, lux=0      |      | 2   |      | mA    |

|                                                |                              | Peak Current                      | Clock enabled, lux=0      |      | 42  |      | mA    |

|                                                |                              | Standby current                   | Shutdown mode, lux=0      |      | 1   |      | mA    |

| V <sub>RES</sub>                               | Reset Supply                 | Operating voltage                 |                           | -5%  | 3.5 | +5%  | V     |

|                                                |                              | Dynamic Current                   | Clock enabled, lux=0      |      | 2   | 15   | mA    |

|                                                |                              | Peak Current                      | Clock enabled, lux=0      |      | 65  |      | mA    |

|                                                |                              | Standby current                   | Shutdown mode, lux=0      |      | 2   |      | mA    |

| V <sub>RES_AB</sub>                            | Antiblooming                 | Operating voltage                 |                           | -10% | 0.7 | +10% | V     |

| _                                              | Supply                       | Dynamic Current                   | Clock enabled, lux=0      |      | 1   |      | mA    |

|                                                |                              | Peak Current following edge reset | Clock enabled, lux=0      |      | 50  |      | mA    |

|                                                |                              | Standby current                   | Shutdown mode, lux=0      |      | 1   |      | mA    |

| V <sub>RES_DS</sub> Reset Dual<br>Slope Supply |                              | Operating voltage                 |                           | -5%  | 2.5 | +5%  | V     |

|                                                | Slope Supply                 | Dynamic Current                   | Clock enabled, lux=0      |      | 0.4 | 3    | mA    |

|                                                |                              | Peak Current                      | Clock enabled, lux=0      |      | 36  |      | mA    |

| V <sub>RES_TS</sub>                            | Reset Triple                 | Operating voltage                 |                           | -5%  | 1.8 | +5%  | V     |

|                                                | Slope Supply                 | Dynamic Current                   | Clock enabled, lux=0      |      | 0.3 | 2    | mA    |

|                                                |                              | Peak Current                      | Clock enabled, lux=0      |      | 14  |      | mA    |

| V <sub>MEM_L</sub>                             | Memory                       | Operating voltage                 |                           | -5%  | 2.5 | +5%  | V     |

|                                                | Element low<br>level supply  | Dynamic Current                   | Clock enabled, lux=0      |      | 0.2 | 1    | mA    |

|                                                | level supply                 | Peak Current during FOT           | Clock enabled, lux=0      |      | 62  |      | mA    |

|                                                |                              | Peak Current during FOT           | Clock enabled, bright     |      | 30  |      | mA    |

| V <sub>MEM_H</sub>                             | Memory                       | Operating voltage                 |                           | -5%  | 3.3 | +5%  | V     |

|                                                | Element high<br>level supply | Dynamic Current                   | Clock enabled, lux=0      |      | 1   |      | mA    |

|                                                | level supply                 | Peak Current during FOT           | Clock enabled, lux=0      |      | 45  |      | mA    |

| V <sub>PRECH</sub>                             | Pre_charge                   | Operating voltage                 |                           | -10% | 0.7 | +10% | V     |

|                                                | Driver Supply                | Dynamic Current                   | Clock enabled, lux=0      |      | 0.3 | 3    | mA    |

|                                                |                              | Peak Current during FOT           | Clock enabled, lux=0      |      | 32  |      | mA    |

|                                                |                              | Peak Current during FOT           | Clock enabled, lux=bright |      | 25  |      | mA    |

Every module in the image sensor has its own power supply and ground. The grounds can be combined externally, but not all power supply inputs may be combined. Some power supplies must be isolated to reduce electrical crosstalk and improve shielding, dynamic range, and output swing. Internal to the image sensor, the ground lines of each module are kept separate to improve shielding and electrical crosstalk between them.

The LUPA 1300-2 contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, take normal precautions to avoid voltages higher than the maximum rated voltages in this high impedance circuit. Unused inputs must always be tied to an appropriate logic level, for example,  $V_{DD}$  or GND. All cap\_xxx pins must be connected to ground through a 100 nF capacitor.

The recommended combinations of supplies are:

- Analog group of +2.5V supply:  $V_{SAMPLE}$ ,  $V_{RES_DS}$ ,  $V_{MEM_L}$ ,  $V_{ADC}$ ,  $V_{pix}$ ,  $V_{ANA}$ ,  $V_{BUF}$

- Digital Group of +2.5V supply: V<sub>DIG</sub>, V<sub>LVDS</sub>

Page 6 of 41

### Table 5. Power Dissipation <sup>[3]</sup>

These specifications apply for  $V_{DD}$  = 2.5V, Clock = 315 MHz, 500 fps

| Symbol | Parameter                 | Condition        | Тур  | Units |

|--------|---------------------------|------------------|------|-------|

| PDOWN  | Power down                | no clock running | 400  | mW    |

| Power  | Average Power Dissipation | lux = 0          | 1350 | mW    |

### Table 6. AC Electrical Characteristics <sup>[3]</sup>

The following specifications apply for VDD = 2.5V, Clock = 315 MHz, 500 fps.

| Symbol            | Parameter             | Condition           | Тур | Max | Units |

|-------------------|-----------------------|---------------------|-----|-----|-------|

| F <sub>CLK</sub>  | Input Clock Frequency | fps = 500           |     | 315 | MHz   |

| DC <sub>CLK</sub> | Clock Duty Cycle      | At maximum clock    | 50  |     | %     |

| fps               | Frame rate            | Maximum clock speed |     | 500 | fps   |

# **Sensor Architecture**

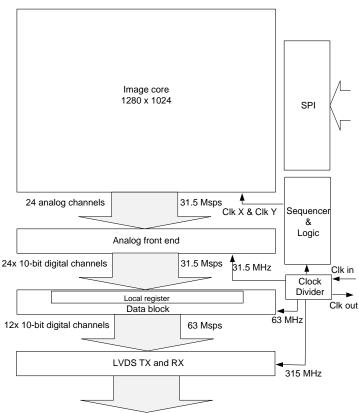

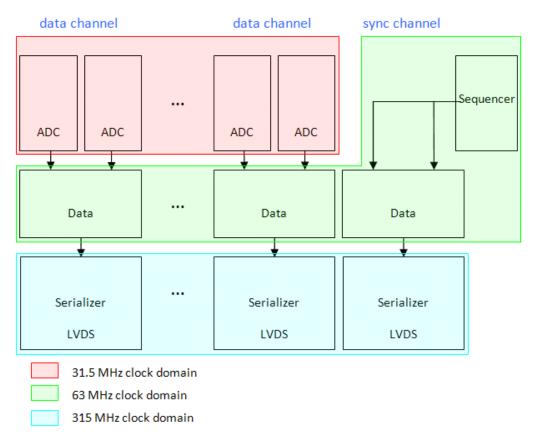

The floor plan of the architecture is shown in Figure 5. The sensor consists of a pixel array, analog front end, data block, and LVDS transmitters and receivers. Separate modules for the SPI, clock division, and sequencer are also integrated. The image sensor of 1280 x 1024 pixels is read out in progressive scan.

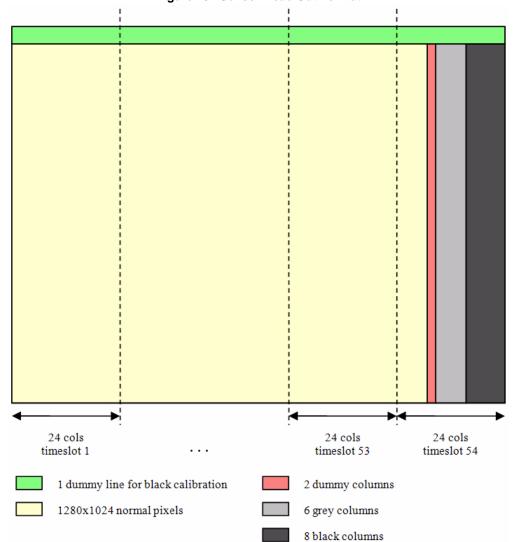

This architecture enables programmable addressing in the x-direction in steps of 24 pixels, and in the y-direction in steps of one pixel. The starting point of the address can be uploaded by the serial parallel interface (SPI).

The AFE prepares the signal for the digital data block when the data is multiplexed and prepared for the LVDS interface.

Figure 5. Floor Plan of the Sensor

12x LVDS outputs at 630 Msps

Document Number: 001-24599 Rev. \*C

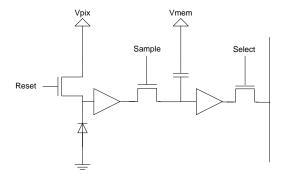

### The 6T Pixel

To obtain the global shutter feature combined with a high sensitivity and good parasitic light sensitivity (PLS), implement the pixel architecture shown in Figure 6. This pixel architecture is designed in a  $14 \,\mu\text{m} \times 14 \,\mu\text{m}$  pixel pitch. The pixel is designed to meet the specifications listed in Table 1 and Table 2 on page 2. This architecture also enables pipelined or triggered mode, as shown in Figure 6.

### Figure 6. 6T Pixel Architecture

## Frame Rate and Windowing

### Frame Rate

The frame rate depends on the input clock, the frame overhead time (FOT), and the row overhead time (ROT). The frame period is calculated by:

Frame period = FOT+Nr. Lines \* (ROT + Nr. Pixels \* clock period)

### Table 7. Frame Rate Parameters

| Parameter    | Comment                                   | Clarification                                                                  |

|--------------|-------------------------------------------|--------------------------------------------------------------------------------|

| FOT          | Frame Overhead<br>Time                    | Programmable: Default<br>315 MHz granularity clock<br>cycles (5 µs at 630 MHz) |

| ROT          | Row Overhead<br>Time                      | Programmable: Default 13<br>granularity clock cycles<br>(206 ns at 630 MHz)    |

| Nr. Lines    | Number of lines<br>read out each<br>frame |                                                                                |

| Nr. Pixels   | Number of pixels<br>read out each line    |                                                                                |

| Clock Period | 1/63 MHz = 15.9 ns                        | Every channel works at<br>63 MHz →12 channels<br>result in 756 MHz data rate   |

#### Example

Readout of the full resolution at nominal speed (756 MHz pixel rate = 1.32 ns)

Frame period = 5  $\mu$ s + (1025 \* (206 ns+1.32 ns\*1296) = 1.97 ms => 507 fps

The real speed of the LUPA1300-2 is reduced to 500 fps, because overhead pixels are read out for black level calibration and other on board features.

### Windowing

Windowing is easily achieved by SPI. The starting point of the x and y address and the window size can be uploaded. The minimum step size in the x-direction is 24 pixels (choose only multiples of 24 as start or stop addresses). The minimum step size in the y-direction is one line (every line can be addressed) in normal mode, and two lines in sub sampling mode.

The section Sequencer on page 10 discusses the use of registers to achieve the desired ROI.

| Table 8. | Typical | Frame Rates | for 630 | MHz Clock |

|----------|---------|-------------|---------|-----------|

|----------|---------|-------------|---------|-----------|

| Image<br>Resolution (X*Y) | Frame Rate<br>(fps) | Frame Read<br>Out Time (µs) |

|---------------------------|---------------------|-----------------------------|

| 1296x1025                 | 507                 | 1970                        |

| 640 x 512                 | 1842                | 550                         |

| 256 x 256                 | 6933                | 146                         |

### Analog to Digital Converter

The sensor has 24 10-bit pipelined ADCs on board. The ADCs nominally operate at 31.5 Msamples/s.

### Table 9. ADC Parameters

| Parameter    | Specification   |

|--------------|-----------------|

| Data rate    | 31.5 Msamples/s |

| Quantization | 10 bit          |

| DNL          | Typ. < 1 DN     |

| INL          | Typ. < 1 DN     |

### **Programmable Gain Amplifiers**

The PGAs amplify the signal before sending it to the ADCs. The amplification inside the PGA is controlled by one SPI setting

The amplification inside the PGA is controlled by one SPI setting: afemode [5:3].

Six gain steps can be selected by the afemode<5:3> register.

Table 10 lists the six gain settings. The unity gain selection of the PGA is done by the default afemode<5:3> setting.

#### Table 10. Gain Settings

| afemode<5:3> | Gain |

|--------------|------|

| 000          | 1    |

| 001          | 1.5  |

| 010          | 2    |

| 011          | 2.25 |

| 100          | 3    |

| 101          | 4    |

# **Operation and Signaling**

### Digital Signals

Depending on the operation mode (Master or Slave), the pixel array of the image sensor requires different digital control signals. The function of each signal is listed in this table.

| Signal Name | I/O    | Comments                                                                |

|-------------|--------|-------------------------------------------------------------------------|

| MONITOR_1   | Output | Output pin for integration timing, high during integration              |

| MONITOR_2   | Output | Output pin for dual slope integration timing, high during integration   |

| MONITOR_3   | Output | Output pin for triple slope integration timing, high during integration |

| INT_TIME_3  | Input  | Integration pin triple slope                                            |

| INT_TIME_2  | Input  | Integration pin dual slope                                              |

| INT_TIME_1  | Input  | Integration pin first slope                                             |

| RESET_N     | Input  | Sequencer reset, active LOW                                             |

| CLK         | Input  | System clock (630 MHz)                                                  |

| SPI_CS      | Input  | SPI chip select                                                         |

| SPI_CLK     | Input  | Clock of the SPI                                                        |

| SPI_IN      | Input  | Data line of the SPI, serial input                                      |

| SPI_OUT     | Output | Data line of the SPI, serial output                                     |

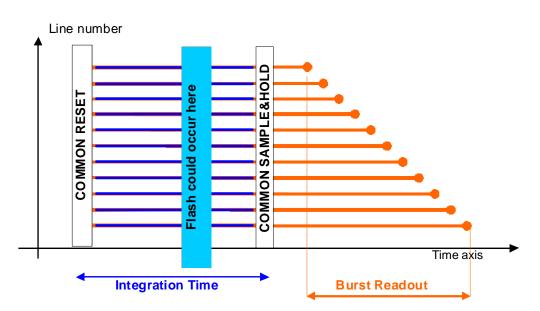

### Synchronous Shutter

In a synchronous (snapshot or global) shutter, light integration occurs on all pixels in parallel, although subsequent readout is sequential. Figure 7 shows the integration and readout sequence for the synchronous shutter. All pixels are light sensitive at the same period of time. The whole pixel core is reset simultaneously, and after the integration time, all pixel values are sampled together on the storage node inside each pixel. The pixel core is read out line by line after integration. Note that the integration and readout cycle can occur in parallel or in sequential mode (pipelined or triggered). Refer to the section Image Sensor Timing and Readout on page 18.

### Figure 7. Synchronous Shutter Operation

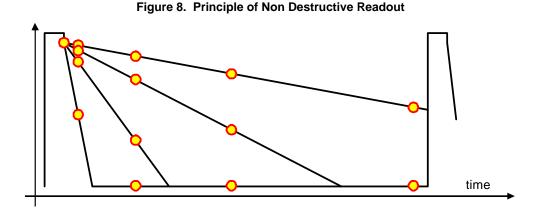

### Non Destructive Readout (NDR)

The sensor can also be read out in a nondestructive method. After a pixel is initially reset, it can be read multiple times, without being reset. You can record the initial reset level and all intermediate signals. High light levels saturate the pixels quickly, but a useful signal is obtained from the early samples. For low light levels, the later or latest samples must be used. Essentially, an active pixel array is read multiple times, and reset only once. The external system intelligence interprets the data. Table 12 on page 10 summarizes the advantages and disadvantages of nondestructive readout.

| Advantages                                                                            | Disadvantages                                                                 |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Low noise, because it is true CDS                                                     | System memory required to record the reset level and the intermediate samples |

|                                                                                       | Requires multiples readings of each pixel, so there is higher data throughput |

| High dynamic range. The results include signals for short and long integration times. | Requires system level digital calculations                                    |

Note that the amount of samples taken with one initial reset is programmable in the nr\_of\_ndr\_steps register. If nr\_of\_ndr\_steps is one, the sensor operates in the default method, that is one reset and one sample. This is called the disable nondestructive read out mode.

When nr\_of\_ndr\_steps is two, there is one reset and two samples, and so on. In the slave mode, nothing changes on the protocol of the signals int\_time\_\*. The sequencer suppresses the internal reset signal to the pixel array.

### Sequencer

The sequencer generates the complete internal timing of the pixel array and the readout. The timing can be controlled by the user through the SPI register settings. The sequencer operates on the same clock as the data block. This is a division by 10 of the input clock (internally divided).

Table 13 lists the internal registers. These registers are discussed in detail in the section Detailed Description of Internal Registers on page 15.

### Table 13. Internal Registers

| Block          | Register Name | Address [60] | Field | Reset Value | Description           |

|----------------|---------------|--------------|-------|-------------|-----------------------|

| MBS (reserved) | Fix1          | 0            | [7:0] | 0x00        | Reserved, fixed value |

|                | Fix2          | 1            | [7:0] | 0xFF        | Reserved, fixed value |

|                | Fix3          | 2            | [7:0] | 0x00        | Reserved, fixed value |

|                | Fix4          | 3            | [7:0] | 0x00        | Reserved, fixed value |

|                | Fix5          | 4            | [7:0] | '0x08'      | Reserved, fixed value |

| Block      | Register Name | Address [60] | Field | Reset Value | Description                       |

|------------|---------------|--------------|-------|-------------|-----------------------------------|

| LVDS clk   | lvdsmain      | 5            | [3:0] | '0110'      | lvds trim                         |

| divider    |               |              | [7:4] | 0           | clkadc phase                      |

|            | lvdspwd1      | 6            | [7:0] | 0x00        | Power down channel 7:0            |

|            | lvdspwd2      | 7            | [5:0] | 0           | Power down channel 13:8           |

|            |               |              | [6]   | 0           | Power down all channels           |

|            |               |              | [7]   | 0           | lvds test mode                    |

|            | Fix6          | 8            | [7:0] | 0x00        | Reserved, fixed value             |

| AFE        | afebias       | 9            | [3:0] | '1000'      | afe current biasing               |

|            | afemode       | 10           | [2:0] | '111'       | vrefp, vrefm settings             |

|            |               |              | [5:3] | '000'       | Pga settings                      |

|            |               |              | [6]   | 0           | Power down AFE                    |

|            | afepwd1       | 11           | [7:0] | 0x00        | Power down adc_channel_2x 7 to 0  |

|            | afepwd2       | 12           | [3:0] | 0x00        | Power down adc_channel_2x 11 to 8 |

| Bias block | bandgap       | 13           | [0]   | '0'         | Power down bandgap and currents   |

|            |               |              | [1]   | '1'         | External resistor                 |

|            |               |              | [2]   | '0'         | External voltage reference        |

|            |               |              | [5:3] | '000'       | Bandgap trimming                  |

| Image Core | imcmodes      | 14           | [0]   | 0           | Power down                        |

|            |               |              | [1]   | '1'         | Enable vrefcol regulator          |

|            |               |              | [2]   | '1'         | Enable precharge regulator        |

|            |               |              | [3]   | 0           | Disable internal bias for vprech  |

|            |               |              | [4]   | '1'         | Disable column load               |

|            |               |              | [5]   | '0'         | clkmain invert                    |

|            | Fix7          | 15           | [7:0] | 0x00        | Reserved, fixed value             |

|            | Fix8          | 16           | [7:0] | 0x00        | Reserved, fixed value             |

|            | imcbias1      | 17           | [3:0] | '1000'      | Bias colfpn DAC buffer            |

|            |               |              | [7:4] | '1000'      | Bias precharge regulator          |

|            | imcbias2      | 18           | [3:0] | '1000'      | Bias pixel precharge level        |

|            |               |              | [7:4] | '1000'      | Bias column ota                   |

|            | imcbias3      | 19           | [3:0] | '1000'      | Bias column unip fast             |

|            |               |              | [7:4] | '1000'      | Bias column unip slow             |

|            | Imcbias4      | 20           | [3:0] | '1000'      | Bias column load                  |

|            |               |              | [7:4] | '1000'      | Bias column precharge             |

| Block       | Register Name   | Address [60] | Field | Reset Value | Description                                                                       |

|-------------|-----------------|--------------|-------|-------------|-----------------------------------------------------------------------------------|

| Data Block  | Fix9            | 21           | [7:0] | 0x20        | Reserved, fixed value                                                             |

|             | Fix10           | 22           | [7:0] | 0xC0        | Reserved, fixed value                                                             |

|             | dataconfig1     | 23           | [1:0] | 0x00        | Reserved, fixed value                                                             |

|             |                 |              | [2]   | 0           | '1': Enables user upload of dacvrefadc register value<br>'0': Keeps default value |

|             |                 |              | [3]   | 0           | Enable PRBS generation                                                            |

|             |                 |              | [4]   | 0           | Reserved, fixed value                                                             |

|             |                 |              | [5]   | 0           | Reserved, fixed value                                                             |

|             |                 |              | [7:6] | 0x03        | Training pattern inserted to sync LVDS receivers                                  |

|             | dataconfig2     | 24           | [7:0] | 0x2A        | Training pattern inserted to sync LVDS receivers                                  |

|             | Fix11           | 25           | [7:0] | 0           | Reserved, fixed value                                                             |

|             | dacvrefadc      | 26           | [7:0] | 0x80        | Input to DAC to set the offset at the input of the ADC                            |

|             | Fix12           | 27           | [7:0] | 0x80        | Reserved, fixed value                                                             |

|             | Fix13           | 28           | [7:0] |             | Reserved, fixed value                                                             |

|             | Fix14           | 29           | [7:0] |             | Reserved, fixed value                                                             |

|             | datachannel0_1  | 30           | [0]   | 0           | Bypass the data block                                                             |

|             |                 |              | [1]   | 0           | Enables the FPN correction                                                        |

|             |                 |              | [2]   | 0           | Overwrite incoming ADC data by the data in the testpat register                   |

|             |                 |              | [3]   | 0           | Reserved, fixed value                                                             |

|             |                 |              | [5:4] | 0x00        | Pattern inserted to generate a test image                                         |

|             | datachannel0_2  | 31           | [7:0] | 0x00        | Pattern inserted to generate a test image                                         |

|             | datachannel1_1  | 32           | [0]   | 0           | Bypass the data block                                                             |

|             |                 |              | [1]   | 0           | Enables the FPN correction                                                        |

|             |                 |              | [2]   | 0           | Overwrite incoming ADC data by the data in the testpat register                   |

|             |                 |              | [3]   | 0           | Reserved, fixed value                                                             |

| Data Block  |                 |              | [5:4] | 0x00        | Pattern inserted to generate a test image                                         |

| (continued) | datachannel1_2  | 33           | [7:0] | 0x00        | Pattern inserted to generate a test image                                         |

|             | datachannel12_1 | 54           | [0]   | 0           | Bypass the data block                                                             |

|             |                 |              | [1]   | 0           | Enables the FPN correction                                                        |

|             |                 |              | [2]   | 0           | Overwrite incoming ADC data by the data in the testpat register                   |

|             |                 |              | [3]   | 0           | Reserved, fixed value                                                             |

|             |                 |              | [5:4] | 0x00        | Pattern inserted to generate a test image                                         |

|             | datachannel12_2 | 55           | [7:0] | 0x00        | Pattern inserted to generate a test image                                         |

| Block     | Register Name | Address [60] | Field | Reset Value | Description                                                                                                                                                                                                                             |

|-----------|---------------|--------------|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sequencer | seqmode1      | 56           | [0]   | 0           | Enables image capture                                                                                                                                                                                                                   |

|           |               |              | [1]   | 1           | '1': Master mode, integration timing is generated<br>on-chip<br>'0': Slave mode, integration timing is controlled<br>off-chip through INT_TIME1, INT_TIME2 and<br>INT_TIME3 pins                                                        |

|           |               |              | [2]   | 0           | '0': Pipelined mode<br>'1': Triggered mode                                                                                                                                                                                              |

|           |               |              | [3]   | 0           | Enables('1')/disables('0') subsampling                                                                                                                                                                                                  |

|           |               |              | [4]   | 0           | '1': Color subsampling scheme: 1:1:0:0:1:1:0:0<br>'0': B&W subsampling scheme: 1:0:1:0:1                                                                                                                                                |

|           |               |              | [5]   | 0           | Enable dual slope                                                                                                                                                                                                                       |

|           |               |              | [6]   | 0           | Enable triple slope                                                                                                                                                                                                                     |

|           |               |              | [7]   | 0           | Enables continued row select (that is, assert row select during pixel read out)                                                                                                                                                         |

|           | seqmode2      | 57           | [4:0] | '10000'     | Must be overwritten with 10001' to this register after startup, before readout.                                                                                                                                                         |

|           |               |              | [6:5] | ʻ00'        | Number of active windows:<br>"00": 1 window<br>"01": 2 windows<br>"10": 3 windows<br>"11": 4 windows                                                                                                                                    |

|           | seqmode3      | 58           | [0]   | '1'         | Enables the generation of the CRC10 on the data and sync channels                                                                                                                                                                       |

|           |               |              | [1]   | '0'         | Not applicable                                                                                                                                                                                                                          |

|           |               |              | [2]   | '0'         | Enable column fpn calibration                                                                                                                                                                                                           |

|           |               |              | [5:3] | "001"       | Number of frames in nondestructive read out:<br>"000": invalid<br>"001": one reset, one sample (default mode)<br>"010": one reset, two samples<br>                                                                                      |

|           |               |              | [6]   | 0           | Controls the granularity of the timer settings (only for<br>those that have 'granularity selectable' in the<br>description):<br>'0': Expressed in number of lines<br>'1': Expressed in clock cycles (multiplied by<br>2**seqmode4[3:0]) |

|           |               |              | [7]   | 0           | Allows delaying the syncing of events that happen<br>outside of ROT to the next ROT. This avoids image<br>artefacts.                                                                                                                    |

| Block | Register Name   | Address [60] | Field | Reset Value | Description                                                                                                                                                                                     |

|-------|-----------------|--------------|-------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | seqmode4        | 59           | [3:0] | 0x00        | Multiplier factor (=2**seqmode4[3:0]) for the timers when working in clock cycle mode                                                                                                           |

|       |                 |              | [5:4] | 0x0         | Selects the source signals to put on the digital test<br>pins (monitor pins):<br>"00": integration time settings<br>"01": EOS signals<br>"10": frame sync signals<br>"11": functional test mode |

|       |                 |              | [6]   | '0'         | Reverse read out in X direction                                                                                                                                                                 |

|       |                 |              | [7]   | '0'         | Reverse read out in Y direction                                                                                                                                                                 |

|       | window1_1       | 60           | [7:0] | 0x00        | Y start address for window 1                                                                                                                                                                    |

|       | window1_2       | 61           | [1:0] | 0x00        | Y start address for window 1                                                                                                                                                                    |

|       |                 |              | [7:2] | 0x00        | X start address for window 1                                                                                                                                                                    |

|       | window1_3       | 62           | [7:0] | 0xFF        | Y end address for window 1                                                                                                                                                                      |

|       | window1_4       | 63           | [1:0] | 0x3         | Y end address for window 1                                                                                                                                                                      |

|       |                 |              | [7:2] | 0x36        | X width for window 1                                                                                                                                                                            |

|       | window2_1       | 64           | [7:0] | 0x00        | Y start address for window 2                                                                                                                                                                    |

|       | window2_2       | 65           | [1:0] | 0x00        | Y start address for window 2                                                                                                                                                                    |

|       |                 |              | [7:2] | 0x00        | X start address for window 2                                                                                                                                                                    |

|       | window2_3       | 66           | [7:0] | 0xFF        | Y end address for window 2                                                                                                                                                                      |

|       | window2_4       | 67           | [1:0] | 0x3         | Y end address for window 2                                                                                                                                                                      |

|       |                 |              | [7:2] | 0x36        | X width for window 2                                                                                                                                                                            |

|       | window3_1       | 68           | [7:0] | 0x00        | Y start address for window 3                                                                                                                                                                    |

|       | window3_2       | 69           | [1:0] | 0x00        | Y start address for window 3                                                                                                                                                                    |

|       |                 |              | [7:2] | 0x00        | X start address for window 3                                                                                                                                                                    |

|       | window3_3       | 70           | [7:0] | 0xFF        | Y end address for window 3                                                                                                                                                                      |

|       | window3_4       | 71           | [1:0] | 0x3         | Y end address for window 3                                                                                                                                                                      |

|       |                 |              | [7:2] | 0x36        | X width for window 3                                                                                                                                                                            |

|       | window4_1       | 72           | [7:0] | 0x00        | Y start address for window 4                                                                                                                                                                    |

|       | window4_2       | 73           | [1:0] | 0x00        | Y start address for window 4                                                                                                                                                                    |

|       |                 |              | [7:2] | 0x00        | X start address for window 4                                                                                                                                                                    |

|       | window4_3       | 74           | [7:0] | 0xFF        | Y end address for window 4                                                                                                                                                                      |

|       | window4_4       | 75           | [1:0] | 0x3         | Y end address for window 4                                                                                                                                                                      |

|       |                 |              | [7:2] | 0x36        | X width for window 4                                                                                                                                                                            |

|       | res_length1     | 76           | [7:0] | 0x02        | Length of pix_rst (granularity selectable)                                                                                                                                                      |

|       | res_length2     | 77           | [7:0] | 0x00        | Length of pix_rst (granularity selectable)                                                                                                                                                      |

|       | res_dsts_length | 78           | [7:0] | 0x01        | Length of resetds and resetts (granularity selectable)                                                                                                                                          |

|       | tint_timer1     | 79           | [7:0] | 0xFF        | Length of integration time (granularity selectable)                                                                                                                                             |

|       | tint_timer2     | 80           | [7:0] | 0x03        | Length of integration time (granularity selectable)                                                                                                                                             |

|       | tint_ds_timer1  | 81           | [7:0] | 0x40        | Length of DS integration time (granularity selectable)                                                                                                                                          |

|       | tint_ds_timer2  | 82           | [1:0] | 0x00        | Length of DS integration time (granularity selectable)                                                                                                                                          |

|       | tint_ts_timer1  | 83           | [7:0] | 0x0C        | Length of TS integration time (granularity selectable)                                                                                                                                          |

|       | tint_ts_timer2  | 84           | [1:0] | 0x00        | Length of TS integration time (granularity selectable)                                                                                                                                          |

Document Number: 001-24599 Rev. \*C

| Block | Register Name     | Address [60] | Field | Reset Value | Description                                                 |

|-------|-------------------|--------------|-------|-------------|-------------------------------------------------------------|

|       | tint_black_timer  | 85           | [7:0] | 0x06        | Reserved, fixed value                                       |

|       | rot_timer         | 86           | [7:0] | 0x0D        | Length of ROT (granularity clock cycles)                    |

|       | fot_timer         | 87           | [7:0] | 0x36        | Length of FOT (granularity clock cycles)                    |

|       | fot_timer         | 88           | [1:0] | 0x01        | Length of FOT (granularity clock cycles)                    |

|       | prechpix_timer    | 89           | [7:0] | 0x7C        | Length of pixel precharge (granularity clock cycles)        |

|       | prechpix_timer    | 90           | [1:0] | 0x00        | Length of pixel precharge (granularity clock cycles)        |

|       | prechcol_timer    | 91           | [7:0] | 0x03        | Length of column precharge (granularity clock cycles)       |

|       | rowselect_timer   | 92           | [7:0] | 0x09        | Length of rowselect (granularity clock cycles)              |

|       | sample_timer      | 93           | [7:0] | 0xF8        | Length of pixel_sample (granularity clock cycles)           |

|       | sample_timer      | 94           | [1:0] | 0x00        | Length of pixel_sample (granularity clock cycles)           |

|       | vmem_timer        | 95           | [7:0] | 0x10        | Length of pixel_vmem (granularity clock cycles)             |

|       | vmem_timer        | 96           | [1:0] | 0x01        | Length of pixel_vmem (granularity clock cycles)             |

|       | delayed_rdt_timer | 97           | [7:0] | 0           | Readout delay for testing purposes (granularity selectable) |

|       | delayed_rdt_timer | 98           | [7:0] | 0           | Readout delay for testing purposes (granularity selectable  |

|       | Fix29             | 99           | [0]   | 0           | Reserved, fixed value                                       |

|       | Fix30             | 100          | [0]   | 0           | Reserved, fixed value                                       |

|       | Fix31             | 101          | [0]   | 0           | Reserved, fixed value                                       |

|       | Fix32             | 102          | [0]   | 0           | Reserved, fixed value                                       |

|       | Fix33             | 103          | [0]   | 0           | Reserved, fixed value                                       |

|       | Fix34             | 104          | [0]   | 0           | Reserved, fixed value, write 0x4 to it                      |

### Detailed Description of Internal Registers

The registers must be changed only during idle mode, that is, when seqmode1[0] is '0'. Uploaded registers have an immediate effect on how the frame is read out. Parameters uploaded during readout may have an undesired effect on the data coming out of the images.

#### MBS Block

The register block contains registers for sensor testing and debugging. All registers in this block must remain unchanged after startup.

### LVDS Clock Divider Block

This block controls division of the input clock for the LVDS transmitters or receivers. This block also enables shutting down one or all LVDS channels. For normal operation, this register block must remain untouched after startup.

### AFE Block

This register block contains registers to shut down ADC channels or the complete AFE block. This block also contains the register for setting the PGA gain: AFE\_mode[5:3]. Refer to Electrical Specifications on page 5 for more details on the PGA settings.

### **Biasing Block**

This block contains several registers for setting biasing currents for the sensor. Default values after startup must remain unchanged for normal operation of the sensor.

#### Image Core Block

The registers in this block have an impact on the pixel array itself. Default settings after startup must remain unchanged for normal operation of the image sensor.

#### **Data Block**

The data block is positioned in between the analog front end (output stage + ADCs) and the LVDS interface. It muxes the outputs of 2 ADCs to one LVDS block and performs some minor data handling:

- CRC calculation and insertion

- Training and test pattern generation

- The most important registers in this block are:

**Dataconfig.** The dataconfig1[7:6] and dataconfig2[7:0] registers insert a training pattern in the LVDS channels to sync the LVDS receivers.

**Datachannels.** DatachannelX\_1 and DatachannelX\_2 (with X=0 to 12) are registers that allow you to enable or disable the FPN correction (DatachannelX\_1[1]), and generate a test pattern if necessary (datachannelX\_1[5:4] and datachannelX\_2[7:0]).

#### Sequencer Block

The sequencer block group registers allow enabling or disabling image sensor features that are driven by the onboard sequencer. This block consists of the following registers:

**Seqmode1.** The seqmode1 registers have the following subregisters:

Seqmode1[0]: Enables image capture, must be '1' during image acquisition.

Seqmode1[1]: This subregister has two modes:

'1': In this default mode the integration timing is generated on-chip.

'0': In this slave mode, the integration timing must be generated through the int\_time1, int\_time2, and int\_time3 pins.

Seqmode1[2]: This bit enables pipelined (0) or triggered (1) mode.

Seqmode1[3]: Enable (1) or disable (0) subsampling.

Seqmode1[4]: This bit sets the type of subsampling scheme used when subsampling is enabled.

'1': Color (1:1:0:0:1:1:0:0:1...)

'0': Black and White (1:0:1:0:1)

Seqmode1[5]: This bit enables or disables the dual slope integration.

Seqmode1[6]: This bit enables or disables the triple slope integration.

Seqmode2. The seqmode2 register consists of only two subregisters:

Seqmode2[4:0]: Default value after startup is '10000', but this must be overwritten with the new value '10001' immediately after startup.

Seqmode3[6:5]: These two bits set the number of active windows:

'00': 1 window

'01': 2 windows

'10': 3 windows

'11': 4 windows (max)

**Seqmode3.** The seqmode3 register consists of the following subregisters:

Seqmode3[0]: This bit enables or disables the CRC10 generation on the data and sync channels

Seqmode3[1]: Enables or disables black level calibration

Seqmode3[2]: Enables or disables column FPN correction

Seqmode3[5:3]: Enables or disables, and sets the number of frames grabbed in nondestructive readout mode.

'000': Invalid

'001': Default, 1 reset, 1 sample

'010': 1reset, 2 samples

'011': 1 reset, 3 samples

Seqmode3[6]: Controls the granularity of the timer settings (only for those that have 'granularity selectable' in the description). As a result, all timer settings are set either in number of applied clock cycles, or in the number of 'readout lines'.

'0': expressed in number of lines

'1': expressed in clock cycles (multiplied by 2\*\*seqmode4 [3:0])

Seqmode3[7]: Allows syncing of events that happen outside of ROT to be delayed to the next ROT to avoid image artifacts.

Seqmode4. This register consists of four subregisters:

Seqmode4[3:0]: Multiplier factor (2\*\*seqmode4[3:0]) for the timers when working in clock cycle mode.

Seqmode4[5:4]: Selects the source signals to be put on the digital test pins (monitor1, monitor2, and monitor3 pins)

"00": integration time settings

"01": EOS signals

"10": frame sync signals

"11": functional test mode

Seqmode4[6]: Enables (1) and disables (0) reverse X read out.

Seqmode4[7]: Enables (1) and disables (0) reverse Y read out.

Y1\_start (60 and 61, 10 bit). These registers set the Y start address for window 1 (default window).

X1\_start (61, 6bit). This register sets the X start address for window 1 (default window).

Y1\_end (62 and 63, 10 bit). These registers set the Y end address for window 1 (default window).

X1\_kernels (63, 6 bit). This register sets the number of kernels or X width to be read out for window 1 (default window).

**Y2\_start (64 and 65, 10 bit).** These registers set the Y start address for window 2 (if enabled).

**X2\_start (65, 6bit).** This register sets the X start address for window 2 (if enabled).

**Y2\_end (66 and 67, 10 bit).** These registers set the Y end address for window 2 (if enabled).

**X2\_kernels (67, 6 bit).** This register sets the number of kernels or X width to be read out for window 2 (if enabled).

**Y3\_start (68 and 69, 10 bit).** These registers set the Y start address for window 3 (if enabled).

**X3\_start (69, 6bit).** This register sets the X start address for window 3 (if enabled).

**Y3\_end (70 and 71, 10 bit).** These registers set the Y end address for window 3 (if enabled).

**X3\_kernels (71, 6 bit).** This register sets the number of kernels or X width to be read out for window 3 (if enabled).

Y4\_start (72 and 73, 10 bit). These registers set the Y start address for window 4 (if enabled).

**X4\_start (73, 6bit).** This register sets the X start address for window 4 (if enabled).

**Y4\_end (74 and 75, 10 bit).** These registers set the Y end address for window 4 (if enabled).

**X4\_kernels (75, 6 bit).** This register sets the number of kernels or X width to be read out for window 4 (if enabled).

**Res\_length (76 and 77).** This register sets the length of the internal pixel array reset (how long are all pixel reset simultaneously). This value is expressed in 'number of lines' or in clock cycles (depends on seqmode3[6]).

**Res\_dsts\_length.** This register sets the length of the internal dual and triple slope reset pulses when enabled. This value is expressed in 'number of lines' or in clock cycles (depends on seqmode3[6]).

**Tint\_timer (79 and 80).** This register sets the length of the integration time. This value is expressed in 'number of lines' or in clock cycles (depends on seqmode3[6]).

**Tint\_ds\_timer (81 and 82).** This register sets the length of the dual slope integration time. This value is expressed in 'number of lines' or in clock cycles (depends on seqmode3[6]).

**Tint\_ts\_timer (83 and 84).** This register sets the length of the triple slope integration time. This value is expressed in 'number of lines' or in clock cycles (depends on seqmode3[6]).

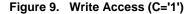

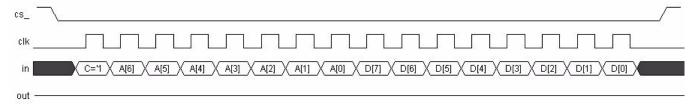

### Data Interface (SPI)

The serial 4-wire interface (or Serial to Parallel Interface) uses a serial input or output to shift the data in or out the register buffer. The chip's configuration registers are accessed from the outside world through the SPI protocol. A 4-wire bus runs over the chip and connects the SPI I/Os with the internal register blocks.

The interface consists of:

- cs\_n: chip select, when LOW the chip is selected

- clk: the spi clock

- in: Master out, Slave in, the serial input of the register

- out: Master in, Slave out, the serial output of the register

### **SPI Protocol**

- The information on the data 'in' line is:

- A command bit C, indicating a write ('1') or a read ('0') access

- 7-bit address

- 8-bit data word (in case of a write access)

The data 'out' line is generally in High Z mode, except when a read request is performed.

Data is always written on the bus on the falling edge of the clock, and sampled on the rising edge, as seen in Figure 9 and Figure 10. This is valid for both the 'in' and 'out' bus. The system clock must be active to keep the SPI uploads stored on the chip. The SPI clock speed must be slower by a factor of 30 when compared to the system clock (315 MHz nominal speed).

The 'out' line is held to High Z. The data for the address A is transferred from the shift register to the active register bank (that is, sampled) on a rising edge of cs\_n. Only the register block with address A can write its data on the 'out' bus. The data on 'in' is ignored.

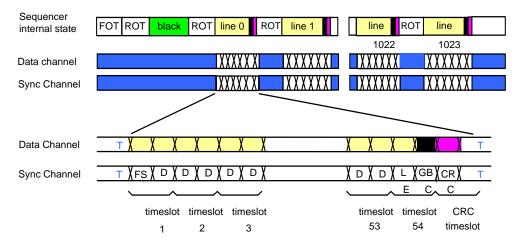

# **Image Sensor Timing and Readout**

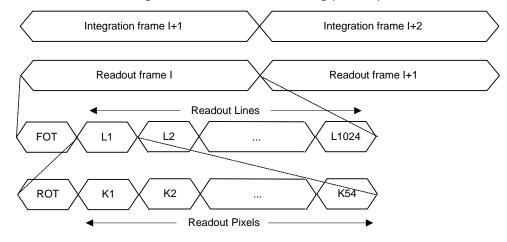

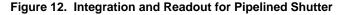

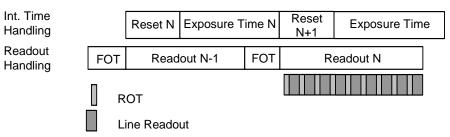

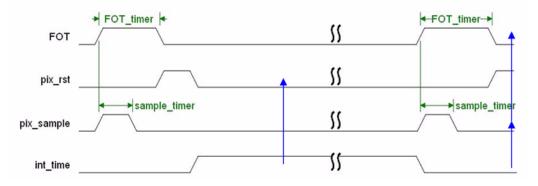

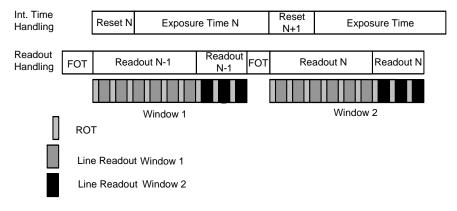

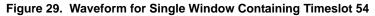

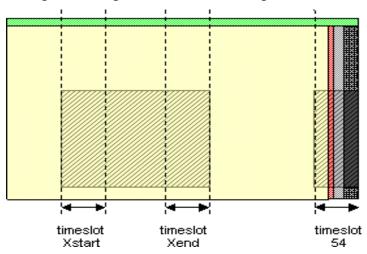

The timing of the sensor consists of two parts. The first part is related to the exposure time and the control of the pixel. The second part is related to the read out of the image sensor. Integration and readout are in parallel or triggered. In the first case, the integration time of frame I is ongoing during the readout of frame I-1. Figure 11 shows this parallel timing structure.

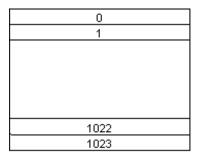

The readout of every frame starts with a FOT, during which the analog value on the pixel diode is transferred to the pixel memory element. After this FOT, the sensor is read out line by line. The read out of every line starts with a ROT, during which the pixel value is put on the column lines. Then the pixels are selected in groups of 24 (12 on rising edge, and 12 on the falling edge of the internal clock). So in total, 54 kernels of 24 pixels are read out every line. The internal timing is generated by the sequencer. The sequencer can operate in two modes: master mode and slave mode. In master mode, all internal timing is controlled by the sequencer, based on the SPI settings. In slave mode, the integration timing is directly controlled by over three pins, and the readout timing is still controlled by the sequencer. The seqmode1[1] register of the SPI selects between the master and slave modes.

### Figure 11. Global Readout Timing (Parallel)

### **Pipelined Shutter**

Integration and readout occur in parallel and are continuous. You only need to start and stop the batch of image captures.

Integration of frame N is always ongoing during readout of frame N-1. The readout of every frame starts with a FOT, during which the analog value on the pixel diode is transferred to the pixel memory element. After this FOT, the sensor is read out line by line. The readout of every line starts with a ROT, during which the pixel value is put on the column lines. Then the pixels are muxed in the correct ADCs, processed, and then sent to the LVDS output block.

You have two options in the pipelined shutter mode. The first option is to program the reset and integration through the configuration interface and let the sequencer handle integration time automatically. This mode is called master mode. The second option is to drive the integration time through an external pin. This mode is called slave mode.

### Programming the Exposure Time

In master mode, the exposure time is configured in two distinct methods (controlled by register seqmode3[6]):

- #lines: Obvious, changing signals that control integration time. They are always changed during ROT to avoid any image artefacts.

- #clock cycles: Must be multiplied by (2\*\*seqmode4[3:0]). When the counter expires, changes are put into effect immediately. Asserting the configuration signal (seqmode3[7]) forces delaying signal updates until the next ROT.

Table 14 lists the user programmable timer settings and how they are interpreted by the hardware.

### Table 14. User Programmable Timer Settings

| Setting               | Granularity  |

|-----------------------|--------------|

| reg_res_length        | Lines/cycles |

| reg_tint_timer        | Lines/cycles |

| reg_tint_ds_timer     | Lines/cycles |

| reg_tint_ts_timer     | Lines/cycles |

| reg_rot_timer         | clock cycles |

| reg_fot_timer         | clock cycles |

| reg_sel_pre_timer     | clock cycles |

| reg_precharge_timer   | clock cycles |

| reg_sample_timer      | clock cycles |

| reg_vmem_timer        | clock cycles |

| reg_delayed_rdt_timer | Lines/cycles |

Note that the seqmode3[7] can also be used to sync the user signals in slave mode. The behavior is exactly the same.

### Master Mode

In master mode the reset and exposure time is written in registers.

Ensure that the added value of the registers res\_length and tint\_timer always exceeds the number of lines that are read out. This is because the sequencer samples a new image after integration is complete, without checking if image readout is finished. Enlarging res\_length to accommodate for this has no impact on image capture.

### Slave Mode

In slave mode, the register values of res\_length and tint\_timer are ignored. The integration time is controlled by the int\_time pin. The relationship between the input pin and the integration time is shown in Figure 14. When the input pin int\_time is asserted, the pixel array goes out of reset and exposure can begin. When int\_time goes low again and the desired exposure time is reached, the image is sampled and read out can begin.

### Figure 14. Integration and Image Readout in Slave Mode

Changing a pixel's reset level during line readout might result in image artefacts during a small transient period. As a result, it is advised to only change the value of int\_time during ROT.

### **Triggered Shutter**

The two main differences in the pipelined shutter mode are:

- One single image is read upon every user action.

- Integration (and read out) is under control of the user through pin int\_time.

This means that for every frame, you need to manually intervene. The pixel array is kept in reset state until you assert the int\_time input. Similar to the pipelined shutter mode, there is a master mode in which the sequencer can control the integration time, or a slave mode in which you can define the integration time.

The possible applications for this triggered shutter mode are:

- Synchronize external flash with exposure

- Apply extremely long integration times (only in slave mode)

### Master Mode

In this mode, a rising edge on int\_time1 pin is used to trigger the start of integration and read out. The tint\_timer defines the integration time independent of the assertion of the input pin int\_time1. After the integration time counter runs out, the FOT automatically starts and the image readout is done. During readout, the image array is kept in reset. A request for a new frame is started again when a new rising edge on int\_time is detected. The time of the falling edge is not important in this mode.

# Slave Mode

Integration time control is identical to the pipelined shutter slave mode. The int\_time1 pin controls the start of integration. When int\_time is deasserted, the FOT starts (analog value on the pixel diode is transferred to the pixel memory element). Only at that time, image read out can start (similar to the pipelined read out). During read out, the image array is kept in reset. A request for a new frame is started when int\_time goes high again.

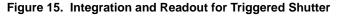

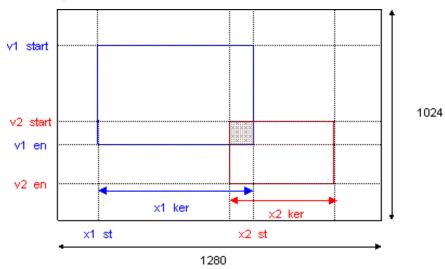

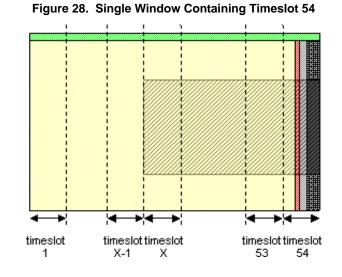

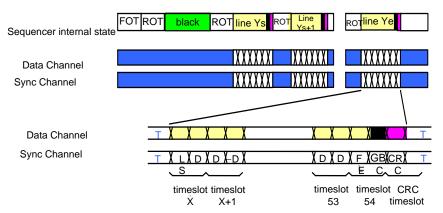

### Windowing

A fully configurable window can be selected for readout.

### Figure 16. Window Selected for Readout

The parameters to configure this window are:

**x\_start.** The sensor reads out 24 pixels in one single clock cycle. The granularity of configuring the X start position is also 24. Every value written to the windowX\_2 register must be multiplied by 24 to find the corresponding column in the pixel array.

**x\_kernels.** The number of columns that is read out (x\_kernels\*24 in full frame mode) in subsampling mode x\_kernels\*48 represents the number of columns over which subsampling is done. The x\_kernels value must be written to the windowX\_4 register.

**y\_start.** The starting line of the readout window, granularity of 1. Note that in subsample mode, the correct y\_start position must be uploaded (exact value depends on color or B/W subsampling mode). This value must be written to the windowX\_1 and windowx\_2 register.

**y\_end.** The end line of the readout window, granularity of 1. In all cases (even in reverse scan), y\_end are larger than y\_start. Note that in subsample mode, the correct y\_end position must be uploaded (exact value depends on color or B/W subsampling mode). This value must be written to the windowX\_3 and windowX\_4 register.

In case of windowing, the effective readout time is smaller than in full frame mode, because only the relevant part of the image array is accessed. As a result, it is possible to achieve higher frame rates.

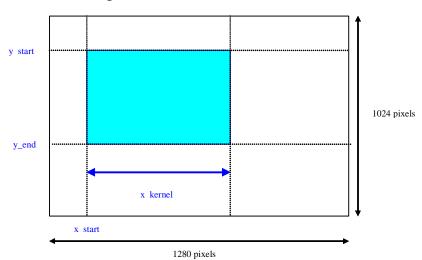

### **Reverse Scan**

Reverse scanning is supported in the X and Y direction. Line 0 (first line on the output) is the top line in normal mode and the bottom line in reverse scanning, as shown in Figure 17. As a result, the line numbers always increment. When reverse scanning in X, the operation is analogous. To enable reverse readout in X and Y, set the seqmode4[6:7] bits. In addition, the Y\_start and X\_start addresses must be changed to the new starting address.

### Figure 17. Normal and Reverse Scanning in Y

Normal scanning

Reverse scanning

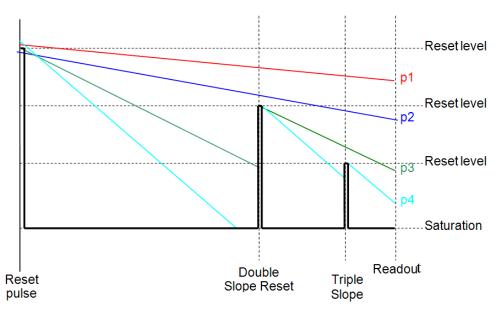

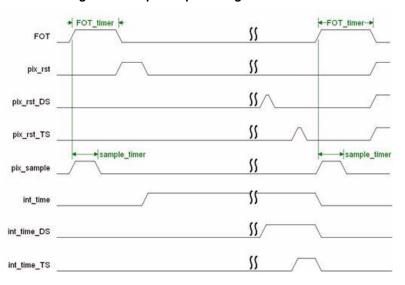

### **Multiple Windows**