# SCC1300-D04 COMBINED GYROSCOPE AND 3-AXIS ACCELEROMETER WITH DIGITAL SPI INTERFACES

#### **Features**

- ±300 °/s angular rate measurement range

- ±6 q 3-axis acceleration measurement range

- Angular rate measurement around X axis

- Angular rate sensor exceptionally insensitive to mechanical vibrations and shocks

- Superior bias stability for MEMS gyroscopes

- · Digital SPI interfacing

- Enhanced self diagnostics features

- Small size 8.5 x 18.7 x 4.5 mm (w x l x h)

- RoHS compliant robust packaging suitable for lead free soldering process and SMD mounting

- Proven capacitive 3D-MEMS technology

- Temperature range -40 °C...+125 °C

# **Applications**

SCC1300-D04 is targeted to applications with high stability and tough environmental requirements. Typical applications are:

- Inertial Measurement Units (IMUs) for highly demanding environments

- Platform stabilization and control

- Motion analysis and control

- · Roll over detection

- · Robotic control systems

- · Guidance systems

- Navigation systems

# **General Description**

SCC1300-D04 is a combined high performance gyroscope and accelerometer component. The sensor is based on VTI's proven capacitive 3D-MEMS technology. The component integrates angular rate and acceleration sensing together with flexible separate digital SPI interfaces. Small robust packaging guarantees reliable operation over product lifetime. The housing is suitable for SMD mounting and the component is compatible with RoHS and ELV directives.

SCC1300-D04 is designed, manufactured and tested against high stability, reliability and quality requirements. The angular rate and acceleration sensors provide highly stable output over wide ranges of temperature and mechanical noise. The angular rate sensor bias stability is in the elite of MEMS gyros and it is also exceptionally insensitive to all mechanical vibrations and shocks. Component has several advanced self diagnostics features.

# **TABLE OF CONTENTS**

| 1 G        | eneral Description                                  | 4  |

|------------|-----------------------------------------------------|----|

| 1.1        | Introduction                                        | 4  |

| 1.2        | General Product Description                         | 4  |

| 1.2        | 2.1 Factory Calibration                             |    |

| 1.3        | Abbreviations                                       | 5  |

| 2 Sp       | pecifications                                       | 6  |

| 2.1        | Performance Specifications for Gyroscope            | 6  |

| 2.2        | Performance Specifications for Accelerometer        | 7  |

| 2.3        | Absolute Maximum Ratings                            | 8  |

| 2.4        | Digital I/O Specification                           | 8  |

| 2.5        | SPI AC Characteristics                              | 9  |

| 3 Re       | eset and Power Up                                   | 10 |

|            |                                                     |    |

| 3.1        | Power-up Sequence for Gyroscope                     | 10 |

| 3.2        | Start-up and Operation Sequence for Accelerometer   |    |

|            | 2.1 Recommended Start-up Sequence                   |    |

|            | •                                                   |    |

| 4 Cc       | omponent Interfacing                                | 12 |

| 4.1        | SPI Interfaces                                      | 12 |

| 4.2        | Gyroscope Interface                                 | 12 |

|            | 2.1 SPI Transfer                                    |    |

|            | 2.2 SPI Transfer Parity Mode                        |    |

| 4.3<br>4.3 | Gyroscope ASIC Addressing Space                     |    |

|            | 3.2 Data Register Block                             |    |

| 4.4        | Accelerometer Interface                             | 16 |

| 4.4        |                                                     |    |

|            | 4.2 MOSI data of SPI commands4.3 Error Conditioning |    |

| 4.5        | Accelerometer ASIC Addressing Space                 |    |

| 4.5<br>4.5 | <b>9</b> 1                                          |    |

| 4.5        | 5.2 Control Register (CTRL)                         | 21 |

| 4.5        | 5.3 Temperature Output Registers                    | 21 |

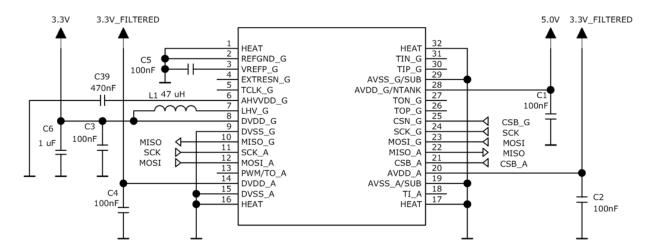

| 5 Application Information                                        | 22 |

|------------------------------------------------------------------|----|

| 5.1 Pin Description                                              | 22 |

| 5.2 Application Circuitry and External Component Characteristics |    |

| 5.3 Boost Regulator and Power Supply Decoupling in Layout        | 26 |

| 5.3.2 Thermal Connection                                         |    |

| 5.5 Package Characteristics                                      |    |

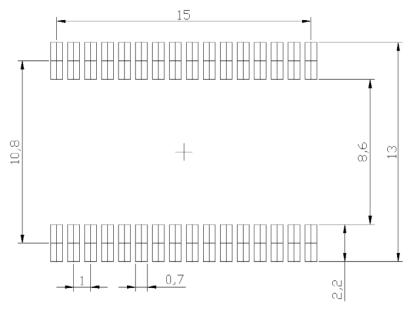

| 5.5.2 PCB Footprint                                              | 29 |

| 5.6 Assembly instructions                                        |    |

| 6 Contact Information                                            | 30 |

$Downloaded \ from \ \underline{Elcodis.com} \ \ electronic \ components \ distributor$

# 1 General Description

### 1.1 Introduction

This document contains essential technical information for SCC1300 sensor. Specifications, SPI interface descriptions, user accessible register details, electrical properties and application information etc. This document should be used as a reference when designing in SCC1300 component.

# 1.2 General Product Description

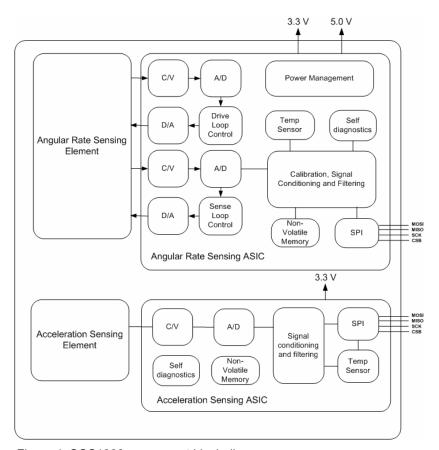

The SCC1300 sensor consists of independent acceleration and angular rate sensing elements, and separate independent Application Specific Integrated Circuits (ASICs) used to sense and control those elements. Figure 1 represents an upper level block diagram of the component. Both ASICs have their own independent digital SPI interfaces used to control and read the accelerometer and the gyroscope.

Figure 1. SCC1300 component block diagram.

The angular rate and acceleration sensing elements are manufactured using VTI proprietary High Aspect Ratio (HAR) 3D-MEMS process, which enables making robust, extremely stable and low noise capacitive sensors.

The acceleration sensing element consists of four acceleration sensitive masses. Acceleration causes capacitance change that is converted into a voltage change in the signal conditioning ASIC.

The angular rate sensing element consists of moving masses that are purposely exited to in-plane drive motion. Rotation in sensitive direction causes out-of-plane movement that can be measured as capacitance change with the signal conditioning ASIC.

# 1.2.1 Factory Calibration

SCC1300 sensors are factory calibrated. No separate calibration is required in the application. Trimmed parameters during production include sensitivities, offsets and frequency responses. Calibration parameters are stored during manufacturing inside non-volatile memory. The parameters are read automatically from the internal non-volatile memory during the start-up.

It should be noted that assembly can cause minor offset/bias errors to the sensor output. If best possible offset/bias accuracy is required, system level offset/bias calibration (zeroing) after assembly is recommended.

### 1.3 Abbreviations

| ASIC | Application Specific Integrated Circuit                                   |

|------|---------------------------------------------------------------------------|

| SPI  | Serial Peripheral Interface                                               |

| RT   | Room Temperature                                                          |

| STC  | Self Test Continuous (continuous self testing of accelerometer element)   |

| STS  | Self Test Static (gravitational based self test of accelerometer element) |

#### 2 **Specifications**

#### 2.1 **Performance Specifications for Gyroscope**

Table 1. Gyroscope performance specifications (Avdd = 5 V, Dvdd = 3.3 V and ambient temperature unless otherwise specified).

| Parameter                        | Condition                        | Min <sup>A)</sup> | Тур  | Max A) | Units     |

|----------------------------------|----------------------------------|-------------------|------|--------|-----------|

| Analog supply voltage            |                                  | 4.75              | 5    | 5.25   | V         |

| Analog supply current            | Temperature range -40 +125 °C    | 24                | 26   | 29.5   | mA        |

| Digital supply voltage           |                                  | 3.0               | 3.3  | 3.6    | V         |

| Digital supply current           | Temperature range -40 +125 °C    | 16                | 20   | 24     | mA        |

| Operating range                  | Measurement axis X               | -300              |      | 300    | °/s       |

| Offset error B)                  |                                  |                   | TBD  |        | °/s       |

| Offset over temperature          | Temperature range -40 +125 °C    | -0.9              |      | 0.9    | °/s       |

|                                  | Temperature range -10 +60 °C     | -0.5              |      | 0.5    | °/s       |

| Offset drift velocity            | Temperature gradient ≤ 2.5 K/min | -0.6              |      | 0.6    | (°/s)/min |

| Offset short term instability C) |                                  |                   | TBD  |        | °/h       |

| Angular random walk (ARW) C)     |                                  |                   | 1.12 |        | °/√h      |

| Sensitivity                      |                                  |                   | 18   |        | LSB/(°/s) |

| Sensitivity over temperature     | Temperature range -40 +125 °C    | -1                |      | 1      | %         |

| Total sensitivity error B)       |                                  | -2                |      | 2      | %         |

| Nonlinearity                     | Temperature range -40 +125 °C    | -1                |      | 1      | °/s       |

| Noise (RMS)                      |                                  |                   | 0.14 | 0.23   | °/s       |

| Noise Density                    |                                  |                   | 0.02 |        | (°/s)/√Hz |

| Cross-axis sensitivity           |                                  |                   |      | 1.7    | %         |

| G-sensitivity                    |                                  | -0.1              |      | 0.1    | (°/s)/g   |

| Shock sensitivity                | 50g, 6ms                         |                   |      | 2.0    | °/s       |

| Shock recovery time              |                                  |                   |      | 50.0   | ms        |

| Amplitude response               | -3dB frequency                   |                   | 50   |        | Hz        |

| Quantization                     |                                  |                   |      | 0.05   | °/s       |

| Power on setup time              |                                  |                   |      | 8.0    | S         |

| Output data rate                 |                                  |                   | 2    |        | kHz       |

| Output load                      |                                  |                   |      | 200    | pF        |

| SPI clock rate                   |                                  | 0.1               |      | 8      | MHz       |

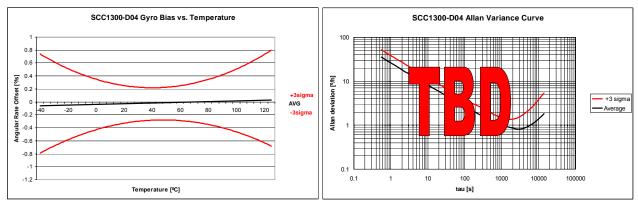

MIN/MAX values are ±3 sigma variation limits from validation test population.

Based on noise measurements and calculations (Allan variance measurements TBD Figure 2b).

Figure 2 a) SCC1300-D04 Gyroscope offset over full temperature range, b) Allan variance curve

B) Including calibration error and drift over lifetime.

# **Performance Specifications for Accelerometer**

Table 2. Acclerometer performance specifications (Vdd=3.3 V and ambient temperature unless otherwise specified).

| Parameter                         | Condition                             | Min <sup>A)</sup> | Тур  | Max A) | Units  |

|-----------------------------------|---------------------------------------|-------------------|------|--------|--------|

| Analog and digital supply voltage |                                       | 3.0               | 3.3  | 3.6    | V      |

| Current consumption               | Active mode                           |                   | 3    | 5      | mA     |

|                                   | Power down mode                       |                   | 0.12 |        | mA     |

| Measurement range                 | Measurement axes X, Y & Z             | -6                |      | 6      | g      |

| Offset error B)                   | @25 °C ±5°C                           | -70               |      | 70     | mg     |

| Offset temperature drift C)       | Temperature range -40 +125 °C         | -40               |      | 40     | mg     |

| Sensitivity                       | 13 bit output                         |                   | 650  |        | LSB/g  |

| Total sensitivity error           | Temperature range -40 +125 °C         | -4                |      | 4      | % FS   |

| Sensitivity calibration error     | @25 °C ±5°C                           | -1                |      | 1      | % FS   |

| Sensitivity temperature drift     | Temperature range -40 +125 °C         | -1                |      | 1      | % FS   |

| Linearity error                   | +1g1g range                           | -40               |      | 40     | mg     |

| Cross-Axis sensitivity            |                                       | -2.5              |      | 2.5    | %      |

| Zero acceleration output          | 2-complement                          |                   | 0    |        | LSB    |

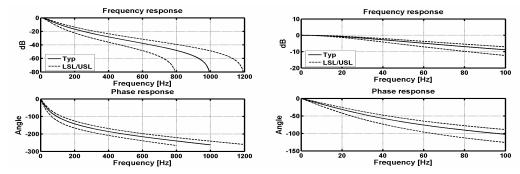

| Amplitude response D)             | -3dB frequency                        | 30                |      | 55     | Hz     |

| Noise                             |                                       |                   | 5    | 7      | mg RMS |

| Power on setup time               |                                       |                   |      | 0.1    | s      |

| Output data rate                  |                                       |                   | 2000 |        | Hz     |

| Output load                       |                                       |                   |      | 50     | pF     |

| SPI clock rate                    |                                       |                   |      | 8      | MHz    |

| ID register value                 | Customer readable ID register (27hex) |                   | TBD  |        |        |

MIN/MAX values are ±3 sigma variation limits from validation test population. B)

Includes offset deviation from 0g value, including calibration error and drift over lifetime.

Biggest change of output from RT value due temperature.

D) See Figure 3.

C)

Figure 3. SCC1300-D04 Accelerometer frequency response curves

# 2.3 Absolute Maximum Ratings

Table 3. Absolute maximum ratings of the SCC1300 sensor.

| Parameter                                    | Condition  | Min  | Тур  | Max             | Units |

|----------------------------------------------|------------|------|------|-----------------|-------|

| Gyroscope supply voltages                    |            |      |      |                 |       |

| Analog supply voltage, AVDD_G                |            | -0.5 |      | 7               | V     |

| Digital supply voltage, DVDD_G               |            | -0.3 |      | 3.6             | V     |

| Maximum voltage at analog input/output pins  |            | -0.3 |      | $AVDD_G + 0.3V$ |       |

| Maximum voltage at digital input/output pins |            | -0.3 |      | DVDD_G + 0.3    | V     |

| Accelerometer supply voltages                |            |      |      |                 |       |

| Digital supply voltage, DVDD_A               |            | -0.3 |      | 3.6             | V     |

| Analog supply voltage, AVDD_A                |            | -0.5 |      | 7.0             | V     |

| Maximum voltage at input / output pins       |            | -0.3 |      | DVDD_A + $0.3V$ | V     |

| General Component Ratings                    |            |      |      |                 |       |

| Operating temperature                        |            | -40  |      | 125             | °C    |

| Storage temperature                          |            | -40  |      | 125             | °C    |

|                                              | Max 96h    | -40  |      | 150             | °C    |

| Maximum junction temperature during          |            |      |      | 155             | °C    |

| lifetime. Note: device has to be functional, |            |      |      |                 |       |

| but not in full spec.                        |            |      |      |                 |       |

| Mechanical Shock                             |            |      | 3000 |                 | g     |

| ESD                                          | HBM        |      |      | 2               | kV    |

|                                              | CDM        |      |      | 500             | V     |

| Ultrasonic Cleaning                          | Prohibited |      |      |                 |       |

# 2.4 Digital I/O Specification

Table 4 (gyroscope interface) and (accelerometer interface) below describe the DC characteristics of SCC1300 sensor digital I/O pins. Supply voltage is 3.3 V unless otherwise noted. Current flowing into the circuit has positive values.

Table 4. Absolute maximum ratings of the SCC1300 gyroscope SPI interface.

| Parameter                          | Conditions                         | Symbol            | Min          | Тур | Max    | Unit |

|------------------------------------|------------------------------------|-------------------|--------------|-----|--------|------|

| Input terminal CSN_G               |                                    |                   |              |     |        |      |

| Pull up current                    | $V_{IN} = 0 V$                     | $I_{PU}$          | 10           |     | 50     | μΑ   |

| Input high voltage                 | DVDD_G = 3.3 V                     | $V_{IH}$          | 2            |     | DVDD_G | V    |

| Input low voltage                  | DVDD_G = 3.3 V                     | $V_{IL}$          |              |     | 8.0    | V    |

| Hysteresis                         | DVDD_G = 3.3 V                     | $V_{HYST}$        | 0.3          |     |        | V    |

| $V_{IN}$                           | Open circuit                       | $V_{IN}$          | 2            |     |        | V    |

| Input terminal SCK_G               |                                    |                   |              |     |        |      |

| Input high voltage                 | DVDD_G = 3.3 V                     | $V_{IH}$          | 2            |     | DVDD_G | V    |

| Input low voltage                  | DVDD_G = 3.3 V                     | $V_{IL}$          |              |     | 8.0    | V    |

| Hysteresis                         | DVDD_G = 3.3 V                     | $V_{HYST}$        | 0.3          |     |        | V    |

| Input leakage current              | $0 < V_{MISO} < 3.3 V$             | I <sub>LEAK</sub> | -1           |     | 1      | uA   |

| Output terminal MOSI_G             |                                    |                   |              |     |        |      |

| Input high voltage                 | DVDD_G = 3.3 V                     | $V_{IH}$          | 2            |     | DVDD_G | V    |

| Input low voltage                  | DVDD_G = 3.3 V                     | $V_{IL}$          |              |     | 8.0    | V    |

| Hysteresis                         | DVDD_G = 3.3 V                     | $V_{HYST}$        | 0.3          |     |        | V    |

| Input current source (pull-down)   | $V_{IN} = V_{DVDD\_G}$             | I <sub>LEAK</sub> | 10           |     | 50     | uA   |

| $V_{IN}$                           | Open circuit                       | $V_{IN}$          |              |     | 0.3    | V    |

| Output terminal MISO_G (Tri-state) |                                    |                   |              |     |        |      |

| Output high voltage                | $I_{OUT} = -1mA$                   | $V_{OH}$          | DVDD_G -0.5V |     |        | V    |

|                                    | $I_{OUT} = -50\mu A$               |                   | DVDD_G -0.2V |     |        | ٧    |

| Output low voltage                 | $0 \le V_{MISO} \le 3.3 \text{ V}$ | $V_{OL}$          |              |     | 0.5    | V    |

| Capacitive load                    |                                    |                   |              |     | 200    | pF   |

| Table 5. Absolute r | maximum ratings | of the | SCC1300 | accelerometer | SPI interface. |

|---------------------|-----------------|--------|---------|---------------|----------------|

|                     |                 |        |         |               |                |

| Parameter                    | Conditions               | Symbol     | Min           | Тур | Max    | Unit |

|------------------------------|--------------------------|------------|---------------|-----|--------|------|

| Input terminal CSB_A         |                          |            |               |     |        |      |

| Pull up current              | $V_{IN} = 0 V$           | $I_{PU}$   | 10            |     | 50     | μΑ   |

| Input high voltage           | DVDD_A = 3.3 V           | $V_{IH}$   | 2             |     | DVDD_A | V    |

| Input low voltage            | DVDD_A = 3.3 V           | $V_{IL}$   |               |     | 8.0    | V    |

| Hysteresis                   | DVDD_A = 3.3 V           | $V_{HYST}$ | 0.18          |     |        | V    |

| Input terminal MOSI_A, SCK_A |                          |            |               |     |        |      |

| Pull down current            | $V_{IN} = 3.3 \text{ V}$ | $I_{PD}$   | 10            |     | 50     | μΑ   |

| Input high voltage           | DVDD_A = 3.3 V           | $V_{IH}$   | 2             |     | DVDD_A | V    |

| Input low voltage            | DVDD_A = 3.3 V           | $V_L$      |               |     | 8.0    | V    |

| Hysteresis                   | DVDD_A = 3.3 V           | $V_{HYST}$ | 0.18          |     |        | V    |

| Output terminal MISO_A       |                          |            |               |     |        |      |

| Output high voltage          | I > -1mA                 | $V_{OH}$   | DVDD_A - 0.5V |     |        | V    |

|                              | DVDD_A = 3.3 V           |            |               |     |        |      |

| Output low voltage           | I < 1 mA                 | $V_{OL}$   |               |     | 0.5    | V    |

| Tri-state leakage            | $0 < V_{MISO} < 3.3 V$   | $I_{LEAK}$ | -3            |     | 3      | uA   |

# 2.5 SPI AC Characteristics

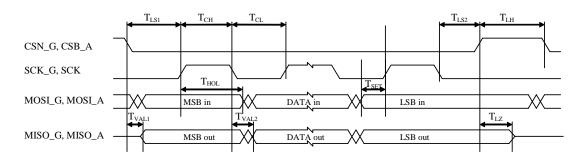

The AC characteristics of SCC1300 are defined in Figure 4 and Table 6.

Figure 4. Timing diagram of SPI communication

Table 6. Timing Characteristics of SPI Communication.

| Parameter         | Condition                                      | Min                 | Тур                 | Max                       | Units |

|-------------------|------------------------------------------------|---------------------|---------------------|---------------------------|-------|

| F <sub>SPI</sub>  |                                                |                     |                     | 8                         | MHz   |

| T <sub>SPI</sub>  |                                                |                     | 1/ F <sub>SPI</sub> |                           |       |

| T <sub>CH</sub>   | SCK_G, SCK_A high time                         | T <sub>SPI</sub> /2 |                     |                           | ns    |

| T <sub>CL</sub>   | SCK_G, SCK_A low time                          | T <sub>SPI</sub> /2 |                     |                           | ns    |

| T <sub>LS1</sub>  | CSN_G, CSB_A setup time                        | T <sub>SPI</sub> /2 |                     |                           | ns    |

| T <sub>VAL1</sub> | Delay CSN_G -> MISO_G                          |                     |                     | T <sub>SPI</sub> /4       | ns    |

| <b>T</b>          | Delay CSB_A -> MISO_A                          | T /4                |                     |                           |       |

| T <sub>SET</sub>  | MOSI_G, MOSI_A setup time                      | T <sub>SPI</sub> /4 |                     |                           | ns    |

| T <sub>HOL</sub>  | MOSI_G, MOSI_A data hold time                  | T <sub>SPI</sub> /4 |                     |                           | ns    |

| T <sub>VAL2</sub> | Delay SCK_G -> MISO_G<br>Delay SCK_A -> MISO_A |                     |                     | 1.3 * T <sub>SPI</sub> /4 | ns    |

| T <sub>LS2</sub>  | CSN_G, CSB_A hold time                         | T <sub>SPI</sub> /2 |                     |                           | ns    |

| T <sub>LZ</sub>   | Tri-state delay time                           |                     |                     | T <sub>SPI</sub> /4       | ns    |

| T <sub>RISE</sub> | Rise time of the SCK_G, SCK_A                  |                     |                     | 10                        | ns    |

| T <sub>FALL</sub> | Fall time of the SCK_G, SCK_A                  |                     |                     | 10                        | ns    |

| T <sub>LH</sub>   | Time between SPI cycles                        | $T_{SPI}$           |                     |                           | ns    |

# 3 Reset and Power Up

After the start-up the angular rate and acceleration data is immediately available through SPI registers. There is no need to initialize the gyroscope or accelerometer before starting to use it. If the application requires monitoring operation correctness there are several options available to monitor the status.

# 3.1 Power-up Sequence for Gyroscope

To ensure correct ASIC start up please connect the digital supply voltage  $V_{DVDD\_G}$  (3.3V) before the analog supply voltage  $V_{AVDD\_G}$  (5.0V) to the gyro ASIC. After power up please read Status register twice to clear error flags. Angular rate data is available immediately so no start up command sequence is required if error flags are not used.

Table 7. SCC1300 gyroscope power-up sequence.

| Procedure                            | Functions                              | Check |

|--------------------------------------|----------------------------------------|-------|

| Set V <sub>DVDD_G</sub> V=3.03.6V    |                                        |       |

| Wait 10ms                            |                                        |       |

| Set V <sub>AVDD_G</sub> V=4.755.25V  |                                        |       |

| Wait 800 ms                          |                                        |       |

| Read Status register (08h) two times | Acknowledge error flags after start up |       |

# 3.2 Start-up and Operation Sequence for Accelerometer

## 3.2.1 Recommended Start-up Sequence

For correct device operation there are no specific configuration needed for the device before starting of measuring the acceleration. However if the device diagnostic features are being used the following operations could be made after the powering on the device.

Table 8. SCC1300 accelerometer part start-up sequence.

| Procedure                                                         | Functions                                                                           | Check                                                                                              |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Set Vdd=3.03.6V                                                   | Release part from reset                                                             |                                                                                                    |

| Wait 35ms                                                         | Memory reading and self-diagnostic Settling of signal path                          |                                                                                                    |

| Read INT_STATUS                                                   | Acknowledge for possible saturation (SAT-bit) Checksum pass detected from SPI frame | SPI fixed bits<br>SPI ST=0                                                                         |

| Write CTRL=00001010 (a) or CTRL=00001000 (b) or CTRL=00000000 (c) | Set PORST=0 (abc) Start STC (ab) Start STS (a)                                      | SPI fixed bits<br>SPI FRME=0<br>SPI ST=0<br>SPI SAT=0                                              |

| Wait 10ms                                                         | STS calculation                                                                     |                                                                                                    |

| Read CTRL                                                         | Check that STC is on, if enabled Check that STS is over if enabled                  | CTRL.ST=1 CTRL.ST_CFG=0 SPI fixed bits SPI FRME=0 SPI PORST=0 SPI ST=0 SPI SAT=0 dPAR, data parity |

| Read Z_MSB, Z_LSB, Y_MSB, Y_LSB, X_MSB, X_LSB                     | Read acceleration data                                                              | SPI fixed bits SPI FRME=0 SPI PORST=0 SPI ST=0 SPI SAT=0 dPAR, data parity                         |

# 3.2.2 Recommended Operation Sequence for Acceleration Data Reading

# Table 9. Reading of the acceleration data

| Procedure                            | Functions                                                                                   | Check                                                                      |

|--------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Read acceleration data               | Desired x, y, or/and z-data                                                                 | SPI fixed bits SPI FRME=0 SPI PORST=0 SPI ST=0 SPI SAT=0 dPAR, data parity |

| Repeat previous line (N-1) times     | Noise averaging                                                                             |                                                                            |

| Calculate average (AVE) of N-samples | Noise averaging                                                                             |                                                                            |

| Read acceleration data               | Desired x, y, or/and z-data (one read before sending AVE forward to check SPI failure bits) | SPI fixed bits SPI FRME=0 SPI PORST=0 SPI ST=0 SPI SAT=0 dPAR, data parity |

| Send calculated AVE forward          |                                                                                             |                                                                            |

| Jump back to item 2                  |                                                                                             |                                                                            |

### 4 Component Interfacing

### 4.1 SPI Interfaces

SCC1300 sensor has two individual SPI interfaces for accelerometer and angular rate sensor that need to be addressed separately. Both interfaces have their own four wire interconnection pins in the component package. SPI communication transfers data between SPI master and registers of the SCC1300 ASICs. SCC1300 ASICs always operate as slave devices in the master-slave operation mode.

### SCC1300 Angular rate sensor ASIC SPI interface:

| MOSI_G | master out slave in      | $\mu P \rightarrow ASIC$ |

|--------|--------------------------|--------------------------|

| MISO_G | master in slave out      | $ASIC \rightarrow \mu P$ |

| SCK_G  | serial clock             | $\mu P \rightarrow ASIC$ |

| CSN_G  | chip select (low active) | $\mu P \rightarrow ASIC$ |

#### SCC1300 Accelerometer ASIC SPI interface:

| MOSI_A | master out slave in      | $\mu P \rightarrow ASIC$ |

|--------|--------------------------|--------------------------|

| MISO_A | master in slave out      | $ASIC \rightarrow \mu P$ |

| SCK_A  | serial clock             | $\mu P \rightarrow ASIC$ |

| CSB_A  | chip select (low active) | $\mu P \rightarrow ASIC$ |

PLEASE NOTICE THAT EXACTLY THE SAME SPI ROUTINES DOES NOT WORK FOR BOTH ASICS! E.g. SCC1300 accelerometer ASIC uses 8 bit addressing in SPI and SCC1300 angular rate sensor ASIC uses 16 bit addressing.

Both SPI interfaces and instructions to use them are explained separately in the following chapters.

# 4.2 Gyroscope Interface

This chapter describes the SCC1300 angular rate sensor ASIC interface and how to use it. The angular rate sensor ASIC SPI interface has 16 bit addressing.

### 4.2.1 SPI Transfer

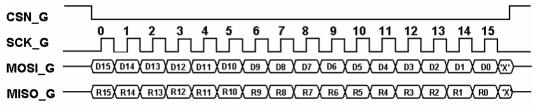

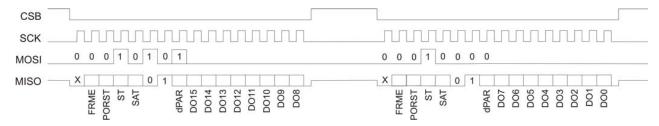

The SPI transfer is based on a 16-bit protocol. Figure 5 shows an example of a single 16-bit data transmission. Each output data/status-bits are shifted out on the falling edge of SCK (MISO line). Each bit is sampled on the rising edge of SCK (MOSI line).

Figure 5. SCC1300 angular rate sensor 16-bit data transmission.

After the falling edge of CSN\_G the device interprets the first 16-bit word is an address transfer having a bit coding scheme below.

### Address Transfer:

| D15 | D14 | D13 | D12 | D11 | D10 | D9   | D8   | D7   | D6   | D5   | D4   | D3   | D2 | D1 | D0  |

|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|------|----|----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | ADR6 | ADR5 | ADR4 | ADR3 | ADR2 | ADR1 | ADR0 | RW | 0  | Par |

|     |     |     |     |     |     |      |      |      |      |      |      |      |    |    | odd |

VTI Technologies Oy

Subject to changes

12/30

www.vti.fi

Doc.Nr. 82 1131 00 A

Rev. 1.0

ADR[6:0]: Register address RW: RW=1: Write access RW=0: Read access

par odd: odd parity bit.

par odd = 0 : the number of ones in the data word (D15:D1) is odd. par odd = 1 : the number of ones in the data word (D15:D1) is even.

The address selects an internal register of the device; the RW bit selects the access mode.

RW = '0' The master performs a read access on the selected register. During the transmission of the next word, the slave sends the requested register value to MISO\_G. The slave interprets the next word at MOSI\_G as an address transfer.

RW = '1' The master performs a write access on the selected register. The slave stores the next transmitted word in the selected device register of MOSI\_G and sends the actual register value in response to MOSI\_G. The transmission goes on with an address transfer to MOSI\_G and the address mode flags to MISO G.

If the device is addressed by a nonexistent address it will respond with '0'.

The next table shows the encoding scheme of a data value for a write access.

#### **Data Transfer:**

| D15   | D14   | D13   | D12   | D11   | D10  | D9   | D8   | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0  |

|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|-----|

| Dat14 | Dat13 | Dat12 | Dat11 | Dat10 | Dat9 | Dat8 | Dat7 | Dat6 | Dat5 | Dat4 | Dat3 | Dat2 | Dat1 | Dat0 | Par |

|       |       |       |       |       |      |      |      |      |      |      |      |      |      |      | odd |

dat[14:0]: data value for write access (15 Bit)

par odd : see Address Transfer

It is possible to combine the two access modes (write and read access) during one communication. The communication can be finished after last transmitted word of mixed access communication frame with CSN\_G='1'. CSN\_G must be '0' during mixed access communication frame.

#### SPI result values on MISO\_G

Within SPI communication SCC1300 gyro ASIC sends Status Flags (Status/Config register value) and register result values on MISO\_G. The following two tables show the encoding scheme:

### Status Flags:

|     |     | <u> </u> |     |     |     |    |    |    |    |    |    |    |    |      |         |

|-----|-----|----------|-----|-----|-----|----|----|----|----|----|----|----|----|------|---------|

| D15 | D14 | D13      | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1   | D0      |

|     |     |          |     |     |     |    |    |    |    |    |    |    |    | s_ok | par odd |

S\_OK is generated out of the monitoring flags in the status register (08h).

# Register Result:

| D15    | D14    | D13    | D12   | D11    | D10  | D9   | D8   | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0         |

|--------|--------|--------|-------|--------|------|------|------|------|------|------|------|------|------|------|------------|

| reg 14 | reg 13 | reg 12 | reg11 | reg 10 | reg9 | reg8 | reg7 | reg6 | reg5 | reg4 | reg3 | reg2 | reg1 | reg0 | par<br>odd |

reg[14:0]: value of the internal register. All bits, which are not used, are set to zero.

par odd: see Address Transfer

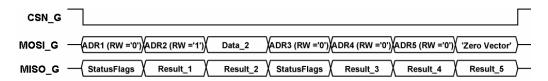

Figure 6 shows an example of communication sequence.

Figure 6. Communication example.

Each communication frame in the figure 6 contain 16 SCK cycles. After communication start (CSN\_G falling edge) the master sends ADR1 and performs a read access. In parallel the slave sends Status Flags. During the transmission of the next data word (ADR2) the slave sends the register value of ADR1 (Result\_1). On ADR2 the master performs a write access (RW='1'). The slave stores Data\_2 in the register of ADR2 and sends the current register value of ADR2 to MISO\_G. After the transmission of data value during a write access the slave always sends Status Flags. To receive Result\_5 of the last read access the Master has to send an additional word ('Zero Vector').

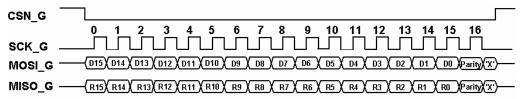

# 4.2.2 SPI Transfer Parity Mode

SCC1300 gyro ASIC is able to support parity check during SPI Transfer. This functionality is controlled by the IC Identification Register. The internal parity status is reported in Status/Config Register.

With parity enable bit set the SCC1300 gyro ASIC is expecting an additional parity bit after the transmission of each 16 bit data word. This additional parity bit requires an additional SCK cycle, i.e. the SPI frame consists of 17 SCK cycles instead of the normal 16 SCK cycles. Detecting a wrong parity bit has the following consequences:

## During read access:

The Parity Error Flag in the Status/Config Register is set. The SCC1300 reports the contents of the received register address.

# During write access:

The Parity Error Flag in the Status/Config Register is set. The SPI Write Access is cancelled. These actions are performed either if the parity failure is detected in the address word or the data word.

Due to the additional parity bit a single SPI Transfer is using now 17 Bit as shown in the Figure 7.

Figure 7. Communication in parity mode.

At the end of the data word the SPI master and the SPI slave have to add an additional parity bit. Both devices have to check the received parity according to the selected parity mode odd or even.

# 4.3 Gyroscope ASIC Addressing Space

# 4.3.1 Register Definition

The ASIC has multiple register and EEPROM blocks. The EEPROM blocks holding the calibration data will be programmed via SPI during manufacturing process. User only needs to access the Data Register Block at addresses 00h and 07h - 0Ah (addresses 01h-06h are reserved). The content of this register block is described below.

### 4.3.2 Data Register Block

Table 10. Register map of data register block

| Address<br>Dec (hex) | Register Name<br>[bit definition] | Number of<br>Bits | Read/<br>Write/<br>Factory | Data Format | Description                                                                                                                                                                                                                                                                     |

|----------------------|-----------------------------------|-------------------|----------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00(00)               | Rate_X[0]                         | 1                 | R                          | -           | odd Parity bit of Rate_X[14,1]  S_OK =0 Rate_X failed  S_OK =1 Rate_X valid (ok)  S_OK is generated out of the monitoring flags in the status register (08h).  If either one of the flags in register 08h [15:2] is 0,  S_OK will be 0. Only if all flags in register 08h[15:2] |

| 00(00)               | (S_OK Flag)                       | 1                 | R                          | -           | are 1 S_OK is set to 1                                                                                                                                                                                                                                                          |

|                      |                                   |                   |                            |             |                                                                                                                                                                                                                                                                                 |

| 00(00)               | Rate_X[15:2]                      | 14                | R                          | S           | Sensor output data format two's complement                                                                                                                                                                                                                                      |

| 07(07)               | IC Identification [14, 11:1]      | 14                | F                          | -           | Reserved                                                                                                                                                                                                                                                                        |

| 07(07)               | IC Identification[12]<br>HWParEn  | 1                 | W                          |             | Setting this bit to '1' is enabling the Parity functionality                                                                                                                                                                                                                    |

| 07(07)               | IC Identification[13]<br>HWParSel | 1                 | W                          |             | This bit is selecting an even or an odd parity mode.  Bit = 0: Even Parity mode means that the number of ones in the data word including the parity bit is even.  Bit = 1: Odd Parity mode means that the number of ones in the data word including the parity bit is odd.      |

| 08(08)               | Status/Config [14:10, 8:1]        | 14                | F                          | -           | Reserved                                                                                                                                                                                                                                                                        |

| 08(08)               | Status/Config[9]<br>(Parity_OK)   | 1                 | R                          | -           | This bit is set as soon as the SPI logic is detecting a wrong parity bit received from the $\mu$ C. This bit is automatically cleared during read access to this register. Bit = 0 : Parity error Bit = 1 : Parity check ok.                                                    |

| 09(09)               | Reserved                          | 14                | F                          | -           | Reserved                                                                                                                                                                                                                                                                        |

| 10(0A)               | Temp[0]                           | 1                 | R                          | -           | odd Parity bit of TEMP[14,1]                                                                                                                                                                                                                                                    |

| ì í                  | ,,,                               |                   |                            |             | S_OK =0 Rate_X failed                                                                                                                                                                                                                                                           |

| 10(0A)               | Temp[1] (S_OK Flag)               | 1                 | R                          | -           | S_OK =1 Rate_X valid                                                                                                                                                                                                                                                            |

| 10(0A)               | Temp[15,2]                        | 14                | R                          | S           | Temperature sensor output                                                                                                                                                                                                                                                       |

The offset of temperature data is factory calibrated but sensitivity of the temperature data varies from part to part. Note: Registers marked with F are reserved for factory use only and not to be written to.

#### 4.4 Accelerometer Interface

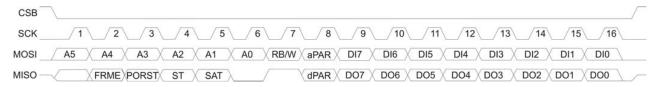

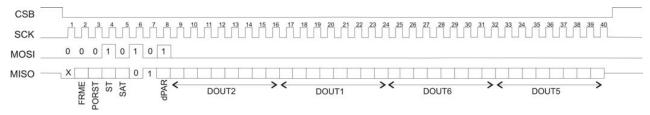

This chapter describes the SCC1300 accelerometer part SPI interface and how to use it. SPI frame format and transfer protocol for SCC1300 accelerometer ASIC is presented in Figure 8.

Figure 8. SPI frame format for accelerometer interface.

- MOSI A

- A5:A0 Register address

- RB/W Read/Write selection, '0'=read

aPAR Odd parity for bits A5:A0, RB/W

DI7:DI0 Input data for data write

- MISO A

- Bit 1 not defined bit

- FRME Frame error indication (previous frame)

- Bit 3-5 status bits

- PORST Power On Reset Status

- ST Self Test error

- SAT Output SATuration indicator

- Bit 6 always '0', fixed bit

Bit 7 always '1', fixed bit

- dPAR Odd parity for output data (DO7:DO0)

- DO7:DO0 Output data

Each communication frame contains 16 bits. Each output data/status-bits are shifted out on the falling edge of SCK (MISO line). Each bit is sampled on the rising edge of SCK (MOSI line). The first 8 bits in MOSI\_A line contains info about the operation (read/write) and the register address being accessed. First 6 bits define 6 bit address for selected operation, which is defined by bit 7 ('0' = read '1' = write), which is followed by odd parity bit (aPAR) for 8 bit pattern. The later 8 bits in MOSI\_A line contain data for a write operation and are ignored in case of read operation.

The first bits in MISO\_A line are frame error bit (FRME, bit2) of previous frame, reset status bit (PORST, bit3), self-test status bit (ST, bit4), saturation status (SAT, bit5), fixed zero bit (bit6), fixed one bit (bit7) and odd parity bit of output data (dPAR, bit8)). Parity is calculated from data, which is currently sent. The later 8 bits contain data for a read operation. During the write operation, these data bits are previous data bits of addressed register.

For write commands, data is written into the addressed register on the rising edge of CSB\_A. If the command frame is invalid, data will not be written into the register.

The output register is shifted out MSB first over MISO\_A output. Attempt to read a reserved register outputs data of 00h.

When CSB is high state between data transfers, MISO\_A line is in high-impedance state. If bit CTRL.SDODIS is set to '1', MISO\_A line is always in high-impedance state. In multi-chip SPI bus master can send data to all slave chips simultaneously.

### 4.4.1 Output of Acceleration Data

16-bit data is sent in 8-bit data bytes during two frames. Each frame contains odd parity bit of data bits. Number format of acceleration data is two's complement number.

### 4.4.1.1 Register read operation

An example of X-axis acceleration read command is presented in Figure 9. Master gives the register address to be read via MOSI\_A line: '05' in hex format and '000101' in binary format, register name is  $X_MSB$  (X-axis MSB frame).  $7^{th}$  bit is set to '0' to indicate the read operation and  $8^{th}$  bit is 1 for odd parity.

The sensor replies to asked operation by transferring the register content via MISO\_A line. After transferring the asked X\_MSB register content, master gives next register address to be read: '04' in hex format and '000100' in binary format, register name is X\_LSB (X-axis LSB frame). The sensor replies to asked operation by transferring the register content MSB first.

Figure 9: Example of 16 bit acceleration data transfer from registers DOUT2-1 (05h,04h).

DO15...DO0 bits are acceleration data bits (DO15=MSB) and parity (dPAR) is odd parity of register of 8 data bits. FRME is possible frame error bit of previous frame, PORST is reset bit, ST is self-test status bit and SAT is output saturation status bit.

### 4.4.1.2 Decremented register read operation

In Figure 10 is presented a decremented read operation where the content of four output registers is read by one SPI frame. After normal register addressing and one register content reading the  $\mu$ C keeps CSB\_A line low and continues supplying the SCK\_A pulses. After every 8 SCK pulses the output data address is decremented by one and the previous DOUT register's content is shifted out without parity bits. Parity bit is calculated and transferred only for the first data frame. From X\_LSB register address the ASIC jumps to Z\_MSB. Decremented reading is possible only for registers X\_LSB ... Z\_MSB.

Decremented read is not recommended in fail-safe critical applications because output data parity is only available for first 8bit data.

Figure 10: An example of decremented read operation.

### 4.4.2 MOSI data of SPI commands

Table 11. MOSI A data during SPI read command

| Register to be read | Function                         | MOSI (15:0) [bits] | MOSI [hex] |

|---------------------|----------------------------------|--------------------|------------|

| REVID               | Read ASIC revision ID            | 000000 01 xxxxxxxx | 01xx       |

| CTRL                | Read CTRL register               | 000001 00 xxxxxxxx | 04xx       |

| STATUS              | Read Status register             | 000010 00 xxxxxxxx | 08xx       |

| X_LSB               | Read acceleration on X-axis, LSB | 000100 00 xxxxxxxx | 10xx       |

| X_MSB               | Read acceleration on X-axis, MSB | 000101 01 xxxxxxxx | 15xx       |

| Y_LSB               | Read acceleration on Y-axis, LSB | 000110 01 xxxxxxxx | 19xx       |

| Y_MSB               | Read acceleration on Y-axis, MSB | 000111 00 xxxxxxxx | 1Cxx       |

| Z_LSB               | Read acceleration on Z-axis, LSB | 001000 00 xxxxxxxx | 20xx       |

| Z_MSB               | Read acceleration on Z-axis, MSB | 001001 01 xxxxxxxx | 25xx       |

| TEMP_LSB            | Read temperature, LSB            | 010010 01 xxxxxxxx | 49xx       |

| TEMP_MSB            | Read temperature, MSB            | 010011 00 xxxxxxxx | 4Cxx       |

| INT_STATUS          | Read INT_STATUS register         | 010110 00 xxxxxxxx | 58xx       |

| ID                  | Read product ID number           | 100111 01 xxxxxxxx | 9Dxx       |

Table 12. MOSI\_A data during write command

| Register to be written | Function                      | MOSI (15:0) [bits] | MOSI [hex] |

|------------------------|-------------------------------|--------------------|------------|

| RESET                  | Reset component (data C'hex ) | 000011 10 00001100 | 0E0C       |

| RESET                  | Reset component (data 5'hex)  | 000011 10 00000101 | 0E05       |

| RESET                  | Reset component (data F'hex)  | 000011 10 00001111 | 0E0F       |

|                        |                               |                    |            |

| CTRL                   | Set PORST to zero             | 000001 11 00000000 | 0700       |

| CTRL                   | Set chip to power down mode   | 000001 11 00100000 | 0720       |

| CTRL                   | Start self-diagnostic         | 000001 11 00001000 | 0708       |

| CTRL                   | Start memory self-test        | 000001 11 00000100 | 0704       |

## 4.4.3 Error Conditioning

### FRME-bit

While sending a frame, if CSB is raised to 1 before sending 16 SCKs, the frame is considered invalid. The frame error is raised only if number of SCK pulses is not divisible by 8 to support decremented mode reading. When an invalid frame is received, the last command is simply ignored and the register contents are left unchanged. Status bit STATUS.FRME is set to indicate this error condition. During next SPI frame error bit send out as bit number 2. Bit STATUS.FRME will be reset, if correct frame is received.

### PORST-bit

PORST length is 1bit in SPI frame. PORST bit is set if chip is reset (HW reset by POR or supply on/off) or under-voltage is detected. PORST bit is also set after power-up because chip has been in reset state. PORST can be set to zero (reseted) by writing CTRL.PORST =0. Software (SW) reset does not set PORST.

When CTRL.PORST bit is written to 0 via SPI, there is 300ns delay before register value is set to zero.

### ST-bit

Self-test frame status (ST) is set if STC or STS is alarmed or checksum is not passed.

- CASE 1: Checksum fails and ST-frame bit is set 1. ST is set back to zero when (and only

if) new checksum calculation is passed.

- CASE 2: ST-frame bit is set because STC or STS is alarmed. In this case ST-frame bit can be cleared by INT STATUS register reading.

### **SAT-bit**

Saturation status (SAT) is set if any of axis xyz is saturated and it can be cleared by INT\_STATUS register reading. This bit is kept active even failure condition is over if it is not acknowledged.

#### aPAR-bit

aPAR is odd parity bit of input address+RB/W-bit. Master write it and slave check that bit.

- If there is parity error and RB/W='1', write command is ignored and frame error bit is set to STATUS-register and to SPI frame. Next correct SPI frame will zero this bit.

- If there is parity error and RB/W='0', read command is performed normally and frame error bit is set to STATUS-register and to SPI frame. Next correct SPI frame will zero this bit.

Table 13. Address parity.

| Addres | ss |    |    |    |    |      |      | Notes         |

|--------|----|----|----|----|----|------|------|---------------|

| A5     | A4 | A3 | A2 | A1 | A0 | RB/W | aPAR |               |

| 0      | 0  | 0  | 0  | 0  | 0  | 0    | 1    | correct frame |

| 1      | 1  | 1  | 1  | 1  | 1  | 1    | 0    | correct frame |

| 1      | 0  | 1  | 0  | 1  | 0  | 1    | 1    | correct frame |

| 0      | 1  | 0  | 1  | 0  | 1  | 0    | 0    | correct frame |

#### dPAR-bit

dPAR bit is odd parity bit of 8bit data that is currently sent in the frame. Master checks this bit and compares to received data. Using dPAR at least one bit errors in data transmission can be detected.

#### **Fixed bits**

Bits 6 and 7 are always fixed in MISO line. Bit 6 should always be '0' and bit 7 always '1'

# **Output data**

- 1. Reset stage: When component is in reset or under voltage state, PORST bit in SPI frame and CTRL. PORST bit is set. Furthermore, all register values are set to 00'hex.

- 2. Saturation: When acceleration exceeds measurement range, the output data is saturated to specified positive or negative full-scale.

- 3. Self-diagnostic failure: The ST bit in SPI frame is set when memory diagnostic or signal path diagnostic functions fail. Furthermore acceleration output data is forced to 7FFF'hex if memory diagnostic fails or to FFFF'hex if signal path diagnostic functions (STC/STS) fail.

#### 4.5 **Accelerometer ASIC Addressing Space**

The SCC1300 register contents and bit definitions are described in detail in the following sections.

#### 4.5.1 **Register Map of Accelerometer**

Table 14. Register address space

| Address<br>Dec (hex) | Register Name [bit definition] | Number<br>of Bits | Read/<br>Write | Data format | Description                                                                        |

|----------------------|--------------------------------|-------------------|----------------|-------------|------------------------------------------------------------------------------------|

| 00(00)               | REVID                          | 8                 | R              | _           | ASIC revision identification number, each ASIC version has different REVID-number. |

| 01(01)               | CTRL                           | 8                 | R/W            | _           | Please refer to chapter 4.5.2 for CONTROL register details.                        |

| 02(02)               | STATUS [7:3]                   | 5                 | R              | -           | Reserved                                                                           |

| 02(02)               | STATUS [2]                     | 1                 | R              |             | Analog test mode status                                                            |

| ()                   | (ATEST)                        |                   |                |             | 1 – Test mode is active                                                            |

| 20(20)               | 07.47.10.141                   |                   | _              |             | 0 – Test mode is not active                                                        |

| 02(02)               | STATUS [1]<br>(CSMERR)         | 1                 | R              |             | EEPROM Checksum Error. ST bit of SPI frame is also set if CSMERR is set.           |

| 02(02)               | STATUS [1]                     | 1                 | R              |             | SPI frame error. Bit is reset, when next correct SPI frame is                      |

| . ,                  | (FRME)                         |                   |                |             | received. Bit is also visible in SPI frame.                                        |

| 03(03)               | RESET                          | 8                 | R/W            |             | Writing 0C'hex, 05'hex, 0F'hex in this order resets component.                     |

| 04(04)               | X_LSB [7:2]                    | 6                 | R              |             | X-axis LSB data frame (Read always X_MSB prior to X_LSB)                           |

| 04(04)               | X_LSB [1:0]                    | 2                 | R              |             | Reserved                                                                           |

| 05(05)               | X_MSB [6:0]                    | 7                 | R              |             | X-axis MSB data bits (Reading of this register latches X_LSB)                      |

| 05(05)               | X_MSB [7]                      | 1                 | R              |             | Reserved                                                                           |

| 06(06)               | Y_LSB [7:2]                    | 6                 | R              |             | Y-axis LSB data frame (Read always Y_MSB prior to Y_LSB)                           |

| 06(06)               | Y_LSB [1:0]                    | 2                 | R              |             | Reserved                                                                           |

| 07(07)               | Y_MSB [6:0]                    | 7                 | R              |             | Y-axis MSB data bits (Reading of this register latches Y LSB)                      |

| 07(07)               | Y_MSB [7]                      | 1                 | R              |             | Reserved                                                                           |

| 08(08)               | Z_LSB [7:2]                    | 6                 | R              |             | Z-axis LSB data frame (Read Z_MSB prior to Z_LSB)                                  |

| 08(08)               | Y_LSB [1:0]                    | 2                 | R              |             | Reserved                                                                           |

| 09(09)               | Z_MSB [6:0]                    | 7                 | R              |             | Z-axis MSB data bits (Reading of this register latches Z_LSB)                      |

| 09(09)               | Z_MSB [7]                      | 1                 | R              |             | Reserved                                                                           |

| 12(0C)               | TEMP_LSB                       | 8                 |                | See chapter | Data bits [7:0] of temperature sensor.                                             |

|                      |                                |                   |                | 4.5.3.      | Read always TEMP_MSB prior to TEMP_LSB.                                            |

| 13(0D)               | TEMP_MSB                       | 8                 |                | See chapter | Data bits [15:8] of temperature sensor.                                            |

|                      |                                |                   |                | 4.5.3.      | Reading of this register latches TEMP_LSB.                                         |

| 16(10)               | INT_STATUS [7]                 | 1                 | R              |             | Reserved                                                                           |

| 16(10)               | INT_STATUS [6]                 | 1                 | R              |             | Saturation status of output data                                                   |

|                      | (SAT)                          |                   |                |             | 1 – Over range detected, one or 2-3 of xyz axis is saturated                       |

|                      |                                |                   |                |             | and output data is not valid.                                                      |

|                      |                                |                   |                |             | 0 – Data in range                                                                  |

|                      |                                |                   |                |             | SAT bit is also visible in SPI frame. This bit can be active after                 |

|                      |                                |                   |                |             | start-up or reset stage before signal path settles to final value                  |

|                      |                                |                   |                |             | and it has to be acknowledged in start-up sequence (see                            |

|                      |                                |                   |                |             | Table 8) or after SW reset or after PORST stage.                                   |

| 16(10)               | INT_STATUS [5]                 |                   | R              |             | Status of gravitation based start-up self test                                     |

|                      | (STS)                          |                   |                |             | 1 – Failure                                                                        |

|                      |                                |                   |                |             | 0 – No failure                                                                     |

|                      |                                |                   |                |             | STS sets also ST bit in SPI frame.                                                 |

| 16(10)               | INT_STATUS [4]                 |                   |                |             | Status of continuous self test                                                     |

|                      | (STC)                          |                   |                |             | 1 – Failure                                                                        |

|                      |                                |                   |                |             | 0 – No failure                                                                     |

|                      |                                |                   |                |             | STC sets also ST bit in SPI frame.                                                 |

| 16(10)               | INT_STATUS [3:0]               |                   |                |             | Reserved                                                                           |

| 27(1B)               | ID                             | 8                 |                |             | Component identification number (write operation by user is                        |

|                      |                                |                   |                |             | possible to this register but not to non-volatile memory)                          |

Note: The acceleration data is presented in 2's complement format. At 0 g acceleration the output is ideally 0000h. Note: INT\_STATUS: The bits in this interrupt status register and corresponding SPI frame bits are cleared after register has been read. Register reading is treated as interrupt acknowledgement signal. These bits are kept active even failure condition is over if they are not acknowledged.

# 4.5.2 Control Register (CTRL)

Table 15. SCC1300 accelerometer ASIC control register bit level description.

| Bits | Mode | Initial<br>Value | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|------|------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | RW   | 0                |        | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6    | RW   | 0                | PORST  | 1 means reset state. Bit gets set to 1 when the digital gets reset by supply off control or under voltage control. Bit is set after supply off/on transition or startup. This bit can not be set by SPI but it can be reset to 0 by writing a 0 over the SPI. This bit is also sent as Bit3 of SPI output data frame on MISO.                                                                                                                                                                                                           |

| 5    | RW   | 0                | PDOW   | Set chip to power down mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4    | RW   | 0                | SLEEP  | Set chip to sleep mode. This bit can not be set to 1 if PDOW is already 1 or if PDOW is being set by the current SPI command.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3    | RW   | 0                | ST     | Set chip to self-test mode. Start continuous self-test calculation (STC). This bit can not be set to 1 if PDOW or SLEEP or MTST is already 1 or if PDOW or SLEEP or MTST is being set by the current SPI command. Use INT_STATUS.STC and ST bit of SPI frame for test result monitoring.                                                                                                                                                                                                                                                |

| 2    | RW   | 0                | MST    | Memory self-test function is activated, when user sets bit to '1'. This bit is reset to 0 when test is over. During memory self test, SPI access is prevented for 85us. This bit can not be set to 1 if PDOW or SLEEP is already 1 or if PDOW or SLEEP is being set by the current SPI command. Test is done automatically during start-up. Set other bits to zero in CTRL register by previous SPI command before starting memory self-test by CTRL.MST command. Use STATUS.CSMERR for test result monitoring and ST bit in SPI frame. |

| 1    | RW   | 0                | ST_CFG | Self-test configuration. Start gravitation based start-up self-test calculation (STS). This bit can not be set to 1 if PDOW or SLEEP or MTST is already 1 or if PDOW or SLEEP or MTST is being set by the current SPI command. STC and STS have same priority and they can be set and used simultaneously. This bit is set to 0 when test is over. Use INT_STATUS.STS and ST bit of SPI frame for test result monitoring.                                                                                                               |

| 0    | RW   | 0                | MISO   | <ul> <li>0 = Set MISO line to normal state (= High impedance state between SPI transfers, data out state during transfers)</li> <li>1 = Set MISO like to a continuous high impedance state (same write command to multiple slaves, which share MISO line).</li> </ul>                                                                                                                                                                                                                                                                   |

# 4.5.3 Temperature Output Registers

The offset of temperature data is factory calibrated but sensitivity of the temperature data varies from part to part. Temperature data is in unsigned format and 13 bits (13:1) of TEMP\_MSB/TEMP\_LSB are used for temperature. Here is presented temperature calculation using 10bit but 3-extra LSB bit can be used to improve resolution in noise sense if needed.

Table 16 Bit level description for accelerometer temperature registers

| Register                    | TEMP_N | 1SB |    |    |    |    |    | TEN | /IP_L | SB |    |       |    |

|-----------------------------|--------|-----|----|----|----|----|----|-----|-------|----|----|-------|----|

| Bit number                  | B7:B6  | B5  | B4 | B3 | B2 | B1 | B0 | B7  | B6    | B5 | B4 | B3:B1 | B0 |

| Bit in temperature register | XX     | t9  | t8 | t7 | T6 | T5 | t4 | t3  | t2    | t1 | t0 | rrr   | Χ  |

x = not used bit r=reserved

Temperature registers' typical output at +23 °C is 512 counts and 1 °C change in temperature typically corresponds to 3.2 LSB change in temperature output. Temperature information is converted to [°C] as follows

$$Temp [°C] = (23 \pm 10)°C + \frac{Temp_{dec} - 512LSB}{k \frac{LSB}{°C}},$$

where Temp[°C] is temperature in Celsius and Temp<sub>dec</sub> is temperature from TEMP\_MSB and TEMP\_LSB registers in decimal format, bits(t9:0). k is temperature slope factor specified as

|   | Min | Тур | Max | Unit   |

|---|-----|-----|-----|--------|

| k | 2.8 | 3.2 | 3.6 | LSB/°C |

VTI Technologies Oy

Subject to changes

21/30

www.vti.fi

Doc.Nr. 82 1131 00 A

Rev. 1.0

# 5 Application Information

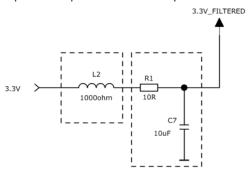

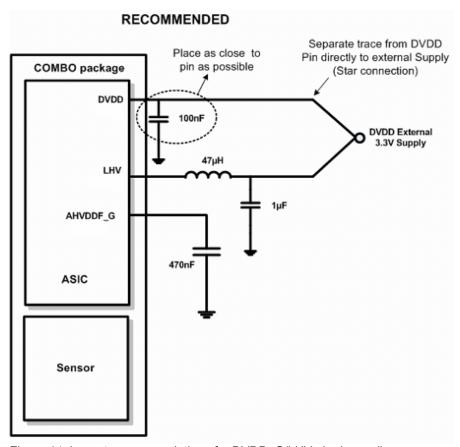

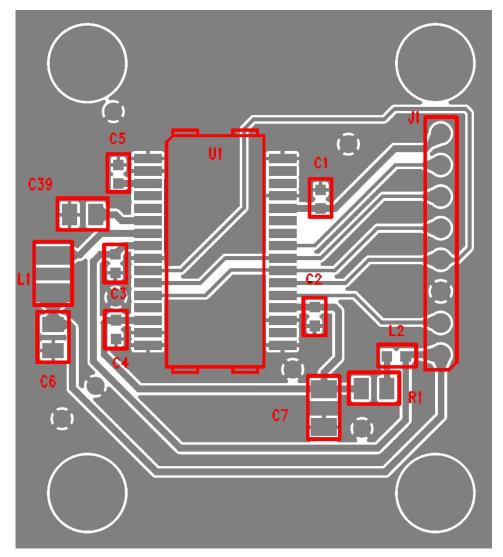

# 5.1 Pin Description

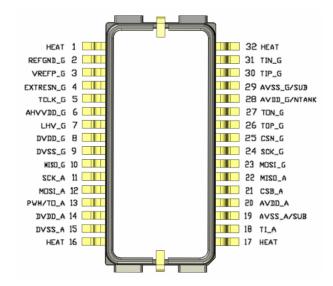

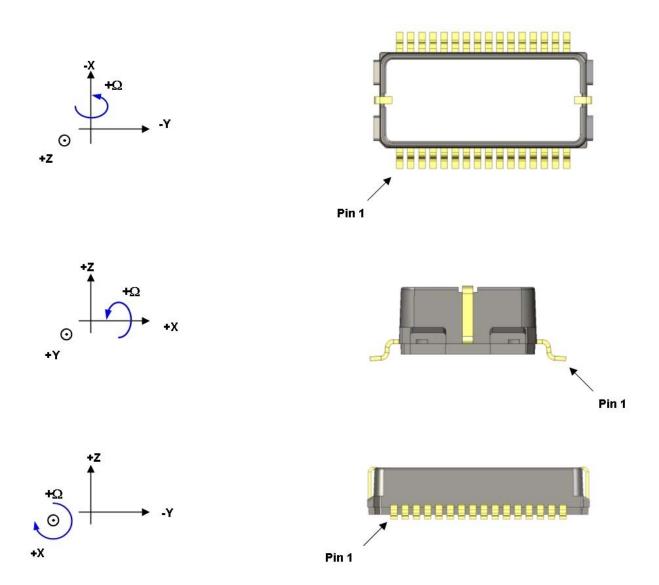

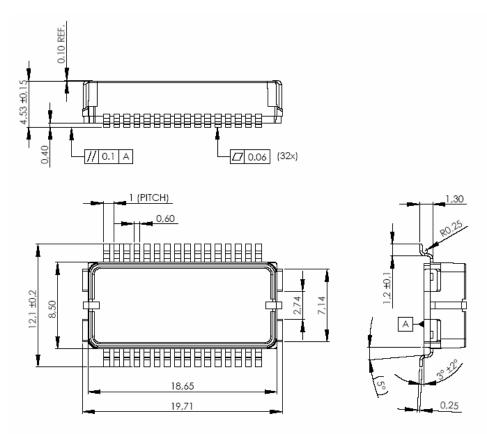

The pin out for SCC1300 is presented in Figure 11 (pin descriptions can be found from Table 17).

Figure 11. SCC1300 pinout diagram.

Table 17. SCA1300 pin descriptions.

| pin# | Name      | Type 1) | PD/PU/HV 3) | Description                                                                                                                                                                                                                                                                                              |

|------|-----------|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | HEAT      | A1      |             | Heatsink connection, externally connected to AVSS_G.                                                                                                                                                                                                                                                     |

| 2    | REFGND_G  | Al      |             | Analog reference ground should be connected external to AVSS_G                                                                                                                                                                                                                                           |

| 3    | VREFP_G   | АО      |             | External C for positive reference voltage and output pin for use as supply for external load. Max load current compare section TBD. Note this voltage can only be used as supply for analog circuits. Circuits that produce high current spikes due to switching circuit can not be driven by this node. |

| 4    | EXTRESN_G | DI      | PU          | External Reset, 3.3V level Schmitt-trigger input with internal pull-up, High low transition cause system restart                                                                                                                                                                                         |