# **EMIRR Evaluation Boards** for LMV831/LMV832/ **LMV834**

National Semiconductor Application Note 1867 Gerrit de Wagt October 3, 2008

### **General Description**

To demonstrate the EMI robustness of the LMV831/LMV832/ LMV834 and to be able to measure the parameter EMIRR, three evaluation boards have been developed; one for each device. This document describes the evaluation boards and explains how to perform EMIRR measurements. Focus is on one of the input pins as those are most sensitive to EMI. Based on symmetry considerations, it can be expected that both inputs have the same EMIRR. For reasons of simplicity of the required schematic the measurement on the IN+ pin is selected. A detailed description on EMI and EMIRR for the other pins can be found in Application Note AN-1698.

To identify EMI robust op amps, a parameter is defined that quantitatively describes the EMI performance. A quantitative measure enables the comparison and the ranking of op amps on their EMI robustness. The definition of the parameter EMIRR is given by:

$$\mathsf{EMIRR}_{\mathsf{V}_{\mathsf{RF\_PEAK}}} = 20 \log \left( \frac{\mathsf{V}_{\mathsf{RF\_PEAK}}}{\Delta \mathsf{V}_{\mathsf{OS}}} \right)$$

where  $V_{\text{RF\_PEAK}}$  is the amplitude of the applied unmodulated RF signal  $\overline{(V)}$  and  $\Delta V_{OS}$  is the resulting input-referred offset voltage shift (V).

## **Op Amp Configuration**

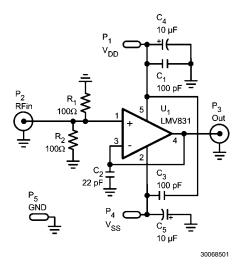

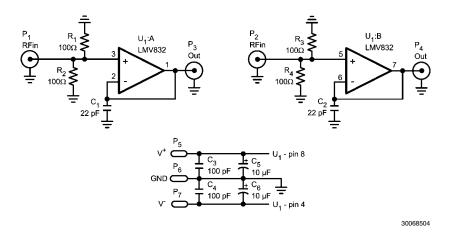

To have best defined RF levels on the pin under test, no op amp feedback elements should be in the RF signal path. Therefore, the op amp is connected in an unity-gain configuration. This yields the lowest level of RF filtering due to a feedback network. Schematics and layouts are included in this document.

# Applying the RF Signal

Care needs to be taken in applying the RF signal to the pin under test. Signals up to a few GHz will be used, so the whole RF signal path needs to match the characteristic impedance of the RF generator. This requires proper coaxial cabling from the generator to the test board. On the test board a  $50\Omega$ stripline needs to be used to bring the RF signal as close as possible to the pin under test. In this case the stripline can be connected directly from the connector to the IN+ pin. A  $50\Omega$ termination at the pin under test is also required. For symmetry reasons this is done with two  $100\Omega$  resistors in parallel, one on each side of the strip line. Setting up the test environment with a  $50\Omega$  resistor close to the LMV831/LMV832/ LMV834 ensures that the RF levels at the pin under test are well defined. This  $50\Omega$  resistor is also used to set the bias level of the IN+ pin to ground level. The DC measurements are taken at the output of the op amp. Since the op amp is in the unity gain configuration, the input referred offset voltage shift corresponds one-to-one to the measured output voltage

### Isolating the Other Pins

When the pin under test is tested, the other pins need to be decoupled for RF signals. This ensures that the obtained offset voltage shift is dominantly a result of coupling the RF signal to the pin under test. For this decoupling standard SMD components can be used.

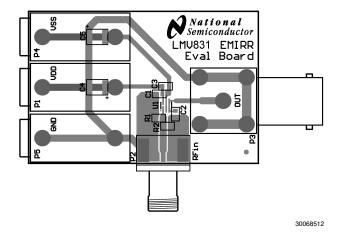

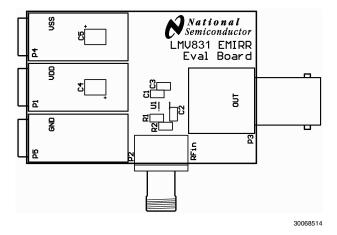

### Layout Considerations

The layout of the evaluation board requires some attention. For decoupling the supply lines it is suggested that 10 nF capacitors be placed as close as possible to the op amp. For single supply, place a capacitor between V+ and V-. For dual supplies, place one capacitor between V+ and the board ground, and a second capacitor between ground and V-. On the LMV831 evaluation board, the decoupling of the negative pin V- is implemented by a capacitor between V+ and V-. This is done for easy routing and to keep connections to the pins short. Even with the LMV831/LMV832/LMV834's inherent hardening against EMI, it is still recommended to keep the input traces short and as far as possible from RF sources. Then the RF signals entering the chip are as low as possible, and the remaining EMI can be, almost, completely eliminated in the chip by the EMI reducing features of the LMV831/ LMV832/LMV834.

#### Measurement Procedure

The measurement procedure is the same for all test circuits. To measure the input referred offset voltage shift needed for calculating the EMIRR, the following procedure can be used:

- Measure  $V_{\text{OUT}}$  when the RF signal is off.

- Measure V<sub>OUT</sub> when the RF signal is on.

- Translate measured V<sub>OUT</sub> voltages to input referred voltages. Translation is one-to-one in this case since the gain is one in the IN+ test setup.

- Subtract the two measured input referred voltages.

- Verify if the offset shift is above the noise level of the op amp setup and the op amp is not saturated. If this is not the case choose another RF level and start the procedure again.

- Calculate the EMIRR.

- If needed, transform the results to an EMIRR based on a 100 mV<sub>P</sub> RF signal.

## **LMV831 Evaluation Board**

FIGURE 1. Schematic for LMV831, Coupling RF Signal to the IN+ Pin

FIGURE 2. Layout for LMV831, All Layers

FIGURE 3. Layout for LMV831, Silk Screen

# **LMV832 Evaluation Board**

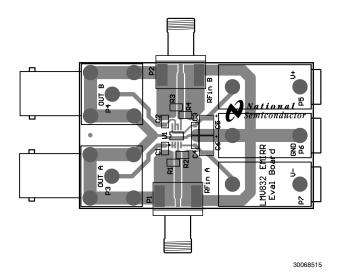

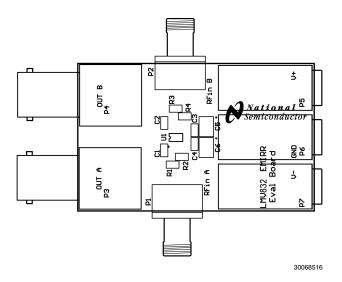

FIGURE 4. Schematic for LMV832, Coupling RF Signal to the IN+ Pin

FIGURE 5. Layout for LMV832, All Layers

FIGURE 6. Layout for LMV832, Silk Screen

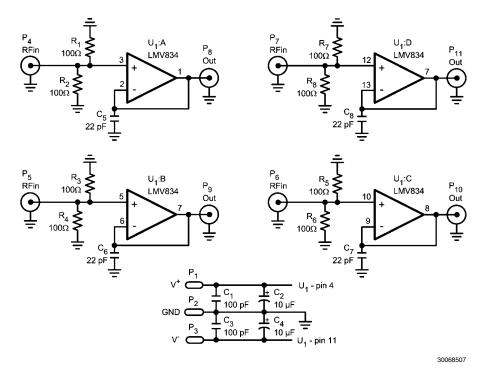

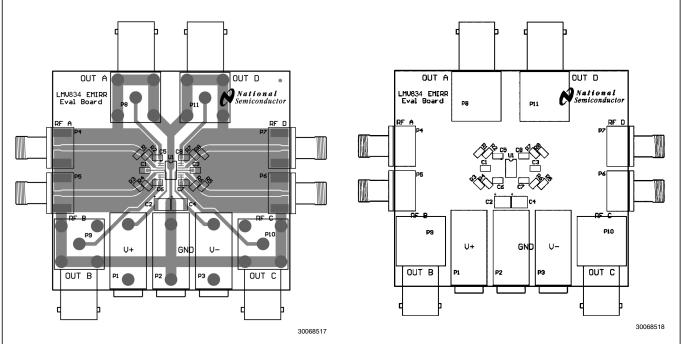

## **LMV834 Evaluation Board**

FIGURE 7. Schematic for LMV834, Coupling RF Signal to the IN+ Pin

4

FIGURE 8. Layout for LMV834, All Layers

FIGURE 9. Layout for LMV834, Silk Screen

#### Measurement Results

To show the sensitivity of the IN+ pin two types of measurement results are presented using the LMV831 evaluation board:

- The EMIRR as a function of the frequency of the applied signal. The level of the signal is set to the standard level of 100 mV<sub>P</sub> (-20 dBV<sub>P</sub>).

- The EMIRR as a function of the level of the applied signal.

The frequency is set to four typical values: 400 MHz,

900 MHz, 1.8 GHz, and 2.4 GHz.

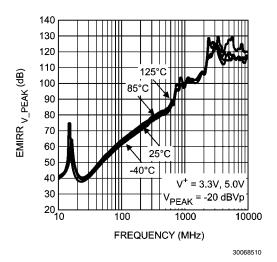

#### **EMIRR VS. FREQUENCY**

Figure 10 depicts the EMIRR versus frequency for the various temperatures. The measurement is performed with a fixed RF level of  $-20~{\rm dBV_P}$  and a varying RF signal frequency. The frequency range is 10 MHz to 10 GHz.

FIGURE 10. EMIRR vs. Frequency

#### **EMIRR VS. POWER**

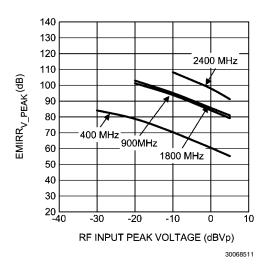

Figure 11 depicts the EMIRR as a function of power at four typical frequencies.

FIGURE 11. EMIRR vs. Power

In this figure two areas can be distinguished. At the left side of the figure, the EMIRR increases as a function of input level; whereas at the right side the EMIRR decreases as a function of the input level.

The left side of the figure is actually an artifact resulting from the limited accuracy of the measurement setup. For the relatively low input levels, the resulting offset voltage shift is well below the noise level. Thus, when calculating the EMIRR for that region, the ratio of the input level to the noise level is depicted. As the noise level is constant for the setup, an increasing EMIRR is obtained for increasing input signal level. For the right side, the obtained offset-shift is well above the noise level. As the relation between offset voltage shift and RF input level is quadratic, the ratio as used in the EMIRR is inversely proportional to the RF input level, which is in line with the displayed slope of "-1".

#### **Bill Of Materials**

The Bill of Materials (BOM) of the **LMV831** evaluation board is given in the table below.

| Designator | Description      | Comment  |

|------------|------------------|----------|

| C1, C3     | 0603 Capacitor   | 100 pF   |

| C2         | 0603 Capacitor   | 22 pF    |

| C4, C5     | Case_B Capacitor | 10 μF    |

| P1         | Connector        | Banana   |

| P2         | Connector        | SMA      |

| P3         | Connector        | BNC      |

| P4         | Connector        | Banana   |

| P5         | Connector        | Banana   |

| R1, R2     | 0603 Resistor    | 100Ω     |

| U1         | SC70             | LMV831MG |

The Bill of Materials (BOM) of the **LMV832** evaluation board is given in the table below.

| Designator     | Description      | Comment  |

|----------------|------------------|----------|

| C1, C2         | 0603 Capacitor   | 22 pF    |

| C3, C4         | 0603 Capacitor   | 100 pF   |

| C5, C6         | Case_B Capacitor | 10 μF    |

| P1, P2         | Connector        | SMA      |

| P3, P4         | Connector        | BNC      |

| P5             | Connector        | Banana   |

| P6             | Connector        | Banana   |

| P7             | Connector        | Banana   |

| R1, R2, R3, R4 | 0603 Resistor    | 100Ω     |

| U1             | MSOP             | LMV832MM |

The Bill of Materials (BOM) of the  ${\bf LMV834}$  evaluation board is given in the table below.

| Designator              | Description      | Comment  |

|-------------------------|------------------|----------|

| C1, C3                  | 0603 Capacitor   | 100 pF   |

| C2, C4                  | Case_B Capacitor | 10 μF    |

| C5, C6, C7, C8          | 0603 Capacitor   | 22 pF    |

| P1                      | Connector        | Banana   |

| P2                      | Connector        | Banana   |

| P3                      | Connector        | Banana   |

| P4, P5, P6, P7          | Connector        | SMA      |

| P8, P9, P10, P11        | Connector        | BNC      |

| R1, R2, R3, R4, R5, R6, | 0603 Resistor    | 100Ω     |

| R7, R8                  |                  |          |

| U1                      | TSSOP            | LMV834MT |

## **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Products                       |                              | Design Support          |                                |

|--------------------------------|------------------------------|-------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |

| Switching Regulators           | www.national.com/switchers   |                         |                                |

| LDOs                           | www.national.com/ldo         |                         |                                |

| LED Lighting                   | www.national.com/led         |                         |                                |

| PowerWise                      | www.national.com/powerwise   |                         |                                |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com