# **Evaluation Board for G** = 1, 2, 4, 8, **10 MHz**, 20 V/ $\mu$ s Programmable Gain In-Amp

## AD8251-EVALZ

#### **FEATURES**

Quick evaluation On-board gain control switches SMA connectors for high speed gain testing

#### **GENERAL DESCRIPTION**

The AD8251-EVALZ is designed to enable quick evaluation of the AD8251 programmable gain instrumentation amplifier (PGIA). The evaluation board includes on-board gain setting switches to quickly demonstrate the software gain programmability of the AD8251. In addition, an external logic generator can be connected to the AD8251-EVALZ SMA ports to test the gain control of the PGIA.

Rev. 0

Evaluation boards are only intended for device evaluation and not for production purposes. Evaluation boards as supplied "as is" and without warranties of any kind, express, implied, or statutory including, but not limited to, any implied warranty of merchantability or fitness for a particular purpose. No license is granted by implication or otherwise under any patents or other intellectual property by application or use of evaluation boards. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Analog Devices reserves the right to change devices or specifications at any time without notice. Trademarks and registered trademarks are the property of their respective owners. Evaluation boards are not authorized to be used in life support devices or systems.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2007 Analog Devices, Inc. All rights reserved.

### EVALUATION BOARD HARDWARE QUICK START GUIDE

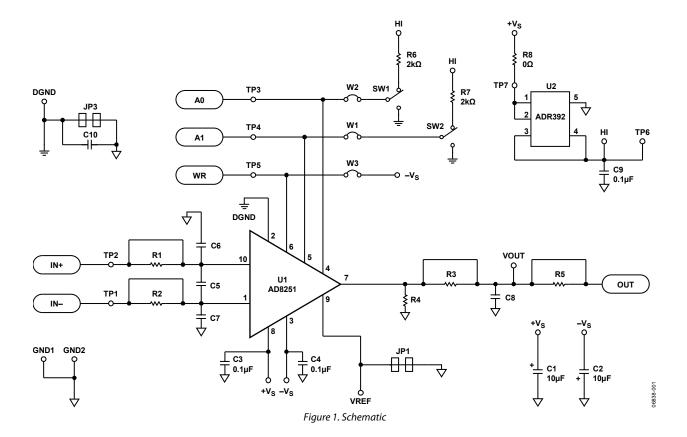

By default, the AD8251-EVALZ is configured for gain change using the on-board switches, SW1 and SW2, as shown in Table 1.

| 8 8         |      |      |      |  |  |

|-------------|------|------|------|--|--|

| W3 (Jumper) | SW2  | SW1  | Gain |  |  |

| In place    | Low  | Low  | 1    |  |  |

| In place    | Low  | High | 2    |  |  |

| In place    | High | Low  | 4    |  |  |

| In place    | High | High | 8    |  |  |

#### Table 2. Default Settings (From the Factory)

| Name                     | Default Status               |

|--------------------------|------------------------------|

| W1, W2, W3               | In place (tied)              |

| JP1, JP3, R1, R2, R3, R5 | Shorted by design (on trace) |

#### **USING EXTERNAL LOGIC TO CHANGE GAIN**

The AD8251-EVALZ accepts external logic signals such as those from logic generators or FPGAs. To change gains using external logic signals, Jumper W1, Jumper W2, and Jumper W3 must be removed. Only then are the A0, A1, and  $\overline{\rm WR}$  pins on the AD8251 directly tied to TP3, TP4, and TP5 (and to the respective SMA connectors). External logic can be tied via the test points TP3, TP4, and TP5, or via the respective SMA connector.

#### **TERMINATION**

The AD8251-EVALZ has 50  $\Omega$  traces leading to the A0, A1, and  $\overline{\rm WR}$  pins. However, it does not have terminations to those pins. If terminations are added, remove Jumper W1, Jumper W2, and Jumper W3.

#### **RFI FILTER**

An RFI filter pattern is included at the input traces of the AD8251-EVALZ. R1 and R2 are shorted. The shorted traces must be cut before R1 and R2 are placed on the board.

#### **OUTPUT FILTER**

An output filter pattern is included at the output trace of the AD8251-EVALZ. To use R3 or R5 in a filter, cut the shorted traces prior to placing resistors in those locations.

#### REFERENCE

To level shift the output, a nonzero reference voltage can be applied to REF. By default, REF is tied to analog GND. Cutting the trace at JP1 opens the connection between REF and analog GND.

#### ANALOG AND DIGITAL GROUND

Analog and digital grounds are tied at JP3. To sever the connection between them, JP3 can be cut with a knife to open the connection between the two grounds.

#### GAIN SELECTION (FROM AD8251 DATA SHEET)

This section shows users how to configure the AD8251 for basic operation. Logic low and logic high voltage limits are listed in the Specifications section of the AD8251 data sheet. Typically, logic low is 0 V and logic high is 5 V; both voltages are measured with respect to DGND. Refer to the specifications table of the AD8251 for the permissible voltage range of DGND. The gain of the AD8251 can be set using two methods.

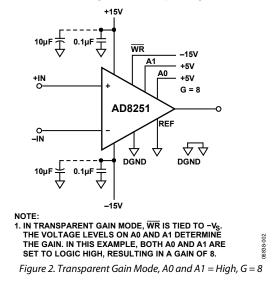

#### Transparent Gain Mode

The easiest way to set the gain is to program it directly via a logic high or logic low voltage applied to A0 and A1. Figure 2 shows an example of this gain setting method, referred to throughout the data sheet as transparent gain mode. Tie WR to the negative supply to engage transparent gain mode. (On the AD8251-EVALZ board, put Jumper W3 in place.) In this mode, any change in voltage applied to A0 and A1 from logic low to logic high, or vice versa, immediately results in a gain change. Table 3 is the truth table for transparent gain mode and Figure 2 shows the AD8251 configured in transparent gain mode.

| WR (W3)        | A1 (SW2) | A0 (SW1) | Gain |

|----------------|----------|----------|------|

| –Vs (in place) | Low      | Low      | 1    |

| –Vs (in place) | Low      | High     | 2    |

| –Vs (in place) | High     | Low      | 4    |

| –Vs (in place) | High     | High     | 8    |

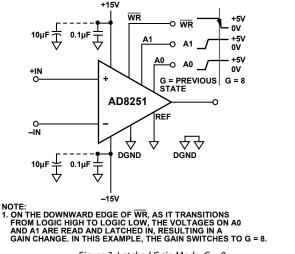

#### Latched Gain Mode

Some applications have multiple programmable devices such as multiplexers or other programmable gain instrumentation amplifiers on the same PCB. In such cases, devices can share a data bus. The gain of the AD8251 can be set using  $\overline{WR}$  as a latch, allowing other devices to share A0 and A1. Figure 3 shows a schematic using this method, known as latched gain mode. (On the AD8251-EVALZ, remove the W1, W2, and W3 jumpers, and drive A0, A1, and  $\overline{WR}$  with external logic to test this gain setting mode.) The AD8251 is in this mode when  $\overline{WR}$  is held at logic high or logic low, typically 5 V and 0 V, respectively. The voltages on A0 and A1 are read on the downward edge of the  $\overline{WR}$  signal as it transitions from logic high to logic low. This latches in the logic levels on A0 and A1, resulting in a gain change. See the truth table listing in Table 4 for more information on these gain changes.

Figure 3. Latched Gain Mode, G = 8

Table 4. Truth Table Logic Levels for Latched Gain Mode

| Tuble II Thui Tuble Logie Levels for Luceneu Guilt froue |                 |                        |             |  |  |  |

|----------------------------------------------------------|-----------------|------------------------|-------------|--|--|--|

| WR <sup>1</sup>                                          | A1 <sup>1</sup> | <b>A0</b> <sup>1</sup> | Gain        |  |  |  |

| High to low                                              | Low             | Low                    | Change to 1 |  |  |  |

| High to low                                              | Low             | High                   | Change to 2 |  |  |  |

| High to low                                              | High            | Low                    | Change to 4 |  |  |  |

| High to low                                              | High            | High                   | Change to 8 |  |  |  |

| Low to low                                               | X <sup>2</sup>  | X <sup>2</sup>         | No change   |  |  |  |

| Low to high                                              | X <sup>2</sup>  | X <sup>2</sup>         | No change   |  |  |  |

| High to high                                             | X <sup>2</sup>  | X <sup>2</sup>         | No change   |  |  |  |

<sup>1</sup> Jumper W1, Jumper W2, and Jumper W3 must be removed and external logic must be used to test latched gain mode.

$^{2}$  X = don't care.

On power-up, the AD8251 defaults to a gain of 1 when in latched gain mode. In contrast, if the AD8251 is configured in transparent gain mode, it starts at the gain indicated by the voltage levels on A0 and A1 upon power-up.

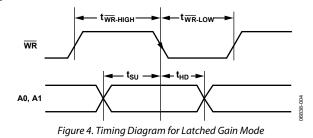

#### Timing for Latched Gain Mode

In latched gain mode, logic levels at A0 and A1 have to be held for a minimum setup time,  $t_{SU}$ , before the downward edge of WR latches in the gain. Similarly, they must be held for a minimum hold time of  $t_{HD}$  after the downward edge of WR to ensure that the gain is latched in correctly. After  $t_{HD}$ , A0 and A1 may change logic levels but the gain does not change (until the next downward edge of WR). The minimum duration that WR can be held high is t  $\overline{WR}$ -HIGH, and t  $\overline{WR}$ -LOW is the minimum duration that  $\overline{WR}$  can be held low. Digital timing specifications are listed in the Specification section of the AD8251 data sheet. The time required for a gain change is dominated by the settling time of the amplifier. A timing diagram is shown in Figure 4.

When sharing a data bus with other devices, logic levels applied to those devices can potentially feed through to the output of the AD8251. Feedthrough can be minimized by decreasing the edge rate of the logic signals. Furthermore, careful layout of the PCB also reduces coupling between the digital and analog portions of the board.

## AD8251-EVALZ

## **ORDERING INFORMATION**

#### **ORDERING GUIDE**

Model AD8251-EVALZ<sup>1</sup>

/ALZ<sup>1</sup> Evaluation Board

**Package Description**

$^{1}$  Z = RoHS Compliant Part.

#### ESD CAUTION

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

©2007 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. EB06838-0-6/07(0)

www.analog.com